# **NANOSIL FINAL REPORT**

**Grant Agreement number: 216171**

Project acronym: NANOSIL

Project title: Silicon-based nanostructures and nanodevices for long term nanoelectronics

applications.

Funding Scheme: NoE

**Period covered:** from January 1<sup>st</sup>, 2008 to March 31<sup>st</sup>, 2011.

Final Report

Name of the scientific representative of the project's co-ordinator<sup>1</sup>, Title and Organisation:

Director of Research Francis BALESTRA, Grenoble INP - CNRS

Tel: +33 (0)4 56 52 95 10

Fax: +33 (0)4 56 52 95 01

E-mail: balestra@minatec.grenoble-inp.fr

Project website address: http://www.nanosil-noe.eu

<sup>&</sup>lt;sup>1</sup> Usually the contact person of the coordinator as specified in Art. 8.1. of the Grant Agreement.

## TABLE OF CONTENTS

| 4.1 Final publishable summary report                                                          | 3   |

|-----------------------------------------------------------------------------------------------|-----|

| 4.1.1 Executive summary                                                                       | 3   |

| 4.1.2 Summary description of project context and objectives                                   | 5   |

| 4.1.3 A description of the main S&T results/foregrounds                                       | 8   |

| 4.1.4 The potential impact (including the socio-economic impact and the wider societal        |     |

| implications of the project so far) and the main dissemination activities and exploitation of |     |

| results                                                                                       | 40  |

| 4.2 Use and dissemination of foreground                                                       | 50  |

| 4.3 Report on societal implications                                                           | 102 |

## 4.1 Final publishable summary report

Coordinator: INPG SA (administrative and financial coordination)

Final Report

- Scientific and project coordination: Grenoble INP

- Project web site: http://www.nanosil-noe.eu/

- Logo:

## 4.1.1 Executive summary

- Introduction: The shrinking dimensions of electronic components will continue in the next two decades. In the sub-10nm range, "Beyond-CMOS" devices will certainly play an important role and could be integrated on CMOS platforms in order to pursue integration down to nm structures. The needed performance improvements for the end of the roadmap will lead to a substantial enlargement of the number of materials, technologies and device architectures. Therefore, new generations of Nanoelectronic ICs present increasingly formidable multidisciplinary challenges at the most fundamental level resulting in an urgent need of academic research, using joint flexible processing, characterization and modelling platforms. During Nanosil, close links with other European Projects, the ENIAC ETP, the AENEAS organization and National projects in the same fields have been established in order to enhance the overall efficiency of the European Research in Nanoelectronics. The interaction between the Scientific Community and the European Industry has also been strenghened. Many Nanosil Partners and Sinano Institute Members have contributed to the "Sinano Institute vision", driven by the European Academic Community, in order to determine the most promising research topics in the More Moore, More than Moore and Beyond CMOS Nanoelectronic domains. During the project, we have studied some of the main scientific and technical challenges put forward by the International ITRS Roadmap and European ENIAC Strategic Research Agenda. Some very important specific actions have also been launched for the strengthening of the durable integration of the NoE: i) seven new Partners became Members of the Sinano Institute in 2009, which is a legal entity (Scientific Association) created in January 2008 for the coordination of the European Academic Community working in the field of Nanoelectronics; ii) the Joint Processing, Joint Characterization and Modelling Platforms, which have been developed and used in the framework of the Nanosil NoE for our joint research activities are now integrated as open Research Infrastructures in the Sinano Institute; iii) Nanosil Partners and Sinano Institute Members have been strongly associated, as representatives of the academic community, to the new initiative launched in 2010 by STMicroelectronics called ENI2 (European Nanoelectronics Infrastructure for Innovation).; iv) a significant part of Nanosil Partners have launched a new FP7 complementary NoE, Nanofunction, and the FET Flagship "Guardian Angels" proposal that has been selected as a pilot project.

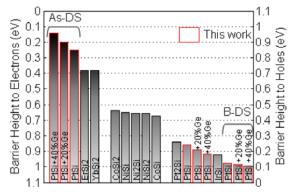

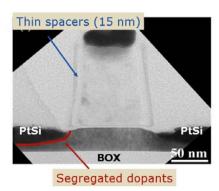

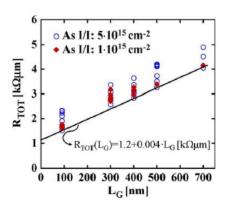

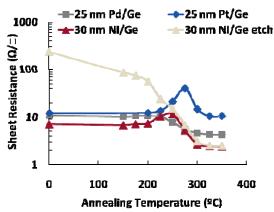

- **WP1:** Many of the aspirations coming out of the SiNANO NoE in terms of network interactions and technological advancements have been realized in NANOSIL, with a a new Flagship Project (FP) concept proved to be effective, and with good cross-FP interactions allowing the realisation of some very challenging device fabrication activity on the processing platform (via WP3). We were also able to very effectively engage related simulation work from WP4. At the onset we knew that the objectives of this WP were very ambitious and certainly world leading. The big results from WP1 include some very significant progress on the realisation of new 'platforms' for future CMOS, primarily based on Ge. Significantly enhanced device hole mobilities were realised, both on insulator (OI) and on new designs of virtual substrates. In the latter case we were able to access IMEC's world leading work on short channel Ge device process, together with the development an implant-free process that is yielding excellent short channel characteristics - initially on bulk Ge. Cumulative network activity strongly suggests that the (110) orientation is required to get the most out of strained Ge, but this has to be on a OI platform to achieve ultimate p-channel performance, and shows excellent prospects for the Ge n-channel. As channel lengths approach the 10 nm regime, contact resistance

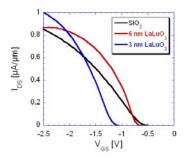

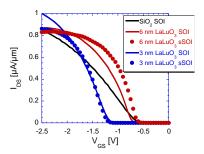

looms as a major performance limiter, particularly so with the concurrent restrictions in thermal budgets imposed by the new channel and gate stack materials. Here we made some very significant advancements using dopant segregation (DS) to reduce Schottky barrier heights to acceptable levels (<0.1eV). DS processes were developed with temperatures generally <600°C, primarily for Pt but also included the first study on Er, which produced the required dopant pile-up of either As (for n- channel) or B (for p-channel) close to the silicide/channel interface. Scaling/integration issues were also addressed, obtaining good short channel device behaviour and enhanced on-currents - requiring low Schottky barrier height and low contact-channel resistance under the spacer layer. Studies of Ni silicide contacts were also undertaken and 80nm DS-NiSi nMOSFETS showed excellent RF performance with good prospects for further downscaling. It was also found that epitaxial Ni produced very low contact resistance on both SOI and SSOI devices. Very recently, we also showed for the first time, that DS can be used to good effect in Schottky barriers to SSOI, giving low barrier heights that decrease with increasing strain (0-40% equivalent), aided by dopant segregation. Early work on Ge channels produced some excellent results, showing very low barriers heights (<0.1eV) for both holes and electrons with DS techniques. On the new gate stack we soon decided to put all our eggs into the LaLuO<sub>3</sub> basket. Undoubtedly HfO<sub>2</sub> has more life left in it, but a new material with higher energy offsets and high k value will be needed by the end of this decade. Our results strongly suggest that this material could meet the required spec of gate leakage, interface state density and bulk oxide trap density. This is a very exciting result coming out of our Network. Without question, however, control of the interfacial LaLuO<sub>3</sub>/Si layer will be critical to achieve low EOT- and maintain high k- values, and here lower processing temperatures could be key. Our forward look (Visionary Project) proved to be a fascinating foray into future nanoelectronics, coming up with the view that Europe should focus activity on FD-SOI technologies including relevant More Moore and Beyond CMOS work, and that there is money to be made in advanced More-than-Moore technologies!

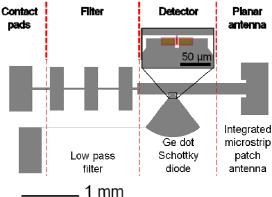

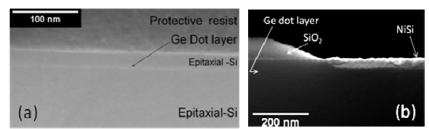

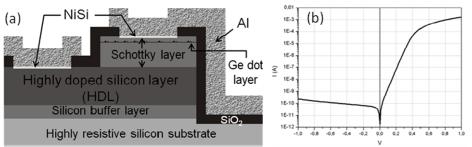

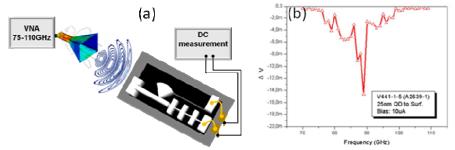

- WP2: The main objectives of WP2 within Nanosil are to explore the horizon beyond CMOS and/or beyond MOORE by following closely the emerging technologies for alternative silicon-based post nano-electronic devices. Embedded within the other work packages of Nanosil, WP2 activities cover a wide spectrum ranging from new fabrication methods and novel switching memory concepts to new functionalities and architectures. These activities were fairly balanced among the different groups working on five sub-tasks: i) Si-Nanowires, ii) Carbon Electronics, iii) Small Slope Switches, iv) Templated Self-Organization and v) Visionary Beyond CMOS. Significant progress has been made in these focused efforts, exemplified by the following selected highlights: i) Fabrication of junctionless multi-gate MOSFET (MuGFET), ii) Significant advances in small-slope switches with a grant of the STREP project STEEPER (steep subthreshold slope switches for energy efficient nanoelectronic circuits), iii) Fabrication of Single Electron Memory Devices, iv) Implementation of Ge-QDs in electrical devices, especially in QD-Schottky diodes with cut-off frequency up to 1,1 THz implemented in mm-wave detection circuits. In general these focused research attempts within the network have provided substantial insight in both the confidence of individual groups as well as the ability to collaborate. A large body of "beyond CMOS knowledge" has been accumulated among leading groups in Europe, providing an excellent platform for future projects as well as a decisive orientation for future industrial roadmaps beyond CMOS.

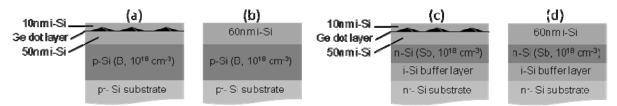

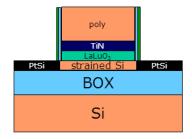

- WP3: The JPP has executed 7 batches of fully processed MOSFETs within NANOSIL. Process modules that have been integrated and evaluated in the MOSFET process line are Dopant Segregated Schottky Barrier contacts and LaLuO3/TiN gate stack on bulk-Si, FD SOI and FD strained SOI. Strained Ge channel PMOSFETs and embedded Ge stressors in N and P bulk MOSFETs have also been fabricated. Substantial work has been performed to adopt and tailor the process modules and the MOSFET fabrication line in order to successfully fabricate MOSFETS with new and innovative architectures and materials. The close collaboration between partners involved in the integration of process modules from FPs into the JPPs MOSFET process line has spurred several collaborations and activities that are envisioned to continue many years after the end of NANOSIL.

- **WP4:** WP4 main objective has been to set in operation and strengthen the Joint Characterization and Modelling Platform that was established in the SINANO NoE, by integrating and validating the modelling approaches and tools against ad-hoc, well-characterized template devices. The core of the activity stemmed from the early definition of common template devices for benchmarking simulation models, including 32 nm and 22 nm gate length Bulk and Double gate MOSFETs and nanowire FETs.

Based on these common work-benches, a number of comprehensive investigations were performed, involving several partners in a truly cooperative effort. The topics spanned from the thorough understanding of the lowfield mobility in biaxially-strained n-MOS and p-MOS transistors, to a comparison of up to eight different transport models, ranging from a 3D NEGF solver including the scattering mechanisms, to a deterministic solver of the one-dimensional Boltzmann transport equation, applied to DG-MOSFETS and nanowires. Other highlights of WP4 include the development of an analytical electron and hole mobility model for ultrathin body FETs on different crystallographic orientations for simulation of SOI-FETs, FinFETs and Silicon nanowires, implemented in the commercial simulator Sentaurus by Synopsys, the calibration of the compact models based also on numerical simulations carried out by NANOSIL partners on template devices, and advances in characterization including a new method to measure the threshold voltage VT in nanoscale transistors and the investigation on the origins of high-field mobility enhancements in uniaxially strained Si by high resolution AFM measurements on strained Si beams with varying degrees of uniaxial strain.

Final Report

**WP5**: Large and growing from year to year number of joint activities (38 in 2008, 47 in 2009, 58 in 2010-11), indicates good and progressive integration of Nanosil partners. It is also reflected by increasing number of within- and cross-WPs/FPs "technical meetings" (18 in 2008, 32 in 2009 and 41 in 2010-11). Partners' integration was reinforced by common PhD students. Then, exchange of personnel served for further strengthening the exchange of knowledge/competence and complementarity between partners. 59 exchanges with total duration of 227 weeks were done during the project. Interaction with industrial partners aiming at roadmapping, assessing the results and assuring theirs transferability to industry was realized through their participation in E&SC Meetings, technical meetings/seminars/workshops; common industry-academia PhD students. Efficiency of partners' integration is proven by high number of joint papers (>100) and joint conference presentations (>130); many newly submitted projects involved 2 or more Nanosil partners, both academia and industry (7 in 2008, 15 in 2009 and 14 in 2010-11). Targeting dissemination of Nanosil knowledge for a wide scientific community, 66 schools/ whorkshops/conferences were organized by Nanosil partners (13 in 2008, 21 in 2009 and 32 in 2010-11) either with or without financial support from Nanosil. Then, Nanosil poster, News Letters, monthly updated Breaking News available on the Nanosil web-site further promote Nanosil achievements. Moreover, 2 books and 33 book chapters published by Nanosil partners assure durable accessibility to the knowledge and developments gathered within Nanosil.

## 4.1.2 Summary description of project context and objectives

**WP1** was devoted to "More Moore" activities that aim to improve CMOS performance for the 22nm node technology and beyond. It has become increasingly clear that for all the exciting developments of "More than Moore" activities there is still a strong requirement for developments of the underlying transistor performance (see D1.10). The outcomes of WP1 should be applicable both in pushing forward highly scaled devices and as technology boosters that allow longer life to existing geometries. Joint activity has focused on three areas that can be expected to provide significant impact on future CMOS - materials for high speed channels, low access resistance, and high dielectric constant gate stacks. Each flagship project has integrated activities in design, fabrication, characterization and modelling, and has been supported in carrying out that work by the Joint Platforms of WP3 & WP4. A fourth activity has provided a forum for discussing hot topics in ultimate CMOS and identifying areas where the partners of this Network can make a contribution, now and in future.

Flagship Project 1.1 New Channel Materials (coordinated by FZJ)

Flagship Project 1.2 Very Low Schottky Barrier MOSFETs (coordinated by ISEN-IEMN)

Flagship Project 1.3 Advanced gate stacks/ High k dielectric materials (coordinated by Chalmers)

Visionary Project 1.4 More Moore Forum (coordinated by GRENOBLE INP-FMNT)

Objective 1.1: To fabricate and investigate new channel materials enabling enhanced mobilities and to assess their properties when transferred to insulator platforms. Specifically to identify the material, platform design, crystallographic orientation, channel direction, layer thickness and strain that maximises electron and hole mobility.

**Objective 1.2:** To develop a global approach to very low Schottky barrier (SB) MOSFETs, including material aspects, device integration challenges, and assessment of this technology as a potential end-of-roadmap solution.

Objective 1.3: To find gate stack candidates for the final chapters of scaling that fulfil the ITRS leakage current targets for high performance, low power and low standby power devices for the 16 nm node. Activities focused on  $LaLuO_3$  to improve leakage of  $TiN/LaLuO_3/Si$  stacks, increase understanding of the  $LaLuO_3/Si$  interface including the nature of the interlayer and tune the  $TiN/LaLuO_3$  workfunction

**Objective 1.4:** To hold discussions that will gather information and understanding, and to generate ideas (brainstorming) from academic partners about some hot topics related to ultimate CMOS devices

• **WP2:** In WP2 many different research aspects have to be considered to explore the future emerging CMOS technologies for fabrication of alternative Si-based Nano-Devices. The investigated approaches include the improving of top-down and bottom-up methods for fabrication of nanostructures for Si-NW devices, novel logic switching devices and devices with new functionalities and/or architectures. In the reporting period an enforced cooperation was established between the WP2 partners and expanded to other Nanosil partners, especially to WP1, WP3 and WP4. The direct collaborations between the partners are clearly visible now. The most activities and achievements were in full accordance to the plan of the FSP proposals. The WP2 network activity has been designed to cover the following flagship projects:

#### **FSP2.1 Si-Nanowires**

The aim of this project was to define advanced fabrication processes in order to move to high performance devices to assure the availabilities of Si nanowires (NW) for characterization, modeling and simulation tasks. In the reporting period the research activities of FSP2.1 were concentrated on investigation and fabrication of Si nanowires by vertical and horizontal growing techniques for new NW-MOSFETs, the fabrication and characterization of Junctionless Si-nanowire MOSFETs, the investigation of dynamic self-heating effects in Fin-FETs including the influence and correlation between the surface roughness and the induced strain on such structures.

The Junctionless multiple-gate MOSFET (MuGFET) proposed and fabricated by the Tyndall group is the most important highlight, published as Breaking News. This device has demonstrated near-ideal sub-threshold slope, extremely low leakage currents, and less degradation of mobility with gate voltage and temperature than classical transistors.

#### P2.2. (Associated STREP) Carbon Electronics

The goal of this associated project was to establish collaboration between European Research Institutions on carbon based electronics.

## FSP2.3 Small slope nanoelectronic switch for low power integrated circuits

In this task, key technological, simulation and modeling contributions for beyond CMOS nanoelectronic switches focused on *Tunnel FET* with very abrupt transition (small slope) between the off and on states were developed. In 2009 a joint STREP FP7 Call 5 proposal STEEPER (Steep subthreshold slope switches for energy efficient nanoelectronics circuits) was prepared. The proposal was evaluated and accepted spring 2010 and is successfully running currently. This STREP proposal coordinated by EPFL based on the participation of four core Nanosil partners and three external industrial partners (Global Foundries, IBM Zurich and Infineon).

## FSP2.4 Templated Self-Organization

This project opened a route from defined positioning of self-organized nanostructures, to functionalization and to fabrication schemes for new integrated devices. The research focus was concentrated on templated growth of Si NWs (vertical and horizontal growth) including electrical operation of NW test devices. Various NW transistors were investigated in comparison to top-down versus bottom-up approaches. In addition the implementation of space charge techniques for characterization of Ge-QDs embedded in Si was investigated. Furthermore Single Electron Memory devices (SEM) were fabricated and electrically characterized. Finally, Ge-QDs were implemented successful in electrical devices in response of the reviewer comments.

The main highlight is obtained by a subtractive process which allowed the successful fabrication of single Si/SiGe-QD floating gate self-aligned to Si-NW channel of Single Electron Memory (SEM) structure. For the

Final Report

fabricated SEM, single electron injection in the floating gate has been demonstrated. Additionally, QD Schottky diodes with cut-off frequency up to 1.1THz have been fabricated and successfully implemented in an mm-wave detection circuit (89GHz RECTENNA). Also, room temperature NDR of Ge QD interband tunneling diodes have been achieved.

#### **Visionary Project 2.5 Beyond CMOS Vision**

The goal of this project was to provide a forum (especially workshops) between European Research Institutions on innovative visionary "Beyond CMOS" ideas. A lot of workshops were provided, for example on Brain-Inspired Electronic Systems (BIECS), on Convergence of Electronics and Photonics and on Beyond CMOS routes.

- **WP3:** Work package 3 is devoted to the Joint Processing Platform (JPP) within NANOSIL. The main objective is to provide partners with a flexible processing platform that can fabricate MOSFETs down to 60 nm gate length. Academic partners within work package 1, 2 and 4 perform research on selected areas such as a particular process module e.g. new channel materials, new high-k/metal gate stacks or Schottky barrier contacts. The purpose of WP3 is to provide a full MOSFET process line where a particular process module can be inserted to evaluate and exploit the potential in fully processed P and NMOSFETs. The JPP is designed to be able to provide short gate length devices but still flexible enough to allow the insertion of new materials and architecture in an early stage of the research. The main objectives are as follows: 1) executtion of MOSFET batches for the flagship projects (FPs), 2) to ensure 3,5 months turn-around time, 3) to coordinate processing between different partners, 4) to fabricate test structures and MOSFETs for WP4 and 5) to develop and integrate processes especially needed for the FPs. KTH coordinated WP3 and had the responsibility to coordinate the MOSFET batches in the JPP for the other work packages and FPs. The JPP is to be seen as a support to the FPs and work within WP3 was dedicated both to tailor and adopt process modules from the FPs as well as tailoring the MOSFET fabrication line in order to integrate the work performed within the FPs. The JPP takes the overall responsibility for the MOSFET fabrication and in close collaboration with partners in WP1 and WP2 coordinate and execute the work needed to integrate a particular process module within a full MOSFET process. Academic partners within WP1 and 2 is thus provided with knowledge and know-how of a flexible full device processing line in order to successfully integrate their work into short gate length MOSFETs. Finally JPP executed batches of MOSFETs with the most promising or scientifically most important process modules as determined in mutual agreement between partners in WP1,2 and 4.

- **WP4:** The European semiconductor research community has a long-standing tradition in the development of tools for electron device simulation, both in Academia and Industry. Over the years, several research groups have tackled the issue of modelling nanoscale transistors adopting different approaches and transport models. Among them, Full Quantum models based on the tight-binding (TB) Hamiltonian provide a detailed physical description of nano-structures, while Semi-classical models based on the solution of the Boltzmann Transport Equation (e.g. by Monte Carlo techniques) have been recently extended to the description of nano-FET inversion layers for both the low field and the far from equilibrium quasi-ballistic regime where conventional TCAD tools become inaccurate. These models underpins the recent developments in the modelling and characterization of strain induced mobility enhancements in advanced CMOS technologies concern both the understanding of the underlying physical mechanisms for the mobility modulation and the design and optimization of the devices.

From the experimental point of view, the electrical characterisation of advanced CMOS devices featuring short channel length and ultra thin gate oxides presents major difficulties. This is mainly due to gate length or gate width shortening, which renders effective channel length/width extraction problematic. Moreover, huge gate leakage makes very difficult to get reliable measurements of C-V characteristics, which prevent correct extraction of basic parameters of MOS structures. Main challenges concern the dielectric-channel interface characterization, the transport assessment in ultra-short devices where ballistic effect should occur, and, reliability or instability issues related to few carrier and few dopant number phenomena.

The main objective of WP4 has been to set in operation and strengthen the Joint Characterization and Modelling Platform that was established in the SINANO NoE. This has been accomplished by a two-fold approach: from one end specific problems were tackled by single partners or by a small cluster of partners; on the other end a relatively large number of partners joined forces to integrate and

validate the most advanced modelling approaches and tools against ad-hoc, well-characterized template devices. Successful examples of this truly cooperative activity, are: the results reported in D4.1 (definition of template devices), a thoroughly comparison between the MC simulators (semi-classical model) for a subset of template devices [1], and a comprehensive comparison of full-quantum vs. semi-classical models carried out on the most advanced template devices, including model assessment.

We believe this is an important objective of the NANOSIL Network of Excellence, since such a systematic comparison can be a useful guide to a young researcher entering the field, and can represent in an objective way the relative merits of different tools to a large group potential users, both in Industry and in Academia. [1] F. Bufler, et al., the 14th International Workshop on Computational Electronics (IWCE-14) Conference, Pisa 2010.

- **WP5:** The main goal of WP5 is to reinforce the integration and spread of knowledge between Nanosil partners as well as promoting the network and its achievements towards the whole scientific community. The particular objectives are as follows:

- coordination/stimulation of joint activities between partners by WPs leaders;

- integration between partners through common PhD students, personnel exchanges, etc.

- collaboration with other European and national projects;

- Spreading of excellence / dissemination of knowledge inside and beyond Nanosil through the organization/participation in workshops, courses, conferences, etc.

## 4.1.3 A description of the main S&T results/foregrounds

#### WP1:

## **FP1.1 New Channel Materials**

## Strain inducing platforms

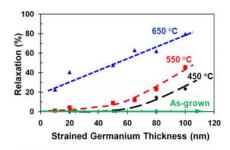

Throughout NANOSIL strain continued to be one of the prime performance boosters with no sign, at least from simulation, of significant saturation up to  $\approx$ 4GPa. Although primarily achieved by local processing techniques, global inducement remains a good approach for at least development work. Also the leverage for a move to on-insulator(OI) platforms for mainstream production remains high and certainly in the low power regime where many of the killer applications are.

There was significant related activity in NANOSIL in these areas, the highlights being:

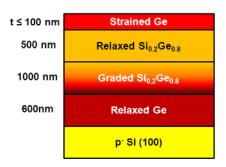

#### *a)* Reverse graded (100) virtual substrates

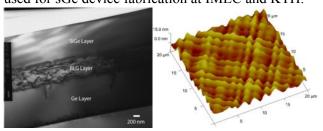

By compositionally "reverse" grading from a Ge layer grown on Si it was found possible to produce relatively thin and smooth high Ge strain tuning platforms compared to growth directly from Si. A CVD process was developed(Warwick) giving platforms of 80% Ge content with a roughness of  $\approx$ 2.5nm (Fig 2). These were used for sGe device fabrication at IMEC and KTH.

**Fig 2.** Reverse graded virtual substrate in cross section TEM view and surface profile from AFM.

**Fig 3**. XTEM of re-grown 24 nm strained Si layer on 45%Ge VS, AFM image indicates a smooth surface (roughness < 1 nm).

#### b) High strained SOI and sGeOI platforms

Development work to create high strain (up to≈ 6GPa) SOI and sGeOI platforms was initiated on Nanosil though a collaboration with Juelich and MPI-Halle (sub-contracted to Juelich). For high sSOI a CMP process was developed at IMEC on 30, 40, 50% and 80% virtual substrates yielding a smooth (roughness in range 0.4 to 0.1nm) and clean surface, Fig. 3. Si CVD regrowth on these VSs yielded a comparably smooth sSi layer. sGe layers on reverse graded VSs were also shipped to Halle for early development work on a sGeOI process. but as with the high sSOI, only very limited layer transfer work has been possible at Halle due to resource limitations. But this remains an on-going activity involving Juelich, MPI-Halle and Warwick.

#### **Ge MOSFETS**

**NANOSIL**

Vd=-20mV WxL=10x10um2 Split CV mobility (cm<sup>2</sup>/V.s) 200 #07 - strained Ge 150 100 50 0.0 0.2 0.4 0.6 0.8 Effective Field (MV/cm)

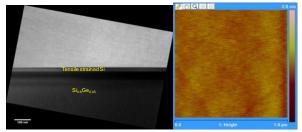

Fig 4: 65 nm strained Ge MOSFET fabricated at IMEC on wafers grown at Warwick.

Fig 5: Hole mobility boost from strained Ge by 70%, including boost at high field (long channel devices).

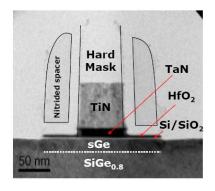

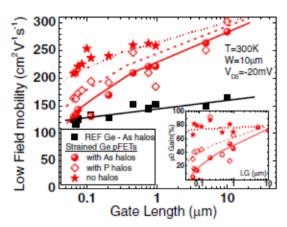

Interest in the Ge channel remains intense particularly as n-channel work now looks as promising as the initial p-channel. There has been very significant work looking at sGe devices on the reverse graded 80% VSs. These VSs were considered sufficiently smooth for this early work and 25, 200mm wafers complete with sGe overgrowth were shipped to IMEC to access their low temperature short-channel process (Fig 4). These produced some very interesting device data showing that this level strain yielded significant mobility enhancements (up to 70% compared to the bulk Ge devices) (Fig 5) and drive current enhancement up to 35% in 100nm devices. Short channel device performance was, however, compromised by local strain relaxation in the halo implanted regions causing a progressive loss of the mobility advantage in shorter channel devices (Fig 6). Following this work an implant-free process is being developed at IMEC, showing considerable promise in short channel bulk Ge MOSFETs.

Fig 6. Low-field mobility of holes in strained and relaxed Ge pMOSFETs as a function of gate length showing the effects of different halo implants.

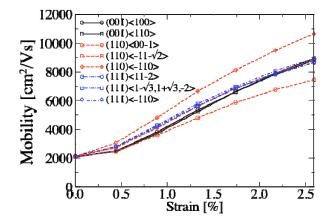

Fig 7: Variation of Ge hole mobility with strain for different substrate/channel orientations. The maximum strain of 2.6% corresponds to 60% Si in the relaxed Si<sub>1</sub>. <sub>x</sub>Ge<sub>x</sub> substrate.

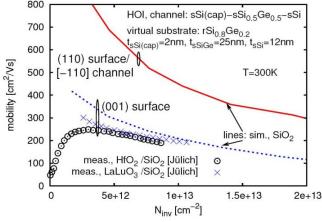

Related simulation work (Glasgow) indicating the advantage of sGe as a channel material particularly for different crystallographic orientations (Fig. 7), with (110) showing particular promise, especially with OI platforms, which avoid high channel doping – which can kill this advantage. This activity continues looking at both hole and electron mobility enhancements in (110) and (111) orientations and new funding is being sort. A further batch of sGe devices is being undertaken very recently at KTH. It was intended that the gate dielectric was to be the Juelich's very exciting  $LaLuO_3$  and work was carried out involving a passivating  $Al_2O_3$  layer to produce a working gate stack ( TiN gate metal) on r-Ge and s-Ge channel layers (Fig 8). This was however not ready in time and an alternative gate stack fabricated at KTH is being used. This device batch complete with a qualified NiGe contacts is scheduled for completion very shortly. This work on sGe devices involving KTH, Warwick and Juelich will continue beyond Nanosil.

**Fig 8:** Mobility characteristics of strained SiGe HOI (001) and (110) PMOS with different gate oxide dielectrics.

Fig 9: Mobility in (110) Si depending on channel direction.

#### (100) heterostructure-on-Insulator (HOI) Platforms

These structures enable enhancement of both electron and hole mobilities by combining tensile strained Si and compressively strained SiGe layer OI. In all cases high k dielectrics were used in the gate stack. High mobility short channel p-MOSFETs with compressively strained Si<sub>0.5</sub>Ge<sub>0.5</sub>/sSOI channel and TiN/HfO<sub>2</sub> or TiN/GdScO<sub>3</sub> gate stacks were demonstrated (Juelich).

Good short channel (100 nm) behaviour was seen and hole mobilities as high as 260 cm<sup>2</sup>/Vs were achieved and approx 200 cm<sup>2</sup>/Vs was obtained in strong inversion, about a 2.5x enhancement compared to Si/SiO<sub>2</sub> devices. This all indicates good potential for further scaling. Simulation work (TUBS) showed good agreement with this mobility behaviour and that further enhancements were to be had from comparable (110) platforms (Fig 8).

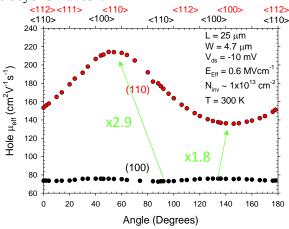

## (110) Platforms

Some early work was undertaken involving (110) oriented Si substrates.

#### a) Hole mobility enhancement

Hole mobilities were measured (Warwick) in devices fabricated at KTH in high inversion on (110) Si layers grown by CVD. Mobility enhancements approaching x3 were seen depending on channel direction, similar to previously reported (Fig 9). However, simulation by Granada indicated these arose from variations in effective mass in the heavy hole band as opposed to scattering variations.

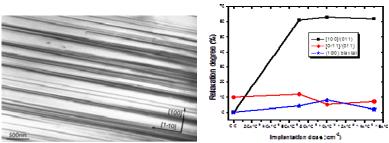

#### b) Global uniaxial strain

Uniaxial strain is optimal for mobility enhancement in many cases and a global uniaxially strain platform is a potentially significant development. A thin (50nm) SiGe layer was deposited on (110) Si, followed by a 5nm thick Si layer(LETI). The SiGe was then relaxed using the Juelich process, creating a smooth tensile strained top Si layer where strain relaxation was predominantly in the [100] direction (Fig 10).

Fig 10: Uniaxial strained (110) Si, showing anisotropic relaxation

#### FP1.2 Very Low Schottky Barrier (SB) MOSFETs

It is widely recognized that source/drain (S/D) engineering takes an increasing importance in the development of leading edge CMOS generations because of the increasing impact of S/D series resistances on transistor performance. To address this challenge, Flagship project 1.2 has proposed to implement metallic S/D combined to a dopant segregation (DS) strategy to control the doping profile of S/D regions and to mitigate the impact of high thermal budget on new sensitive materials introduced in the gate stack. The first benefit is to potentially reduce the specific contact resistance of the metal/semiconductor junction, while keeping activated dopants sharply localized at the interface. The second benefit is to dramatically lower the junction annealing temperatures to ensure compatibility with many candidate material systems used in alternative gate stacks that cannot stand high temperature processing. By demonstrating performance comparable to conventional implanted and annealed contacts, the DS-SB technique becomes highly relevant for future implementation. Over the of entire duration of the NANOSIL project, significant advances have been achieved within the framework of FSP1.2 bearing on 'Very Low Schottky Barrier MOSFETs', through the seven complementary tasks below: Over the full duration of the Nanosil project, the activity in this FSP1.2 has been the object of 48 peer-reviewed international publications, 30 of which in journals and 18 in conferences/workshops.

#### Schottky contact engineering by dopant segregation,

As far material engineering is concerned, dopant segregation has been extensively investigated for producing very low Schottky barrier heights, including some work on contact resistance for both n- and p-type source/drain. Many silicide/dopant couples have been studied and included rare earth silicides (erbium, ytterbium), the use of plasma doping, and how carbon incorporation can improve arsenic pile-up leading to a concomitant barrier lowering. The targeted sub-0.1 eV effective barrier height has been demonstrated through several dopant/silicide systems.

#### Integration issues and compatibility associated to alternative silicides

This task focused on integration strategies and issues associated to segregated Schottky S/D contacts. Original achievements have been obtained, such as the selective etching method of Pt with respect to PtSi using a sacrificial low-temperature germanidation process, the validation of Ti-capping layer strategies to protect rare-earth silicides from oxidation, the determination of the volume expansion upon platinum silicidation applied to nanowires and the dramatic yield improvement in SB-MOS process through accurate placement and engineering of gate-to-S/D spacers.

## Scalability of the DS technique

The scalability of the S/D dopant segregation on ultra-thin SOI has been consolidated through the integration of many different flavours of dopant segregated contacts. State-of-the-art results have been obtained like the demonstration of DS CMOS technology, the in-depth study of variability directly related to the DS Schottky architecture or the extremely low contact resistivity of the NiSi2 phase.

## Impact of strained silicon on dopant segregated Schottky contacts

The integration of Schottky S/D on strained SOI and the coupling of n- and p-type DS Ni and Pt silicides to strained SOI layers has been systematically studied for the first time. It has been shown that bi-axial tensile strained SOI layers (0-40% equivalent strain) contribute to lower the effective SB, as expected from valence

and conduction band shifts, and was amenable to the DS technique. Complementarily, ultra-thin epitaxial NiSi2 on highly doped SOI and on biaxially tensile strained SOI substrates was found to be about one order of magnitude lower than that of a NiSi layer on both As and B doped SOI and sSOI (Fig. 11). The measured SBHs for PtSi on sSOI are given in the table below.

|                      | No DS(φ <sub>bp</sub> meV) | B ITS DS(φ <sub>bp</sub> meV) | As ITS DS (φ <sub>bn</sub> meV) |

|----------------------|----------------------------|-------------------------------|---------------------------------|

| Unstrained SOI       | 250                        | 125                           | 270                             |

| sSOI (20% Ge buffer) | 210                        | 115                           | 220                             |

| sSOI (40% Ge buffer) | 183                        | 105                           | 160                             |

Final Report

Fig 11: Extracted SBHs in strained Si, showing reduction with increasing strain and DS.

Fig, 12: Extractred SBH of PtGe2/n-Ge contacts as a function of implantation dose.

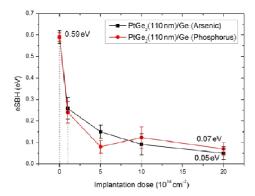

## Relevance of the DS technique on germanium

The synthesis of uniform NiGe and PtGe2 layers has been demonstrated on GOI and SiGe. Extremely low SBs to holes (<0.1eV) were obtained for both silicides. For PtGe2, As and P dopant segregation leads to less than 70 meV SBH to electrons (Fig 12), although it is not as effective in NiGe. The morphology of NiSiGe layer was shown to improve with C implantation into the SiGe, which increases the thermal stability of NiSiGe by about 200 °C.

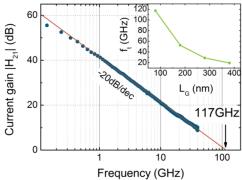

## Benchmarking of the DS technique

The DS SB-MOS technology has been further consolidated with the demonstration (Fig 13) of state-of-the-art RF performance of 80 nm As-segregated NiSi n-MOSFETs featuring a unity current gain cut-off frequency of 140 GHz. This result completes similar performance at 180 GHz previously obtained for 30 nm p-MOSFETs.

Fig, 14: Multi-subband Monte Carlo simulation of FD-SOI SB MOSFET at 32 nm gate length.

## Simulation and modelling of DS systems.

Finally, simulation studies based on drift-diffusion, Monte Carlo (Fig 14) and Green's function have supported the analysis and understanding of SB-MOSFETs operation in many respects encompassing both static and dynamic modes.

## FP1.3 Appraisal of Gate Stack Materials for End of CMOS Era

#### Focused activities on LaLuO3

At an early stage of NANOSIL, two gate dielectrics, GdSiO and LaLuO<sub>3</sub>, were selected as interesting choices for fulfilling the targets set in the DoW. As described in Delivery D.1.12, for GdSiO, which was successfully used for the 22 nm ITRS node in the PULLNANO project, the lower EOT values needed for the present project made it unpractical by technological reasons. Taking into consideration the outstanding properties of LaLuO<sub>3</sub>, we decided at the end of 2008 to focus on this oxide.

#### Sample preparation and measurement techniques

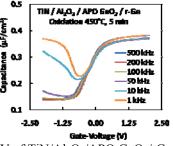

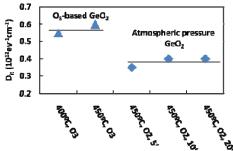

For the investigation of current leakage, electrical interface properties and bulk oxide traps, MOS capacitors have been used throughout the project, prepared on 3 inch, 1 – 10 ohmom n- and p- silicon wafers. The LaLuO<sub>3</sub> dielectric was deposited by molecular beam deposition (MBD) at FZ Jülich, combined with TiN metal contact preparation by sputtering at AMO. For n-type wafers an n<sup>+</sup> backside doping has been necessary, which was prepared at Chalmers. Samples were processed with physical oxide thicknesses of 3, 6, 20 and 40 nm in each set, and were sent out to all experimental groups. Special samples have been prepared for physical investigations (VASE, XPS, MEIS, AFM, STEM, EELS, IPE and Raman spectroscopy) at Liverpool, ITE and Tyndall. The rest of the experimental groups, including Liverpool, ITE, Tyndall, WUT, AMO, INPG/FMNT, Sapienza and Chalmers have been engaged in electrical characterization (C-V, I-V, G-V and multi-parameter admittance spectroscopy (MPAS)). FD SOI transistors were prepared by FZ-Jülich.

#### Current leakage

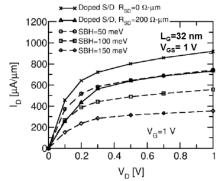

For our MOS-capacitor samples with EOT in the range 0.9 - 1.0 nm, a current density of 0.3 A/cm<sup>2</sup> was obtained at 1.5 V gate voltage. A simulation for "calibrating" results from MOS-capacitors to corresponding data for FD SOI transistors with 16 nm gate length was performed. From this, we found that MOS-capacitors with the materials data used are expected to have a 1.5 times higher leakage than the corresponding FD SOI devices. Therefore, in our comparison with the ITRS Roadmap, we use a leakage current vaue of 0.2 A/cm<sup>2</sup>, which fulfils ITRS requirements for LSTP and for 14 - 12 nm gate lengths. (Fig.15, below).

| Year of prod.                                                | 2013 | 2015 | 2017 | 2019 | 2021 | 2023 | This<br>work |

|--------------------------------------------------------------|------|------|------|------|------|------|--------------|

| Physical gate length                                         | 22   | 17   | 14   | 11.7 | 9.7  | 8.1  |              |

| Bulk,EOT (mm)                                                | 0.9  |      |      |      |      |      |              |

| Bulk, gate leak.<br>(A/cm²)                                  | 0.15 |      |      |      |      |      |              |

| MuG SO , EOT<br>(nm)                                         |      | 1.1  | 1    | 0.9  | 8.0  | 0.7  | 0.9 -<br>1.0 |

| MuG SO , gate leak.<br>(A/cm²)                               |      | 0.19 | 0.23 | 0.30 | 0.38 | 0.45 | 0.2          |

| Interface state dens.<br>(10 <sup>11</sup> cm <sup>2</sup> ) |      | 2    | 2.2  | 1.8  | 1.9  | 1.9  | 3.0          |

| Oxide state dens.<br>(10 <sup>18</sup> cm <sup>-3</sup> )    |      | 0.89 | 1.3  | 1.0  | 1.8  | 1.2  | 1.3          |

| Supply voltage (V)                                           |      | 0.95 | 0.85 | 0.85 | 0.75 | 0.75 |              |

| Sat. drive current<br>(m/V/μm)                               |      | 0.51 | 0.97 | 1.16 | 1.08 | 1.29 |              |

| Off-state current<br>(nA/µm)                                 |      | 0.1  | 0.1  | 0.1  | 0.1  | 0.1  |              |

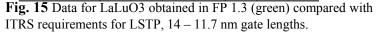

**Fig.16:** Band diagram for the TiN/LaLuO3/Interlayer/Si stack with barriers measured by XPS and IPE

## Interface states and interlayer

Similar to all high-k/Si interfaces investigated by us earlier (HfO<sub>2</sub>, PrO<sub>2</sub>, HfPrO<sub>2</sub>, Gd<sub>2</sub>O<sub>3</sub>, GdSiO, LaSiO), the P<sub>b</sub> centre is recognized also at the interface between LaLuO<sub>3</sub> and silicon. Furthermore, a second type of centres with a different mechanism for electron capture was found. The interface state concentrations obtained

were found to be close to the specifications for the 14 - 12 nm gate length requirements by ITRS (Fig. 15). Controlling the high-k/Si interlayer will be a crucial issue for reaching the end of the Roadmap at 8 – 5 nm gate length. The LaLuO<sub>3</sub> interlayer was investigated by XPS and found to be an SiO<sub>x</sub> like layer with a clear content of the metals included in the high-k dielectric, without a significant deviation from  $k \approx 4$  of this material. This was also supported by preliminary MEIS data.

Final Report

#### **Bulk** oxide traps

Bulk oxide traps were investigated by C-V, pulse C-V, variable angle spectroscopic ellipsometry (VASE), luminescence and charge carrier statistical considerations. An interesting agreement with theoretical literature estimates of energy level positions for oxygen vacancies in HfO<sub>2</sub> and with charge carrier statistics was found. Corresponding theoretical considerations for LaLuO<sub>3</sub> predict energy a level scheme for oxygen vacancies very similar to that of HfO<sub>2</sub>. Continued experimental confirmation in this area is vital for future development. The total concentration of bulk oxide traps, in the ITRS definition fulfils the requirements for 14-12 nm gate lengths.

#### **Energy barriers**

TiN/LaLuO<sub>3</sub> and LaLuO<sub>3</sub> energy barriers were measured by XPS and internal photo emission (IPE) with results as shown in Fig. 16.

#### **Transistor data**

Test transistors with LaLuO<sub>3</sub> gate dielectrics were prepared by FZ Jülich. Strained and unstrained SOI n/p-MOSFETs were fabricated with a full replacement gate process. The LaLuO3/Si interface showed a Dit level of 4.5 × 1011 (eV cm2)-1. Fully depleted n/p-MOSFETs with LaLuO3/TiN gate stacks indicated very good performance with steep subthreshold slopes of ~ 70 mV/dec and high Ion/Ioff ratios. In addition, strained SOI showed enhanced electron mobilities with a factor of 1.7 compared to SOI. Both electron and hole mobilities for LaLuO3 on SOI were similar to the mobilities reported for Hf-based high-k devices.

#### Relation to the ITRS Roadmap and conclusion

ITRS relevant data for the LaLuO<sub>3</sub> dielectrics investigated in FSP1.3 is shown in Fig. 15. Depending on future development of the LaLuO<sub>3</sub>/Si interlayer, we consider this dielectric as a potential candidate for fulfilling the requirements along the ITRS Road down to the tapered 8-5 nm end.

#### **VP1.4 More Moore Forum**

The visionary project was designed as a forum to exchange ideas, create discussion and debate, and generate synergies between partners on the topic of advanced CMOS. It was also the opportunity to discuss challenges that are not addressed within flagship projects. Finally, as these meetings also gather non-Nanosil speakers, it is also the occasion to embrace research carried out outside the network, and outside Europe.

Ten workshops were organised during Nanosil, details of which appear in D1.1, D1.5 and D1.10:

- 1. Satellite event of the Third SINANO Device Modelling Summer School, Bertoni, Italy, 2008 "Low Field Transport in Advanced MOSFETs"

- 2. Satellite event of ESSDERC 2008, Edinburg, UK "CMOS variability research in Europe: from atomic scale to circuits and systems"

- 3. Panel session at EUROSOI 2009,

- "What is the killing advantage of multiple-gate SOI MOSFETs: electrostatics and scalability, transport or functionality?"

- 4. Fringe workshop at ULIS 2009, Glasgow, UK

- "Open questions in the Ion Ioff optimisation in Advanced MOSFETs",

- 5. Panel session at the 2nd International Conference on CMOS Variability (ICCS).

- "Are we ready for Design for Variability at sub 32 nm?",

- 6. Satellite event of the European MRS Meeting, Symposium I on "Silicon and Germanium issues for future CMOS devices"

- "High-Mobility Channel Materials and Device Performance",

- 7. Panel session organized during EuroSOI meeting in 2010 Grenoble:

- "SOI technologies: What kind or research for what kind of products?"

- 8. Workshop and panel before ULIS 2010 Glasgow, 17th March 2010: "High mobility nMOS substrates: strained-Si, Ge or III-V?"

- 9. Workshop and panel before SISPAD 2010 Bologna, 9th September 2010 : "Simulation and Characterization of Statistical CMOS Variability and Reliability"

- 10. Workshop after ESSDERC 2010, Friday, Sept. 17th, 2010

Final Report

"At the convergence between More Moore and More Than Moore / Beyond CMOS activities".

#### **Recommendations for European R&D:**

- 1. European R&D should pursue effort in developing FDSOI technologies, as it is now or never for SOI

- 2. More Than Moore activities should be encouraged and supported; however, without neglecting More Moore and Beyond CMOS. Projects that develop the three activities all together should be

- 3. As highlighted by variability, technology and design should work in closer contact. Europe has expertise in both areas. Research and projects integrating technology and design should thus be promoted.

- **WP2:** The main scientific and technical results of WP2 can be described and distributed by the following selected contributions delivered by the mainly experimental flagship project groups FP 2.1, FP2.3 and FP 2.4.

#### FP2.1 "Nanowires"

#### Vertical Si nanowires

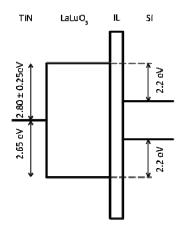

Vertical nanowires based FET is an interesting opportunity for nanoscale devices because of its miniaturization capabilities and its compatibility with wires produced by top-down but also by bottom-up approaches. Nevertheless, this technology is faced on specific technological challenges due to the 3dimensionnal configuration. One example is the contacting of each termination of the Si NWs in order to electrically characterize the structures and to reproduce the configuration of S/D contacts of a future FET device. Previously we demonstrated the formation of highly dense vertical NW arrays by a top-down approach, with 100% reproducibility, and a perfect control of the diameter and the position. In a present work, we demonstrated the fabrication and characterization of two-terminal structures implemented on such NWs arrays defined by a top-down approach, as presented in Fig.1. Each termination of NWs is silicided and contacted to an external metal line. Thanks to a precise control of the radius and number of NWs in an array, we demonstrate a perfect reproducibility in the I-V characteristics (Fig.2) when a large number of NWs is considered (up to 5100 NWs in parallel) compared to a single NW, which proved to be efficient to considerably attenuate variability associated to the stochastic nature fabrication process steps at nanoscale. The temperature dependence and the non-linearity of I-V characteristics (inset Fig.2) are identified as a clear signature indicating that contacts dominate the overall resistance of the NWs arrays.

Fig. 1. (a) SEM image of vertical NW arrays (18x18=324 in parallel) with Φ=32nm, L~200nm, 100% reproducibility and hetero structure PtSi/Si. (b) SEM image (40° titled view) of Al extrinsic measurement pads. Inset: Image zoom on NWs arrays. (c) Schematic cross section view of the measurement set-up that can be schematized by two back to back metal-semiconductor

Fig. 2. average current per NW as function of the applied voltage @ 20°C of 2 contacts device with several NWs in parallel from 1 to 1296 with  $\Phi$ =52nm with, in inset, current evolution with the temperature.

junctions separated by a series resistance. (d) TEM image (cross-section view) of a NWs array embedded in a dielectric SiOx planarization layer. Al is deposited to act as a top contact.

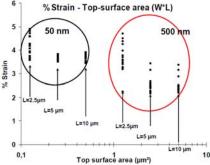

## Self-heating characterization at UNEW of strained Si nanowires from EPFL

100 nm wide Si nanowires were fabricated using a bulk top-down Si nanowire platform, 0.8 μm lithography, hard mask and spacer technology. In the process, a sacrificial oxidation step was used to diminish the size of the wires and introduce tensile strain. Direct strain characterization on the suspended bucked Si NWs represents non-uniform lateral uniaxial tensile stress with a maximum almost at the middle of the Si NW. Strain measurements on EPFL devices have been performed by University of Newcastle. The maximum found tensile stress was 2.6 GPa and the peak of stress depends on the dimensions of the wire (thickness and length), oxidation conditions (temperature and duration) and hard mask. The wire length and wire width on the mask varies from 2.0-20.0 μm and 0.8-1.8 μm, respectively, offering a wide range of Si NWs with different strain and cross-sections (the longer and narrower wires offer suspended and buckled triangular Si NWs after oxidation and stripping steps suitable for gate-all-around architecture after gate stack deposition, however the shorter and wider wires offer attached wires to the substrate suitable for omega-gate architecture). The gate-stack includes ~15 nm SiO<sub>2</sub> (thermal oxide) and 300 nm of in-situ N+ doped poly-Si.

In collaboration with the Newcastle University, the self-heating effects in those devices have been investigated as a function of the wire cross-section. A clear increase of the self-heating impact for narrower wires was observed.

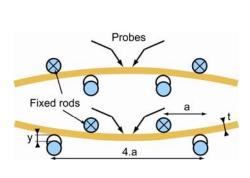

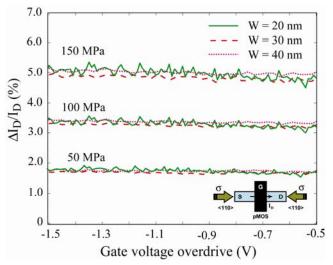

#### Junctionless Si nanowire MOSFETs

Prof. J.-P. Colinge and his research group at Tyndall have been working on the static characterization of junctionless Si nanowire multigate MOSFETs (uniformly and highly doped from the source to drain contacts). The Si nanowire is completed depleted at OFF state ( $V_g = 0 \text{ V}$ ) and is neutral at ON state ( $V_g > V_{th}$ ). The advantages related to the absence of source-to-channel and drain-to-channel junctions and the volume conduction in ON state have been highlighted. They have a near-ideal subthreshold slope, close to 60 mV/dec at room temperature, extremely low leakage currents, exhibit less degradation of mobility than classical transistors when the gate voltage is increased. Of course, due to the high doping level in the channel the poor carrier mobility is the major limitation of those novel devices. However, as for other advanced MOSFETs, strain channel engineering might be applied to improve the carrier mobility. Recently, in collaboration with UCL, static characterizations of junctionless multigate MOSFETs (MuGFET) as a function of an applied mechanical stress using a 4-point bending setup (Fig.3) have been performed. Improvement of current drive in n- and p-type silicon junctionless MOSFETs using strain has been demonstrated. The extracted piezoresistance coefficients are in good agreement with the piezoresistive theory and the published coefficients for bulk silicon even for 10 nm-thick silicon nanowires as narrow as 20 nm (Fig.4). These experimental results demonstrate the possibility of enhancing mobility in heavily doped silicon junctionless MOSFETs using strain technology. These results have been recently published<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup> J.-P. Raskin, J.-P. Colinge, I. Ferain, A. Kranti, C.-W. Lee, N. Dehdashti Akhavan, R. Yan, P. Razavi, R. Yu, "Mobility improvement in nanowire junctionless transistors by uniaxial strain", *Applied Physics Letters* **97**, 042114 (2010).

Fig. 3. 4-point bending measurement setup and relationship between the induced stress  $(\sigma)$  and vertical displacement (y) of the bottom movable rods. For all measurements, the spacing "a" was equal to 20 mm.

**Fig. 4.** The variation of drain current, ΔID/ID, as a function of gate voltage overdrive, VGS-VTH, in a p-type junctionless MuGFET characterized by fin width of 20, 30 or 40 nm for various applied compressive stresses.

## Low frequency noise characteristics of silicon nanowires (FMNT-IMEP)

Final Report

Low-frequency noise has been studied by INPG in collaboration with CEA-LETI in compressively strained  $Si_{0.8}Ge_{0.2}$  core-shell nanowire (NW) p-channel transistors compared with un-strained NWs. The noise has been well interpreted using the carrier number with correlated mobility fluctuation model. As a result, un-strained devices present more surface mode operation than c-strained ones, rendering more efficient the remote Coulomb scattering from oxide/Si cap interface charges and, thereby, increasing the  $\alpha$  coefficient in CMF process. According to the remote Coulomb scattering theory, a reduction of one decade of  $\alpha$  corresponds to about 1.7 nm additional remoteness for c-strained NWs, which is in agreement with the effect of silicon cap around  $1{\sim}1.5$  nm.

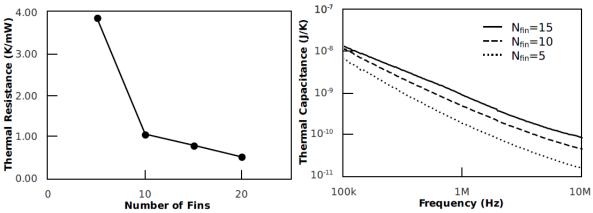

#### **Dynamic self-heating in Fin-FETs**

Dynamic self-heating effect has been characterized in n-channel FinFETs on Silicon-on-Insulator (SOI) platform. RF extraction technique has been deeply analyzed and dependence of thermal resistance on fin width  $(W_{fin})$ , number of parallel fins  $(N_{fin})$  and fin spacing  $(S_{fin})$  was studied.

One of the conventional techniques to characterize self-heating effect in MOSFET which does not require special structures is small-signal AC conductance. It is based on the assumption that at high frequencies channel temperature does not follow voltage oscillations, hence dynamic self-heating is removed. Conductance difference at low and high frequencies (where AC self-heating is removed) can be translated into device thermal resistance. Typical frequencies used in the AC conductance technique are in kHz-MHz range. However, as devices scale down thermal time constants are reducing into ns values and higher frequencies are required to reach self-heating-free characteristics. Indeed, thermal time constant is the product of thermal resistance and thermal capacitance. Whereas thermal resistance is inversely proportional to the surface area of the device, the thermal capacitance is related to its volume. In advanced non-planar devices volume-to-surface ratio is drastically decreasing which leads to smaller time constants. RF extraction technique up to a few GHz was applied to extract self-heating effect parameters in n-channel SOI FinFETs of various geometries. It was found that self-heating is mostly sensitive to number of parallel fins per gate finger (Fig. 9) and less to the fin width and fin spacing. Higher number of parallel fins, increased fin width and fin spacing improve thermal properties of Fin-FETs, however it may introduce additional issues into chip design, poorer electrostatic control and reduced integration density. These results have been obtained in collaboration between UCL and Newcastle University.

Fig. 9. Variation of thermal (a) resistance and (b) capacitance in the devices with different number of parallel fins per gate finger.  $W_{\text{fin}} = 22 \text{ nm}, S_{\text{fin}} = 328 \text{ nm}$

#### Nanomechanical characterization of Si nanowires

Nanomechanical characterization of released silicon nanowires using on-chip loading has been investigated. The aim of this action is to experimentally study the electro-mechanical properties of Si nanowires using the proprietary lab-on-chip methodology developed at UCL. The basic idea is to use internal stress present in one film (named actuator) to provide the actuation for deforming another film (named specimen) attached to the first film on one side and to the substrate on the other side. The measurement of the displacement resulting from the release of both films gives access to the stress and the strain applied to the test specimen provided the Young's modulus and mismatch strain of the actuator film are known. The Si nanomachines have been fabricated at Chalmers University of Technology and released and characterized at UCL. The fracture strain of Si nanowires as a function of the nanowire cross-section and length has been investigated (Fig. 11). Fracture stress as high as 9 GPa has been measured for nanowires with a cross-section of 50 nm x 50 nm. The next step is to measure the I-V characteristics of these strained Si nanowires to extract piezoresistance coefficients in two-dimensional confined Si nanostructures at high level of strain.

Fig. 11. Fracture strain in Si as a function of nanowire dimensions.

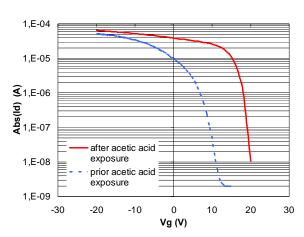

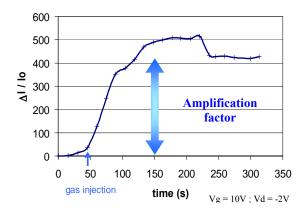

#### Si nanowires as gas sensors

Doped and undoped Si nanowires presenting cross-sections from 100 nm x 50 nm down to 25 nm x 50 nm have been functionalized and used to detect specific gases. A shift of more than 10 V (Fig. 12) of the Si NWs transfer characteristic has been observed when exposed to acetic acid vapour. The observed current change factor for a fixed back gate voltage of 10 V is of approximately 500 (Fig. 13). The sensitivity of Si NWs to other gases and for different dimensions is currently analyzed.

**Fig. 12.** Transfer characteristics of a Si NW presenting a cross-section of 100 nm x 50 nm before and after exposure to acetic acid vapour.

**Fig. 13.** Relative current change as a function of time at fixed back gate and drain drain bias conditions.

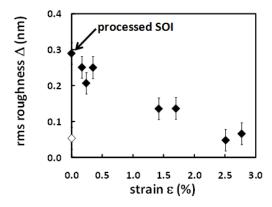

## Correlation between surface roughness and induced strain

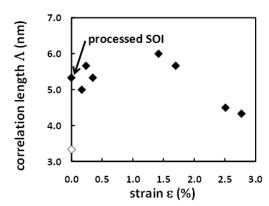

The rms surface roughness and correlation length are key parameters to model carrier mobility in MOSFET inversion layers. Simulations indicate that only a reduction in rms roughness compared with bulk Si values can explain the high values of electron mobility observed experimentally in tensile strained silicon devices. However due to the limited characterization techniques available to measure roughness accurately on a nano and sub-nanoscale, to date such assertions have remained largely unconfirmed. Using the proprietary lab-on-chip concept of UCL, the paucity of roughness measurements by reporting on roughness parameters in uniaxial strained Si beams relevant for state of the art MOSFETs, nanowire and MEMS devices, with varying degrees of strain have been addressed. Nanoscale roughness is characterized high resolution AFM. The test structures comprise a silicon nitride actuator to induce a wide range of deformation levels in the Si beams, from 0.2% to 2.8%, equivalent to a stress range from 0.3 to 4.9 GPa. The rms roughness was found to reduce gradually from 0.29 nm for unstrained Si to 0.07 nm for 2.8% of strain. Similarly, the correlation length of nanoscale surface undulations in the direction of the applied stress reduced from 5.3 to 4.3 nm for the same range of strain values (Fig. 14). These results provide unequivocal confirmation that a reduction in rms roughness accompanies increasing tensile strain.

**Fig. 14.**  $\Delta$  and  $\Lambda$  as a function of strain in the Si beam for 95 x 95 nm<sup>2</sup> images. Error bars correspond to the maximum variation in rms calculation.

#### FP2.3 "Small Slope Switch"

The work corresponding to the 3<sup>rd</sup> periodic report of FSP2.3 was carried out on the topics and based on the collaborations described below.

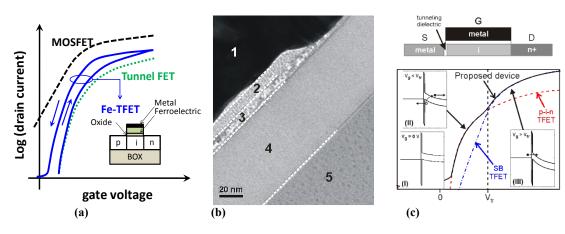

Ferroelectric Tunnel FET (Fe-TFET) with a SiO2/Al2O3/P(VDF-TrFE) gate stack

Tunnel FETs have been fabricated with a ferroelectric polymer layer inserted into their gate stack (Fig. 1(a) and 1(b), SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/PVDF gate stack). This fabrication activity explains also why EPFL has used some resources under the consumable category. This novel family of devices combines the low subthreshold current of band-to-band tunneling transistors with the retention characteristics of ferroelectric devices, enabling interesting features for future one-transistor (1T) memory cells. Hysteretic behaviour of such devices is revealed by experimental measurements and its principle confirmed by calibrated two-dimensional numerical simulations. Low temperature measurements confirm the reduced sensitivity of the Tunnel FET subthreshold swing to temperature, and distinguish them from fabricated reference Fe-MOSFETs.

## Abrupt switch based on internally combined Band-To-Band and Barrier Tunneling mechanisms

A novel Tunnel FET concept has been designed (Fig. 1(c)), which makes use of internally combined quantum mechanical band-to-band and barrier Tunneling mechanisms to achieve improved performances and overcome the intrinsic low current drive limitations of conventional Tunnel FETs and the 60 mV/dec limitation of MOSFETs at room temperature. This new structure, including an ultra-thin dielectric between metal source and silicon channel, allows a sub-60 mV/dec average subthreshold slope (SS ~43 mV/dec) and a uniquely high  $I_{ON}/I_{OFF}$  ratio (~10<sup>11</sup>). The device principle and the potential performances are investigated by numerical simulation. (This project is developed under Nanosil in collaboration with the Steeper project, particularly in collaboration with partners from IUNET and also with additional funding from the Swiss Nanotera project. The thesis of the doctoral student (Luca De Michielis) is co-advised by professor Adrian Ionescu of EPFL and Luca Selmi of University of Udine. Luca De MIchielis received in 2011 the IBM Fellowship Award, which is an extraordinary achievement.

#### Advanced modelling and simulation of Tunnel-FET devices

Final Report

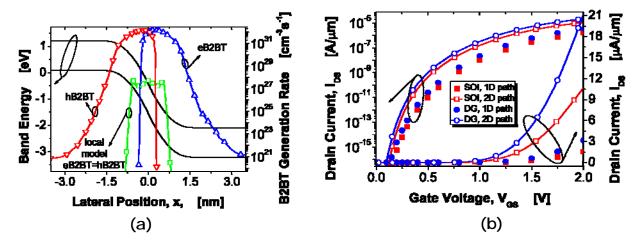

Thanks to a specific mobility action EPFL and IUNET-Udine collaborated to the assessment of device architectures and models for simulation of silicon Tunnel-FETs. As it is well known, differently from conventional MOSFETs, where the injection mechanism is governed by the emission above the source barrier, in Tunnel-FETs the carrier injection mechanism is replaced by the quantum mechanical band to band tunneling. Being inherently based on a quantum effect, a proper modeling of Tunnel-FETs in principle requires a full quantum transport approach, which is however extremely demanding from a computational point of view when applied to realist devices. In order to include the B2BT in TCAD simulations based on the drift-diffusion theory, several different models that describe the local and non-local B2BT as an additional generation-recombination mechanism have been proposed (Fig. 2a).

In the framework of the above mentioned researcher mobility, we have thus used a semiclassical modeling approach based on the solution of the BTE by Monte Carlo techniques made available by the IUNET-Udine partner to comparatively evaluate some of the limitations of current models for an accurate description of B2BT generation mechanisms and to examine conventional Tunnel FET architectures. In particular we explored the impact of different modeling assumptions (e.g. that on the shape of the tunneling path) on the relative performance of different device architectures (Fig. 2b). These analyses proved useful to assess the potentials of the different approaches for the optimization of the architecture of these new devices. Moreover they proved extremely useful to gain a deep insight in the impact of the B2BT mechanism on the device characteristics and led to new ideas on how to optimize Tunnel-FETs for enhanced performance. (This project is developed under Nanosil in collaboration with the Steeper project).

Figure 1: (a) Fe-TFET concept (qualitative comparison with Tunnel FET and Fe-MOSFET) suggesting more abrupt transitions than Tunnel FET and hysteretic behavior. (b) FIB-cut showing the cross section of the SOI and gate stack at the level of the transistor channel. (c) Band diagrams of a Schottky Tunnel FET with thin interfacial dielectric at source under different gate bias conditions.

Figure 2: (a) Numerical simulation of a highly doped p-n junction showing the relevant differences between a local band-to-band tunneling model and a non-local one. (b) Comparison of the choice of the tunneling path on a SOI and a DG device. 1D path means tunneling parallel to the transport direction, whereas 2D path means tunnelling in the direction of the maximum valence band gradient.

## FP2.4 "Templated Self-Organization"

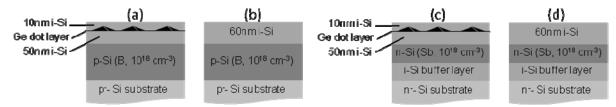

In this report, technical progress is described for activities (NW transistors, Single Electron memories and OD characterization and devices) defined in the previous annual report. These activities have been further focused for the last project period (starting from 06/2010) in accordance to the remarks of the reviewers, and, to the project tasks, Deliverable and Milestone ("D2.6 Nanowires fabricated by Templated Self-Organization", and "M2.7 Electrical operation of nanowire test devices fabricated by Templated Self-Organization). In accordance to the recommendations of the reviewers (2nd review, recommendation #6) the growth of Ge QD wafers was finished by 04/2010. The further activities have been concentrated on the implementation of these layers in devices and circuits and their characterization.

#### Bottom up Si-NW transistor (CEA, INPG, Tyndall), cooperation with FSP 2.1

We have investigated the way to improve the nanowires/metal contact resistance. In order to fabricate devices, nanowires were sonicated in IPA and then dispersed onto a p++ Si <100> substrate covered with a 200 nm thick Si<sub>3</sub>N<sub>4</sub> layer. Optical lithography was then used to define drain and source contacts. After development, contacts were metalized (Ni 80 nm / Al 120 nm) using an e-beam evaporator. A lift-off step was performed to remove resist and an O<sub>2</sub> plasma step was used to clean the wires from all resist wastes which could perturb electrical transport. Finally metallic contacts were silicided at 400 °C under Nitrogen flow using a Rapid Thermal Annealing (RTA) furnace and at varying duration. The electronic properties of the Si NW FETs as a function of gate and source-drain biases were measured using a semiconductor parameter analyzer (Keithley 4200) at room temperature and in ambient air.

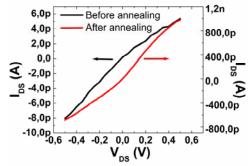

In the present case, we have studied the kinetics of Ni silicide growth for an annealing temperature of 400 °C under  $N_2$  gas by varying the process time. The temperature has been chosen to obtain the less resistive NiSi. Measurements of silicide length were performed using a Scanning Electron Microscope (SEM) allowing us to differentiate the silicide from the silicon nanowire from the contrast observed in the secondary electrons

Prior to silicidation, devices were characterized with a probe station. A comparison of the behaviour of a device before and after silicidation is given in figure 2.4.1 showing a 100 fold increase in the current passing through the nanowire. Measurement of the saturation current flowing through the channel at  $V_{gs} = 0$  V gives

22 / 107

$I_{\text{sat}} = 0.5 \text{ A.cm}^{-2}$ . This can be interpreted in the frame of a pure thermoionic emission model and gives a barrier height of Φ<sub>B</sub>≈0.45 eV, close to one of the two expected values for NiSi/Si barriers (eV), and shows that our nanowires have residual p type doping.

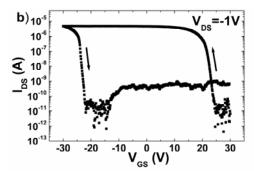

Typical I<sub>DS</sub>-V<sub>DS</sub> and I<sub>DS</sub>-V<sub>GS</sub> characteristics of silicided devices are shown in figures 2.4.1 and 2.4.2. The devices exhibit I<sub>ON</sub>/I<sub>OFF</sub> ratio up to 10<sup>5</sup> with a maximum ON current obtained for negative V<sub>GS</sub> values of the order of ~ 5 μA giving a current density around 28 kA/cm<sup>2</sup>. The characteristic in the ON state is linear with a device resistance around 300 k $\Omega$ , which corresponds to a resistivity of 133 m $\Omega$ .cm. However, this resistance is likely arising from one of the two diodes obtained at the contact between the silicide and the Si channel under backward bias, where transparency is increased by the strong band bending at the junction for decreasing V<sub>G</sub>.

We obtained a transconductance  $g_m \sim 1.2 \mu S$  giving us a hole mobility close to 200 cm<sup>2</sup>/Vs at 300K.

Figure 1.4.1 I<sub>DS</sub>-V<sub>DS</sub> characteristic of a SiNW FET with nickel contacts before and after annealing step at 400 °C for 30 s.

Figure 2.4.2  $I_{DS}$ - $V_{GS}$  characteristic of a SiNW FET with 200 nm Si<sub>3</sub>N<sub>4</sub> back gate insulator recorded at V<sub>DS</sub> =- 1 V. The on-off current ratio of this device is 2x10<sup>5</sup>. Arrows indicate either the positive to negative or negative to positive gate voltage sweep.

#### Joint flagship activity between FP 2.1 and FP 2.4 (horizontal growth & doping of NW)

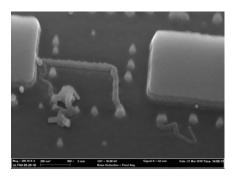

For Si-NW transistor fabrication based on simultaneously grown networks of connected NWs between predefined Si pads on SOI, NW horizontal growth onto SiO<sub>2</sub> between the pad sidewalls has been investigated. Growth recipes using gold colloids dispersed via drop casting on test wafers patterned by UCL have been developed. When placed in contact with a pad sidewall, a gold colloid gives rise to a horizontal nanowire starting from the pad, as seen in the fig. 2.4.3 below. UCL patterned test wafer was sent to Tyndall for selective area deposition of gold and CMOS compatible Pt colloids at the source and drain pads using the dielectrophoresis technique.

Figure 2.4.3 undoped Si NW grown from an Au colloid localized at the pad sidewall.

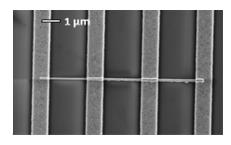

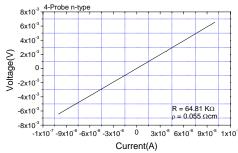

In addition to the above-mentioned work on the localization, the doping of nanowires using diborane (p type doping) and phosphine (n type doping) precursors mixed with silane has been characterized. The resistivities of single nanowires (see in figure 2.4.4) have been measured and incorporation of boron and phosphorous in nanowires has been checked.

**Figure 2.4.4** Single nanowire connected in a four probe configuration (left) and corresponding resistance measurement (right).

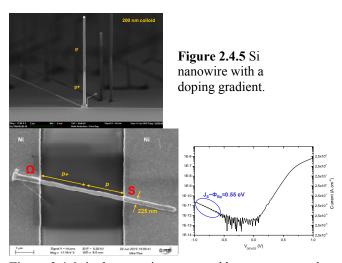

Moreover, doping modulation along a nanowire has been achieved by tuning the reactive mixture composition in the CVD tube during the growth (**fig. 2.4.5**). As an example, a nanowire Schottky diode has been fabricated with a heavily p doped end while the other was set p doped (**fig. 2.4.6**).

**Figure 2.4.6** single nanowire connected between a strongly and lightly p doped ends (left) and corresponding I(V) curve (right).

## Single electron memory (UCL, USTUTT)

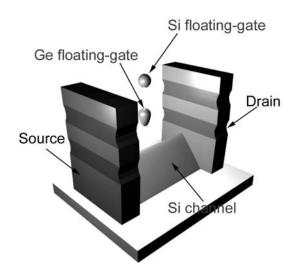

The objective of this work is to realize a self-aligned single-electron memory (SEM). In order to obtain a long data retention time, single-electron memories with double nano floating-gates (fig. 2.4.7) have been fabricated, in which the upper floating-gate is charged/discharged by a few (ideally one) electrons from the MOSFET channel through a double tunnel junction separated by the lower floating-gate. When the size of the lower floating-gate is below 10nm, the quantum confinement and Coulomb Blockade effect induce the splitting of the energy band into a number of energy level at room temperature. The band-offset between the upper and lower floating-gates prevents the charge in the upper floating-gate from returning to the channel, thereby resulting in longer data retention time. In other words, the double floating-gates are analogous to an 'artificial dipole', which is embedded in the gate oxide between the control gate and the MOSFET channel. The electric field surrounding the 'artificial dipole' is weaker than that surrounding the floating-gate in the conventional single-electron memory device. Therefore, the charge can be stored in the upper floating-gate for a long time.

**Figure 2.4.7** Schematic view of a self-aligned double floating-gate single-electron memory.

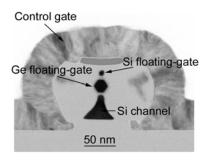

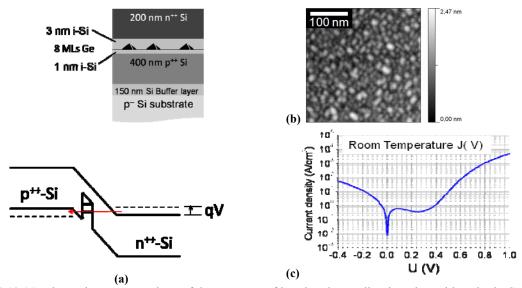

The heterostructure used in this fabrication is composed of a  $Si/Si_{0.7}Ge_{0.3}/Si$  stack (20/20/50 nm) on a 145-nm thick buried oxide. A

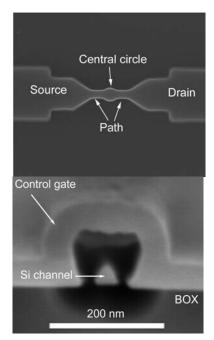

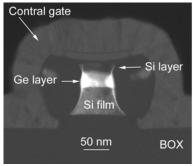

pattern as shown in **fig. 2.4.8a** is then obtained on the heterostructure by lithography and Reactive Ion Etching with a hard mask of silicon nitride. The pattern is composed of a central circle connected to wider source/drain regions by narrow paths. After wet oxidation, the double tunnel oxides separated by the Si<sub>0.7</sub>Ge<sub>0.3</sub> layer is formed in the circle as shown in **fig. 2.4.8b**. The reason is that the interfaces between Si and Ge layers have fast etching and oxidation rates. In this case, the tunnel oxides vertically separate the circle region into top Si dot, middle Ge dot and bottom triangular channel, which are used as the upper floating-gate, lower floating-gate and the channel of the present memory device, respectively. The floating-gates are restricted to the central circle since the Si and Ge dots are completely oxidized in the narrow paths (**fig. 2.4.8c**). In the wide source/drain regions, their widths are large enough to avoid the formation of the tunnel oxides in the interfaces (**fig. 2.4.8d**). Therefore, the floating-gates are self-aligned to the channel and restricted in the central region. The structure is doped by arsenic for reducing the resistance of the source/drain regions. This step results in an n-type junctionless nanowire channel. Then a control gate is formed by depositing a layer of polysilicon or Pt layer. To further simplify the fabrication process, we also design the memory device with two side gates.

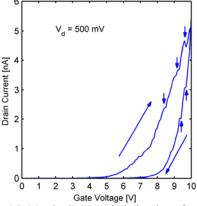

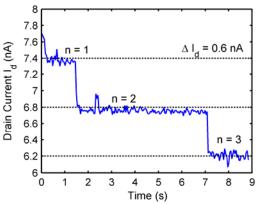

The hysteretic behavior of the device at room temperature is shown in **figure 2.4.9 a**. When the gate voltage is swept from 0 to 10 V, three shifts are observed, while two back shifts are observed when sweep is reversed. This indicates that single electron is injected into the upper floating-gate. The diameter of the upper floating-gate obtained from **figure 2.4.9 b** is 7.5 nm which is compatible with the Coulomb charging and quantization energy at room temperature so that the memory operation can be performed by one electron only. To further support single-charge injection, the time evolution of the drain current is carried out, in which a negative pulse of 10 V is first applied to empty the floating-gates, then a constant voltage of 8.2 V is set and hold on during the measurements. **Figure 2.4.9 b** demonstrates a typical  $I_d$ -t characteristic. When one electron is injected into the floating gate, an abrupt reduction of drain current is observed. The quantization of the current steps, of  $\Delta I_d = 0.3$  nA, confirms that they stem from single electron injection in the floating-gate.