# FP7 - EU

Silicon Quantum Wire Transistors

montl report Deliverable D5.2

# TABLE OF CONTENT

# 1 Project coordinator address

#### 2 Milestones

- MS1 Existing mask set adapted for gated Resistor design

- MS2 Existing mask set adapted for Variable Barrier Transistor Design

- MS3 First 300mm wafers with 10nm SOI thickness delivered to CEA-LETI

- MS4 1st run of Gated Resistors delivered to partners

#### 3 Deliverables

- D2.2 Fabrication Process Specification for Gated Resistors

- D2.3 Fabrication Process Specification for Variable Barrier Transistors

- D4.1 Guidelines on admissible electrical parameter variation for Gated Resistors

- D4.2 TEM cross sections on prototype Gated Resistors

## **4** ■ Quaterly reports

WP1 - June 2011 - Magwel

WP2 - June 2011 - CEA-LETI

WP3 - June 2011 - INPG

WP4 - June 2011 - Intel

# 5 Meetings

- 03/09/2010 meeting # 1 Kick-off meeting

- 14/03/2011 meeting # 2

- 08/06/2011 meeting # 3 Conference Call

#### **Project Coordinator Address**

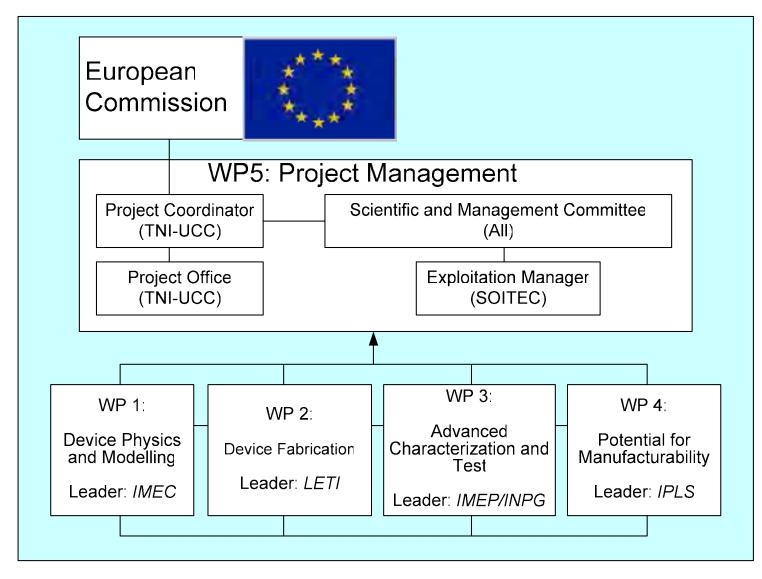

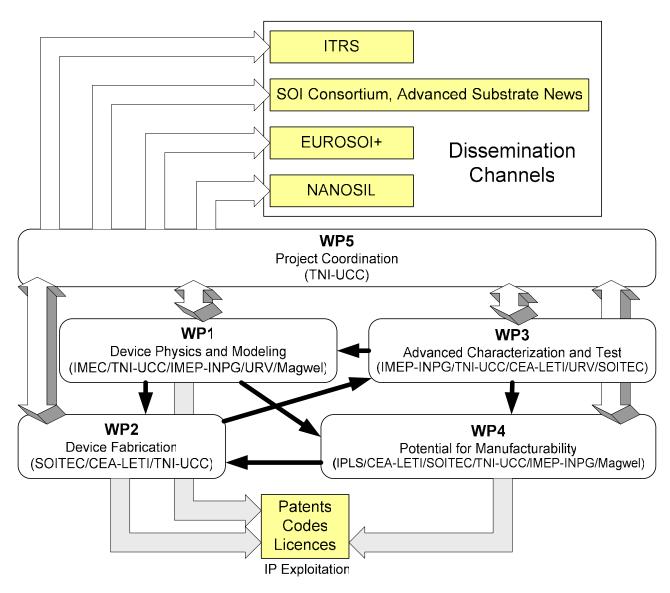

SQWIRE has now been running for a year. The junctionless transistor concept has gained acceptance worldwide and several articles on the device are published every month by different research groups worldwide. The highlights of this first year of research are:

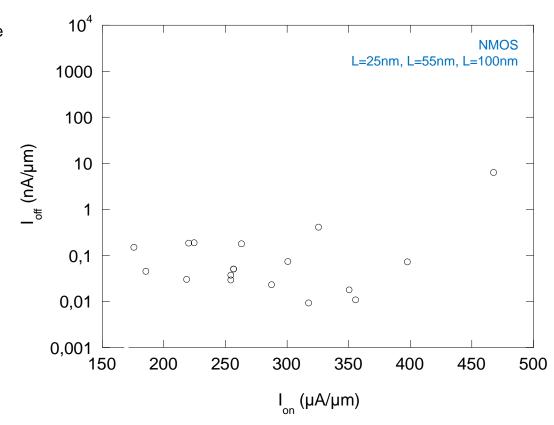

- The SQWIRE consortium maintains its leadership with the experimental demonstration of junctionless transistors with a gate length of 15nm and a DIBL of 27 mV/V. The saturation subthreshold slope is 70 mV/decade for L=15 nm and 62 mV/decade for L=90 nm.  $I_{on}$  and  $I_{off}$  of 280  $\mu A/\mu m$  @  $V_{GS}{=}V_{DS}{=}0.9V$  and 0.36nA/ $\mu m$  @  $V_{GS}{=}0.9V$  and  $V_{DS}{=}0.9V$  have been obtained.

- Devices have been delivered to different partners for characterization and evaluation.

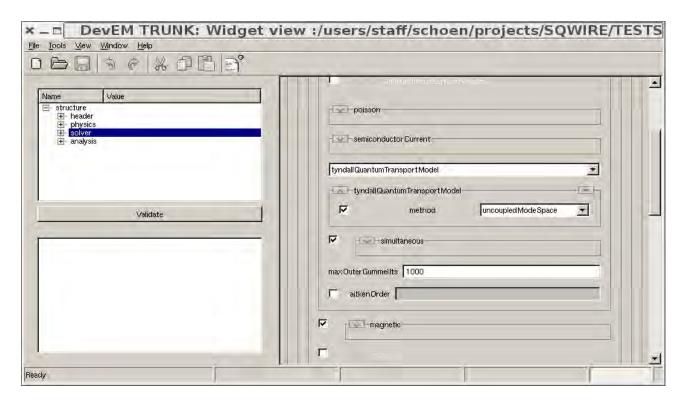

- A simulator capable of simulating tunneling and other quantum effects is being implemented in a commercial GUI.

- A first joint publication "Low-frequency noise in junctionless multigate transistors" was issued in Appl. Phys. Lett. Vol. 98, p. 133502

We are now looking forward to characterizing the devices in detail and providing feedback to the partners developing device models.

J.P. Colinge, SQWIRE Project Coordinator, 2<sup>nd</sup> September 2011

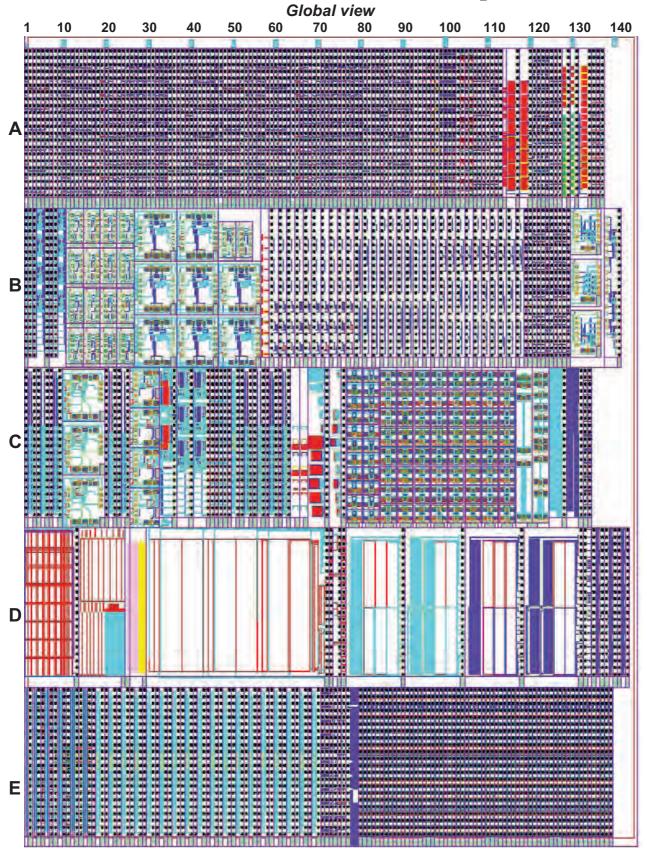

# **Overall Die Description**

# Milestone M2.3: Existing mask set adapted for Variable Barrier Transistors design

#### Sylvain Barraud

CEA-Leti, Minatec campus, 17 rue des martyrs F-38690 Grenoble, Cedex09, France

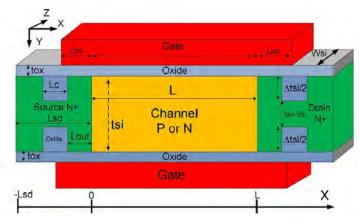

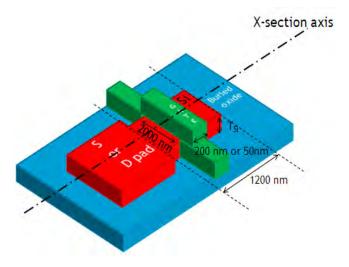

Nanowire (NW) and Tri-gated Complementary Metal Oxide Semiconductor (CMOS) technology appear as an attractive option to overcome standard CMOS bulk technology limits in terms of scaling, performances and power consumption. The electrostatic control over the channel is indeed improved in NWs, leading to a significant reduction of short channel effects and thus leakage currents in the OFF state. Based on existing expertise in fabrication of FD-SOI nanowire devices, we will develop a fabrication route for n-channel and p-channel *Variable Barrier* nanowire transistor. We propose the fabrication of tri-gate nanowire transistors that include soft tunnel barriers which should strongly reduce source-to-drain tunneling and could even, in theory, achieve sub-60 mV/dec subthreshold slopes.

Existing mask set is used, with the exception of the active area level which will have to be redrawn. The FD-SOI route is adapted in order to target NW with width varying from  $10\text{nm} \leq W \leq 20\text{nm}$ , silicon thickness  $T_{SOI}$ =10nm and with a gate length  $L_G < 30\text{nm}$ . Below the results of the first run are presented.

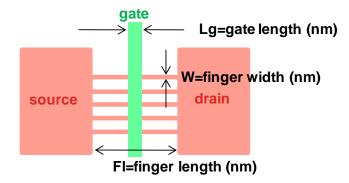

#### I. SCRIBES DESCRIPTION

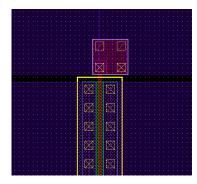

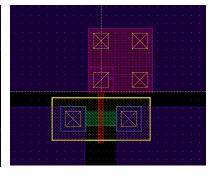

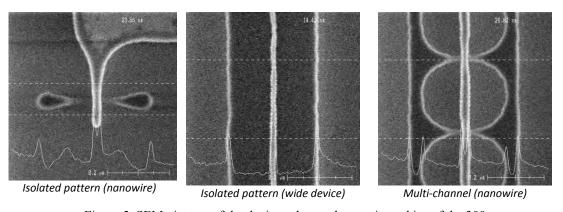

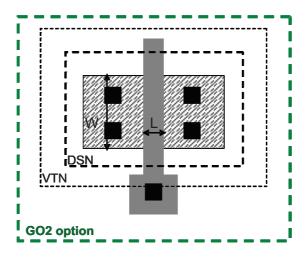

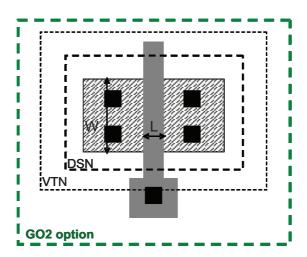

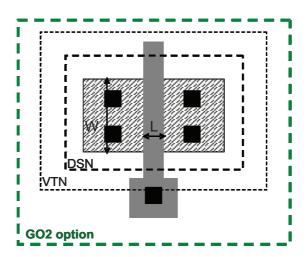

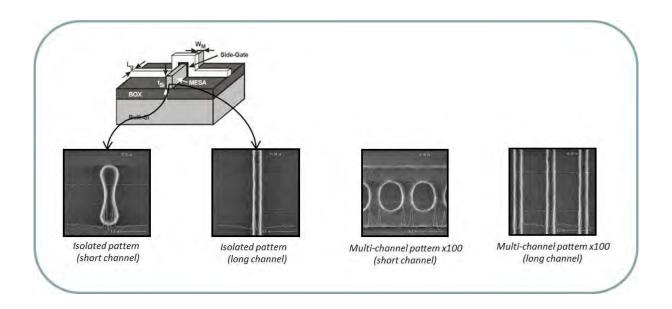

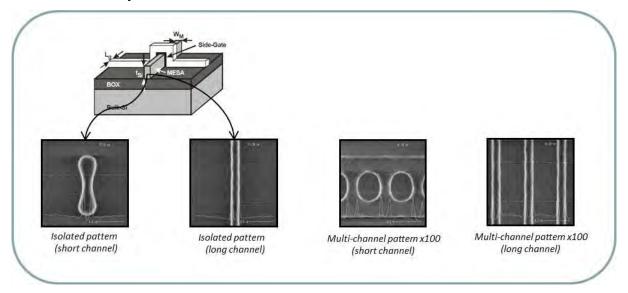

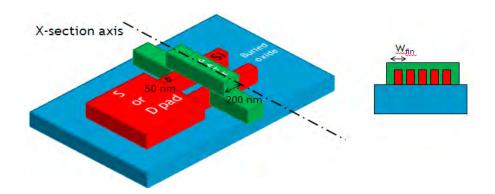

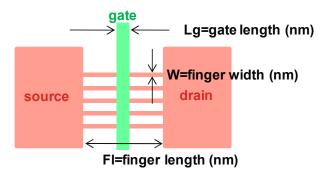

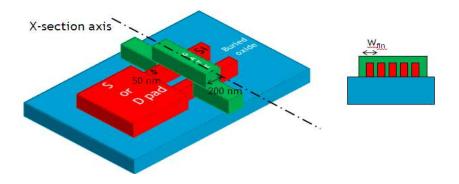

The fabrication of variable barrier transistors is based on different scribes with various gate lengths and various widths. The gate length and the nanowire width can be varied from 10µm down to 20nm (for the gate), and from 10µm down to 15nm (for the width). Examples of device drawn in the existing mask set are represented in Fig. 1a,b,c.

Fig. 1a: Future VBT MOSFET transistor with wide width (10μm)

Fig. 1b: Array of future VBT MOSFET transistors with small width (~15nm after trimming and etching)

Fig. 1c: Future VBT MOSFET transistor with small width (~15nm after trimming and etching)

#### II. PROCESS DESCRIPTION

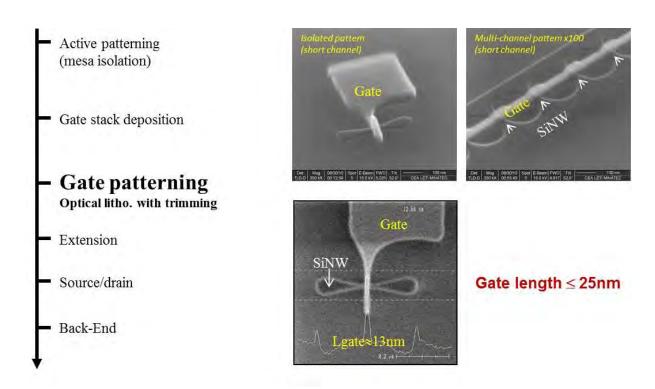

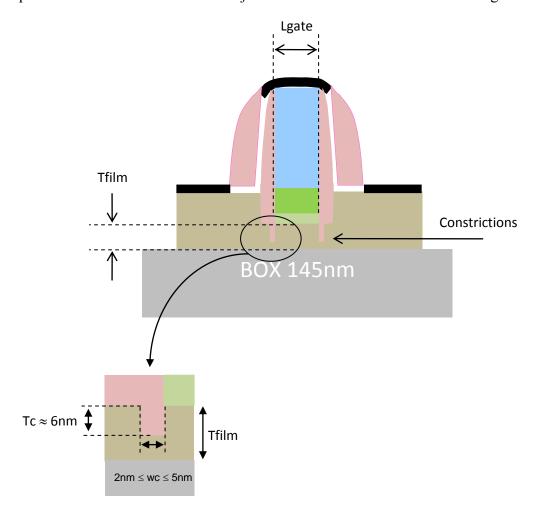

Silicon-on-Insulator (SOI) structures with silicon layers of 12 nm in thickness are used. The key for the fabrication of variable barrier tunneling MOSFET transistors is the formation and the control of both constrictions at the edges of the gate. The silicon layer is patterned to create the silicon nanowires and wide devices by using a mesa isolation technique. To do that, the active stack used is consisted of a 12nm undoped Si, 2.5nm SiO<sub>2</sub> dielectric layer and an organic bottom anti-reflective coating (BARC) layer of around 24nm patterned using 193nm ArF resist. The thickness of the photoresist is around 160nm. The active zone (i.e. nanowire feature) is carried out using the trimmed resist/BARC as a mask. Obviously, the final linewidth of nanowires is determined mainly by the amount of trimmed resist. The investigated structures after the photolithography are shown in Fig. 2. They comprised isolated lines (NW) and arrays of lines with long and short dimensions. The arrays of lines with long dimensions are used to extract the capacitance and the carrier mobility. The smallest devices (Lg) are used to investigate electrical performances as for example DIBL, subthreshold slope, I<sub>DS</sub>(V<sub>GS</sub>), and I<sub>DS</sub>(V<sub>DS</sub>) characteristics, etc. All the critical

dimension (CD) measurements (after photolithography and after active patterning) are done using in-line field-emission-scanning electron microscope (SEM).

Isolated pattern (long channel)

Multi-channel (short dimension)

Multi-channel (long dimension)

Figure 2: SEM pictures of the devices observed on various chips of the 300mm wafers after the photo-lithography. Long and short isolated devices with long and short arrays of devices (x100 fingers)

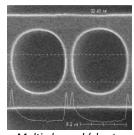

The linewidth before etching is around 80nm. After etching, the reduction of the silicon nanowire width induces by the trimming is targeted to 65 nm in order to have nanowire width of around 15nm. Due to the dispersions induce by the photolithography, the NW width after etching is expected to vary between 10nm and 20nm. In Fig. 3, the same pattern that in Fig. 2 are presented after the etching (active patterning).

Isolated pattern (short channel)

Isolated pattern (long channel)

Multi-channel (short dimension)

Multi-channel (long dimension)

Figure 3: SEM pictures of the devices observed on various chips of the 300mm wafers after the active patterning. Long and short isolated devices with long and short arrays of devices (x100 fingers)

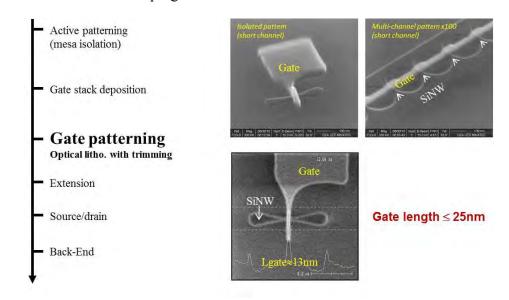

The gate stack used is composed of high-κ/metal gate. 2.3nm chemical vapour deposition (CVD) HfSiON with 5nm ALD TiN and Poly-Silicon (50nm) layers are deposited. This corresponds to an equivalent oxide thickness (EOT) of around 1.2nm. As for the active patterning, 193nm lithography tool is used with a resist trimming in order to address gate lengths down to 20nm. Two ways are investigated to create the both constrictions.

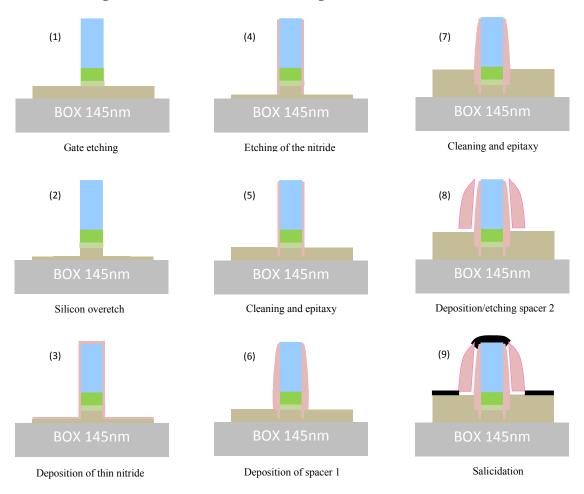

<u>First approach</u>: The both constrictions are fabricated after the gate etching. A overetch of the silicon film is done in order to reduce the thickness. Then, we propose to

do a deposition of thin spacer (SiN nitride) to create the barrier between the source-drain and the channel. After the thin spacer etching, an epitaxial undoped silicon growth is realized to recover the barrier and to form the both constrictions. Afterwards, a nitride spacer thickness of around 15nm will be formed on the silicon source-drain. Then, low parasitic resistance will be realized by epitaxial doped silicon growth on the source-drain ( $\Delta T_{SI}$ =18nm).

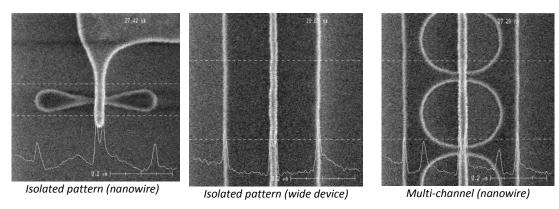

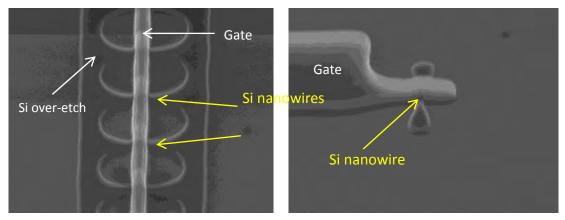

In Fig. 4, we present the first results obtained after the over-etch of the silicon film.

Figure 4: SEM pictures of the devices observed on various chips of the 300mm wafers after the over-etch of the Si film. Long and short isolated devices with short arrays of devices (x100 fingers)

In the Fig. 4, the nanowire width was around 30nm before the over-etch. For the smallest dimension (sub-20nm for the width), the results are shown in Fig. 5.

Figure 5: SEM pictures of the devices observed on various chips of the 300mm wafers after the over-etch of the Si film. Long and short isolated devices with short arrays of devices (x100 fingers)

We can clearly observed that for wide device, the over-etch of the silicon film is correctly done. However, in the case of nanowire, the over-etch (which can be characterized by an oxidation) remove the Si wire on both side of the gate. The control of this over-etch is currently in progress. The next steps will be the following: A thin spacer deposition, etching of the spacer, source/drain epitaxy to create the

constrictions. The formation of both constrictions will be characterized by using TEM image after the source/drain epitaxy.

**Second approach**: In the second approach, the over-etch is done just after the first spacer deposition. A over-etch of the silicon film is done in order to reduce the thickness. As previously, we propose to do a deposition of thin spacer (SiN) to create the barrier between the source-drain and the channel. After the thin spacer etching, an epitaxial undoped silicon growth will be realized to recover the barrier and to form the both constrictions. Afterwards, a nitride spacer thickness of around 15nm will be formed on the silicon source-drain. Then, low parasitic resistance will be realized by epitaxial doped silicon growth on the source-drain ( $\Delta T_{SI}$ =18nm). Then, a second spacer will be deposited and etched before the source-drain doping. In Fig. 6, we show the result obtained after the over-etch of the Si film.

Over-etch of the Si film of around 6nm

Figure 6: SEM pictures of the devices observed on various chips of the 300mm wafers after the over-etch of the Si film.

In Figure 7, a TEM image shows the result after the source-drain epitaxy. Here, the thin spacer of around 9nm has been deposited to create the both constrictions. After the etching and the various cleaning performed before the epitaxial growth (to recover the barrier), the constrictions have been fully removed. Then, new thicknesses must be tested in order to keep around 2-3nm of SiN after etching and cleaning. New tests are in progress.

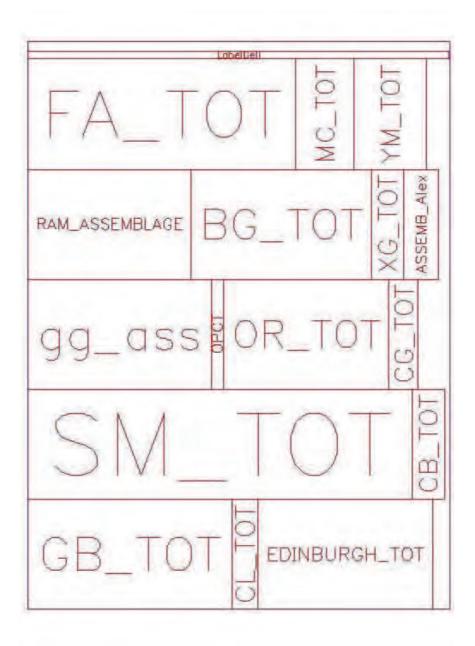

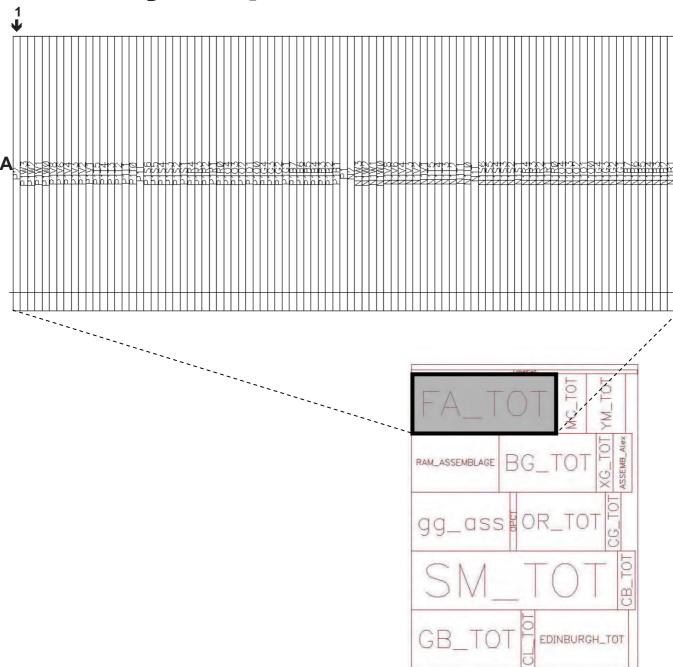

#### **Block view**

FA\_TOT: Fully Depleted SOI transistors

MC\_TOT: Capacitance modules YM\_TOT: Front End Modules

RAM\_ASSEMBLAGE: small SRAM cells BG\_TOT: NAND, NOR and TEM modules

XG\_TOT: Body contacted devices ASSEMB Alex: 16 bit adder

Gg ass: ESD and Mismatch modules

OPCT: OPC model

OR\_TOT: Varactor and RF modules

CG\_TOT:

SM\_TOT: Back End Modules CB\_TOT: ESD and analog Modules GB\_TOT: ESD and Mismatch modules

CL\_TOT: MOS capacitors

EDINBURGH TOT: Double patterning

# **Fully Depleted Devices**

| ully Depleted Devices | 56 |

|-----------------------|----|

| N1, P1                | 58 |

| N2, P2                | 59 |

| N100, P100            | 60 |

| N101, P101            | 61 |

| N102, P102            | 62 |

| N103, P103            | 63 |

| N104, P104            | 64 |

| N1T, P1T              | 65 |

| N1T0, P1T0            | 66 |

| N1R0, P1R0            |    |

| Scribe name | Coordinates | Responsible |

|-------------|-------------|-------------|

| N1, P1      |             | F. ANDRIEU  |

#### Brief description of the scribe

Standard isolated N and pMOS with various gate lengths at W=10µm.

#### **Device list**

| # | Device type *         | Parameters                                 |

|---|-----------------------|--------------------------------------------|

| 1 | Standard Nmos or Pmos | W=10µm, L=30nm, Orientation=0°, 1 channel  |

| 2 | Standard Nmos or Pmos | W=10µm, L=40nm, Orientation=0°, 1 channel  |

| 3 | Standard Nmos or Pmos | W=10µm, L=50nm, Orientation=0°, 1 channel  |

| 4 | Standard Nmos or Pmos | W=10µm, L=60nm, Orientation=0°, 1 channel  |

| 5 | Standard Nmos or Pmos | W=10µm, L=70nm, Orientation=0°, 1 channel  |

| 6 | Standard Nmos or Pmos | W=10µm, L=80nm, Orientation=0°, 1 channel  |

| 7 | Standard Nmos or Pmos | W=10µm, L=100nm, Orientation=0°, 1 channel |

<sup>\*:</sup> as defined in the DRM for transistors and gated diodes

#### Scribe pads structure

| ▼ Standard (22 pads) | □ No pads        | Other choice (    | user defined) |

|----------------------|------------------|-------------------|---------------|

| Testing levels       |                  |                   |               |

| ☐ Active             | Poly1/Poly2      | ✓ Metal 1         | ✓ Metal 2     |

| Number of modu       | le spaces reserv | ed for the scribe |               |

| Above pads line 0    | Belo             | ow pads line 0    |               |

#### Pads assignment

| Pad | Connection         | Pad | Connection         |

|-----|--------------------|-----|--------------------|

| 1   | Source of device 1 | 12  | Gate of device 4   |

| 2   | Drain of device 1  | 13  | Source of device 5 |

| 3   | Gate of device 1   | 14  | Drain of device 5  |

| 4   | Source of device 2 | 15  | Gate of device 5   |

| 5   | Drain of device 2  | 16  | Source of device 6 |

| 6   | Gate of device 2   | 17  | Drain of device 6  |

| 7   | Source of device 3 | 18  | Gate of device 6   |

| 8   | Drain of device 3  | 19  | Source of device 7 |

| 9   | Gate of device 3   | 20  | Drain of device 7  |

| 10  | Source of device 4 | 21  | Gate of device 7   |

| 11  | Drain of device 4  | 22  |                    |

**Device description**

| Scribe name | Coordinates | Responsible |

|-------------|-------------|-------------|

| N1T, P1T    |             | F. ANDRIEU  |

#### Brief description of the scribe

Standard isolated N and pMOS with various gate lengths at W=80nm.

#### **Device list**

| # | Device type *         | Parameters                                 |

|---|-----------------------|--------------------------------------------|

| 1 | Standard Nmos or Pmos | W=80nm, L=30nm, Orientation=0°, 1 channel  |

| 2 | Standard Nmos or Pmos | W=80nm, L=40nm, Orientation=0°, 1 channel  |

| 3 | Standard Nmos or Pmos | W=80nm, L=50nm, Orientation=0°, 1 channel  |

| 4 | Standard Nmos or Pmos | W=80nm, L=60nm, Orientation=0°, 1 channel  |

| 5 | Standard Nmos or Pmos | W=80nm, L=70nm, Orientation=0°, 1 channel  |

| 6 | Standard Nmos or Pmos | W=80nm, L=80nm, Orientation=0°, 1 channel  |

| 7 | Standard Nmos or Pmos | W=80nm, L=100nm, Orientation=0°, 1 channel |

<sup>\*:</sup> as defined in the DRM for transistors and gated diodes

#### Scribe pads structure

| ▼ Standard (22 pads) | □ No pads          | Other choice ( | user defined) |

|----------------------|--------------------|----------------|---------------|

| Testing levels       |                    |                |               |

| ☐ Active             | Poly1/Poly2        | ✓ Metal 1      | ✓ Metal 2     |

| Number of modu       | le spaces reserved | for the scribe |               |

| Above pads line 0    | Below              | pads line 0    |               |

#### Pads assignment

| Pad | Connection         | Pad | Connection         |

|-----|--------------------|-----|--------------------|

| 1   | Source of device 1 | 12  | Gate of device 4   |

| 2   | Drain of device 1  | 13  | Source of device 5 |

| 3   | Gate of device 1   | 14  | Drain of device 5  |

| 4   | Source of device 2 | 15  | Gate of device 5   |

| 5   | Drain of device 2  | 16  | Source of device 6 |

| 6   | Gate of device 2   | 17  | Drain of device 6  |

| 7   | Source of device 3 | 18  | Gate of device 6   |

| 8   | Drain of device 3  | 19  | Source of device 7 |

| 9   | Gate of device 3   | 20  | Drain of device 7  |

| 10  | Source of device 4 | 21  | Gate of device 7   |

| 11  | Drain of device 4  | 22  |                    |

#### **Device description**

| Scribe name | Coordinates | Responsible |

|-------------|-------------|-------------|

| N1W0, P1W0  |             | F. ANDRIEU  |

#### Brief description of the scribe

Standard isolated multi-fin N and pMOS with various gate widths at L=30nm.

#### **Device list**

| # | Device type *         | Parameters                                   |

|---|-----------------------|----------------------------------------------|

| 1 | Standard Nmos or Pmos | W=0.08µm, L=30nm, Orientation=0°, 50 channel |

| 2 | Standard Nmos or Pmos | W=0.1µm, L=30nm, Orientation=0°, 50 channel  |

| 3 | Standard Nmos or Pmos | W=0.25µm, L=30nm, Orientation=0°, 50 channel |

| 4 | Standard Nmos or Pmos | W=0.35µm, L=30nm, Orientation=0°, 50 channel |

| 5 | Standard Nmos or Pmos | W=0.5µm, L=30nm, Orientation=0°, 50 channel  |

| 6 | Standard Nmos or Pmos | W=1µm, L=30nm, Orientation=0°, 50 channel    |

| 7 |                       |                                              |

<sup>\*:</sup> as defined in the DRM for transistors and gated diodes

| ^   |     |     |      | 4    | 4    |     |

|-----|-----|-----|------|------|------|-----|

| Scr | IDE | pac | 18 9 | STru | ICTL | ıre |

| ▼ Standard (22 pads)                            | No pads           | ☐ Other choice (user defined) |           |  |  |

|-------------------------------------------------|-------------------|-------------------------------|-----------|--|--|

| Testing levels                                  |                   |                               |           |  |  |

| ☐ Active                                        | Poly1/Poly2       | ✓ Metal 1                     | ✓ Metal 2 |  |  |

| Number of module spaces reserved for the scribe |                   |                               |           |  |  |

| Above pads line 0                               | Below pads line 0 |                               |           |  |  |

#### Pads assignment

| Pad | Connection         | Pad | Connection         |

|-----|--------------------|-----|--------------------|

| 1   | Source of device 1 | 12  | Gate of device 4   |

| 2   | Drain of device 1  | 13  | Source of device 5 |

| 3   | Gate of device 1   | 14  | Drain of device 5  |

| 4   | Source of device 2 | 15  | Gate of device 5   |

| 5   | Drain of device 2  | 16  | Source of device 6 |

| 6   | Gate of device 2   | 17  | Drain of device 6  |

| 7   | Source of device 3 | 18  | Gate of device 6   |

| 8   | Drain of device 3  | 19  |                    |

| 9   | Gate of device 3   | 20  |                    |

| 10  | Source of device 4 | 21  |                    |

| 11  | Drain of device 4  | 22  |                    |

#### **Device description**

| Scribe name | Coordinates | Responsible |

|-------------|-------------|-------------|

| N1W1, P1W1  |             | F. ANDRIEU  |

#### **Brief description of the scribe**

Standard isolated multi-fin N and pMOS with various gate widths at L=50nm.

#### **Device list**

| # | Device type *         | Parameters                                   |

|---|-----------------------|----------------------------------------------|

| 1 | Standard Nmos or Pmos | W=0.08µm, L=50nm, Orientation=0°, 50 channel |

| 2 | Standard Nmos or Pmos | W=0.1µm, L=50nm, Orientation=0°, 50 channel  |

| 3 | Standard Nmos or Pmos | W=0.25µm, L=50nm, Orientation=0°, 50 channel |

| 4 | Standard Nmos or Pmos | W=0.35µm, L=50nm, Orientation=0°, 50 channel |

| 5 | Standard Nmos or Pmos | W=0.5µm, L=50nm, Orientation=0°, 50 channel  |

| 6 | Standard Nmos or Pmos | W=1µm, L=50nm, Orientation=0°, 50 channel    |

| 7 |                       |                                              |

<sup>\*:</sup> as defined in the DRM for transistors and gated diodes

|           |       | 4 4    |     |

|-----------|-------|--------|-----|

| Scribe pa | ads s | tructi | Ire |

| ▼ Standard (22 pads)                            | □ No pads   | Other choice | (user defined) |  |  |

|-------------------------------------------------|-------------|--------------|----------------|--|--|

| Testing levels                                  |             |              |                |  |  |

| ☐ Active                                        | Poly1/Poly2 | ✓ Metal 1    | ✓ Metal 2      |  |  |

| Number of module spaces reserved for the scribe |             |              |                |  |  |

| Above pads line 0                               | Below pa    | ads line 0   |                |  |  |

#### Pads assignment

| Pad | Connection         | Pad | Connection         |

|-----|--------------------|-----|--------------------|

| 1   | Source of device 1 | 12  | Gate of device 4   |

| 2   | Drain of device 1  | 13  | Source of device 5 |

| 3   | Gate of device 1   | 14  | Drain of device 5  |

| 4   | Source of device 2 | 15  | Gate of device 5   |

| 5   | Drain of device 2  | 16  | Source of device 6 |

| 6   | Gate of device 2   | 17  | Drain of device 6  |

| 7   | Source of device 3 | 18  | Gate of device 6   |

| 8   | Drain of device 3  |     |                    |

| 9   | Gate of device 3   |     |                    |

| 10  | Source of device 4 |     |                    |

| 11  | Drain of device 4  |     |                    |

# **Device description**

| Scribe name | Coordinates | Responsible |

|-------------|-------------|-------------|

| N1W2, P1W2  |             | F. ANDRIEU  |

#### Brief description of the scribe

Standard isolated multi-fin N and pMOS with various gate widths at L=100nm.

#### **Device list**

| # | Device type *         | Parameters                                    |

|---|-----------------------|-----------------------------------------------|

| 1 | Standard Nmos or Pmos | W=0.08µm, L=100nm, Orientation=0°, 50 channel |

| 2 | Standard Nmos or Pmos | W=0.1µm, L=100nm, Orientation=0°, 50 channel  |

| 3 | Standard Nmos or Pmos | W=0.25µm, L=100nm, Orientation=0°, 50 channel |

| 4 | Standard Nmos or Pmos | W=0.35µm, L=100nm, Orientation=0°, 50 channel |

| 5 | Standard Nmos or Pmos | W=0.5µm, L=100nm, Orientation=0°, 50 channel  |

| 6 | Standard Nmos or Pmos | W=1µm, L=100nm, Orientation=0°, 50 channel    |

| 7 |                       |                                               |

<sup>\*:</sup> as defined in the DRM for transistors and gated diodes

| C | ~ wi | ha |     | ۵ م  | 4   | -4. |     |

|---|------|----|-----|------|-----|-----|-----|

| 2 | cri  | pe | pad | IS S | tru | CIL | ıre |

| ▼ Standard (22 pads)                            | □ No pads   | Other choice ( | user defined) |  |  |

|-------------------------------------------------|-------------|----------------|---------------|--|--|

| Testing levels                                  |             |                |               |  |  |

| □ Active                                        | Poly1/Poly2 | ✓ Metal 1      | ✓ Metal 2     |  |  |

| Number of module spaces reserved for the scribe |             |                |               |  |  |

| Above pads line 0                               | Belo        | w pads line 0  |               |  |  |

#### Pads assignment

| Pad | Connection         | Pad | Connection         |

|-----|--------------------|-----|--------------------|

| 1   | Source of device 1 | 12  | Gate of device 4   |

| 2   | Drain of device 1  | 13  | Source of device 5 |

| 3   | Gate of device 1   | 14  | Drain of device 5  |

| 4   | Source of device 2 | 15  | Gate of device 5   |

| 5   | Drain of device 2  | 16  | Source of device 6 |

| 6   | Gate of device 2   | 17  | Drain of device 6  |

| 7   | Source of device 3 | 18  | Gate of device 6   |

| 8   | Drain of device 3  | 22  | Common Source      |

| 9   | Gate of device 3   |     |                    |

| 10  | Source of device 4 |     |                    |

| 11  | Drain of device 4  |     |                    |

#### **Device description**

| Scribe name | Coordinates | Responsible |

|-------------|-------------|-------------|

| N1W3, P1W3  |             | F. ANDRIEU  |

#### **Brief description of the scribe**

Standard isolated multi-fin N and pMOS with various gate widths at L=10 $\mu$ m.

#### **Device list**

| # | Device type *         | Parameters                                   |

|---|-----------------------|----------------------------------------------|

| 1 | Standard Nmos or Pmos | W=0.08µm, L=10µm, Orientation=0°, 50 channel |

| 2 | Standard Nmos or Pmos | W=0.1µm, L=10µm, Orientation=0°, 50 channel  |

| 3 | Standard Nmos or Pmos | W=0.25µm, L=10µm, Orientation=0°, 50 channel |

| 4 | Standard Nmos or Pmos | W=0.35µm, L=10µm, Orientation=0°, 50 channel |

| 5 | Standard Nmos or Pmos | W=0.5µm, L=10µm, Orientation=0°, 50 channel  |

| 6 | Standard Nmos or Pmos | W=1µm, L=10µm, Orientation=0°, 50 channel    |

| 7 |                       |                                              |

<sup>\*:</sup> as defined in the DRM for transistors and gated diodes

| C | ~ wi | ha |     | ۵ م  | 4   | -4. |     |

|---|------|----|-----|------|-----|-----|-----|

| 2 | cri  | pe | pad | IS S | tru | CIL | ıre |

| ▼ Standard (22 pads) |                  | Other choice (    | user defined) |

|----------------------|------------------|-------------------|---------------|

| Testing levels       |                  |                   |               |

| □ Active             | Poly1/Poly2      | ✓ Metal 1         |               |

| Number of modu       | le spaces reserv | ed for the scribe |               |

| Above pads line 0    | Belo             | ow pads line 0    |               |

#### Pads assignment

| Pad | Connection         | Pad | Connection         |

|-----|--------------------|-----|--------------------|

| 1   | Source of device 1 | 12  | Gate of device 4   |

| 2   | Drain of device 1  | 13  | Source of device 5 |

| 3   | Gate of device 1   | 14  | Drain of device 5  |

| 4   | Source of device 2 | 15  | Gate of device 5   |

| 5   | Drain of device 2  | 16  | Source of device 6 |

| 6   | Gate of device 2   | 17  | Drain of device 6  |

| 7   | Source of device 3 | 18  | Gate of device 6   |

| 8   | Drain of device 3  | 22  |                    |

| 9   | Gate of device 3   |     |                    |

| 10  | Source of device 4 |     |                    |

| 11  | Drain of device 4  |     |                    |

#### **Device description**

| Scribe name | Coordinates | Responsible |

|-------------|-------------|-------------|

| N1G3, P1G3  |             | F. ANDRIEU  |

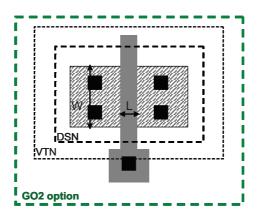

#### **Brief description of the scribe**

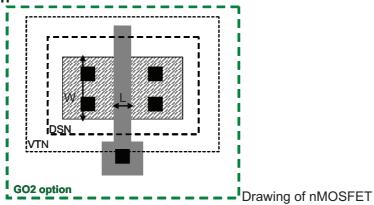

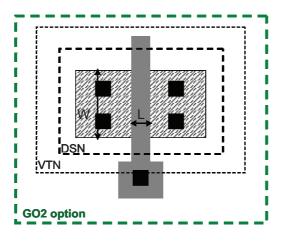

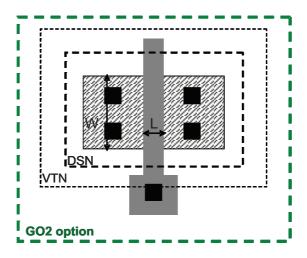

GO2 Isolated standard nMOS or pMOS with various gate lengths at W=10µm.

#### **Device list**

| # | Device type *             | Parameters                                  |

|---|---------------------------|---------------------------------------------|

| 1 | Standard GO2 Nmos or Pmos | W=10µm, L=0.15µm, Orientation=0°, 1 channel |

| 2 | Standard GO2 Nmos or Pmos | W=10µm, L=0.25µm, Orientation=0°, 1 channel |

| 3 | Standard GO2 Nmos or Pmos | W=10µm, L=0.35µm, Orientation=0°, 1 channel |

| 4 | Standard GO2 Nmos or Pmos | W=10µm, L=0.5µm, Orientation=0°, 1 channel  |

| 5 | Standard GO2 Nmos or Pmos | W=10µm, L=0.75µm, Orientation=0°, 1 channel |

| 6 | Standard GO2 Nmos or Pmos | W=10µm, L=1µm, Orientation=0°, 1 channel    |

| 7 | Standard GO2 Nmos or Pmos | W=10µm, L=10µm, Orientation=0°, 1 channel   |

<sup>\*:</sup> as defined in the DRM for transistors and gated diodes

| C | cri | ha | pad | ا د  | tru  | cti | ıro |

|---|-----|----|-----|------|------|-----|-----|

| 3 | CLI | De | oso | IS S | HILL | CTL | ıre |

| ▼ Standard (22 pads) | No pads     No pads | ☐ Other choic  | e (user defined) |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|

| Testing levels       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                  |

| ☐ Active             | Poly1/Poly2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ✓ Metal 1      |                  |

| Number of module     | e spaces reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | for the scribe | •                |

| Above pads line 0    | Below pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ads line 0     |                  |

#### Pads assignment

| Pad | Connection         | Pad | Connection         |

|-----|--------------------|-----|--------------------|

| 1   | Source of device 1 | 12  | Gate of device 4   |

| 2   | Drain of device 1  | 13  | Source of device 5 |

| 3   | Gate of device 1   | 14  | Drain of device 5  |

| 4   | Source of device 2 | 15  | Gate of device 5   |

| 5   | Drain of device 2  | 16  | Source of device 6 |

| 6   | Gate of device 2   | 17  | Drain of device 6  |

| 7   | Source of device 3 | 18  | Gate of device 6   |

| 8   | Drain of device 3  | 19  | Source of device 7 |

| 9   | Gate of device 3   | 20  | Drain of device 7  |

| 10  | Source of device 4 | 21  | Gate of device 7   |

| 11  | Drain of device 4  | 22  |                    |

#### **Device description**

# Milestone 2.4: First run of gated resistors delivered to partners

Sylvain Barraud

CEA-Leti, Minatec campus, 17 rue des martyrs F-38690 Grenoble, Cedex09, France

Nanowire (NW) and Tri-gated Complementary Metal Oxide Semiconductor (CMOS) technology appear as an attractive option to overcome standard CMOS bulk technology limits in terms of scaling, performances and power consumption. The electrostatic control over the channel is indeed improved in NWs, leading to a significant reduction of short channel effects and thus leakage currents in the OFF state. Based on existing expertise in fabrication of FD-SOI nanowire devices, we develop in this work a fabrication route for n-channel and p-channel *junctionless* nanowire MOSFET transistors. Existing mask set is used, with the exception of the active area level which is redrawn. The FD-SOI route is adapted in order to target *junctionless* NW with width varying from  $10 \text{nm} \leq \text{W} \leq 20 \text{nm}$ , silicon thickness  $T_{\text{SOI}}$ =10nm and with a gate length  $L_{\text{G}}$ <30nm.

#### I. Introduction

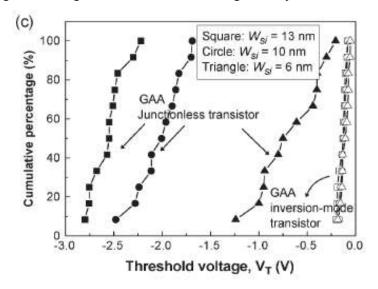

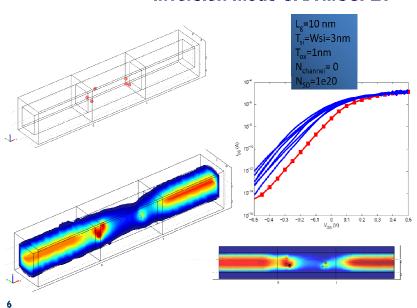

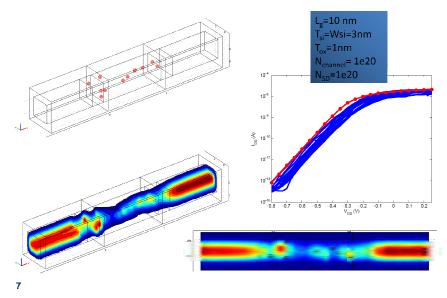

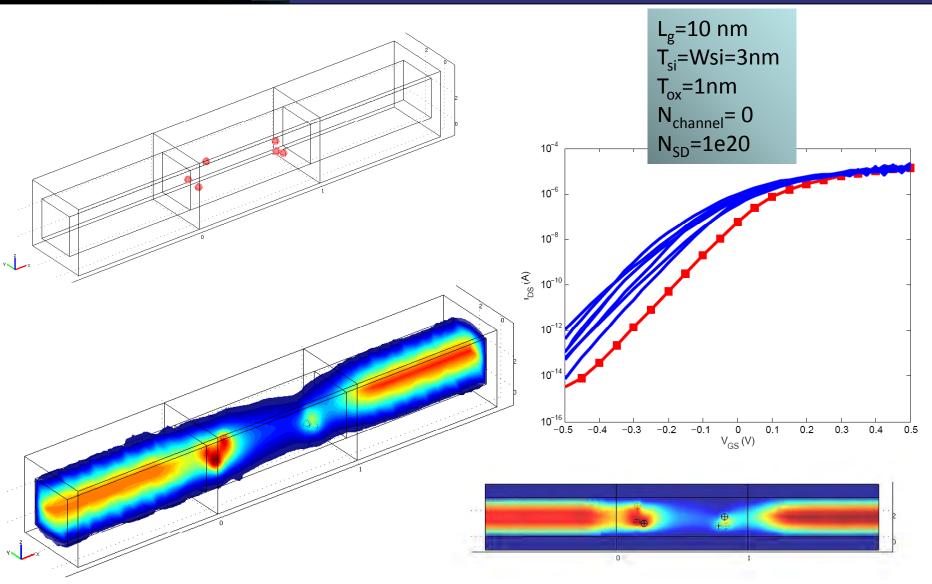

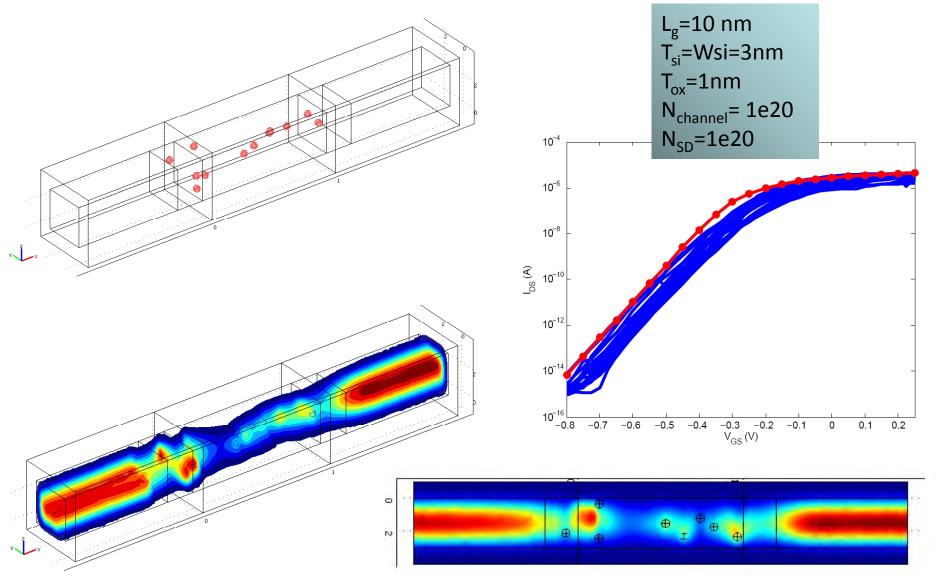

This work demonstrates *junctionless* transistors fully compatible with standard trigate fabrication process, and a single high- $\kappa$ /metal gate stack. In particular, we demonstrate  $V_T$  tuning capabilities with a mid-gap metal gate, by using ion implanted thin SOI channel. We investigate the structure scalability down to 20nm and we evaluate transport and noise properties of *junctionless* nanowire transistors.

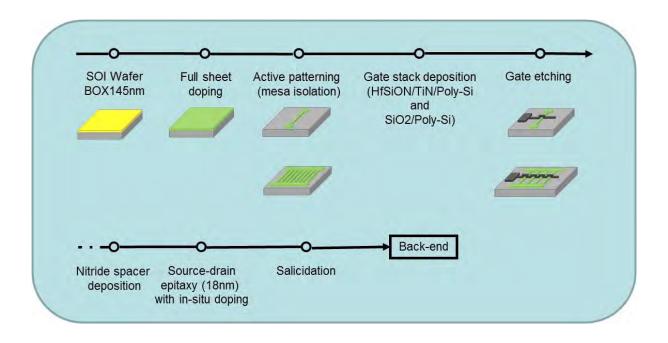

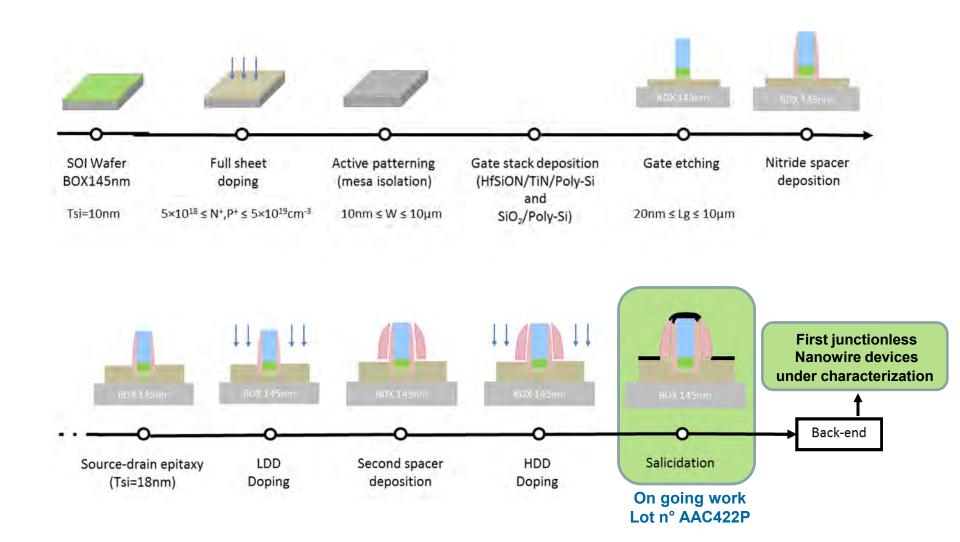

#### II. PROCESS DESCRIPTION

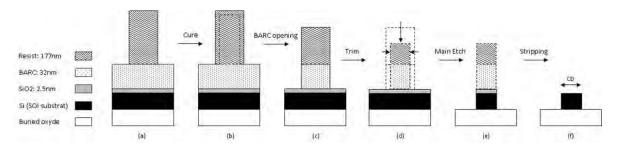

Silicon-on-Insulator (SOI) structures with silicon layers of 10 nm in thickness are used. The key for the fabrication of junctionless gated resistor is the formation of a semiconductor layer that is thin and narrow enough to allow full depletion of carriers when the device is turned off. Then, the silicon layer is thinned down to 10nm. The semiconductor also needs to be heavily doped to allow for a reasonable amount of current flow when the device is turned on. The implant energies and doses are chosen (from process simulation – Athena Silvaco) to yield uniform doping concentration ranging from 5x10<sup>18</sup> cm<sup>-3</sup> up to 5x10<sup>19</sup> cm<sup>-3</sup>. Then, the silicon layer is patterned to create the silicon nanowires by a mesa isolation technique. The active stack used in this work is consisted of a 10nm doped Si, 2.5nm SiO<sub>2</sub> dielectric layer and an organic bottom anti-reflective coating (BARC) layer of around 24nm patterned using 193nm ArF resist. The BARC opening is done using CF<sub>4</sub> chemistry. This chemistry is used in order to ensure vertical resist/BARC profile and correct linewidth roughness. Then, the BARC/resist trimming process is performed just before the main etch to selectively pattern the silicon on the buried oxide. Trimming resist is performed to achieve nanowire structures as small as 15nm in width using the HBr/O<sub>2</sub> plasma. In order to smooth the resist patterns and then reduce the linewidth roughness, a curing step will be performed just before the trimming.

#### II. RESULTS

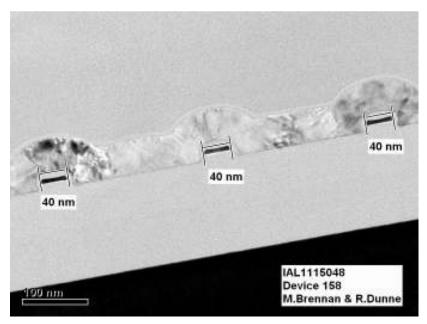

In order to know the dimensions of the *junctionless* nanowires, different scribes are measured: scribes N1T and N1W3. The N1T scribe is used to extract the Ion-Ioff plot, the DIBL, the sub-threshold slope, the threshold voltage, (etc.) for different gate lengths. The scribe N1W3 is used in order to extract capacitance and carrier mobility. The dimensions for the different patterned wafers are summarized below.

|          |                           | N1T-1          | N1T-2          | N1T-3          | N1T-4          | N1T-5          | N1T-6          | N1T-7          | N1W3-1         | N1W3-2         | N1W3-3         | N1W3-4         | N1W3-5         | N1W3-6         |

|----------|---------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|          | H (μm)                    | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           |

| P01      | W Min (µm)                | 0,015          | 0,015          | 0,015          | 0,015          | 0,015          | 0,015          | 0,015          | 0,008          | 0,028          | 0,178          | 0,27           | 0,428          | 0,928          |

| PUI      | W Mean (µm)<br>W Max (µm) | 0,019<br>0,022 | 0,01<br>0,015  | 0,03           | 0,18<br>0,185  | 0,27<br>0,27   | 0,43<br>0,435  | 0,93<br>0,935  |

|          | Lg (µm)                   | 0,02           | 0,03           | 0,04           | 0,05           | 0,06           | 0,07           | 0,09           | 10             | 10             | 10             | 10             | 10             | 10             |

|          | H (µm)                    | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           |

|          | W Min (µm)                | 0,021          | 0,021          | 0,021          | 0,021          | 0,021          | 0,021          | 0,021          | 0,017          | 0,037          | 0,187          | 0,287          | 0,437          | 0,937          |

| P02      | W Mean (µm)<br>W Max (µm) | 0,025<br>0,029 | 0,02<br>0,022  | 0,04<br>0,042  | 0,19<br>0,192  | 0,29<br>0,292  | 0,44<br>0,442  | 0,94<br>0,942  |

|          | Lg (µm)                   | 0,025          | 0,035          | 0,045          | 0,055          | 0,065          | 0,075          | 0,095          | 10             | 10             | 10             | 10             | 10             | 10             |

|          | H (µm)                    | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           |

|          | W Min (µm)                | 0,013          | 0,013          | 0,013          | 0,013          | 0,013          | 0,013          | 0,013          | 0,007          | 0,027          | 0,177          | 0,277          | 0,427          | 0,927          |

| P03      | W Mean (µm)<br>W Max (µm) | 0,017<br>0,023 | 0,008          | 0,028          | 0,178<br>0,18  | 0,278<br>0,28  | 0,428<br>0,43  | 0,928<br>0,93  |

|          | Lg (µm)                   | 0,02           | 0,03           | 0,04           | 0,05           | 0,06           | 0,07           | 0,09           | 10             | 10             | 10             | 10             | 10             | 10             |

|          | Η (μm)                    | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           | 0,01           |

|          | W Min (µm)                | 0,021          | 0,021          | 0,021          | 0,021          | 0,021          | 0,021          | 0,021          | 0,016          | 0,036          | 0,186          | 0,286          | 0,436          | 0,936          |

| P04      | W Mean (µm)<br>W Max (µm) | 0,024<br>0,026 | 0,018<br>0,021 | 0,038<br>0,041 | 0,188<br>0,191 | 0,288<br>0,291 | 0,438<br>0,441 | 0,938<br>0,941 |

|          | Lg (µm)                   | 0,027          | 0,037          | 0,047          | 0,057          | 0,067          | 0,077          | 0,097          | 10             | 10             | 10             | 10             | 10             | 10             |

|          | Η (μm)                    | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          |

|          | W Min (µm)                | 0,022          | 0,022          | 0,022          | 0,022          | 0,022          | 0,022          | 0,022          | 0,009          | 0,029          | 0,179          | 0,279          | 0,429          | 0,929          |

| P05      | W Mean (µm) W Max (µm)    | 0,025<br>0,028 | 0,012<br>0,014 | 0,032<br>0,034 | 0,182<br>0,184 | 0,282<br>0,284 | 0,432<br>0,434 | 0,932<br>0,934 |

|          | Lg (µm)                   | 0,018          | 0,028          | 0,038          | 0,048          | 0,058          | 0,068          | 0,088          | 10             | 10             | 10             | 10             | 10             | 10             |

|          | Η (μm)                    | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          |

|          | W Min (µm)                | 0,007          | 0,007          | 0,007          | 0,007          | 0,007          | 0,007          | 0,007          | too small      | 0,018          | 0,168          | 0,268          | 0,418          | 0,918          |

| P06      | W Mean (µm) W Max (µm)    | 0,01<br>0,015  | 0,01<br>0,015  | 0,01<br>0,015  | 0,01<br>0,015  | 0,01           | 0,01<br>0,015  | 0,01<br>0,015  | too small      | 0,021          | 0,171<br>0,172 | 0,271<br>0,272 | 0,421<br>0,422 | 0,921<br>0,922 |

|          | Lg (µm)                   | 0,022          | 0,032          | 0,042          | 0,052          | 0,062          | 0,072          | 0,092          | 10             | 10             | 10             | 10             | 10             | 10             |

|          | Η (μm)                    | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          |

|          | W Min (µm)                | 0,026          | 0,026          | 0,026          | 0,026          | 0,026          | 0,026          | 0,026          | 0.015          | 0,035          | 0,185          | 0,285          | 0,435          | 0,935          |

| P07      | W Mean (µm) W Max (µm)    | 0,029          | 0,029          | 0,029          | 0,029          | 0,029          | 0,029          | 0,029          | 0,017          | 0,037          | 0,187<br>0,188 | 0,287<br>0,288 | 0,437<br>0,438 | 0,937<br>0,938 |

|          | Lg (µm)                   | 0,02           | 0,03           | 0,04           | 0,05           | 0,06           | 0,07           | 0,09           | 10             | 10             | 10             | 10             | 10             | 10             |

|          | Η (μm)                    | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          |

|          | W Min (µm)                | 0,008          | 0,008          | 0,008          | 0,008          | 0,008          | 0,008          | 0,008          | too small      | 0,02           | 0,17           | 0,27           | 0,42           | 0,92           |

| P08      | W Mean (µm) W Max (µm)    | 0,013<br>0,019 | too small      | 0,022<br>0,024 | 0,172<br>0,174 | 0,272<br>0,274 | 0,422<br>0,424 | 0,922<br>0,924 |

|          | Lg (µm)                   | 0,02           | 0,03           | 0,04           | 0,05           | 0,06           | 0,07           | 0,09           | 10             | 10             | 10             | 10             | 10             | 10             |

|          | Η (μm)                    | 0,0085         | 0,0085         | 0.0085         | 0,0085         | 0,0085         | 0,0085         | 0,0085         | 0,0085         | 0.0085         | 0,0085         | 0,0085         | 0,0085         | 0,0085         |

|          | W Min (µm)                | 0,021          | 0,021          | 0,021          | 0,021          | 0,021          | 0,021          | 0,021          | 0,01           | 0,03           | 0,18           | 0,28           | 0,43           | 0,93           |

| P09      | W Mean (µm) W Max (µm)    | 0,025<br>0,029 | 0,013<br>0,016 | 0,033<br>0,036 | 0,183<br>0,186 | 0,283<br>0,286 | 0,433<br>0,436 | 0,933<br>0,936 |

|          | Lg (μm)                   | 0,02           | 0,023          | 0,04           | 0,05           | 0,06           | 0,023          | 0,023          | 10             | 10             | 10             | 10             | 10             | 10             |

|          | Lg (μπ)                   | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          |

|          |                           |                |                | ĺ              |                |                |                |                |                | Ĺ              |                |                |                |                |

| P10      | W Min (µm) W Mean (µm)    | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | 0,009          | too small      | 0,018          | 0,168<br>0,171 | 0,268<br>0,271 | 0,418          | 0,918<br>0,921 |

|          | W Max (µm)                | 0,015          | 0,015          | 0,015          | 0,015          | 0,015          | 0,015          | 0,015          | too small      | 0,023          | 0,173          | 0,273          | 0,423          | 0,923          |

| <u> </u> | Lg (µm)                   | 0,02           | 0,03           | 0,04           | 0,05           | 0,06           | 0,07           | 0,09           | 10             | 10             | 10             | 10             | 10             | 10             |

|      | Η (μm)                 | 0,009  | 0,009  | 0,009  | 0,009  | 0,009  | 0,009  | 0,009  | 0,009     | 0,009  | 0,009  | 0,009  | 0,009  | 0,009  |

|------|------------------------|--------|--------|--------|--------|--------|--------|--------|-----------|--------|--------|--------|--------|--------|

|      | 14/14/                 |        |        |        |        |        |        |        |           |        |        |        |        |        |

| P11  | W Min (nm) W Mean (µm) | 0,021  | 0,021  | 0,021  | 0,021  | 0,021  | 0,021  | 0,021  | 0,011     | 0,031  | 0,181  | 0,281  | 0,431  | 0,931  |

| FII  | W Max (nm)             | 0,028  | 0,028  | 0,028  | 0,028  | 0,028  | 0,028  | 0,028  | 0,014     | 0,034  | 0,186  | 0,286  | 0,434  | 0,934  |

|      | vv max (mm)            | 0,020  | 0,020  | 0,020  | 0,020  | 0,020  | 0,020  | 0,020  | 0,010     | 0,000  | 0,100  | 0,200  | 0,100  | 0,000  |

|      | Lg (µm)                | 0,02   | 0,03   | 0,04   | 0,05   | 0,06   | 0,07   | 0,09   | 10        | 10     | 10     | 10     | 10     | 10     |

|      |                        |        |        |        |        |        |        |        |           |        |        |        |        |        |

|      | H (μm)                 | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01      | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   |

|      | W Min (µm)             | 0,009  | 0.009  | 0,009  | 0.009  | 0,009  | 0,009  | 0,009  | too small | 0,021  | 0,171  | 0,271  | 0,421  | 0,921  |

| P12  | W Mean (µm)            | 0,013  | 0,013  | 0,013  | 0,013  | 0,013  | 0,013  | 0,013  | too small | 0,023  | 0,173  | 0,273  | 0,423  | 0,923  |

|      | W Max (µm)             | 0,017  | 0,017  | 0,017  | 0,017  | 0,017  | 0,017  | 0,017  | too small | 0,024  | 0,174  | 0,274  | 0,424  | 0,924  |

|      |                        |        |        |        |        |        |        |        |           |        |        |        |        |        |

|      | Lg (µm)                | 0,02   | 0,03   | 0,04   | 0,05   | 0,06   | 0,07   | 0,09   | 10        | 10     | 10     | 10     | 10     | 10     |

|      | Η (μm)                 | 0,0095 | 0,0095 | 0,0095 | 0,0095 | 0,0095 | 0,0095 | 0,0095 | 0,0095    | 0,0095 | 0,0095 | 0,0095 | 0,0095 | 0,0095 |

|      | W Min (um)             | 0.024  | 0.024  | 0.024  | 0.024  | 0.024  | 0.024  | 0.024  | 0.008     | 0.028  | 0.178  | 0.278  | 0.428  | 0.928  |

| P13  | W Mean (µm)            | 0,024  | 0,024  | 0,024  | 0,024  | 0,024  | 0,024  | 0,024  | 0,008     | 0,028  | 0,178  | 0,278  | 0,426  | 0,926  |

|      | W Max (µm)             | 0,028  | 0,028  | 0,028  | 0,028  | 0,028  | 0,028  | 0,028  | 0,017     | 0,037  | 0,187  | 0,287  | 0,437  | 0,937  |

|      |                        |        |        |        |        |        |        |        |           |        |        |        |        |        |

|      | Lg (µm)                | 0,02   | 0,03   | 0,04   | 0,05   | 0,06   | 0,07   | 0,09   | 10        | 10     | 10     | 10     | 10     | 10     |

|      | H (µm)                 | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01      | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   |

|      | · /                    | ŕ      | ,      | ,      | ,      |        | ,      | ,      | ,         | ,      | ,      | ,      | ,      | ,      |

|      | W Min (µm)             | 0,008  | 0,008  | 0,008  | 0,008  | 0,008  | 0,008  | 0,008  | too small | 0,021  | 0,171  | 0,271  | 0,421  | 0,921  |

| P14  | W Mean (µm)            | 0,013  | 0,013  | 0,013  | 0,013  | 0,013  | 0,013  | 0,013  | too small | 0,023  | 0,173  | 0,273  | 0,423  | 0,923  |

|      | W Max (µm)             | 0,016  | 0,016  | 0,016  | 0,016  | 0,016  | 0,016  | 0,016  | too small | 0,025  | 0,175  | 0,275  | 0,425  | 0,925  |

|      | Lg (µm)                | 0,02   | 0,03   | 0,04   | 0.05   | 0,06   | 0,07   | 0,09   | 10        | 10     | 10     | 10     | 10     | 10     |

|      |                        | ,      | ,      | ,      | ,      |        | ,      | ,      |           |        |        |        |        |        |

|      | H (μm)                 | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01      | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   |

|      | M/ Min (uma)           | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.044     | 0.004  | 0.404  | 0.004  | 0.404  | 0.004  |

| P15  | W Min (µm) W Mean (µm) | 0,023  | 0,023  | 0,023  | 0,023  | 0,023  | 0,023  | 0,023  | 0,011     | 0,031  | 0,181  | 0,281  | 0,431  | 0,931  |

|      | W Max (µm)             | 0,020  | 0,020  | 0,020  | 0,020  | 0,020  | 0,020  | 0,020  | 0,019     | 0,039  | 0,189  | 0,289  | 0,439  | 0,939  |

|      | \\ \ /                 | ,      | ,      | ,      | ,      |        | ,      | ,      | ,         | ,      | ,      | ,      | ,      | ,      |

|      | Lg (µm)                | 0,02   | 0,03   | 0,04   | 0,05   | 0,06   | 0,07   | 0,09   | 10        | 10     | 10     | 10     | 10     | 10     |

|      | LI (um)                | 0.01   | 0.01   | 0.01   | 0.01   | 0.01   | 0.01   | 0.01   | 0.01      | 0.01   | 0.01   | 0.01   | 0.01   | 0.01   |

|      | H (µm)                 | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   | 0,01      | 0,01   | 0,01   | 0,01   | 0,01   | 0,01   |

|      | W Min (µm)             | 0,009  | 0,009  | 0,009  | 0,009  | 0,009  | 0,009  | 0,009  | too small | 0,021  | 0,171  | 0,271  | 0,421  | 0,921  |

| P16  | W Mean (µm)            | 0,014  | 0,014  | 0,014  | 0,014  | 0,014  | 0,014  | 0,014  | too small | 0,024  | 0,174  | 0,274  | 0,424  | 0,924  |

| 1 10 | W Max (µm)             | 0,017  | 0,017  | 0,017  | 0,017  | 0,017  | 0,017  | 0,017  | too small | 0,026  | 0,176  | 0,276  | 0,426  | 0,926  |

| 1 10 | U- /                   |        |        |        |        |        |        |        |           |        |        |        |        |        |

|      | Lg (µm)                | 0,02   | 0,03   | 0.04   | 0.05   | 0,06   | 0,07   | 0,09   | 10        | 10     | 10     | 10     | 10     | 10     |

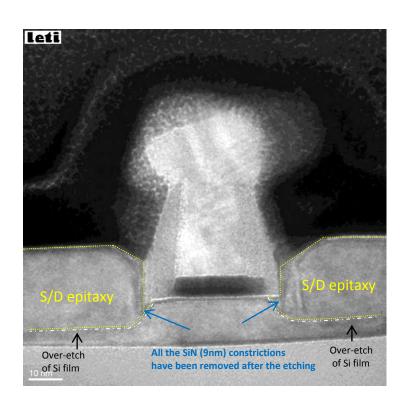

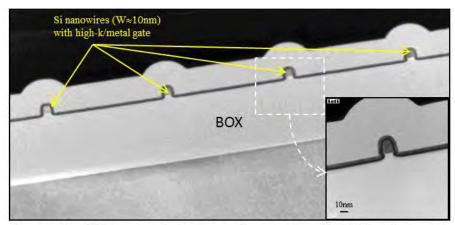

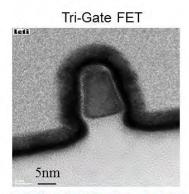

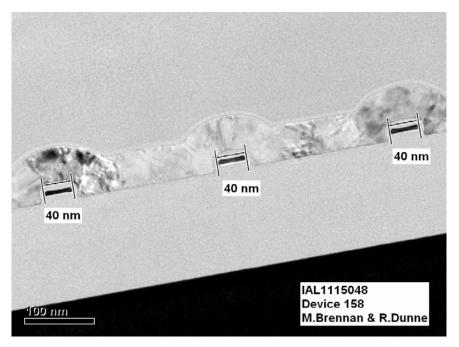

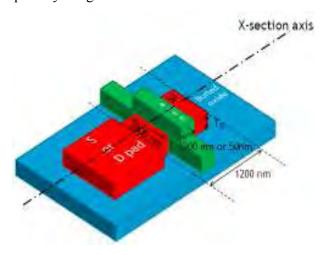

#### This is the doping targeted for the wafers:

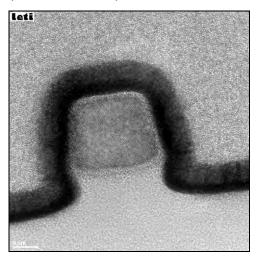

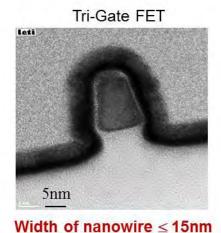

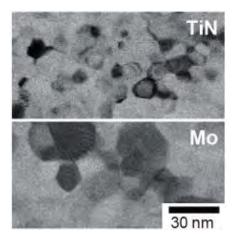

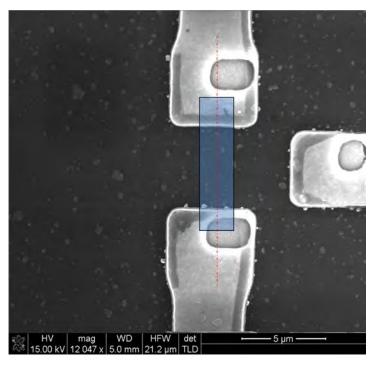

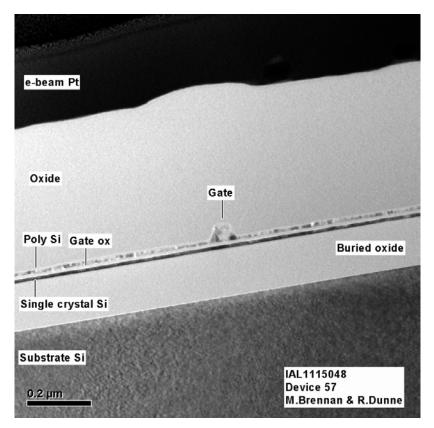

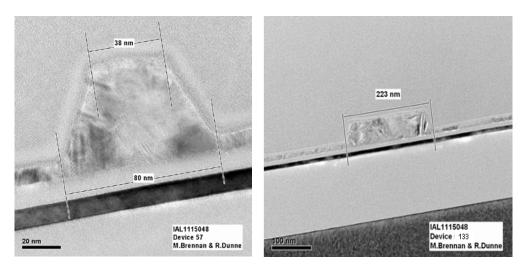

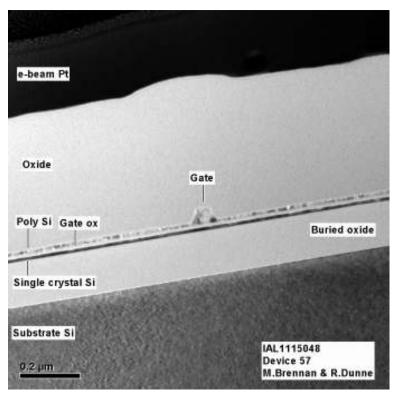

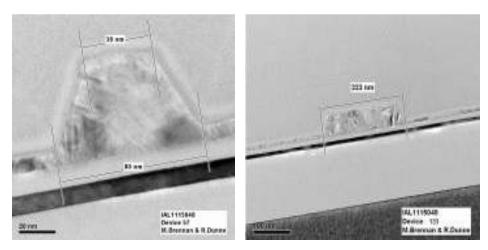

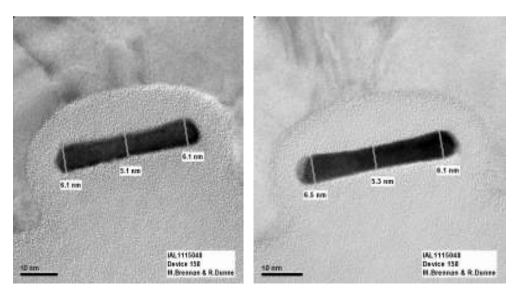

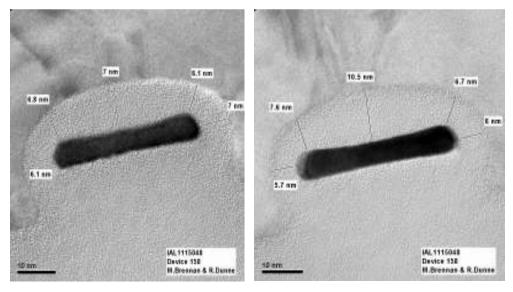

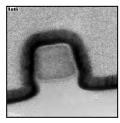

#P01: NMOS (10<sup>19</sup>cm<sup>-3</sup>) #P02: PMOS (10<sup>19</sup>cm<sup>-3</sup>) #P03: NMOS (5×10<sup>18</sup>cm<sup>-3</sup>) #P04: PMOS (5×10<sup>18</sup>cm<sup>-3</sup>) #P05: NMOS (10<sup>19</sup>cm<sup>-3</sup>) #P06: NMOS (10<sup>19</sup>cm<sup>-3</sup>) #P07: NMOS (2×10<sup>19</sup>cm<sup>-3</sup>) #P08: NMOS (2×10<sup>19</sup>cm<sup>-3</sup>) #P09: NMOS (4-5×10<sup>19</sup>cm<sup>-3</sup>) #P10: NMOS (4-5×10<sup>19</sup>cm<sup>-3</sup>) #P11: PMOS (10<sup>19</sup>cm<sup>-3</sup>) #P12: PMOS (10<sup>19</sup>cm<sup>-3</sup>) #P13: PMOS (2×10<sup>19</sup>cm<sup>-3</sup>) #P14: PMOS (2×10<sup>19</sup>cm<sup>-3</sup>) #P15: PMOS (4-5×10<sup>19</sup>cm<sup>-3</sup>) #P15: PMOS (4-5×10<sup>19</sup>cm<sup>-3</sup>) All the critical dimension (CD) measurements (after photolithography and after active patterning) are done using in-line field-emission-scanning electron microscope (SEM). The gate stack is composed of high-κ/metal gate. 2.3nm chemical vapour deposition (CVD) HfSiON with 5nm ALD TiN and Poly-Silicon (50nm) layers are deposited. This corresponds to an equivalent oxide thickness (EOT) of around 1.2nm. A HRTEM picture of the nanowire cross-section has been performed in order to reveal the good conformal gate stack deposition surrounding the nanowire and to evaluate the nanowire width. Fig. 1 shows a cross-sectional TEM micrograph of a conventional triple-gate silicon nanowire with high-k/metal gate stack (isolated devices).

Figure 1: TEM cross-section showing a 14nm×14nm Trigate silicon nanowire with 2.3nm HfSiON/5nm TiN gate stack.

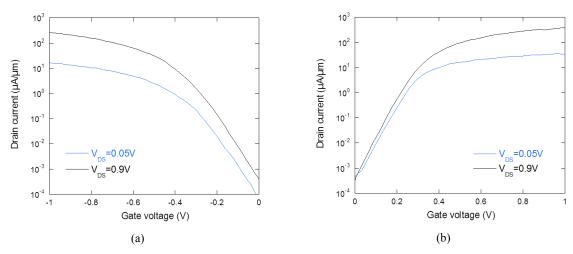

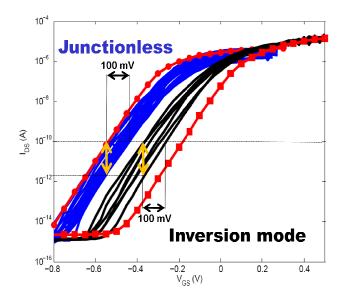

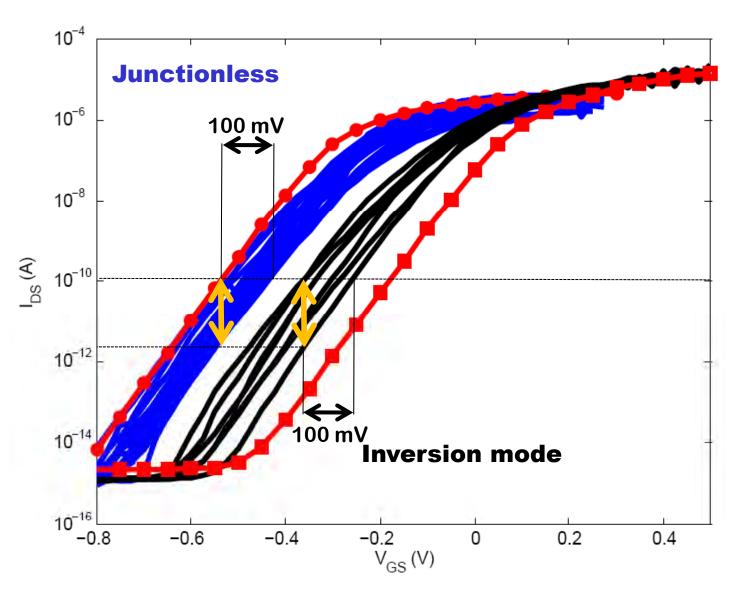

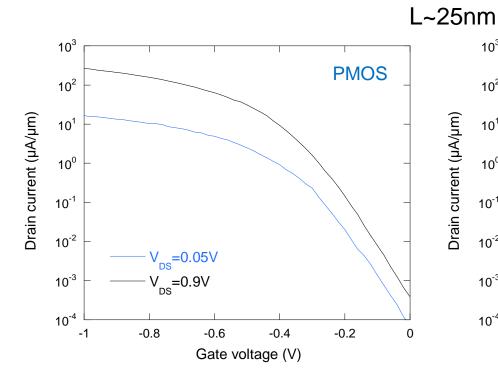

The measured  $I_{DS}$ - $V_{GS}$  (Fig. 2) characteristics for N/P *junctionless* trigate with L=30nm, show well-behaved characteristics with DIBL lower than 30mV/V for NMOS. A good electrostatic integrity for NW is verified.

Figure 2:  $I_{DS}$ - $V_{GS}$  characteristics for PMOS (a) (Ion=206  $\mu$ A/ $\mu$ m @  $V_{GS}$ = $V_{DS}$ =-0.9V Ioff=0.38nA/ $\mu$ m @  $V_{GS}$ =0V and  $V_{DS}$ =0.9V SS=75mV/dec) and for NMOS (b) (Ion=280  $\mu$ A/ $\mu$ m @  $V_{GS}$ = $V_{DS}$ =0.9V Ioff=0.36nA/ $\mu$ m @  $V_{GS}$ =0.9V SS=60mV/dec).

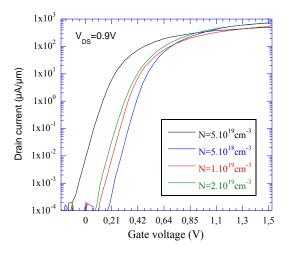

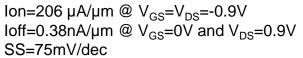

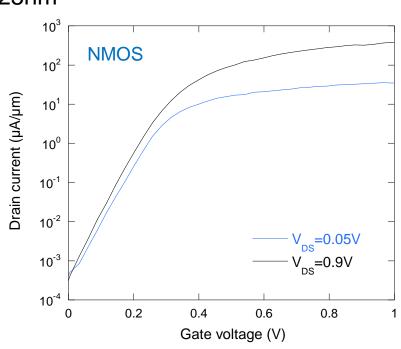

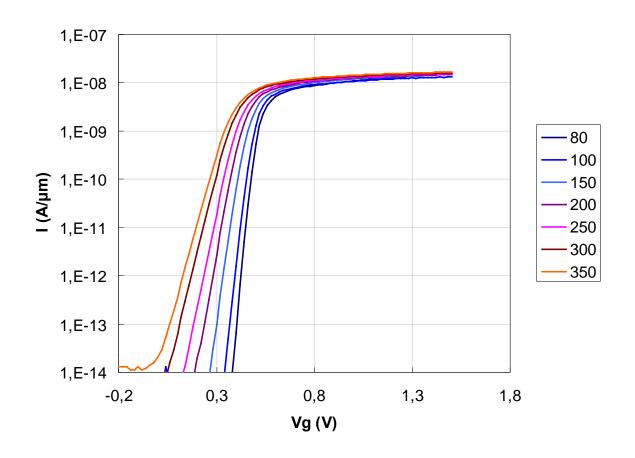

Figure 3 shows the  $I_{DS}$ - $V_{GS}$  characteristics for NMOS *junctionless* trigate with L=100nm. Various doping are used.

Figure 3:  $I_{DS}$ - $V_{GS}$  characteristics for NMOS extracted at  $V_{DS}$ =0.9V for junction trigate nanowire (W~18nm) and channel doping varying from  $5\times10^{19}$ cm<sup>-3</sup> down to  $5\times10^{19}$ cm<sup>-3</sup>. Lg=100nm.

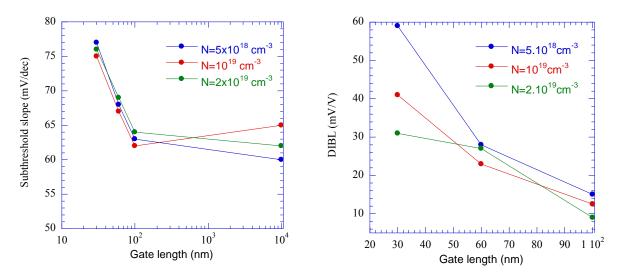

The subthreshold slope and DIBL are shown in figure 4 and 5.

Figure 4: Subthreshold slope (SS) as a function of the gate length for *junctionless* Trigate-NW (NMOSFET)

Figure 5: DIBL as a function of the gate length for *junctionless* Trigate-NW (NMOSFET)

By taking into consideration the better electrostatic control on the channel for junctionless Trigate NW, SS and DIBL are strongly reduced for the smallest gate lengths. The DIBL is improved when the channel doping is increased. Short channel effects (SCE) immunity is clearly evidenced.

#### III. FIRST WAFER DELIVERED TO PARTNERS

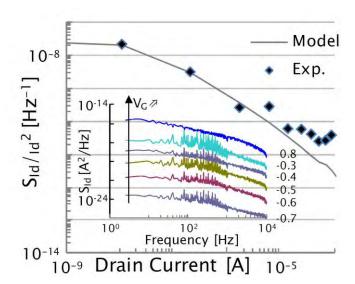

First wafer has been send to partners (IMEP) in order to characterize noise in junctionless trigate devices. Figure 6 shows the noise measurement. The noise measurement follows carrier fluctuations model and reveals trap density levels comparable to wide planar

device. The degraded subthreshold slope observed on PMOS probably comes from this higher trap density.

Figure 6: Fit of noise spectrum with trapping model. Lg=40nm, W= $10\mu$ m. Inset: noise level versus frequency.

#### IV. CONCLUSION

The first junctionless trigated nanowires have been fabricated and characterized. The On-current of measured junctionless transistors seems to be mainly limited by a lower mobility compared to the inversion-mode devices. However, interesting features are their tunable threshold voltage, low noise with control trap density and good scalability.

# **Project Technical Report**

**Project: EU FP7 SQWIRE**

**Reporting period: 2010-09-01 – 2011-08-31**

### Work Package 2

#### **Contributions from Soitec.**

#### **Progress**

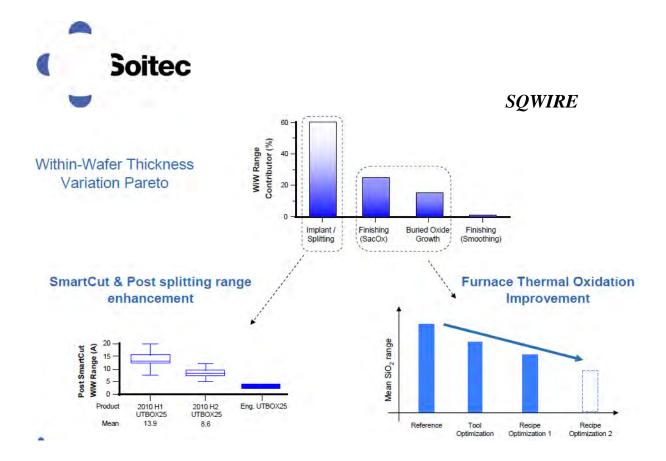

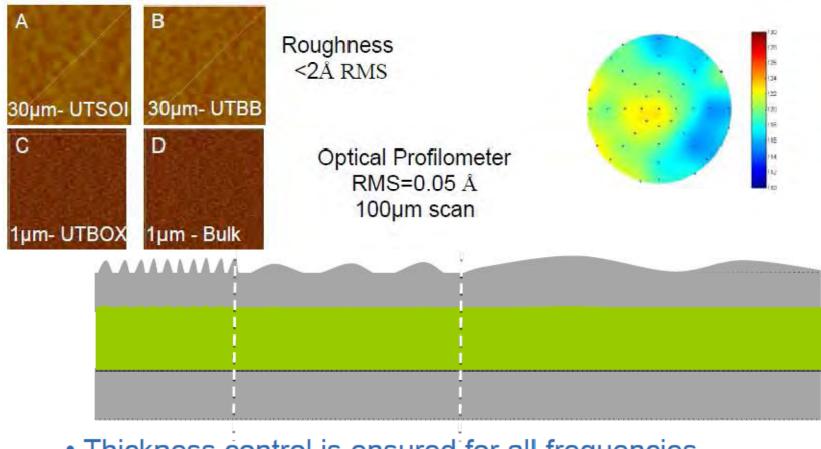

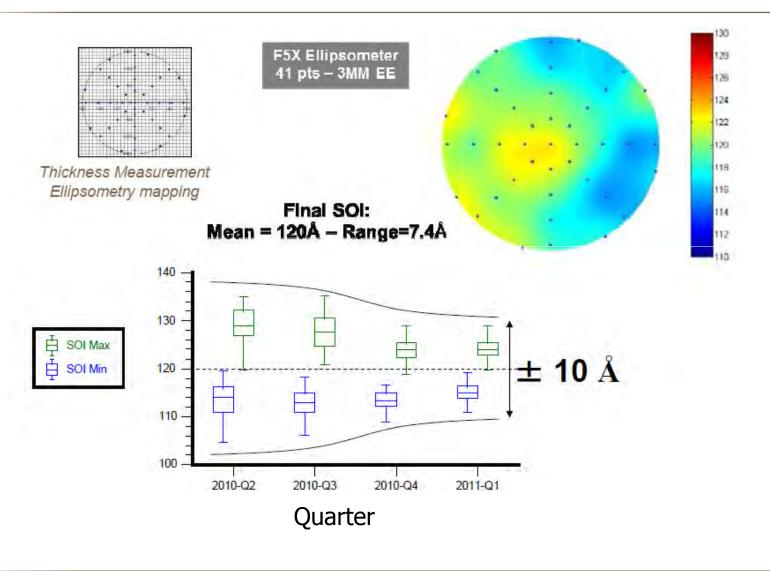

Soitec has worked on the improvement of the thickness uniformity of 300 SOI wafers with a silicon film thickness of less than 20 nm.

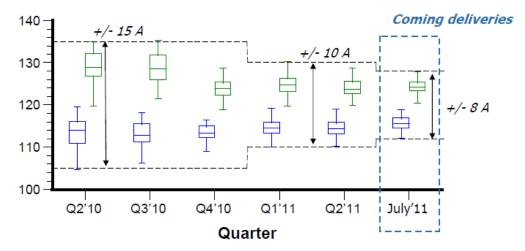

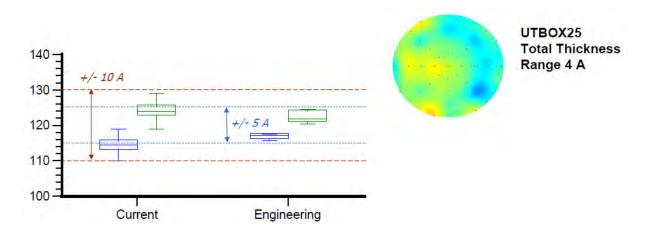

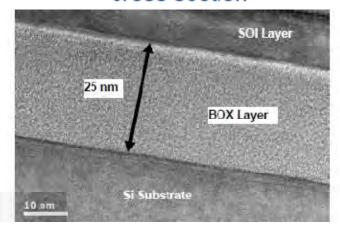

During first 12 month of the Project major efforts have been dedicated to the development of 300 mm wafers with a thin top layer of Si (< 20 nm) and with the BOX thickness < 30 nm. The focus, in close collaboration with LETI, was on the tight thickness control. The figures below for the wafers with BOX = 25 nm illustrate the progress made by Soitec on this path.

Figure 1: UTBOX25 update: Total SOI thickness variation.

Figure 2: UTBOX25 SOI Thickness control improvement.

Figure 3: UTBOX25 SOI thickness control demonstration.

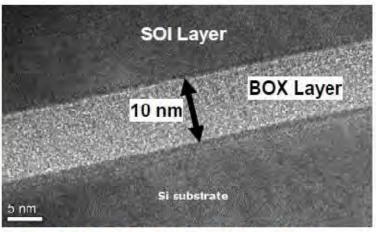

Before the start of SQWIRE project Soitec WP2 partner LETI has already established a nanowire transistor fabrication process flow for the SOI wafers with the BOX thickness of 145 nm. Therefore the first lot of 12 wafers delivered to LETI for the device fabrication in December 2010 has had top Si thickness of 12 nm and BOX thickness of 145 nm. A thinning of these wafers to 10 nm has been done at LETI clean room during fabrication of junctionless devices. The thickness of the top Si layer has been verified by XTEM and spectroscopic ellipsometry. A delivery of the second batch of 24 wafers to LETI is scheduled in the first week of October 2011.

#### **SQWIRE**

#### **Summary**

A path to  $\pm$  2 Å variation for thickness control has been identified and will be implemented before end of 2011. The work to improve the total thickness variation of the top Si layer will continue.

#### **Industrial Exploitation of Project Results/ Information Sharing**

The following paper was published in the beginning of May 2011:

W. Schwarzenbach, X. Cauchy, O. Bonnin, N. Daval, C. Aulnette, C. Girard, B.-Y. Nguyen & C. Maleville "Ultra-thin film SOI/BOX substrate development, its application and readiness", ECS Transactions, 35 (5) 239-245 (2011)The representative publications at

# RAPPORT TECHNIQUE TECHNICAL REPORT

# Deliverable 2.2: SQWIRE – Silicon Quantum Wire Transistors Fabrication Process Specification for *junctionless* MOSFET

Projet / Project: SQWIRE N/Réf : D2NT/10.615/SB

|                                  | Nom / Fonction – Name / Function | Date                | Visa |

|----------------------------------|----------------------------------|---------------------|------|

| Auteur(s) :<br>Author(s)         | Sylvain Barraud                  | November 23th, 2010 |      |

| ( )                              | Tél : 04-38-78-98-45             |                     |      |

| Approbateur :<br>Assentor        | Olivier Faynot                   | November 23th, 2010 |      |

| <u>Diffusion</u> :               |                                  |                     |      |

| Archivage GED / Filing Fiche GED |                                  |                     |      |

|                                  |                                  |                     |      |

|                                  |                                  |                     |      |

|                                  |                                  |                     |      |

|                                  |                                  |                     |      |

|                                  |                                  |                     |      |

|                                  |                                  |                     |      |

|                                  |                                  |                     |      |

|                                  |                                  |                     |      |

Projet: SQWIRE

N/Réf: D2NT/10.615/SB

#### **Abstract**

Nanowire (NW) and Tri-gated Complementary Metal Oxide Semiconductor (CMOS) technology appear as an attractive option to overcome standard CMOS bulk technology limits in terms of scaling, performances and power consumption [1-3]. The electrostatic control over the channel is indeed improved in NWs, leading to a significant reduction of short channel effects [4] and thus leakage currents in the OFF state.

Based on existing expertise in fabrication of FD-SOI nanowire devices, we will develop a fabrication route for n-channel and p-channel *junctionless* nanowire MOSFET transistor. Existing mask set will be used, with the exception of the active area level which will have to be redrawn. The FD-SOI route will be adapted in order to target *junctionless* NW with width varying from  $10 \text{nm} \leq \text{W} \leq 20 \text{nm}$ , silicon thickness  $T_{\text{SOI}} = 10 \text{nm}$  and with a gate length  $L_G < 30 \text{nm}$ .

Those original devices have demonstrated near-ideal subthreshold slope, extremely low leakage current and less degradation of mobility with gate voltage and temperature than conventional transistors [5].

R.C.S. PARIS B 775 685 019

Laboratoire d'électronique et de technologie de l'information Direction de la recherche technologique Département NaNoTec

RAPPORT TECHNIQUE TECHNICAL REPORT

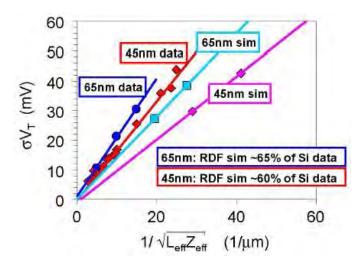

I. Introduction

The silicon nanowire field-effect transistor is one of the promising candidates for future

ultra-scaled CMOS technology. It offers the best gate electrostatic control on short-channel-

effects. The formation of ultra-shallow junctions is a limiting factor to scale and puts severe

constraints on the processing thermal budget. Ultra-short-time annealing techniques are being

employed to eliminate thermal diffusion of the source and drain doping impurities, but even the

lateral impurity spread due to ion implantation itself is starting to cause problems. In addition to

the difficulty of forming ultra-sharp junctions, random impurity fluctuations from source and

drain dopants scattered in the channel region cause variability problems.

Here, a new type of transistor is investigated in which there are no junctions and no doping

concentration gradients. These devices have full CMOS functionality and are made using Tri-

gated silicon nanowires. Those original devices have demonstrated near-ideal subthreshold

slope, extremely low leakage current and less degradation of mobility with gate voltage and

temperature than conventional transistors [5].

The objective of this task (D2.2) is to propose an integration scheme and fabrication process

specifications for junctionless Tri-gated MOSFET transistors on 300 mm wafers based on an

adapted route from FD-SOI MOSFET devices developed at CEA-Leti.

First of all, the integration strategy used for the elaboration of *junctionless* tri-gated nanowire

transistor is presented.

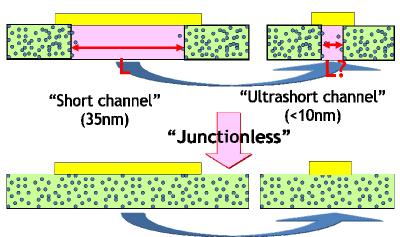

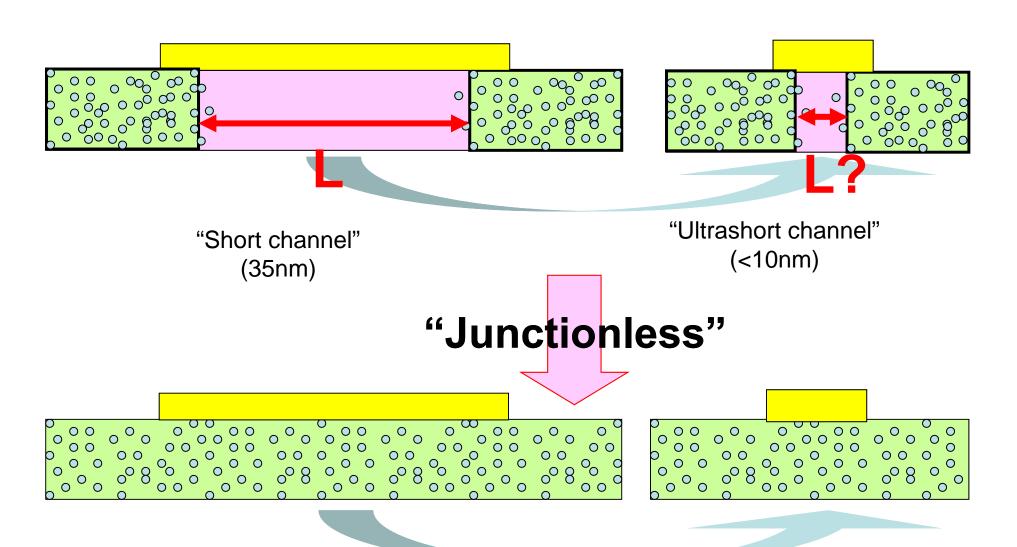

II. JUNCTIONLESS TRANSISTORS

The main difference between conventional and junctionless MOSFET transistors is that

the channel doping is similar to the source-drain doping.

II.1. NANOWIRE ELABORATION ON 300 MM WAFERS FROM DUV193NM LITHOGRAPHY

Silicon-on-Insulator (SOI) structures with silicon layers of 12 nm in thickness are used. The key

for the fabrication of junctionless gated resistor is the formation of a semiconductor layer that is

Commissariat à l'énergie atomique et aux énergies alternatives

CEA, LETI, MINATEC Campus

Centre de Grenoble – 17 rue des Martyrs – 38054 Grenoble CEDEX 9

Tel: 33 - 04 38 78 10 34 - Fax: 33 - 04 38 78 06 24 - veronique.bourdon@cea.fr

Formulaire Rapport Technique – Version 6 du 16/03/2010 Etablissement public à caractère industriel et commercial

R.C.S. PARIS B 775 685 019

3/12

# RAPPORT TECHNIQUE TECHNICAL REPORT

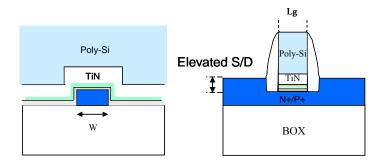

thin and narrow enough to allow full depletion of carriers when the device is turned off [7]. Then, the silicon layer will be thinned down to 10nm. The semiconductor also needs to be heavily doped to allow for a reasonable amount of current flow when the device is turned on. The implant energies and doses will be chosen (from process simulation – Athena Silvaco) to yield uniform doping concentration ranging from  $5 \times 10^{18}$  cm<sup>-3</sup> up to  $5 \times 10^{19}$  cm<sup>-3</sup>. Then, the silicon layer will be patterned to create the silicon nanowires by a mesa isolation technique. The active stack used in this work will be consisted of a 10nm doped Si, 2.5nm SiO<sub>2</sub> dielectric layer and an organic bottom anti-reflective coating (BARC) layer of around 24nm patterned using 193nm ArF resist. The thickness of the photoresist is around 160nm. The active zone (i.e. nanowire feature) will be carried out using the trimmed resist/BARC as a mask. Obviously, the final linewidth of nanowires will be determined mainly by the amount of trimmed resist.

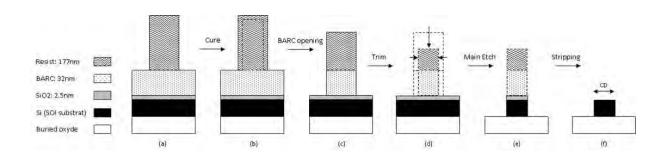

The good electrostatic control being based on low dimensions of nanowire width (or diameter), shorter wavelengths are required for lithography. As a result, an alternative method to *e-beam* lithography is proposed in this study to achieve sub-15nm nanowire width in order to lower the manufacturing cost and shorten the development time.

Today's most advanced lithography uses 193nm wave-length for the production of integrated circuits devices. Following the same philosophy than for the gate patterning, we proposed to develop an approach based on resist trimming by dry plasma etching to elaborate our silicon nanowires. This approach has the advantage of reducing the dimensions without increasing the complexity of the lithography requirements. A schematic of the process flow of this trimming method is summarized in Fig. 1. First of all, HBr plasma curing process was performed in order to harden the 193nm ArF resist for better etching resistance. Then, the BARC opening is done using CF<sub>4</sub> chemistry. This chemistry will be used in order to ensure vertical resist/BARC profile and correct linewidth roughness [6]. Moreover, this sequence consuming a lot of photoresist, the thin thickness of the BARC layer is well suited to minimize the resist budget during the process. Then, the BARC/resist trimming process is performed just before the main etch to selectively pattern the silicon on the buried oxide. Trimming resist is performed to achieve nanowire

Laboratoire d'électronique et de technologie de l'information Direction de la recherche technologique Département NaNoTec

RAPPORT TECHNIQUE TECHNICAL REPORT

structures as small as **15nm in width** using the HBr/O<sub>2</sub> plasma. In order to smooth the resist patterns and then reduce the linewidth roughness, a curing step will be performed just before the

trimming.

The investigated structures after the photolithography are shown in Fig. 2. They comprised

isolated lines (NW) and arrays of lines with long and short dimensions. The arrays of lines with

long dimensions will be used to extract the capacitance and the carrier mobility.

All the critical dimension (CD) measurements (after photolithography and after active

patterning) will be done using in-line field-emission-scanning electron microscope (SEM).

The linewidth before etching –referred to as developed inspection critical dimension- is around

80nm. After etching, the reduction of the silicon nanowire width induces by the trimming is

targeted to 65 nm in order to have nanowire width of around 15nm. Due to the dispersions

induce by the photolithography, the NW width after etching is expected to vary between 10nm

and 20nm.

I.2. GATE STACK DEPOSITION AND CHANNEL LENGTH

For the first run, the gate stack used will be composed of high-κ/metal gate. 2.3nm chemical

vapour deposition (CVD) HfSiON with 5nm CVD TiN and Poly-Silicon (50nm) layers will be

deposited. This corresponds to an equivalent oxide thickness (EOT) of around 1.1nm.

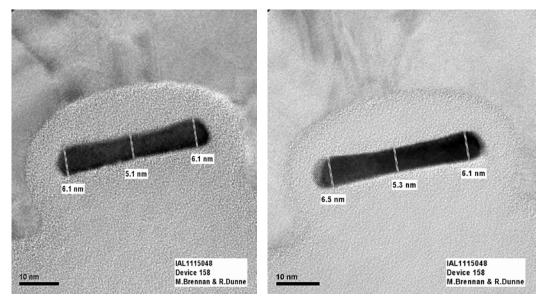

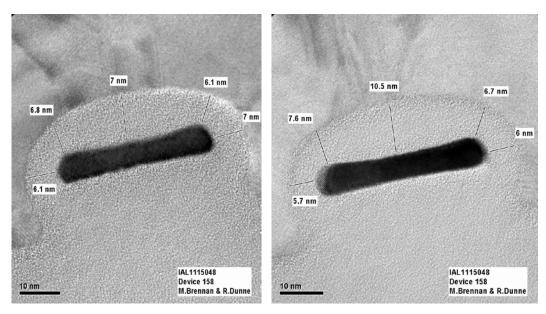

A HRTEM picture of the nanowire cross-section will be performed in order to reveal the good

conformal gate stack deposition surrounding the nanowire and to evaluate the nanowire width.

Fig. 3 shows a cross-sectional TEM micrograph of a conventional triple-gate silicon nanowire

with high-k/metal gate stack (isolated devices).

As for the active patterning, 193nm lithography tool will be used with a resist trimming in order

to address gate lengths down to 25nm. Firt results obtained on regular Tri-gated nanowire are

shown in Fig. 4. Afterwards, a nitride spacer thickness of around 20nm will be formed on the

Commissariat à l'énergie atomique et aux énergies alternatives CEA, LETI, MINATEC Campus

Centre de Grenoble – 17 rue des Martyrs – 38054 Grenoble CEDEX 9

5/12

# RAPPORT TECHNIQUE TECHNICAL REPORT

silicon source-drain. Then, low parasitic resistance will be realized by **epitaxial doped silicon growth on the source-drain** ( $\Delta T_{SI}$ =18nm). A schematic process flow is presented in Fig. 5.

For the second run, additional gate stack composed of  $SiO_2$  (2-3nm)/Poly-Si will be processed to compare with high- $\kappa$ /metal gate stack.

Finally, the main process specifications for the fabrication of junctionless MOSFET are the following:

Doping N<sup>+</sup>/P<sup>+</sup>:  $5 \times 10^{18} \text{cm}^{-3} \le \text{N} \le 5 \times 10^{19} \text{cm}^{-3}$

Silicon thickness  $T_{SOI}=10$ nm

Gate stack: 0.8nm SiO<sub>2</sub> / 2.3nm HfSiON / 5nm TiN / 50nm Poly-Si

CD spacer: 20nm Elevated source/drain: 18nm

# RAPPORT TECHNIQUE TECHNICAL REPORT

#### **REFERENCES**

- [1] S.-D. Suk, K. Hwan, K.-H. Cho, M. Li, Y.Y. Yeoh, S.-Y. Lee, S.M. Kim, E.-J. Yoon, H.-S. Kim, C.W. Oh, S.H. Kim, D.-W. Kim, D. Park, "High-performance Twin silicon nanowire MOSFET (TSNWFET) on Bulk Si wafer" *IEEE Trans. on Nanotechnology*, vol. 7, pp. 181, 2008.