FP7-ICT-2013-11-619871

#### **BASTION**

Board and SoC Test Instrumentation for Ageing and No Failure Found

Instrument: Collaborative Project

Thematic Priority: Information and Communication Technologies

# Report on structural analysis, verification and optimization methodology for ICL networks (Deliverable D2.3)

Due date of intermediate deliverable: December 31, 2015

Ready for submission date: February 11, 2016 Due date of final deliverable: December 31, 2015

Start date of project: January 1, 2014 Duration: Three years

Organisation name of lead contractor for this deliverable: Hochschule Hamm-Lippstadt University of Applied Sciences

Revision 2.0.4

| Project co-funded by the European Commission within the Seventh Framework |                                            |   |  |  |

|---------------------------------------------------------------------------|--------------------------------------------|---|--|--|

| Programme (2014-2016)                                                     |                                            |   |  |  |

| Dissemination Level                                                       |                                            |   |  |  |

| PU                                                                        | Public                                     | X |  |  |

| PP                                                                        | Restricted to other programme participants |   |  |  |

|                                                                           | (including the Commission Services)        |   |  |  |

| RE                                                                        | Restricted to a group specified by the     |   |  |  |

|                                                                           | consortium (including the Commission       |   |  |  |

|                                                                           | Services)                                  |   |  |  |

| CO                                                                        | Confidential, only for members of the      |   |  |  |

|                                                                           | consortium (including the Commission       |   |  |  |

|                                                                           | Services)                                  |   |  |  |

#### **Notices**

For more information, please contact Prof. Dr. Krenz-Baath, e-mail: <a href="mailto:rene.krenz-baath@hshl.de">rene.krenz-baath@hshl.de</a>

This document is intended to fulfil the contractual obligations of the BASTION project concerning deliverable D2.3 described in contract 619871.

© Copyright BASTION 2016. All rights reserved.

# **Table of Revisions**

| Version | Date          | Description and reason                                   | Author                                                        | Affected sections                  |

|---------|---------------|----------------------------------------------------------|---------------------------------------------------------------|------------------------------------|

| 0.1     | June 18, 2014 | Initial document created                                 | R. Krenz-Baath                                                | Contents                           |

| 0.2     | Sept 18, 2014 | Full non-polished document                               | R. Krenz-Baath                                                | All                                |

| 0.3     | Sept 22, 2014 | Update to Section 3                                      | A. Jutman                                                     | Section 3                          |

| 0.4     | Sept 22, 2014 | Updates all Sections added Executive Summary             | All                                                           | All                                |

| 1.0     | Sept 30, 2014 | Reviewing and updating all sections                      | R. Krenz-Baath, F. Zadegan, S. Devadze, A. Jutman, C. Laudert | all                                |

| 2.0.1   | Dec 8, 2015   | Initial version for final document                       | R. Krenz-Baath                                                | all                                |

| 2.0.2   | Dec 10, 2015  | Added and updated contributions by Lund, TUT, IFAG, HSHL | R. Krenz-Baath                                                | Sections<br>3.3.4, 4.3.2,<br>4.3.5 |

| 2.0.3   | Dec 15, 2015  | Merged contributions                                     | R. Krenz-Baath                                                | all                                |

| 2.0.4   | Feb 09, 2016  | Final version                                            | R. Krenz-Baath                                                | all                                |

# **Author, Beneficiary**

René Krenz-Baath, HSHL Erik Larsson, ULUND Farrokh Zadegan, ULUND Jaan Raik, TUT Artur Jutman, TL Sergei Devadze, TL Konstantin Shibin, TL Piet Engelke, IFAG Carsten Laudert, IFAG

# **Executive Summary**

This document presents BASTION contributions in the area of modelling, optimization and verification of IJTAG 1687 networks. First the state of the art is discussed and the described contributions are set into context. Next initial research regarding 1687 network topologies in connection to their ability to keep the time overhead low (robustness) when accessed throughout the lifecycle of a product is presented. Furthermore, methods to perform fault management in 1687 networks are proposed. In addition, an approach to model 1687 networks in order to perform verification and validation is described. Afterwards several verification challenges are discussed which are relevant to ensure the compliance of ICL descriptions as well as to enable efficient re-targeting of PDL instructions and debugging of ICL descriptions. Finally, conclusions are provided.

#### **List of Abbreviations**

BIST

CPU

Central Processing Unit

CSU

Capture-Shift-Update Cycle

DIN Diagnostic Instrumentation Network

DRC Design Rule Check

ECC Error-Correction Code

EDA Electronic Design Automation

FP7 European Union's 7<sup>th</sup> Framework Programme

FSM Finite State Machine

ICL Instrument Connectivity Language

IEEE Institute of Electrical and Electronics Engineers

IJTAG Internal JTAG, a short name for IEEE 1687 standard and infrastructure

collectively

ILP Integer Linear Programming

IM Instrument Manager

IST Information Society Technologies

ITRS International Technology Roadmap for

Semiconductors

JTAG Joint Test Action Group

LBIST Logic BIST

LSIB Locking Segment Insertion Bits

MBIST Memory BIST

MUX Multiplexer

PN Perfect Network

NFF No Fault Found, also No Failure Found

OAT Overall Access Time

OS Operating System

PCB Printed Circuit Board

PDL Procedural Description Language

RMResource Manager Register-Transfer-Level RTL **Boolean Satisfiability SAT** ScanMux Control Bit **SCB** primary Scan Input SI Segment Insertion Bit SIB primary Scan Output SO System-on-Chip SoC **Test Access Point TAP** Test Data Register **TDR**

URL Uniform Resource Locator

# **Table of Contents**

| Table of Revisions                                                   | iii |

|----------------------------------------------------------------------|-----|

| Author, Beneficiary                                                  | iii |

| Executive Summary                                                    | iv  |

| List of Abbreviations                                                | v   |

| Table of Contents                                                    | iv  |

| 1 Introduction                                                       | 2   |

| 1.1 The Structure of the report                                      | 3   |

| 2 Background                                                         |     |

| Analysis, Design and Optimization of IEEE 1687 Networks              | 6   |

| 3.1 Introduction                                                     | 6   |

| 3.2 Related Work                                                     | 7   |

| 3.3 BASTION Contributions                                            | 7   |

| 3.3.1 Robustness of 1687-Compatible Scan Networks                    | 7   |

| 3.3.2 Race on Update Signal                                          | 10  |

| 3.3.3 IEEE 1687 Extensions for Fault Management                      | 11  |

| 3.3.4 Safety and Security Aspects of IEEE 1687 Networks              | 18  |

| 3.4 Summary                                                          | 23  |

| 4 Verification and Validation of IEEE 1687 Networks                  | 24  |

| 4.1 Introduction                                                     | 24  |

| 4.2 Related Work                                                     | 25  |

| 4.3 BASTION Contributions                                            | _   |

| 4.3.1 Modeling of IEEE 1687 Networks for Verification and Validation |     |

| 4.3.2 ICL Compliance, Verification and Silicon Validation            | 33  |

| 4.3.3 Smarter Retargeting                                            |     |

| 4.3.4 Co-verification of ICL and PDL                                 | 38  |

| 4.3.5 Access Time Minimization in IEEE 1687 Networks                 | 39  |

| 4.4 Summary                                                          | 51  |

| 5 Conclusions                                                        |     |

| 6 Bibliography                                                       | 53  |

#### 1 Introduction

In this deliverable, results are reported about the research performed by BASTION partners in the area of structural analysis, verification and optimization methodology for ICL networks. This document is a second and final edition of the deliverable. It concludes work performed in T2.4 "Analysis, verification and optimization of IJTAG network topologies".

The document starts with an introduction to 1687 networks and an overview of the state of the art. After that, the document contains a detailed description of basic building blocks of 1687 networks. Later, the first BASTION contributions are presented and initial conclusions are formulated.

The first contribution in the area of analysis, design and optimization of IEEE 1687 networks investigates the robustness of 1687 networks with respect to the overall access time for different use cases or scenarios. The fundamental problem is that at design time it is very difficult to predict how an IEEE 1687 network will be used through the life-time. Embedded instruments will be applied in a broad range of applications with individual requirements. The contribution evaluates the overall access time on different network topologies. Another contribution discussed in this area is a new approach to extend ICL networks to support fault management. Fault management is increasingly important in context of aging and in-field validation. One of the core contributions is the proposal of flag-based error reporting infrastructure, which allows an effective mechanism to transmit error detection signals through large and complex ICL networks requiring only small implementation effort. Also the aspects of asynchronous fault detection and possible extensions of standard SIBs are discussed. Furthermore, approaches for fault localization and fault diagnosis in 1687 networks are presented. The final presented contribution in the area of analysis, design and optimization of IEEE 1687 networks focuses on safety and security aspects in particular an access protection concept is proposed which is based on separation of the group of instruments applicable by the future device user and the group of security relevant instruments into two separate IEEE 1687 networks.

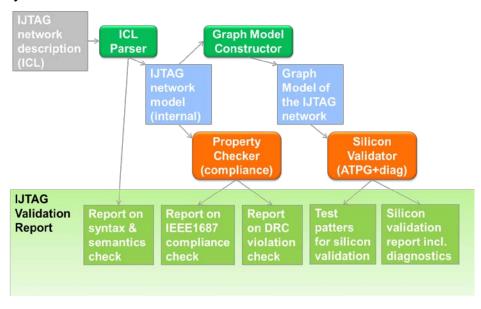

The next set of contributions is related to the area of the verification and the validation of 1687 networks. After the state of the art is discussed, an initial approach to model a given ICL network using a graph representation is presented. Providing an efficient and complete model of a complex 1687 network is an inevitable requirement in order to perform scalable verification and validation of very large networks. The different steps of the modelling process are explained in detail and demonstrated using an explanatory example of an ICL network. Next a validation flow for 1687 networks is proposed which complies with the verification challenges discussed in the same section. Several checks of ICL networks on different levels are proposed, for example the accessibility of individual instruments, instrument correctness checks and detection of hidden or undocumented structures. Furthermore, future challenges with respect to efficient re-targeting techniques as well as the co-verification of PDL instructions in connection to a specific ICL network are discussed in detail.

#### 1.1 The Structure of the report

This report is structured as follows. First the basic idea behind the IEEE 1687 standard including a short description of basic building blocks as well as descriptions of the Instrument Connectivity Language (ICL) and the Procedural Description Language (PDL) is discussed. Section 3 contains an introduction and set of BASTION contributions in the area of design and optimization of 1687 networks. BASTION contributions in verification and validation of 1687 networks as well as the discussion of future verification challenges in the field are discussed in Section 4. This report is concluded in Section 5.

The major differences of the 2<sup>nd</sup> edition of the deliverable compared to the initial version are the following:

- New sections 3.3.4 and 4.3.5 have been added;

- Sections 4.3.1 and 4.3.2 have been modified by updating/improving the algorithms.

Updates in other sections were only introduced where necessary and they are negligible.

# 2 Background

IEEE 1687 specifies JTAG as the main off-chip to on-chip interface to the instrument access infrastructure (the 1687 network) and is informally called Internal JTAG (IJTAG). IEEE 1687 includes (1) specifications on the hardware that interfaces the on-chip dedicated monitors, checkers, sensors, etc. collectively called instruments to the chip boundary, (2) a hardware description language called Instrument Connectivity Language (ICL) which describes the instrument's port functions and logical connection to other instruments and to the (chip-level) test access interface (e.g., JTAG test access port (TAP)), and (3) Procedural Description Language (PDL) which describes how an instrument should be operated at its terminals. The idea in introducing ICL and PDL is to provide an adequate and standardized description of the 1687 network, instruments, and instrument access procedures, and to enable ICL and PDL interpreter tools to automate the retargeting of access procedures. Retargeting is the process of translating the PDL commands at the instrument terminals to the higher design levels up to the chip pins, through the provided ICL.

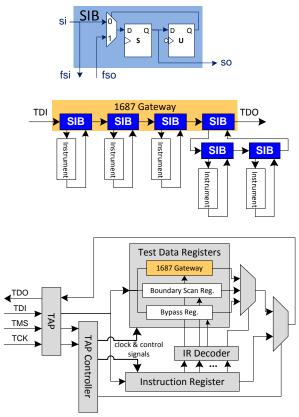

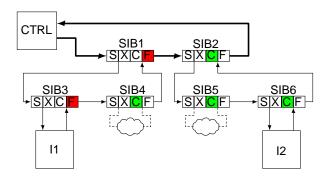

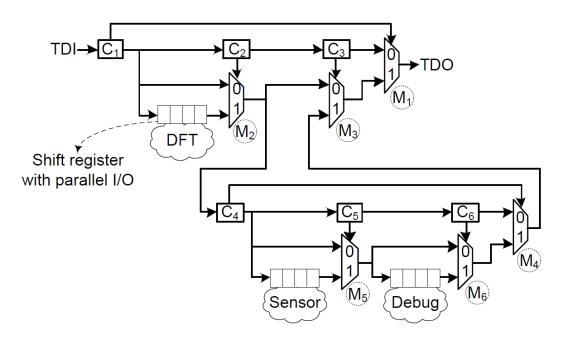

Figure 1 Example SIB, example 1687 network, and how the network is interfaced to the JTAG circuitry

One important feature in the IEEE 1687 specification is the concept of a variable length scan-path which can be implemented through a component called Segment Insertion Bit (SIB). A SIB is a 1-bit shift and update register on the scan-path which can be programmed to insert another segment of IEEE 1687 conform scan-path into the current (active) scan-path—hence the name Segment Insertion Bit. It is possible to build a multitude of different hierarchical 1687 networks for the same set of instruments by using SIBs. Figure 1 shows a possible SIB implementation, a small 1687 network, and an example of how a 1687 network is interfaced to the test access interface (i.e., test access interface in this case). From Figure 1, it can be seen that the on-chip 1687 network is interfaced to the test access interface by using a dedicated Test Data Register (TDR) called Gateway. The Gateway itself is composed of one or more SIBs. The shown network also illustrates the concept of a variable length scan-path in which the first three instruments on the path are on the first hierarchical level and the remaining two instruments are on the second hierarchical level.

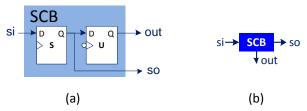

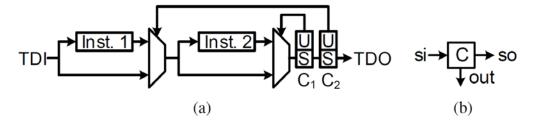

Another programmable component introduced by IEEE 1687 is a *ScanMux* control bit which is used to control the multiplexers on the scan-path. A ScanMux control bit (referred to as SCB in this report) is a one-bit shift-and-update register. Figure 2(a) shows a simple schematic for an SCB, and Figure 2(b) shows the symbol used for SCBs in the rest of this report.

Figure 2: (a) a simplified schematic for an SCB, (b) the symbol for SCB

**ICL:** ICL is not meant to be an exact description of the actual hardware, but a logical description of the instrument access network. For this purpose, ICL introduces a number of building blocks such as *ScanRegister* for describing shift registers, *AccessLink* for describing the interface between the on-chip instrument access network and the test access interface, and so. In the rest of this document, a few more of these building blocks are introduced.

**PDL:** The PDL commands are categorized either as *setup* commands or as *action* commands. Setup commands configure the environment for the action commands, and action commands perform actual operations that make the setup commands take effect. For example, commands such as iTarget, iWrite, iRunLoop, and iRead are setup commands, whereas iPDLLevel and iApply are action commands which are immediately performed. That is, all the reads and writes that are grouped under one iApply are performed together, and the consecutive iApply commands are performed sequentially. This implies that if updates to the network are not to be applied at the same time, they should not be merged under the same iApply group. Moreover, this shows that the PDL code also determines the access schedule.

### 3 Analysis, Design and Optimization of IEEE 1687 Networks

This section discusses aspects of the analysis, the design and optimization of IEEE 1687 networks. After a detailed introduction and an overview of related work the contributions delivered by BASTION participants in this area are described. The first contribution investigates the optimization with respect to the overall access time as well as robustness and hardware overhead of 1687 networks by applying different network topologies. Furthermore, future design challenges and approaches for how to extend 1687 networks for fault management are described. Finally, security and safety aspects in 1687 networks are discussed and represent a new contribution of the 2<sup>nd</sup> edition of this deliverable.

#### 3.1 Introduction

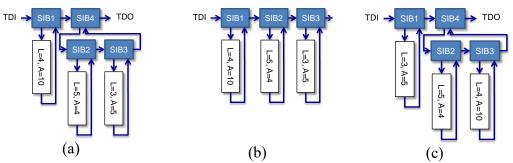

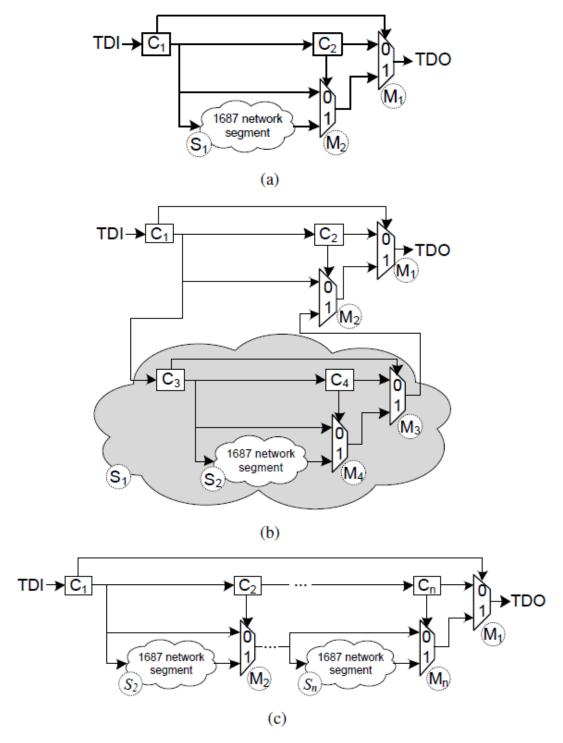

The IEEE Std. 1687 allows creation of dynamically reconfigurable on-chip instrument access networks. The flexibility in such networks brings two types of freedom: (1) the freedom to construct the network in a multitude of different ways, and (2) the freedom to schedule the access to the instruments in a variety of ways according to the given constraints (e.g., resource conflicts and power budget). As an example, consider three instruments with the interface shift-register length (L) of four, five and three flip-flops, which are to be accessed (A) ten, four and five times, respectively. Figure 3 shows three different ways to connect these three instruments as a 1687 network. It can be seen that the network in Figure 3(b) uses less hardware components (i.e., SIBs in this example) compared to the other two networks. Although the instruments are the same, the overall access time (OAT) for the network shown in Figure 3(a) is less than OAT for the networks in Figure 3(b) and Figure 3(c). This can be explained by noting that part of OAT is the time spent on programming the SIB components for every read/write access to the instruments [1]. Therefore, since in the network in Figure 3(a), it is possible to close SIB4 and keep SIB2 and SIB3 off the scan-path when accessing instrument with 10 accesses (which is the largest number of accesses among the three instruments), the time that should otherwise be spent on programming SIB2 and SIB3 is saved.

Figure 3. Three different networks for the same instruments

Moreover, for each of the shown networks in Figure 3, the access to the instruments can be scheduled in a variety of different ways, each way potentially resulting in a different OAT number [2]. The above example shows that there is a need to methods

for design of optimal 1687 networks (in terms of instrument access time, hardware overhead, etc.). Development of such methods, in turn, requires an exact analysis of different trade-offs (e.g., time overhead vs. hardware overhead). In the following sections, we will review the previous work in this regard, and will elaborate on how the BASTION project will enhance the state of the art.

#### 3.2 Related Work

Access time analysis for SIB-based 1687 networks, under sequential and concurrent access schedules, is presented in [1]. Optimized SIB-based network construction is presented in [3], for concurrent and sequential schedules. The work in [2] presents an access time calculation method for general schedules, as well as optimized power- and resource-constrained test scheduling, for SIB-based 1687 networks. In none of these works, it is considered that instruments might be accessed differently under diverse circumstances.

The extension in form of design rules as proposed in [4] for IEEE 1687 standard is aiming at asynchronous interrupt-based in-situ error detection. The scheme targets fault management applications and attempts to minimize the error detection latency as well as the faulty resource localization time. In the BASTION project, enhancements to the work in [4] will be carried out in order to reduce the latency in error detection and localization.

#### 3.3 BASTION Contributions

In this section, the contributions of the BASTION project regarding analysis, design, and optimization of 1687 networks are presented: Section 3.3.1 briefly describes a study performed to compare a number of 1687-compatible networks in terms of overall instrument access time (OAT), hardware overhead, and robustness [5]. Section 3.3.2 describes an example of potential design challenges that should be addressed in design automation for IEEE 1687 network design and PDL retargeting. Section 3.3.3 details how the use of 1687 networks can be extended to fault management. Section 3.3.4 focuses on security and safety aspects in 1687 networks.

#### 3.3.1 Robustness of 1687-Compatible Scan Networks

Embedded instruments might be used in different situations during the life time of a chip, such as for post-silicon validation, debugging, wafer sort, package test, burn-in, printed circuit board (PCB) bring-up, PCB assembly manufacturing test, power-on self-test, and operator-driven in-field test. For each of these situations (referred to as usage scenarios hereafter) it is of interest to access some but not all of the instruments [6]. As an example, a memory built-in-self-test (MBIST) instrument might be accessed (1) during yield learning for a new process to choose the most suitable algorithms, (2) during wafer sort and package test to detect defective devices and perform repair, (3) in the burn-in process to cause activity in the chip and to detect infant mortality [7], [8], (4) during PCB bring-up [9], (5) during PCB assembly manufacturing test [9], and (6) during power-on self-test and operator-driven in-field tests.

Also, the number of accesses to a given instrument typically varies between different scenarios. For example, during yield learning, an embedded memory might be tested several times by running multiple BIST algorithms. Another example is reading out the memory contents for diagnostic purposes [10]. In both examples many accesses might be needed. In contrast, during manufacturing tests, an embedded memory might be tested only by accessing the associated MBIST engine a few times to setup the algorithm, start the BIST, check for its completion, and read the results.

Furthermore, at design time it is (1) difficult to foresee all needed scenarios, and (2) how many times an instrument will be used at each of the scenarios. The number of needed scenarios and the number of accesses might be affected by late design changes, adding/excluding tests, or change of constraints, such as power consumption. Some changes may only be known after manufacturing.

Previous works on network design assume one known scenario where the number of accesses is fixed [3]. However, a 1687 network optimized for one scenario might not be as efficient for another one. And, a network optimized for a fixed number of accesses, might not be optimal if the number of accesses changes. Therefore, we studied [5] the robustness of seven approaches for designing 1687 networks, and we examined their efficiency, in respect to OAT and hardware overhead.

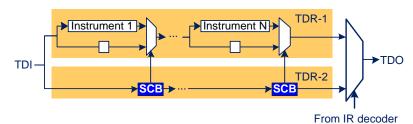

The studied network design approaches are (1) a flat network, (2) a single hierarchical network, and (3) multiple networks, as well as a daisy-chained counterpart for each of those three, namely (4) flat daisy-chain, (5) hierarchical daisy-chain, and (6) multiple daisy-chains. In addition to the six enumerated approaches, we study one more approach in which two separate JTAG test data registers (TDRs) are used for the instrument access network: one for network configuration, and one to access the instruments. This approach will be referred to as "separate control and data TDRs" hereafter.

Since there was a need to OAT calculation methods for performing the comparison among the mentioned network design approaches, we presented in [5] OAT calculation methods for those studied approaches for which such methods were not available from prior work.

Robustness: Ideally, a network should incur zero (or minimal) configuration time overhead (i.e., clock cycles spent on network configuration and the operation of test access interface FSM) regardless of the scenario in which it is used. Therefore, a network can be considered robust against changes in the scenario—namely, changes in number of accesses and changes in the access schedule (for example, change from a concurrent schedule to a sequential schedule)—if such changes do not change the overhead significantly. However, since a change in the number of accesses to instruments changes both instrument data and configuration time overhead, the overhead alone cannot be used as a measure for robustness. That is, it might happen that despite an increase in the overhead (in terms of clock cycles), it becomes negligible compared to the data transferred over the network to the instruments (i.e., instrument data) in the new scenario. Therefore, considering that OAT consists of instrument data and overhead, a network can be said to be robust if the ratio of OAT to instrument data does not change significantly between scenarios. Therefore, we calculate the ratio of OAT to instrument data for each scenario for a given approach, and we consider the standard deviation of the calculated ratios as the metric for robustness of that approach. The smaller the metric value is, the more robust the approach will be.

#### **Experimental results:**

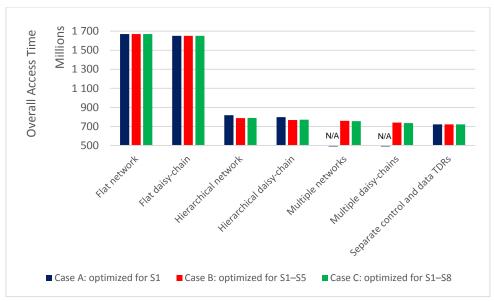

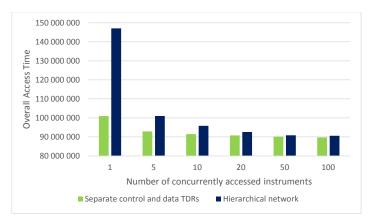

To compare the studied network design approaches, two sets of experiments were performed. In the first set, eight scenarios were considered and it was assumed that a weight is assigned to each scenario by the designer, indicating the relative importance of OAT reduction for that scenario in comparison with other scenarios. For each of the above-mentioned seven approaches, OAT achieved under each scenario was calculated, multiplied by the weight assigned to corresponding scenario, and summed up. This experiment was performed for three cases where (A) only one scenario (out of eight) is known at design time, (B) five out of eight scenarios are known at chip design time, (C) all scenarios are known at design time. The chart in Figure 5 presents the results for the first set of experiments. The second set of experiments studied robustness against change of concurrency in a given scenario. Figure 6 shows the results of this experiment in which for one of the given scenarios, the number of concurrently active instruments is gradually increased from one active instrument to 100 concurrently active instruments.

The experimental results for both sets of experiments showed that the network generated by the "separate control and data TDR" approach results in the least OAT among networks generated by the considered design approaches (see Figure 5), has low hardware overhead (compared with other networks with similar OAT numbers), and is the most robust among the studied approaches. In this approach, SCBs are placed in a TDR separate from the instrument shift-registers' TDR (see Figure 4).

Figure 4. Using separate TDRs for instruments and SCBs

Figure 5. Results for the first set of experiments. The reported numbers are the weighted sum of the individual OAT numbers calculated in test clock cycles for each scenario.

Figure 6. Results for the second set of experiments. Overall access time is reported in number of test clock cycles.

#### 3.3.2 Race on Update Signal

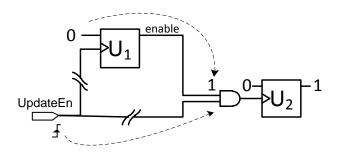

A race hazard is a situation in which the correct operation of a digital circuit becomes dependent on the actual delays that occur on the signal transitions after the chip is being implemented. In this regard, it should be explained that in a hierarchical 1687 network, the control signals such as *ShiftEn*, *UpdateEn*, and *CaptureEn* that are applied to a component at a given hierarchical level, are gated by using an *enable* signal from the parent component—i.e., a component at a hierarchical level closer to the 1687's Gateway (see Figure 1). If as a result of an update, the transition of the *enable* signal reaches a component earlier than the update signal itself, that component might not see the change on the update signal which is gated by the enable signal. As an example, inFigure 7, U1 generates the "enable" signal. Assume that the current input to U1 is '0' and the current output of U1 is '1' (which has propagated to the input of the AND gate). The "UpdateEn" signal has two paths: a path to the clock of U1, and a path to the gating input of the AND gate. If the delays are such that a rising edge in the

UpdateEn signal reaches the AND gate later than the '0' on the U1 input has reached there (as indicated by the dashed arrows), this rising edge will be masked thus blocking the input signal of U2 to the output.

Figure 7. Race between two signals

In this example, the race can be eliminated by adding a delay element (e.g., one that acts on the negative edge of the UpdateEn signal) after the enable signal. In this work, we will investigate if this sort of race on the update signal is automatically addressed by the current tools used for synthesis, static timing analysis, and place and route. If it is not the case, a retargeting tool could prove helpful if it locates where delay elements should be inserted in order to avoid potential races. Moreover, since PDL could be written such that race is avoided by applying successive changes to the hierarchical layers (instead of simultaneous updates), an alternative solution to the problem of race on the update signal, would be that the retargeting tool breaks simultaneous updates (i.e., those in one iApply group) that can cause the such race situation, into multiple consecutive iApply commands.

#### 3.3.3 IEEE 1687 Extensions for Fault Management

It has been shown that IEEE 1687 standard infrastructure can also be successfully and efficiently used or reused later in the field during the product's life cycle. One such application is fault management [4] — the usage that was hardly foreseen by the IJTAG standard development action group. IEEE 1687 standard allows to create an efficient and regular network for continuously handling fault detection information as well as to manage test and system resources as a system-wide background process during the system operation. The IJTAG framework matches especially well the requirements for supporting graceful degradation of the silicon under pressure of aging (which is the main topic of WP1), the problem that has been recently reported by the ITRS among a few most important research challenges. This sub-section describes the way the IEEE 1687 infrastructure can be efficiently extended to support fast emergency signaling for online-fault detection and localization as a background process in a running system. The extension for on-line diagnostics is based on two main components:

- 1. Hierarchy of status flag registers (IJTAG-compliant);

- 2. Asynchronous emergency network (non-IJTAG compliant).

In frames of BASTION we continue the research direction outlined earlier by us in [4] in the direction of error detection latency minimization and faulty resource localization speed acceleration.

#### 3.3.3.1 Introduction to the IEEE 1687 based Fault Management

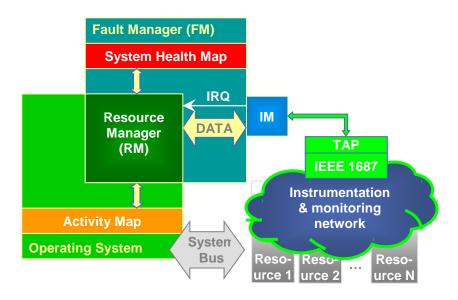

The aging failure resilience framework that we describe is based on fault tolerance and system health monitoring but goes beyond by localizing and classifying faults into different categories that should be handled differently: e.g. transient vs. permanent faults and critical vs. low-priority ones [4]. Independently of their priority, aged blocks with permanent faults are then either fully isolated or marked as reduced-capacity ones. In such a way a system health map is maintained that is used by an operating system (OS) to schedule new tasks. The main benefit of using IEEE 1687 IJTAG infrastructure for in-situ fault management is based on considerable reuse of existing test and debug infrastructure and instrumentation later in the field for the new purpose of resource management.

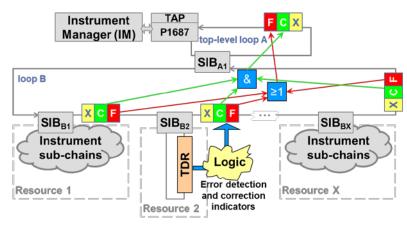

Figure 8. Failure resilient system with IEEE 1687 fault management network

The general concept is depicted in Figure 8. We assume that the fault management framework operates on the same SoC as the target system itself. Its parts - Resource Manager (RM) and Instrument Manager (IM) are closely coupled to the functional part of the system: RM is running on top of OS and exchanges data with IM which can be implemented as software on separate processor core or dedicated hardware. The rest of the SoC has an arbitrary structure but we assume that the target system contains heterogeneous or identical IP cores capable of fully or partially replacing one another, hence providing a room for graceful degradation. More relaxed requirements/scenarios (e.g., analysis on an external processor) are also possible with limited modifications of the basic concept described below.

The actual error detection is taking place in-situ by embedded instruments/monitors. The Diagnostic Instrumentation Network (DIN) should then immediately pass an emergency signal from the monitor to the OS so that the latter could reschedule the failed task immediately to another available resource. After detecting the fault, the failure has to be diagnosed and analyzed in order to update the system health map and isolate the resource in case of permanent fault detection.

The first priority requirements for an effective fault management system are error detection latency, faulty resource localization speed, reliability and scalability of the service infrastructure. They are followed by the possibility of design automation, reuse, and sharing of the IPs and/or instruments. The DIN has to provide unified interfaces to instruments from different vendors as a part of IP cores.

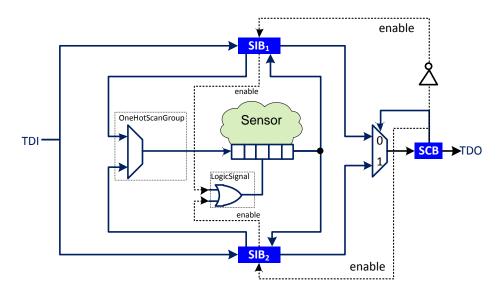

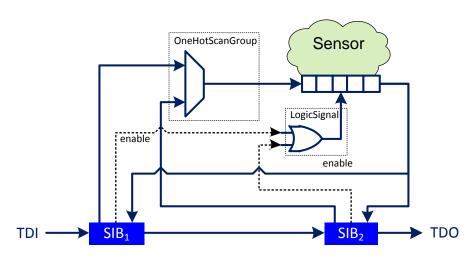

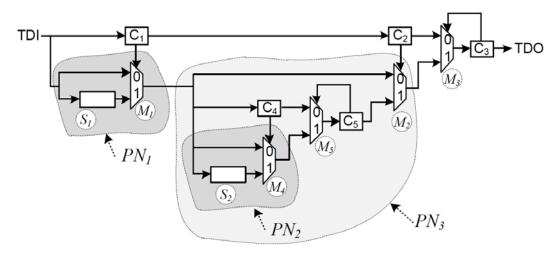

In [4] we proposed a flag-based error reporting system where each block or sub-module is provided with a dedicated flag, whereas all flags are collectively forming a hierarchical error indication and propagation structure tied with IEEE 1687 network. In BASTION, we elaborate and optimize the flag-based asynchronous signaling infrastructure (see Figure 9), elaborate on SIB design, consider DIN behavior in multiple fault scenarios, as well as study conflicting interrupts in the system.

Figure 9. IJTAG network with asynchronous flag-based error reporting and localization system

#### 3.3.3.2 Asynchronous Fault Detection

This subsection details respective requirements (design rules), which enables automatic seamless integration of heterogeneous diagnostic resources into a single homogenous system-wide DIN. As mentioned above, the rules describe two main extensions:

- 1. Hierarchy of status flag registers (IJTAG-compliant);

- 2. Asynchronous emergency network (non-IJTAG compliant).

Thanks to these rules and the IEEE 1687 standard, the DIN can be constructed in a way that allows creation of a single very small controller (instrument manager - IM) that handles all faulty resource localization tasks and instrument control for the whole SoC independently of its size [4].

The main part of our method is to propagate fault indication flags from instruments directly to IJTAG network controller by means of dedicated asynchronous signals. These signals carry information from instruments to higher levels and represent a significant contribution as the original IEEE 1687 standard does not consider such mechanisms at all. Yet, our proposal does not contradict the IEEE 1687 concept but rather appends it.

To be in line with hierarchical network structure with SIBs, asynchronous signals from a lower level of hierarchy are aggregated using logic gates to produce one signal for the higher level of hierarchy (see Figure 9).

There are two status bits and one mask bit for each SIB in the DIN. First status bit F (Fault) indicates the presence of a fault that occurred in an instrument in child segment of the SIB or somewhere further down in the hierarchy. The second status bit C (Correction) shows that the fault was automatically corrected. Mask bit X is used to disable fault detection for the underlying network segment, (e.g. to prevent the instrument from generating "false alarms"). Figure 9 demonstrates an example of such instrumentation network implementation in a many-core SoC.

As described in earlier articles [6], the DIN may have IM which is responsible for controlling the instrumentation network and Resource Manager (RM) which is monitoring the status of instruments [10] and feeding the information to higher levels of system control, like OS scheduler.

#### 3.3.3.3 Extended SIB Design vs. the Standard SIB

The IEEE 1687 standard defines the construction of instrumentation network as a serial scan chain divided into segments and connected together in a hierarchical manner. In such a hierarchical network the segments are connected in host-client (parent-child) manner where child segments must be accessed from parent segment through special blocks or SIBs. These blocks are controllable and allow concatenating the child segment into the scan chain. This allows manipulating the active configuration of the IJTAG network by including and excluding needed segments of the network.

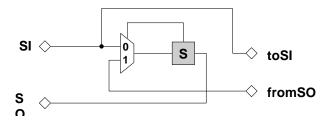

Figure 10. Normal SIB according to IEEE 1687 standard

A *standard SIB* is shown in Figure 10. Standard SIB has a client interface with SI (Serial Input) and SO (Serial Output) ports and a host interface with toSI (to Serial Input) and fromSO (from Serial Output) ports, a scan multiplexer and the SIB register. Depending on the value of SIB register, the scan multiplexer chooses either to:

- (value 0) connect its client signals SI to SO, thus skipping the child segment

- (value 1) connect the output of child segment from SO to SIB's output SO, effectively including child segment into the scan chain

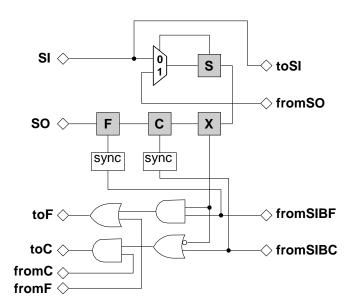

The introduction of asynchronous fault detection requires some modification of the SIB or an add-on module which would accommodate additional fault management features integrated with SIB. These features support additional status bits (F, C and X) as well as propagation of their values to the upper levels of hierarchy.

The registers required to capture the value of Fault, Correction and mask flags can be added to the design of SIB, as well as synchronization circuit that will allow synchronous capture of flag values.

However, there are several possibilities of inserting these registers into SIB. While inserting a register into parent scan chain of the SIB will allow capturing the value of the registers without opening the SIB, it will increase the length of this scan chain. On

the other hand, inserting a register into the child scan chain of the SIB will not lengthen parent scan chain, but it will require opening of the SIB to gain access to the register.

We choose to keep all three registers in the parent scan chain to be able to monitor and control respective network segments as quickly as possible.

Figure 11. Extended SIB with asynchronous fault detection signals

The difference between the normal SIB and the extended SIB is evident when comparing Figure 10 and Figure 11 correspondingly. The extended SIB has 6 additional signals used for asynchronous signal propagation, 4 of which are on the client side:

- **toF**: Fault flag output. It is a result of logic OR operation between the Fault flag of previous SIB in the parent scan chain and Fault flag of child scan chain

- toC: Correction flag output. It is a result of logic AND operation between the Correction flag of previous SIB in the parent scan chain and Correction flag of child scan chain

- **fromF**: Fault flag input from previous SIB in the parent scan chain

- fromC: Correction flag input from previous SIB in the parent scan chain

Additional 2 signals are on the host side:

- **fromSIBF**: Fault flag input from child scan chain. It can be masked with value 0 in Mask bit

- **fromSIBC**: Correction flag input from child scan chain. It can be masked with value 0 in Mask bit

The extended SIB contains 3 additional registers (F, C, X) which are always included in the scan chain of SIB:

- **F bit**: it captures its value from synchronized Fault signal of child scan chain, which can be then shifted out to IJTAG network manager

- **C bit**: it captures its value from synchronized Correction signal of child scan chain, which can be then shifted out to IJTAG network manager

• **X bit**: it is updated by IJTAG network manager to mask Fault and Correction signals from child scan chain of this SIB so that they don't affect the operation of asynchronous fault detection system

Altogether, this additional hardware allows to connect the Fault and Correction signals hierarchically between networks segments (signals come from child segment to parent segment) and in daisy-chain fashion inside one network segment, i.e. similarly to the original IEEE 1687 routing concept.

#### 3.3.3.4 Fault Localization and Diagnosis

Here, we briefly describe the way the IEEE 1687 DIN detects and localizes a faulty resource in event of fault detection. Detailed examples and scenarios will be elaborated in frames of WP3.

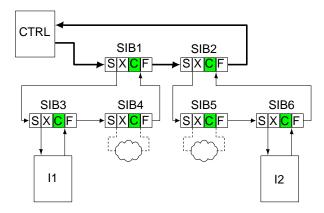

Figure 12. Example of IJTAG instrumentation network with asynchronous fault detection

The end point of the faulty resource localization is the identification of the particular instrument that detected the fault. An example DIN in its normal state is shown in Figure 12. The active scan chain is shown in bold while the inactive parts are shown in thin lines. Let's assume that the fault is detected by instrument II. The fault is not automatically corrected and thus needs to be taken care of by the IM. The initial state of the DIN is with all SIBs closed.

At the time of fault detection, the instrument sets its Fault flag and clears Correction flag. These changes are propagated asynchronously to *SIB3* and then to *SIB1*, although *SIB4* is still in normal state (see Figure 13).

Figure 13. Detection of a single fault by instrument I1

When asynchronous fault detection signals reach the IM, the latter responds by performing localization actions, i.e. by opening *SIB1* and *SIB3* accordingly to corresponding indication FCX flag register. When the localization procedure is finished; the IM recognizes that the fault is situated in the child segment of *SIB3* which consists only of instrument *I1*. Then the IM will open *SIB3* and read out *I1* status. At this point the fault is localized and the control is given over to the FM for fine-grade diagnosis, fault classification and statistics data update.

Further research on fault localization scenarios is being performed in frames of WP3.

#### 3.3.3.5 Interruption of Ongoing Access in Event of Fault

The normal work of IJTAG instrument network consists of read and write accesses to instruments, opening and closing the SIBs which are the results of normal requests from higher levels of the system (like OS). Since the IJTAG network can be constructed hierarchically to optimize access times, it may take considerable time to finish ongoing access and switch to another request.

Since asynchronous fault detection is designed to be as quick as possible to detect and find the source of fault, its speed would be useless if corresponding accesses to faulty re-source were delayed until current normal access is completely finished. Therefore, it is reasonable for IJTAG network with asynchronous fault detection to interrupt ongoing access and service faulty resource localization as soon as possible.

The localization of faulty resource would probably require modifying the configuration of IJTAG network, i.e. closing some SIBs and opening other SIBs. Hence, the current status of IJTAG network must be considered and an optimal modification, i.e. action that leads to quickest access to faulty resource, should be taken.

We foresee two possible solutions that can provide fastest reconfiguration of the IJTAG network in different situations:

- Dynamic retargeting

- Reset of IJTAG instrumentation network

Both procedures will be considered in our ongoing research in frames of WP3.

#### 3.3.3.6 Multiple Fault Scenario

During the lifetime of the system it may happen that multiple faults occur at the same time, or at least, their localization times could overlap. In this case, it is important to make sure that fault management architecture would allow detecting both of them and reacting accordingly.

According to our initial observations the overall status of the asynchronous fault detection scheme remains adequate in case of several faults occurring at the same time or one fault occurs when another is already being localized.

This case will also will be considered in our ongoing research in frames of WP3.

#### 3.3.4 Safety and Security Aspects of IEEE 1687 Networks

The reuse of existing chip internal test instruments on board-level is one method to improve the overall system reliability and allows the screening for potential aging effects. The IEEE 1687 standard simplifies the access and usage of embedded test instruments by describing their integration and test features by the standardized descriptions languages "Instrument Connectivity Language" (ICL) and "Procedural Description Language" (PDL). Even if the usage of chip-level test instruments is beneficial for the quality and diagnosis of board-level tests, this reuse also leads to new safety and security issues.

Not all chip-level test instruments and debug features, that have been initially implemented for the chip-level production test, are intended to be reused on board-level by the customer. Inappropriate usage of these features might cause malfunctions or even damage the device. From the safety point of view there are three different classes of test and debug instruments:

- 1. Instruments that can be used on board-level without any risk

- 2. Instruments that are intended to be reused in the system, but require special care

- 3. Test and debug features not intend to be used in the system

The first category of safe to use instruments contains all kind of health monitors and sensors that allow only the non-intrusive reading of data. As long as the chip-internal parameters are only read and the data cannot be modified, the usage of these instruments can be considered as safe and the access is allowed at any time.

The second class contains active test instruments that can disturb the system functionality when they are triggered. Typical examples are all kind of built-in self-test (BIST) engines. In most cases BIST circuits cannot be used while the application is running as they are modifying chip-internal data. BIST operations are usually performed at the start-up or shut-down of the device. An execution while the device is active is only possible, if the component to be tested is not functionally used at this moment. In addition, the BIST must not disturb the surrounding system. This usually requires some kind of isolation. After finishing the BIST the initial functional state needs to be restored. As a consequence, the user starting a BIST operation needs to be very aware of the system state and the potential impact of the BIST execution. In addition, there are usually other constraints when starting a BIST or using other active test instruments. For instance, running multiple BISTs at the same time might lead to power issues disturbing the test execution or even damaging the device.

The third groups of test and debug instruments contains features not intended for the customer usage. For the production test it is often possible to adjust chip internal voltages, timings and frequencies through the IJTAG network. These features should be usually hidden from the customer to prevent misuse affecting the device stability.

Giving an example for these three different instrument classes e.g. for an embedded memory, it is always safe to read out some ECC statistics monitoring the data corrections. Using an implemented MBIST to test the memory in detail might be

allowed from the board-level, but special care is required when and how to execute the test. Access to memory internal test features e.g. modifying memory internal timings is usually restricted for the customer.

Even if the user intends to access only the public test instruments in the appropriate way, there is a certain risk that accidently a wrong IJATG sequence might lead to a critical system operation. Especially when using the IJTAG network not only for dedicated tests, but also for online monitoring this is a risk to be considered.

Allowing the board-level access to the chip-internal IJTAG network causes not only safety issues as described above, but also leads to security risks. Some components accessible through the IJTAG network might contain or give access to confidential information that needs to be protected from unauthorized access. In addition, the IJTAG network must not enable prohibited circuit manipulations e.g. unauthorized chip tuning. Therefore, it is desirable to hide certain IJTAG functionality and to restrict the access.

The traditional way of accessing chip-internal test registers before the introduction of IJTAG was to use multiple so-called "private instructions" of the IEEE 1149.1TAP controller. The Boundary Scan Description Language (BSDL) specified in the IEEE 1149.1 standard supports these instructions. The content of the user-defined test registers is not described in the BSDL file, only the instruction opcodes of the private instructions are mentioned. This information is needed for board-level Boundary Scan pattern generation tools to prevent the usage of these instructions. This means in IEEE 1149.1 BSDL there is a clear separation of public Boundary Scan instructions and restricted private instructions accessing chip internal test data registers. In the ICL introduced with IEEE 1687 there is no methodology foreseen to distinguish between public and restricted parts of the IJTAG network.

Of course the description of private instructions in the BSDL does not prevent the access to the related test data registers. Even if it is clear that it is not a good idea to access these registers without knowing their functionality, this would not hinder attackers to do so. For this reason, the chip internal test data registers are often secured to prevent an accidental or attacking access. Typical measures to protect the activation of certain test modes are additional passwords needed for the access. In many cases these access restrictions are combined with electrical measures like under- or over-voltage detection at some pins at some time. While the test mode can be easily entered during production test of the chip, the activation on the functional board would be restricted.

There are few publications dealing with the safety and security aspect of the IEEE 1687 IJTAG network. In [11] so-called Locking Segment Insertion Bits (LSIB) are introduced replacing standard IEEE 1687 SIBs by an enhanced version with an additional key input required to "unlock" the SIB. The branch of the IJATG network controlled by the LSIB can be entered only when the condition of the key input is met. This method is extended with so-called trap bits intended to significantly increase the effort for attackers to unlock the LSIBs.

Another proposed solution to restrict the access to IJTAG test instruments is a sequence filter placed between the TAP controller and the IJTAG network [12]. The sequence filter is a Finite State Machine (FSM) operated using the JTAG signals TDI, capture, shift and update as input. An "allow" signal is only asserted for allowed input sequences. In case of a forbidden access sequence the "allow" output becomes 0 and the FSM enters a trap state. The "allow" signal is used to gate the update signal of the IJTAG network preventing any changes in the update registers when not allowed.

In [11] it is assumed that the attacker does not have any initial knowledge about the architecture of the implemented IJTAG network. When allowing an IJTAG based reuse of chip-level test instruments on board-level, the user would require at least a partial ICL description containing the structural information how to access the public instruments. On the other hand, this partial ICL description could be at least a starting point for an attacker. If the public and restricted test instruments would be mixed on various hierarchy levels of the IJTAG network, it would be difficult to hide the restricted parts in the ICL while still providing a valid file that can be understood by tools for an automated pattern retargeting. The main drawback of the method proposed in [12] is the need to recreate the sequence filter hardware each time when the IJTAG network or the allowed access sequences are changed. As both methods are not yet supported by commercial EDA tools an alternative approach has been evaluated in the next section.

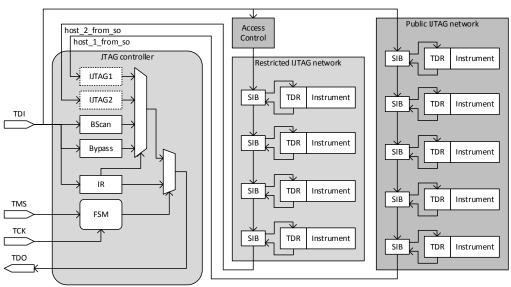

The basic idea of the proposed access protection is the separation of the IJTAG network into two parts. The first part of the IJTAG network contains the test instruments to be reused by the customer and is directly accessible by one JTAG instruction. The restricted functions to be hidden from the public are grouped together in a completely independent IJTAG network accessible by another JTAG instruction (see Figure 14). The restricted IJTAG network can be secured by standard measures as done for normal private JTAG instructions.

Figure 14. Overview of the proposed IJTAG network architecture

The overall design flow using the commercial IJTAG tool "Tessent IJTAG" [13] and the compatibility with the IEEE 1687 standard have been evaluated for a small test case design. The test case is based on a small processor design with four identical CPU cores. Each CPU core is equipped with a LBIST solution allowing a self-test of the digital logic. The LBIST initialization is done by several setup registers. The tool generated RTL code of the LBIST controller contains already an IJTAG interface and several SIBs grouping these configuration registers. The required ICL and PDL files describing the LBIST controller implementation and functionality are automatically generated together with RTL code by the Tessent LBIST tool. The CPU cores are implemented supporting several different scan test modes. The related scan configuration signals are only routed to the core boundary for a later integration by the

IJTAG tool. The test case design contains some more test modes on the top-level that also need to be considered for the IJTAG network generation.

The insertion of the IJTAG network has been done on the gate-level netlist using the "Tessent IJTAG" tool. The existing ICL files of the LBIST controller have been read together with some manually written ICL files describing other test functionality e.g., test clock multiplexers required for the scan based delay test. For the core-level scan configuration pins IJTAG attributes have been defined directly in the tool to trigger their integration into the IJTAG network. In a first step the tool has been free to build an optimized IJTAG network directly connected to a JTAG controller which has been also generated by the tool. The resulting design is used as reference implementation.

In the second phase the IJTAG network specification proposed by the tool has been manually edited to enforce a structure as shown in Figure 14. For the test case it is assumed that the test instruments of two CPU cores should be available for the user, while the test features of the other two CPU cores should be hidden and placed in the separate ICL network. To do so, the proposed IJTAG network specification of the first step has been duplicated using a copy and paste feature of the tool. Afterwards the IJTAG components of the two CPU cores that should be hidden have been removed from the first IJTAG network specification. In the specification of the second IJTAG network only the components of the two restricted cores have been kept. Due to the initial duplication of the IJTAG specification afterwards some component names have been made unique e.g., by simply adding the suffix "\_1" and "\_2" for the first and second IJTAG network. Based on this specification the tool has automatically created and integrated the intended IJTAG architecture into the test case design.

The automatically generated top-level ICL file contains the complete description of both IJTAG networks and their connection to the JTAG controller. Before providing the ICL file to the customer the restricted components need to be removed. For the test case design this has been done simply by editing the file. For more complex designs this could be done by some scripts, especially when the components to be removed have unique naming extensions as mentioned above. There is one part in the remaining ICL file that needs to be patched. The output from the restricted IJTAG network, which has now been removed in the ICL description, can no longer be used as input signal going into the TAP controller (see also Figure 14). To have a legal ICL file the original connection has been replaced by a constant X-value as shown in Figure 15. Of course the original (red) line could have been removed to hide traces to the removed ICL components.

```

Instance chip_tap_main_inst Of

chip_tap_main {

InputPort host_1_from_so = chip_sib_sril_inst.ijtag_so;

// Patch replacing the original connection from hidden IJTAG by constant X

// InputPort host_2_from_so = chip_sib_sri2_inst.ijtag_so;

InputPort host_2_from_so = 1'bx;

InputPort tck = tck;

InputPort tdi = tdi;

...

```

Figure 15. Required change in generated ICL file disconnecting the output of the protected IJTAG network

After the deletion of the restricted components there are only very few traces remaining in the ICL description indicating the hidden second IJTAG network. Of

course, the TAP controller description still contains the private instruction accessing the hidden IJTAG network, but based on the patch of Figure 15 it is no longer visible what kind of network and data can be accessed. Only the names used for the private JTAG instruction and the related scan interface indicate the existence of a second IJTAG network (see Figure 16), but these names could be easily changed.

```

Module chip_tap_main {

...

ScanInterface host_ijtag_2 {

Port host_2_from_so;

Port host_2_to_sel;

}

...

Enum instruction_opcodes {

BYPASS = 4'b1111;

...

HOSTIJTAG_1 = 4'b0111;

HOSTIJTAG_2 = 4'b1000;

}

...

LogicSignal host_2_to_sel_int {

instruction == HOSTIJTAG_2;

}

...

```

Figure 16. Locations in generated ICL indicating the existence of the protected IJTAG network

After the integration of the split IJTAG network into the design the structure has been verified by using the automated test pattern retargeting flow and simulating the resulting patterns. At first the complete ICL description has been used to retarget the core-level LBIST execution for all four CPU cores on the top-level as it could be done during the production test. The IJTAG tool is able to generate the appropriate JTAG sequence to start and evaluate all BISTs making use of both IJTAG networks and the two related JTAG instructions. The generated test patterns have been simulated without any mismatches.

Afterwards the customer application use case accessing only the two "public" LBIST instances based on the reduced ICL description has been verified. Also this pattern retargeting step and the following patter simulation have been performed without any issues

From the design flow and tooling point of view the proposed separation of the overall IJTAG network into a public and restricted part can easily done using today's available EDA tools. Only the removal of the hidden parts from the overall ICL description requires some manual editing or simple scripting. The proposed solution has basically no impact on the IJTAG network area when not considering the special hardware for the protection of the restricted JTAG instruction. The area of this protection hardware depends on the protection mechanism, but it is independent from the size of the protected IJTAG network as the complete private JTAG instruction is secured.

The split of the IJTAG network into two parts can have some impact on the test time. Instead of reconfiguring one SIB it is required to change the JTAG instruction to access the different IJTAG network parts. The test time increase is highly design

specific and depends on the required interaction between the two network branches. Assuming that both IJTAG networks themselves are optimized for performance, the overall test time increase can be considered as low as long as there is only limited interaction required between the two network parts. For the analyzed test case the split of the IJTAG network into two parts resulted in 268 additional test cycles compared to the reference implementation for a scenario of configuring and executing two different LBIST runs for each of the four CPU cores. This runtime increase is negligible compared to the overall test execution time. Of course this number is not really representative as it highly depends on the used instruments and access scenarios.

#### 3.4 Summary

In this section BASTION contributions in the field of analysis and optimization of different 1687 network topologies with respect to OAT and robustness are discussed. It has been shown that the overall access time varies significantly depending on the applied topology while applying different application scenarios. Next the impact of race hazards in 1687 networks has been investigated. Furthermore, this section provides a discussion how 1687 networks could be extended in order to efficiently provide fault management capabilities such as emergency signaling for online-fault detection or the fault diagnosis capabilities during runtime. Finally, safety and security aspects in 1687 networks are discussed and an application example is described.

#### 4 Verification and Validation of IEEE 1687 Networks

This section provides an overview of BASTION contributions in the area of verification and validation of IEEE 1687 networks. First, the topic is introduced and the state-of-the-art is discussed. Next the modelling of IEEE 1687 networks for the verification and validation is described in detail. In the next part of the section specific aspects of the verification and the validation of 1687 networks are discussed and their application are discussed, such as ICL compliance, smarter and optimal retargeting as well as the co-verification of ICL and PDL. Finally a new retargeting approach is described which guarantees minimal access time for a set of re-targeted PDL-instructions.

#### 4.1 Introduction

A scan network typically consists of a multiple scan segments (also referred as test data registers – TDRs or scan registers) where each TDR is used to communicate with one or more embedded instruments. In the most cases, scan segments are not directly connected with each other. Instead of this, a typical scan network implements some kind of multiplexing logic that enables selection of only part of the segments at a time. Complex reconfigurable scan architectures capable for accommodation of hundreds of instruments normally include multiple levels of multiplexing logic that results in a large variety of different possible network configurations. The particular configuration is determined by the current state of multiplexers that are controlled via internal control signals. A control signal in its turn may be defined as a result of a logic operation on current state of scan segments of the network. Within a hierarchical scannetwork, establishing of particular configuration turn out to be a complicated procedure because some of control signals may depend on configuration of scan segments located in different levels of hierarchy. As a consequence, the resulting scannetwork may have very complex structure which verification and validation is problematic.

A single scan segment of the network normally consists of two parts: one is used for scanning through the test data during the shift operation (shift part), while the second part (update part) holds the previously scanned data (similar to data registers defined in IEEE 1149.1 standard). Two scan segments can either be directly connected into one scan-path or a multiplexer can be used to allow individual access to one of the segments. A single scan configuration defines the state of all multiplexers controlling the concatenation of scan-segments. There is also exists a default scan configuration that determines the initial state of scan-network after reset. An active scan-path is a number of scan-segments consecutively concatenated together by current scan configuration, starting from primary scan input (SI) and ending at primary scan output (SO). The standard enforces that the active scan-path should always be determinable and should not contain loops.

The access to the scan network (reading or writing a particular TDR) comprises of the following stages: (1) setting up the corresponded scan configuration that will place the scan segment of interest into the active scan-path and (2) performing capture-shift-update operation to carry out data exchange with this scan-register. The first step may

require sequence of capture-shift-update operations in case if inclusion of scan register into active scan path demands to change values of number of internal control. The overall performance of the target network is determined by the average number of test clocks needed to execute read or write operation on the network's scan registers.

#### 4.2 Related Work

Efficient verification and optimization of reconfigurable IEEE 1687 networks is one of the key necessities to enable broad application of IEEE 1687. State-of-the-art approaches offer solutions to solve verification and retargeting challenges. In [14] the authors proposed a first approach to model 1687 networks in order to proof specific properties of the network, for example reachability of specific instruments, and to retarget PDL commands. In [15] the authors extend the earlier proposed method by pseudo-Boolean optimization in order to minimize the number of scan access operations and hence the time to perform PDL commands on the 1687 network.

#### 4.3 BASTION Contributions

In this section, the contributions of the BASTION project regarding verification and validation of IEEE 1687 networks are presented: Section 4.3.1 presents an approach to model IEEE 1687 networks for verification and validation. The following section proposes a detailed concept for the ICL compliance and Silicon validation. The Sections 4.3.3 and 4.3.4 discuss aspects of smarter retargeting in IEEE 1687 networks and challenges on the co-verification of ICL and PDL, respectively. Finally Section 4.3.5 presents a novel approach for optimal retargeting in generalized IEEE 1687 networks.

# 4.3.1 Modeling of IEEE 1687 Networks for Verification and Validation

In order to effectively represent complex scan structures as well as to discard implementation-specific details not needed for verification and validation tasks we describe IEEE 1687 networks using formal graph-based model. For that, the source description of scan network (in ICL language) has to be converted to abstract graph model by using special algorithm described below. This model is thereafter used to carry out verification and validation tasks. In the following paragraphs the description of a graph model of IEEE1687 networks is presented.

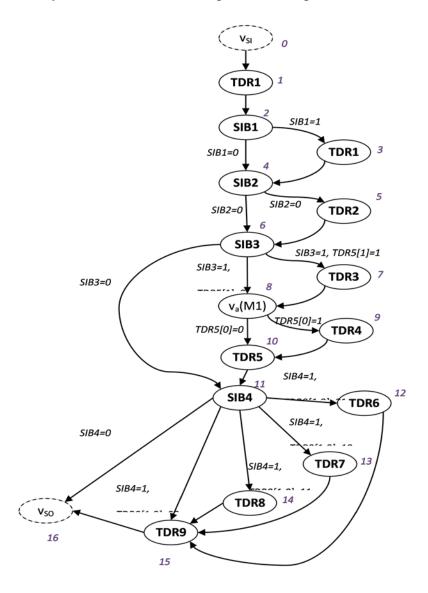

We model the structure of a scan network with a partially ordered directed acyclic graph G = (V, E), where V is the set of vertices and E is the set of edges. The set of vertices V consists of scan segment nodes  $V_S$ , auxiliary nodes  $V_A$  and two special nodes  $v_{SI}$  and  $v_{SO}$ . The set  $V_S$  embraces all scan cells in the network, while elements of  $V_S$  are addressable objects of the scan chain such as scan registers or SIB registers consisting of one or many scan cells each. Essentially every node  $v_i \in V_S$  has different weight  $w_i$  equal to the number of scan cells in that node. Auxiliary nodes  $V_A$  are used to model converging/fanout points between two adjacent multiplexers (e.g. node 8 in Figure 19). The weight of any auxiliary node  $v_a \in V_A$  is zero. In addition, each graph contains two special auxiliary nodes  $v_{SI}$  and  $v_{SO}$  that denote primary scan input SI and primary scan output SO.

The set of edges  $E \subseteq V \times V$  represents connections between scan network elements such that an edge  $e = (v_i, v_j) \in E$  if and only if the two elements corresponding to  $v_i, v_j \in V$  are either directly connected together or can be concatenated through a multiplexer to form a single segment of a scan-path. If a node has more than one successor or in other words subsequent elements, each outgoing edge  $e_k$  is labeled with a set of activation condition  $C_k$ , which also corresponds to the select signal sel(v) of the corresponding scan segment, which in its turn is issued in agreement with the current state of the corresponding multiplexer. A particular outgoing edge  $e_k$  is activated in the current state of the network if and only if each condition  $c_l \in C_k$  is satisfied.

A scan path in G is defined as a directed path from the primary scan-in node  $v_{SI}$  through zero or more directly connected nodes  $v_i \in V$ , to the primary scan-out node  $v_{SO}$ . A graph node  $v \in V_S$  is defined active if and only if the select signal of the corresponding scan segment is asserted: sel(v) = 1. Otherwise the node is inactive, sel(v) = 0. An active scan path is a scan path in G that contains only active nodes.

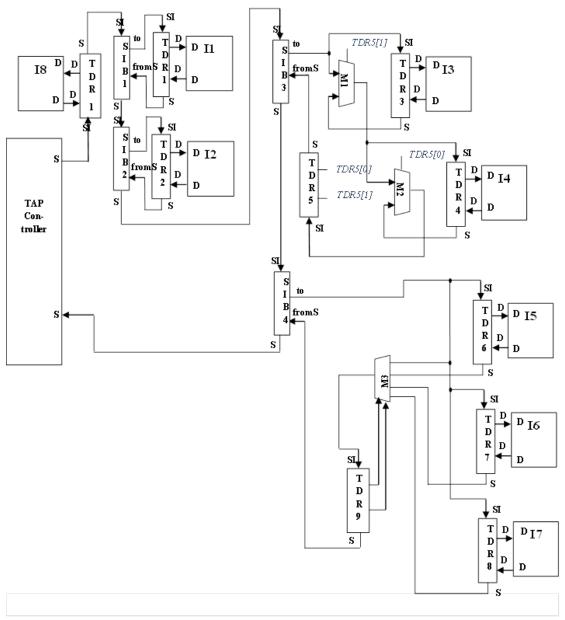

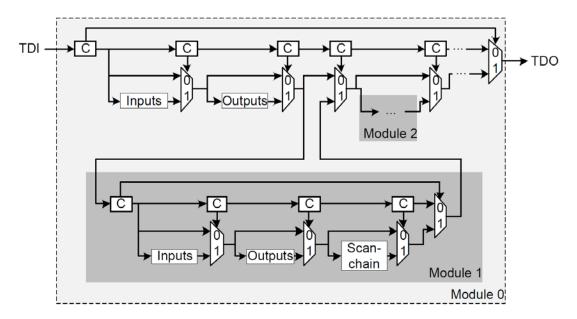

An example scan network and the resulting graph are shown in Figure 17 and Figure 19 correspondingly. They illustrate the main ideas of constructing the graph from a scan network. Scan registers are shown as rectangles in Figure 17 and labelled as TDR or SIB. SIB is a special kind of scan register that contains an integrated multiplexer. Standalone multiplexers are shown as trapezoids labeled with M.

Figure 17. Example scan-network with SIBs and scan multiplexers

```

Module sib {

ScanInPort SI;

ScanInPort fromSO;

ScanOutPort SO { Source Mux; }

ScanOutPort toSl { Source SR; }

ScanRegister SR { ScanInSource SI; CaptureSource SR; ResetValue 1'b0; }

ScanMux Mux SelectBy SR { 1'b0: SR;

1'b1: fromSO; }

}

Module tdr {

ScanInPort SI;

ScanOutPort SO { Source SR[0]}

ScanRegister SR[L:0] { ScanInSource SI; CaptureSource DI; ResetValue 1'b0; }

}

Module top {

ScanInPort SI;

ScanOutPort SO { Source SIB4.SO }

Instance TDR10 of tdr { InputPort SI = SI; InputPort DI = I8.DO; }

Instance TDR1 of tdr { InputPort SI = SIB1.toSI; InputPort DI = I1.DO; }

Instance TDR2 of tdr { InputPort SI = SIB2.toSI; InputPort DI = I2.DO; }

Instance TDR3 of tdr { InputPort SI = SIB3.toSI; InputPort DI = I3.DO; }

Instance TDR4 of tdr { InputPort SI = M1; InputPort DI = I4.DO; }

Instance TDR6 of tdr { InputPort SI = SIB4.toSI; InputPort DI = I5.DO; }

Instance TDR7 of tdr { InputPort SI = SIB4.toSI; InputPort DI = I6.DO; }

Instance TDR8 of tdr { InputPort SI = SIB4.toSI; InputPort DI = I7.DO; }

Instance SIB1 of sib { InputPort SI = TDR10.SO; InputPort fromSO = TDR1.SO; }

Instance SIB2 of sib { InputPort SI = SIB1.SO; InputPort fromSO = TDR2.SO; }

Instance SIB3 of sib { InputPort SI = SIB2.SO; InputPort fromSO = TDR5[0]; }

Instance SIB4 of sib { InputPort SI = SIB3.SO; InputPort fromSO = TDR9[0]; }

ScanMux M1 SelectBy TDR5[1] {1'b0 : SIB3.toSI; 1'b1: TDR3.SO; }

ScanMux M2 SelectBy TDR5[0] {1'b0 :M1; 1'b1: TDR4.SO; }

ScanMux M3 SelectBy TDR9[1:0] { 2'b00 :SIB4.toSI;

2'b01: TDR6.SO;

2'b10: TDR7.SO;

2'b11: TDR8.SO; }

Instance I1 of Instrument {InputPort DI = TDR1.DO; }

Instance I2 of Instrument {InputPort DI = TDR2.DO; }

Instance I3 of Instrument {InputPort DI = TDR3.DO; }

Instance I4 of Instrument {InputPort DI = TDR4.DO; }

Instance I5 of Instrument {InputPort DI = TDR6.DO: }

Instance I6 of Instrument {InputPort DI = TDR7.DO; }

Instance I7 of Instrument {InputPort DI = TDR8.DO; }

Instance I8 of Instrument {InputPort DI = TDR10.DO; }

ScanRegister TDR5[1:0] {ScanInSource M2; CaptureSource 2'b00; ResetValue 2'b00; }

ScanRegister TDR9[1:0] {ScanInSource M3; CaptureSource 2'b00; ResetValue 2'b00; }

}

```

Figure 18. Formal description of example scan-network in IEEE1687 ICL language The corresponded ICL description of this scan network is presented in Figure 18. To make our example simpler we intentionally removed some of ICL constructs that are

required by the standard but are not directly related to the description of example scan network structure.

The structure of the resulting graph in Figure 19 directly corresponds to the structure of the initial scan network. The nodes  $v_i \in V_S$  in the graph are labeled in accordance with the scan register labels (SIB or TDR in Figure 17). Auxiliary nodes  $v_a \in V_A$  are labeled by the name of the corresponded multiplexer to which the signals from the

Figure 19. Graph representation of example scan-network

preceding nodes are connected. Multiplexers (including those inside the SIBs) define edges  $e_i$  of the graph and corresponding sets of activation conditions  $C_i$ . In case of SIBs, there are exactly two successors and edges with complementary activation conditions defined by a one-bit shift register inside the SIB. In case of multiplexers, the number of outgoing edges is defined by the multiplexer width. The activation conditions, in this case, could be any arbitrary collection of data bits of any scan register (depending on the scan network design).

It is important to mention that nodes in graph are partially ordered to improve the efficiency of the graph traversal algorithm. The order of edges is implied by the topological ordering of nodes in the graph. In the graphical representation the leftmost successor of a node always has highest rank than the ranks of other successor nodes.

In the context of scan-network, the ordering is related to the fact that scan multiplexers usually contain one or more register loops and one empty (direct) path. Thus the empty path is always placed first and shown as the leftmost edge in the graph. In rare occasions all branches of a multiplexer could be connected to a scan register (not a typical configuration of an IEEE1687 scan-path). Then either no edge is getting a special priority or the edge leading to the node with lowest weight (shortest register) is put first. The sorting helps to identify the shortest active scan path in the graph for each scan segment and, hence, to speed up the validation algorithms. Graph sorting is also the main differentiator of our approach compared to the one reported in [5].

The second important aspect is the way of introducing auxiliary nodes. Such nodes are needed to mark sections in the graph where two or more adjacent multiplexers are serially connected. In order to be able to distinguish them in the graph, an empty (zero-weight) auxiliary node is added at every such connecting point. In Figure 17, multiplexers M1 and M2 illustrate this case. Both multiplexers are controlled from TDR5 (by two separate bits). In order to reflect the structural composition of the scan network (two multiplexers are actually two consequent components on the scan path, and not a single cluster based on larger multiplexer), an empty auxiliary node 8 is inserted (see Figure 19).

Next we will discuss the algorithm, shown in Figure 21, for construction of graph model out of scan-network description. As the source for graph construction we use a description of scan-network in ICL format (part of IEEE1687 standard) which is at first being preprocessed (flattened) to obtain a set of atomic elements of scan-network:

$SN = SR \cup SM \cup SO$ . Here, SR is a set of scan registers (correspond to ScanRegister statement in ICL description), SM is a set of multiplexers (correspond to ScanMux in ICL) and SO denotes primary output.