FP7-ICT-2013-11-619871

#### **BASTION**

Board and SoC Test Instrumentation for Ageing and No Failure Found

**Instrument: Collaborative Project**

Thematic Priority: Information and Communication Technologies

# Reuse adaptation, and integration of embedded instruments at the board level test environment (Deliverable D4.3)

Due date of deliverable: April 30, 2017 Ready for submission date: June 26, 2017

Start date of project: January 1, 2014 Duration: 40 months

Organisation name of lead contractor for this deliverable: Testonica Lab

Revision 1.0

| Proj | Project co-funded by the European Commission within the Seventh Framework Programme (2014-2017) |   |  |

|------|-------------------------------------------------------------------------------------------------|---|--|

|      | Dissemination Level                                                                             |   |  |

| PU   | Public                                                                                          | × |  |

| PP   | Restricted to other programme participants (including the Commission Services)                  |   |  |

| RE   | Restricted to a group specified by the consortium (including the Commission Services)           |   |  |

| CO   | Confidential, only for members of the consortium (including the Commission Services)            |   |  |

#### **Notices**

For information, please contact Artur Jutman, e-mail: artur@testonica.com

This document is intended to fulfil the contractual obligations of the BASTION project concerning deliverable D4.3 described in contract 619871.

© Copyright BASTION 2017. All rights reserved.

#### **Table of Revisions**

| Version | Date           | <b>Description</b> and | Author           | Affected        |

|---------|----------------|------------------------|------------------|-----------------|

|         |                | reason                 |                  | sections        |

| 0.1     | March 24, 2017 | Structure created      | A. Jutman        | All             |

| 0.2     | April 4, 2017  | Section 6 added        | M. Sonza Reorda  | Mainly          |

|         |                |                        |                  | Section 6, plus |

|         |                |                        |                  | minor changes   |

|         |                |                        |                  | elsewhere       |

| 0.3     | April 11, 2017 | Section 2 added        | H. Ebrahmi, H.G. | Section 2 &     |

|         |                |                        | Kerkhoff         | references      |

| 0.4     | April 25, 2017 | Section 5 added        | I. Aleksejev     | Section 5       |

| 0.4a    | April 26, 2017 | Section 7 added        | I. Aleksejev     | Section 7       |

| 0.5     | April 28, 2017 | Section 4 added        | E. Larsson       | Section 4       |

| 0.6     | May 24, 2017   | Section 3 added        | J. Raik          | Section 3       |

| 0.7     | May 31, 2017   | Integration of all     | A. Jutman        | All             |

|         |                | contributions          |                  |                 |

|         |                | together               |                  |                 |

| 0.8     | June 8-9, 2017 | Correcting             | A. Jutman        | All             |

|         |                | references and         |                  |                 |

|         |                | numbering              |                  |                 |

| 0.9     | June 22, 2017  | Writing                | A. Jutman        | Section 1 and   |

|         |                | Introduction and       |                  | Section 8       |

|         |                | Conclusions            |                  |                 |

| 1.0     | June 26, 2017  | Final polishing        | A. Jutman        | All             |

|         |                | and preparing for      |                  |                 |

|         |                | submission             |                  |                 |

# **Author, Beneficiary**

- R. Cantoro, E. Sanchez, M. Sonza Reorda, Politecnico di Torino

- I. Aleksejev, S. Odintsov, A. Jutman, S. Devadze, Testonica Lab

- J. Raik, TU Tallinn

- H. G. Kerkhoff, H. Ebrahimi, University of Twente

- E. Larsson, University of Lund

# **Executive Summary**

This document reports on the activities performed within two tasks of the BASTION project: T4.3 and T4.4. Being the last deliverable in WP4, it concludes the work done in the frames of this work package, presenting solutions for reuse and adaptation of various embedded instruments both in the field and in a system/board test environment. These results are mainly based on combined achievements already reported in D4.1 and D4.2 but also rely on key research done in the rest of the project, especially in WP1 and WP2. The document first presents techniques for wear-out and aging fault detection including IRFs and Low-Latency SEUs. Secondly, we describe instruments and methods for testing marginal and delay faults at the board level. Finally, automation and integration into board test environment is described.

#### List of Abbreviations

ADC Analog-to-Digital Converter

ATE Automatic Test Equipment

BBIST Board Built-In Self-Test

BIST Built-In Self-Test

BSDL Boundary-Scan Description Language

BS Boundary-Scan

BST Boundary-Scan Test

CAD Computer Aided Design (also EDA)

CPU Central Processing Unit, also Processor

DFT Design For Testability

DNL Differential Non-Linearity

DPM Defects Per Million

DRAM Dynamic RAM

DRC Design Rule Check

EDA Electronic Design Automation (also CAD)

EMS Enhanced Manufacturing Services

FIFO First In, First Out (data buffer)

FPGA Field Programmable Gate Array

FP7 European Union's 7<sup>th</sup> Framework Program

HW Hardware

IC Integrated Circuit ICT In-Circuit Test

IJTAG Internal JTAG, a short name for IEEE 1687 standard and

infrastructure collectively

INL Integral Non-Linearity

IP Intellectual Property (hardware module in FPGA or SoC)

IRF Intermittent Resistive Fault

JTAG Joint Test Action Group; also Boundary Scan; often used as a short

name of the IEEE 1149.1 standard and respective infrastructure

including test access port and header on the board;

LSSD Level-Sensitive Scan Design

NBTI Negative Bias Temperature Instability

NFF No Fault Found or No Failure Found (also NTF)

NTF No Trouble Found (also NFF)

PCB Printed Circuit Board

PCBA Printed Circuit Board Assembly

PDL Procedural Description Language

POST Power-On Self-Test

RAM Random-Access Memory

RTD Research and Technological Development SAR-ADC Successive-Approximation-Register ADC

SBST Software-Based Self-Test

SEU Single Event Upset

SIB Segment Insertion Bit

SoC System on Chip

SVF Serial Vector Format

SW Software

TDR Test Data Register

UUT Unit Under Test

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

# **Table of Contents**

| Ta | able of F         | Revisions                                                              | iii  |

|----|-------------------|------------------------------------------------------------------------|------|

| Αı | uthor, B          | eneficiary                                                             | iii  |

| E> | cecutive          | Summary                                                                | iii  |

| Li | st of Ab          | breviations                                                            | iv   |

| Tá | able of (         | Contents                                                               | iv   |

| 1  | Intro             | oduction                                                               | 2    |

|    | 1.1               | Structure of the document                                              | 3    |

| 2  | Emb               | edded instruments for IRF detection on ICs and boards                  | 4    |

|    | 2.1               | Introduction                                                           |      |

|    | 2.2               | State-of-the-art                                                       | 4    |

|    | 2.3               | IRF Detection at Chip-level                                            | 6    |

|    | 2.3.1             | The proposed monitor                                                   | 6    |

|    | 2.3.2             | Intermittent Resistive Faults Model                                    | 8    |

|    | 2.3.3             | Intermittent Resistive Fault Simulation                                | 9    |

|    | 2.3.4             | 8 8                                                                    |      |

|    | 2.4               | IRF Detection at Board-level                                           |      |

|    | 2.5               | Section Conclusions                                                    | . 13 |

| 3  | A Fra             | amework for Combining Concurrent Checking and Functional Test for Lo   | w-   |

| La |                   | EU and Aging Fault Detection                                           |      |

|    | 3.1               | Motivation                                                             |      |

|    | 3.2               | State-of-the-art                                                       | 14   |

|    | 3.3               | The Concept of Concurrent Checkers                                     | 16   |

|    | 3.4               | Framework and Methodology                                              | . 17 |

|    | 3.4.1             | Checker Qualification and Minimization                                 | 18   |

|    | 3.4.2             |                                                                        |      |

|    | 3.4.3             | Fault Simulation of the Functional Test                                | 19   |

|    | 3.5               | Experimental Results                                                   |      |

|    | 3.5.1             |                                                                        |      |

|    | 3.5.2             |                                                                        |      |

|    | 3.5.3             |                                                                        |      |

|    | 3.5.4             |                                                                        |      |

|    | 3.6               | Section Conclusions                                                    | 24   |

| 4  | Faul <sup>-</sup> | t Extraction in Self-Reconfiguring IEEE 1687 Networks                  | .25  |

|    | 4.1               | Introduction                                                           |      |

|    | 4.2               | Background and Prior Work                                              |      |

|    | 4.3               | Self-Reconfiguring Network                                             |      |

|    | 4.4               | Fault Manager                                                          |      |

|    | 4.4.1             | 6                                                                      |      |

|    | 4.4.2             | 1 6                                                                    |      |

|    | 4.5               | Validation and Hardware Overhead                                       |      |

|    | 4.6               | Section Conclusions                                                    | 34   |

| 5  | Emp               | loying Bit Error Rate Measurements for Board-Level Marginal Fault Test | 35   |

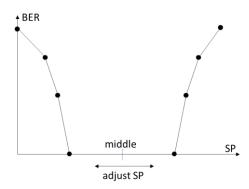

|    | 5.1   | BERT instrument                                                  | 35      |

|----|-------|------------------------------------------------------------------|---------|

|    | 5.2   | DDR memory tester                                                | 36      |

|    | 5.2.1 | State-of-the-art                                                 | 36      |

|    | 5.2.2 | Method description                                               | 37      |

|    | 5.2.3 | Experimental setup                                               | 44      |

|    | 5.2.4 | Experimental results                                             | 44      |

|    | 5.2.5 | Summary                                                          | 46      |

|    | 5.3   | Section Conclusions                                              | 46      |

| 6  | 0     | the detection of board delet faults through the everytion of fu  |         |

| _  |       | the detection of board delay faults through the execution of fur |         |

| pı | •     | : analysis and methods for improvements                          |         |

|    | 6.1   | Introduction                                                     |         |

|    | 6.2   | Delay Fault Models and Observation Mechanisms                    |         |

|    | 6.3   | Experimental Setup                                               |         |

|    | 6.3.1 |                                                                  |         |

|    | 6.3.2 |                                                                  |         |

|    | 6.4   | Experimental Results                                             |         |

|    | 6.4.1 | Application Functional Programs                                  | 50      |

|    | 6.4.2 |                                                                  |         |

|    | 6.4.3 | Evaluation of Delay Fault Coverage for Test Program Based on     | March-C |

|    | Algor | ithm                                                             | 52      |

|    | 6.4.4 | Ad hoc Test Program                                              | 52      |

|    | 6.5   | Section Conclusions                                              | 54      |

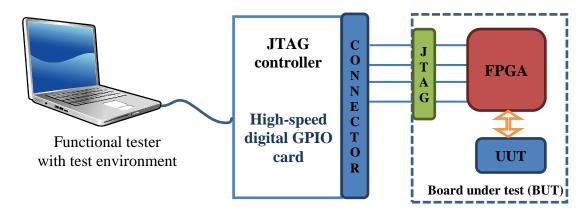

| 7  | Auto  | omation and integration in a board-level test environment        | 55      |

|    |       |                                                                  |         |

| 8  | Cond  | clusions                                                         | 58      |

| 9  | Refe  | rences                                                           | 60      |

#### 1 Introduction

This deliverable is the last one in BASTION project to report research and development activities. The results presented in this document are, hence, connected to all other work packages. Fault coverage metrics developed in WP1 help assessing the results reported in Sections 5 and 6. Results of WP2 contributed to Sections 2, 3, and 5. Section 4 is based on previous results reported in WP3. Prior activities of WP4 were the basis of activities described in Sections 3 and 6. In its turn, the work presented in this deliverable contributes to the major part of the demonstrator, described in D6.2

Board and system level test today cannot any longer rely fully on traditional dedicated test technologies like In-Circuit Test, Optical or X-Ray Inspection and even Boundary Scan. A contemporary high-performance system board is a complex 3D object that may contain dozens of hidden layers, stacked microvias, high density interconnect, with all above not contributing to ease of test and reliability. High-speed signals are normally fine-tuned or even calibrated to deliver pitch perfect timing even in case of now-ubiquitous DDR3 memories. Today, data transmission rates on the board may be reaching multi-gigabit ranges on a single channel. Such defects like dewetting, cold solder, head-in-pillow, voiding/crack in micro-via or excessive solder voids may result in system performance issues, increased error rates, intermittent faults and other sporadic stability issues observed in certain operation modes, at certain workloads or manifesting in a seemingly stochastic manner, which contributes to increasing test escape rates and No Failure Found.

Every mission-critical system today has to successfully pass a fit-for-function qualification test, which is based on a combination of functional tests and application-based tests. Stress testing or endurance testing is often used afterwards to eliminate marginal devices, such that fail due to parametric deviations, dynamic faults, intermittent or marginal defects introduced during final assembly of printed circuit boards. Functional test alone does not any longer guarantee fault-free operation of the target system in the field.

One of the key contributions of WP4 is the concept of combined usage of functional tests and IC-level instruments during the post-assembly system test (board level or product test). Although, D4.2 already addressed this topic, here we present follow-up activities in Section 3 and Section 6. While the former one addresses aging fault detection in the field, the latter one assesses the ability of traditional techniques to cover board-level delay faults and compares the typical test coverage with the BASTION approach. The chip-level instruments help increasing the observability and hence improve the coverage of functional test and the ability of in-situ fault detection both in-field and during the manufacturing test.

Reuse of IC-level instrumentation is also considered in Section 2, which elaborates on IRF monitoring in the field for early detection of mechanical wear out on the board as well as aging on the chip – well before the damage would accumulate to the critical level resulting in system malfunction.

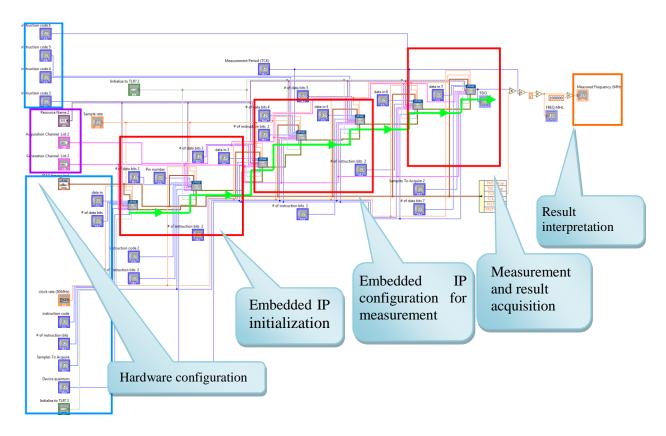

Section 5 addresses the challenge of systematic discovery of marginal defects, timing related faults and stability issues in board assemblies as a part of end-of-line testing in volume production environment. We have develoed a set of embedded instruments on FPGA, which reuse some of the typical functional blocks of the IC converting them into powerful embedded test instruments. The instruments have been evaluated on industry-grade high-end products demonstrating stable detection of injected marginal faults, even such that would otherwise escape the normal functional test.

Section 3 further improves the work done in WP3 by introducing a concept of self-reconfiguring instrumentation networks that would improve the ability of the system to quickly detect and localize faults in the field, including such scenarios as Health Monitoring, Software Based Self-Test, and Power-On Self-Test.

#### 1.1 Structure of the document

This document concludes activities of WP4 reporting the results achieved in two tasks: T4.3 "Chip-Level instrumentation reuse at the board level" and T4.4 "Automation and integration in a board-level test environment". These results are mainly based on combined prior achievements reported in D4.1 and D4.2 as well as in the rest of the project, especially in WP1 and WP2.

This report is structured as follows. First, Section 2 describes embedded instruments for IRF detection as a result of wear out on board and the IC. Section 3 continues the topic of aging aiming for NBTI effects and other issues. Section 4 elaborates on the concept of self-reconfiguring on-chip instrumentation networks for fast on-line fault detection and localization. Section 5 and 6 describe how IC-level instruments can improve delay fault and marginal defect detection on the board. Section 7 presents some details regarding instrument integration into a board-level test environment. Finally, Section 8 draws some conclusions and discusses the progress on KPI5.

# 2 Embedded instruments for IRF detection on ICs and boards

#### 2.1 Introduction

Shrinking feature sizes in semiconductor manufacturing technologies lead to more reliability issues in interconnections. Smaller interconnect dimensions, shrinking transistor geometries, and reduced voltage and noise margins threat the dependability of electronic integrated systems. In electronic systems like system chips and printed-circuit boards, interconnection wiring is heavily dominating the infrastructure and therefore faults in these parts are extremely important.

One of the most challenging interconnect reliability issues that threat dependability of highly-dependable systems are intermittent resistive faults (IRF). IRFs are a specific category of No Fault Founds (NFFs). Like other types of NFFs, they result in many product returns in car and avionic industries; moreover, evoking and detection of these faults are highly time and cost consuming [Dav05].

Marginal or unstable interconnections are the most likely cause of IRFs. In advanced integrated circuits, as well as circuit boards, there are high number of interconnection such as tracks, vias, bumps and junctions. All of these interconnections are vulnerable to IRFs. Moreover, electro migration, corrosion, temperature and mechanical stress cause more increased instability. Cracks and voids in interconnections are susceptible to the above issues.

IRFs manifest themselves as a sequence (burst) of low-level resistance changes in an interconnection. An interconnection can be a chain of interconnect *segments*, including regular chip interconnect, TSVs, vias and micro-bumps in 2.5 and 3D silicon structures. It also extends to (complex) printed-circuit boards level, and can include e.g. cold-solder connections in that case. IRFs might occur randomly during system operational time in any interconnect. IRFs emerge repetitively in a location and they gradually become more severe during the lifetime of the system. Finally they can evolve in a permanent fault [Ria13]. Therefore, it is very important to detect and repair these faults before they become permanent and result in a system failure especially in safety-critical systems.

Intermittent fault (IF) detection is very challenging. IFs are not deterministic and may (probably) not appear during testing. Therefore, for IF detection, highly time and cost consuming techniques such as periodic testing [Kra06] or online monitoring are required. In the case of periodic testing, the probability of detecting IRFs increases whereas in online monitoring technique the behavior of circuits is monitored by different embedded monitors during operational time.

IRF online monitoring may be performed at board- or chip-level. One approach for IRF detection at board-level has been published by us in [Ker15a]. We suggested an enhanced version of IEEE standard 1149.4 to allow online monitoring of wiring tracks in boards. In [Ebr16b] and D2.1 we have proposed a digital monitor which is able to detect IRFs at chip-level. In this deliverable, the proposed IRF monitor has been reused to detect IRF at board level and it has been validated by a programmable hardware IRF generator.

The remainder of this research is organized as follows. First, a review of related works and the state-of-the-art is been introduced. Then, the proposed monitor is presented. In Section 2.3.2, first, a generic simulation model for IRFs is introduced, and then fault simulation results for IRFs as well as aging detection are presented. Last, a hardware implementation of the IRF monitor has been introduced and validated.

#### 2.2 State-of-the-art

Several papers have studied the influence of intermittent faults on digital systems [Gra14], [Gra10]. In [Gra14] the authors studied the impact of intermittent faults on the behavior of a reduced instruction set computing

(RISC) microprocessor by using VHDL-based fault injection. The authors of [Pan12] proposed a metric intermittent vulnerability factor to characterize the vulnerability of microprocessor structures to intermittent faults. Intermittent fault models at logic and RTL abstraction levels have been generated in [Gil12] and [Gra10]. In addition, the behavior of a microcontroller has been studied in the presence of intermittent faults by simulation-based fault injection.

However, none of the previous work has considered the problem of IRFs at circuit level. We have proposed a model for IRFs and analyzed the influence of IRFs on analogue [Wan14] as well as digital circuits [Ker15b] at the transistor level. In [Ker15b], we presented an extension of the mixed-signal boundary-scan standard, IEEE 1149.4, to detect IRFs in boards. In this deliverable, we continue the investigation of IRF detection and introduce an IRF detection technique at chip-level.

IRFs occurrences in interconnections of a chip result in timing deviation in circuit's paths. There are several approaches toward measuring path delay by using dedicated measurement circuits such as tunable replica circuits (TRC), ring oscillator (RO) and time-to-digital converter (TDC). They will be briefly discussed subsequently.

A TRC is a method for detecting (timing) errors due to voltage and delay degradation. Process variations and aging affects replicas in a similar way in the critical path. However, the random component of process variations will result in differences between the TRC and the actual critical path [Bow09].

The ring-oscillator-based architecture can be used more efficiently for path delay measurement by making the path-under-test a part of the oscillator. The ring oscillator frequency can be monitored *continuously* and any degradation in frequency with time can be attributed to device aging affects [Kim15]. Ring-oscillator based test structures can simply be used to measure the aging degradation effects in digital circuits [Kim15], [Hsi15]. A TDC measures the time interval between two transitional signals. It is typically constructed from registers and delay elements and, like ROs, can be used to measure the effect of process, temperature and voltage variation and aging degradation. However, as the TDC is an on-chip circuit, it suffers from both process variation and aging effects. Hence, it needs self-calibration [Kat15].

However, *none* of the above-mentioned methods can be used for IRF detection. As IRFs *occur randomly in time*, an online monitor should always monitor path activities to detect IRF occurrences. TRC is not applicable for IRF detection as an IRF can occur in every interconnection wire independently. As a result, an IRF in a replica does not mean there is an IRF in the actual path. Similarly, a RO needs a dedicated path and therefore it is not suitable for IRF detection. The usage of TDC for IRF detection is not cost effective in terms of area and power consumption.

Yet another approach towards measuring the timing violations is to use slack monitor accompanied by a guard-band. Most of the aging faults change transistor parameters and increase interconnections' delay. In a synchronous system, a delay increment can result in timing failure. Timing failures occur if the delayed data does not meet a flip-flop's setup requirement and has a late transition near to the clock edge. Hence, online delay (or slack) monitoring in an integrated circuit is a suitable metric for measuring the aging of synchronous circuits [Bow09], [Rah14].

The timing slack or guard-band is defined as the delay, between the data arrival time and active edge of the clock, minus the flip-flop setup time. Generally, guard-band assignment is part of pre-silicon design phase. A guard-band for a monitor is determined based on the slack of the target path and the clock frequency of the system. This deliverable does not focuses on time-windows (guard-band) generation. A practical approach to design a time-windows generator has been proposed in [Reb11]. The same approach can be used for the IRF monitor as well.

Recent works [Lai14], [Sad15] show slack monitoring methods are effective in detecting timing errors such as aging and process and voltage variations. In [Rah14] a timing slack monitoring methodology of inserting

monitors at both path ending nets and path intermediate nets is presented. In [Sad15], the authors presented a digital slack monitor which is able to measure the slack of a selected path. However, their monitor is able to detect either rise or fall transitions and it needs re-initialization for each slack monitoring procedure.

The aforementioned methods cannot be used for IRF detection because they need a pre-initialization and calibration; moreover, they do not provide continuous online monitoring on a data path.

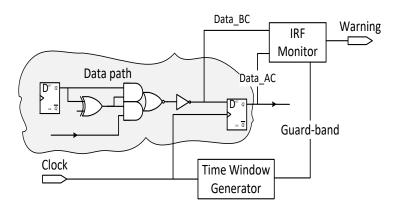

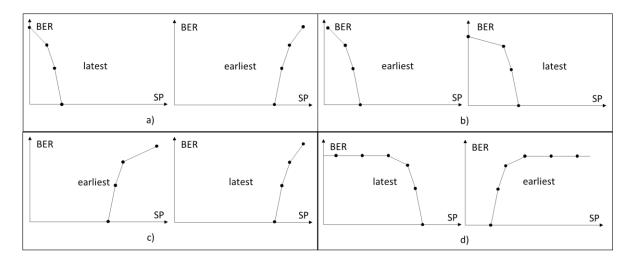

Figure 2-1. An example of a data path with IRF monitor and time window generator

In this deliverable, the usage of slack monitors for IRF detection has been investigated. We have proposed a digital IRF monitor, which is able to detect timing variation and distinguish if it is because of aging or IR faults.

# 2.3 IRF Detection at Chip-level

# 2.3.1 The proposed monitor

Timing slack is an excellent measure for the health of a circuit. Measuring timing slack can allow an early warning of deterioration and trigging pre-emptive actions to avoid failure because of aging or IRFs. Basically, a positive timing slack indicates that a circuit is operating safely, with a margin by which the delay can increase before causing a failure. A small or negative quantity of slack is an indication that the circuit is close to, or beyond the point of failure.

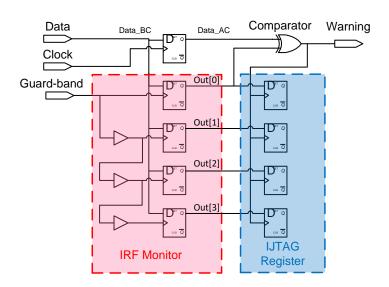

Figure 2-2. The schematic of the proposed IRF monitor

The proposed IRF monitor is based on detecting and measuring slack violation on a data path. It is composed of a slack monitor and a time window generator (Figure 2-1). The monitor is located at the end of a data path of the design. It continuously monitors signal at the end of the data path during a timing window provided by the time window generator. It makes sure there is always no slack violation during operation to avoid wrong data be captured.

The schematic of the proposed IRF monitor is presented in Figure 2-2. It raises a warning flag in case of a specified guard-band (safety margin) is violated, which is a sign of an impending timing failure. It consists of four D-flip-flops. Each flip-flop receives its clock from the previous output of a buffer, except the first flip-flop whose clock is connected to the *Guard-band* line. As a result, each D-flip-flop clock is delayed by the delay of one buffer. As all D-inputs are connected to the *Data* line, all D-flip-flops in the monitor can capture the signal on the Data line at different times. *Data\_AC* and *Data\_BC* are data at the end of the data path after and before capture, respectively.

The IRF monitor uses a very simple concept. If there is not any slack violation in the data line, then correct data is captured in the flip-flop in the path and all flip-flops in the monitor capture the same value. Therefore, the *warning* signal remains zero. In the case of slack violation, e.g. because of aging or IRFs, the *warning* signal becomes one and the degree of violation is captured in the monitor's flip-flops. This degree can be "1000", "1100", "1110" and "1111" in case of fault occurrence in the falling signal or "0111", "0011", "0001" and "0000" in case of fault occurrence in the rising signal. "1000" and "0111" indicate a small timing violation while "1111" and "0000" indicate large timing violation.

Figure 2-3. An IRF monitor wrapped by using the IJTAG standard

The stored data in the monitor's flip-flops will be read by fault-management software through an IJTAG [Shi14] network. Based on this data and the monitors' location, the fault management software can distinguish the type of the detected timing fault: if it is caused by a transient, aging or intermittent fault. If during a certain duration, several faults with different amounts of captured timing violation occurs on a path, it can be classified as an IRF. If only one timing violation happens, it can be classified as transient fault. Finally, it can be an aging fault; in this case the IRF monitor detects several timing violations with the same violation degree.

```

1

iPDLLevel 1

2

iProcsForModule IRF Monitor

3

set Status 0

□while { $Status == 0} {

4

5

iRead IRF Monitor.Warning

6

iApply

7

set Status [iGetReadData IRF Monitor.Warning]

8

1

9

iRead IRF Monitor.Out

iWrite IRF Monitor.Ack 0b1

10

11

iApply

12

set IRF Out [iGetReadData IRF Monitor.Out]

13

iWrite IRF Monitor.Ack 0b0

14

iApply

```

Figure 2-4. Simple example of a PDL file of the IRF monitor wrapped by IJTAG

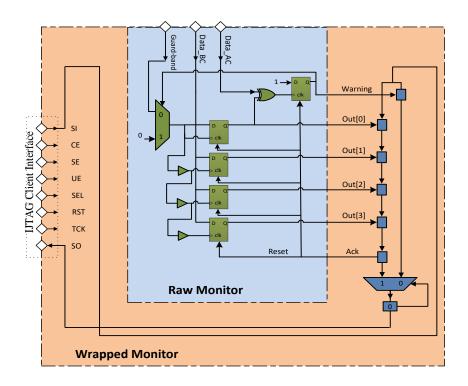

Figure 2-3 shows the raw IRF monitor wrapped with IJTAG registers into an embedded instrument. It receives the signals <code>Data\_BC</code>, <code>Data\_AC</code> and <code>Guard\_band</code>. A simple access procedure written in PDL for the IRF monitor is shown in Figure 2-4. It consists of a simple logical synchronization mechanism between the IJTAG controller and the monitor. This controller <code>continuously polls</code> on the warning flag until a warning is raised (lines 4-8); then it reads the output data and concurrently writes a '1' in the acknowledge register in order to notify the instrument to reset its warning and data outputs (lines 9-11). Finally, the controller resets the acknowledge flag in the next scan cycle (lines 13-14).

#### 2.3.2 Intermittent Resistive Faults Model

We have developed a software module to generate IRFs in a Cadence Virtuoso environment, based on some real IRF measurements in [Ker15b], [Acc08]. A basic scheme of the IRF injector has been introduced in D1.2, 0, and 0. The IRF injector generates a burst of IRF pulses based on six parameters. These parameters consists of the number of pulses in a burst (burst length), start and stop times of the burst, active and inactive times, and resistance value for each resistance pulse. After determining the range of these parameters by the user, the IRF injector randomly generates resistance pulses according to these parameters.

One example of the values and distributions applied for the simulations in this deliverable are listed in Table 2-1. After a random start-time such as 1ns or more passes in simulation time, the burst of resistance pulses starts. Each pulse of the burst has a random resistance value R witch is active during a random activation time (T-active). After each pulse, an inactivation time (T-inactive) is randomly generated in which a fault-free situation exists (R=100 $\Omega$ ). In the case of a burst (burst length > 1), there is a feedback loop and the same procedure will be followed again. The IRF generation procedure is completed by generating a fault-free situation at the end.

Table 2-1: Range of used parameters in the IRF generator during fault simulation

| Parameter  | Minimum | Maximum | Distribution |

|------------|---------|---------|--------------|

| Start time | 1ns     | 10ns    | Uniform      |

| Resistance   | 100 Ω  | 100 kΩ  | Uniform |

|--------------|--------|---------|---------|

| T-active     | 0.1 ns | 2 ns    | Uniform |

| T-inactive   | 0.1 ns | 2 ns    | Uniform |

| Burst length | 1      | 20      | Uniform |

| Safe time    | 1 ns   | (years) | Uniform |

In this model, the concept of seeds in random variable generation is being used to allow an easy replication of the same intermittent fault for comparisons during simulations. The model has been implemented in Verilog-A and allows replacing a normal wire in the net list by one including an IRF.

By using this model, analogue mixed-signal [Wan14] as well as digital circuits [Ker15b] can be evaluated at the transistor level. The next sub-section will show some results of IRF simulation and the validation functionality of the proposed IRF detection monitor.

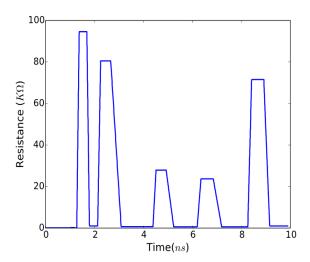

Figure 2-5. Used IRF for the simulations

#### 2.3.3 Intermittent Resistive Fault Simulation

In order to evaluate the ability of the proposed IRF monitor to detect IRFs, a well-known concept of fault injection, simulation-based fault injection [Gil12], is used. As an example, an AES-128 encoder circuit in the 45nm Nangate CMOS technology [Nan08] has been used. After synthesis by Synopsys Design Compiler, the circuit operates at a clock frequency of 1.6 GHz.

IRF simulation and the monitor validation has been performed at transistor-level using Virtuoso Cadence. Several critical path and near critical paths were selected based on area constraint and the design's timing information. The proposed monitor was inserted at the endpoint of the target paths.

One example of a simulation fault injection is shown in Figure 2-6 and Figure 2-7. For these fault simulations, the injected IRF in this simulation is as shown in Figure 2-5. It is a burst of five resistance-related pulses from  $1k\Omega$  to  $100k\Omega$  during 10ns.

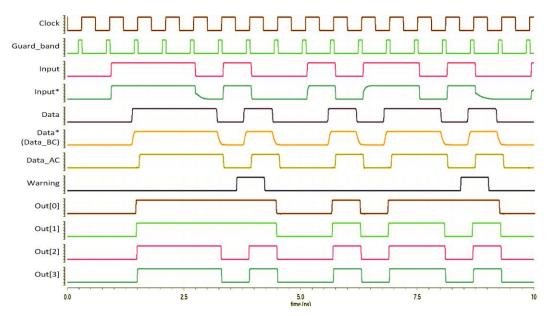

Figure 2-6. Simulated waveform results of the proposed IRF monitor under IRF injection

In Figure 2-6, the clock of the system is shown on the top, other signals from top to down are as follows. *Guard-band* indicates when the proposed monitor should be active. *Input* is a sample of data transitions in the beginning of the critical path. *Input\** shows the signal Input after the injection of the IRF (Figure 2-5). Signals *Data* and *Data\** are the outputs of the path in fault-free and faulty cases, respectively. *Data\_AC* is the signal captured by the flip-flop at the *end* of the path in a case of fault, as it can be seen; there is not any functional error in the signal although two small delay degradations are detected by our monitor. Signal *Warning* is the output of the proposed monitor. It shows the monitor detected two late transitions on the data (signal *Data\**). The last four signals (Out[0], Out[Dav05], Out[Ria13] and Out[Kra06]) are the outputs of the flip-flops of the monitor. The captured values by these flip-flops show the value of degradation and path-slack reduction. At the time 3ns, the monitor captures a timing violation. The value of "1100" is stored by flip-flops of the monitor. Two flip-flops captured a wrong value. It means that the degree of the path's slack is violated as much as two buffer delays. Figure 2-5 shows that the IRF at this time induced by a very high resistance (80 k $\Omega$ ). Similarly, at 8 ns, a slack violation is detected as much as 1 buffer delay because the value of '1000' is stored in the monitor's flip-flops. By referring to Figure 2-5, it can be seen, the value of the IRF has been near 70 k $\Omega$  at 8ns.

Figure 2-7. Simulated waveform results of the proposed IRF monitor under NBTI aging conditions

# 2.3.4 Aging Simulation

The experimental results in [Sto10] show that NBTI is the primary factor leads to timing degradation in current technologies. NBTI has been shown to cause shifts in threshold voltages of up to 50mV over an operating lifespan of 10 years in 65nm technologies. This translates to more than 20% deterioration in circuit operating speed [Wan07]. To model the delay induced by aging faults (NBTI), the Vth of all PMOSs in the target circuit and the monitor have been increased by 50mV in our Cadence simulator.

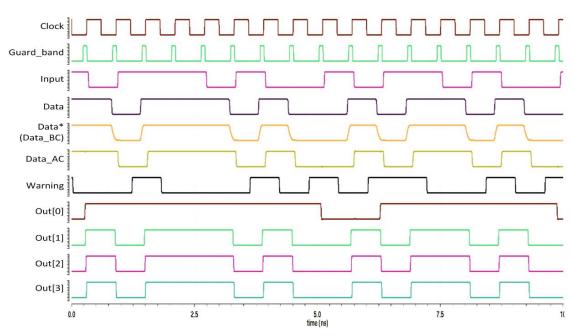

Figure 2-7 shows the Cadence Virtuoso simulation results of a combinational circuit where its transistors are subjected to the aging faults. The output (logic) behavior of the circuit as well as the proposed IRF monitor has been evaluated. The signals in Figure 2-7 are the same as ones in Figure 2-6. Signal *Data* shows the simulation results of the target circuit before aging. In this case, there is not any timing (guard-band) violation detected by the monitor, as to be expected. Signal *Data\** shows the simulation results of the target data path after aging. By looking at the *Warning* signal it can be seen that the monitor has detected some timing violations. The first flip-flop of the monitor has captured wrong values but other three flip-flops have not captured any violation.

From the above simulations, it can be concluded that for aging detection one flip-flop for each monitor is sufficient. Because, the degree of timing violations in aging faults are not random and in fact gradually increase during a system lifetime. Whereas in IRFs, the degree of timing violations change randomly, hence a number of flip-flops are required to capture violation.

In both aging and IRF detection, after a timing violation, a warning flag raises. It enables the degree of timing violation be sorted in the monitor's flip-flop be transferred to the IJTAG [Shi14] registers. Therefore, by extracting timing violation information and the fault localization using the IJTAG standard, a fault management software environment can distinguish the type of occurred faults whether it is an aging, intermittent or transient fault.

Figure 2-8: Measurement set-up of the IRF generator and IRF monitor

#### 2.4 IRF Detection at Board-level

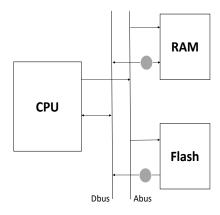

In this section, the ability of the on-chip IRF monitor in board-level IRF detection has been investigated. For this purpose, the IRF monitor has been implemented on a FPGA and has been evaluated by hardware-based fault injections.

In this deliverable a Universal Asynchronous Receiver Transmitter (UART) has been used as an example to investigate IRF detection at board level. A UART transmitter and a receiver was made at logic gate level and implemented on an FPGA (Zynq-7000 board). This is the standard FPGA board used within the BASTION consortium. IRFs have been injected in the transmission line between the transmitter and the receiver by our hardware IRF generator [Ebr16b] (see Figure 2-8).

A number of different IRF sequences were applied to the data input (RX) of the UART. A nominal power supply Vdd of 3.3V was used and the clock frequency was around 5.5MHz (baud rate  $\sim$ 921 kHz). The UART first receives a start bit and then the less significant bits of 8 bits of data and at the end a parity bit and two stop bits. The parameters of the injected IRF are as depicted in Table 2-2. The injected resistance pulses are randomly chosen from a range between 2.5  $\Omega$  and 5 k $\Omega$ , which is rather low and hence less likely to cause logic errors.

Table 2-2: Range of used parameter in IRF generator during fault emulation

| Parameter    | Minimum              | Maximum   | Distribution |

|--------------|----------------------|-----------|--------------|

| Start time   | $0.1 \mu \mathrm{s}$ | $1 \mu s$ | Uniform      |

| Resistance   | 2.5 Ω                | 5 kΩ      | Uniform      |

| T-active     | $0.6 \mu\mathrm{s}$  | $3 \mu s$ | Uniform      |

| T-inactive   | $0.3 \mu\mathrm{s}$  | $1 \mu s$ | Uniform      |

| Burst length | 1                    | 2         | Uniform      |

| Safe time    | 1 μs                 | (years)   | Uniform      |

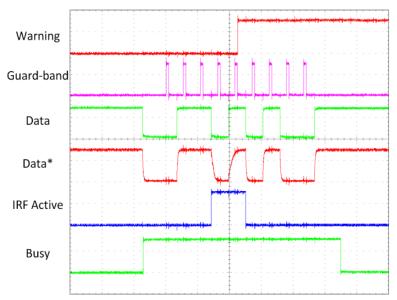

In Figure 2-9, the result of hardware IRF injection is shown. The time scale is 2  $\mu$ s and voltage scale 2 Volt. The *busy* signal shows that when the UART receiver receives data, *Data* and *Data*\* show the bit stream

received by the receiver before and after fault injection on the data line, respectively.  $IRF\_active$  indicates at what time the IRF is injected. The  $Guard\_band$  signal has been generated by an (on-chip) PLL on the FPGA with a frequency 10 times faster than the system clock frequency. As can be seen, the IRF monitor has detected the timing violation and has raised a Warning signal. Here, the detected IRF has been active for 1.8  $\mu$ s with a resistance value of 3.2 k $\Omega$ . The degree of violation has not been shown in this figure but it has been restored in the monitor's flip-flops with a "0111" value. It should be noted that the IRF has not caused a logic error and the sent bit stream "01010110" has been transferred intact without parity or frame error. However, the IRF monitor detected the timing violation caused by injected IRF. This monitor's ability helps a system to avoid going down from a failure.

The comparison of the simulation and hardware-based fault injection shows a significant speed enhancement in IR fault injection. In Section IV, the fault simulation was carried out using a 64-bit Linux machine with 8 GB RAM running at 3.4 GHz. The simulation time was about 300 seconds. Whereas, the hardware-based fault injection can be done in about 30  $\mu$ s. This means that the hardware-based injection IRF is up to seven orders of magnitude faster than simulation-based IRF injection.

Figure 2-9. Measured waveform results of the proposed IRF monitor under hardware IRF injection

#### 2.5 **Section Conclusions**

We have presented a digital online IRF monitor to detect one of the most challenging interconnection reliability issues i.e. intermittent resistive fault (IRF). Early-stage detection of this fault can prevent catastrophic failures in safety-critical systems. The experimental results show that the presented monitor can detect small timing deviations produced by IRFs in data paths. In addition, the proposed monitor in actual hardware by hardware-based fault injection has been evaluated. The experimental results show the ability of the proposed monitor to be reused for IRF detection at board level.

# 3 A Framework for Combining Concurrent Checking and Functional Test for Low-Latency SEU and Aging Fault Detection

The focus of this research carried out in BASTION is detection of faults in chip-level modules by combining concurrent checkers with on-board or on-chip functional test to enable cost-effective trade-offs between area-overhead and test coverage. First, we propose a framework of tools for formally evaluating the quality of the checkers and for optimizing the overhead area with given fault coverage constraints. The stress is in particular on the minimization of the error detection latency, which is a crucial aspect in order to eliminate (or limit) error propagation. Second, the concurrent checkers will be complemented by the functional test to be applied as a periodic routine during the idle periods in router operation. The framework together with the corresponding methodology has been successfully applied to a realistic case-study of a fault tolerant NoC router design. The case study shows that combining concurrent routers with functional test allows reducing the area overhead of the checkers from 31-35% down to 1.5-10% without sacrificing the fault coverage.

#### 3.1 Motivation

One of the main challenges related to the design of modern integrated circuits is the extreme down-scaling of modern technologies that increases the probability of the components to wear-out as well as their vulnerability towards environmental effects. These are phenomena occurring during the life-time of the system and cannot be screened out by manufacturing testing. Thus, cost-efficient mechanisms for detecting faults during system's life-time are needed. These mechanisms should detect errors within routers and enable reconfiguration of the routing network in order to isolate the problem and provide graceful degradation for the system. In BASTION, we propose combining concurrent on-line checkers with functional test in order to achieve early and cost-effective detection of faults.

Regarding the development of on-line checkers, we introduce a new framework and a methodology with a stress on the level of automation, fault coverage, detection latency and area-efficiency. The methodology consists of four main steps. The first step of the methodology is formal checker qualification which includes identification of control-intensive parts of the architecture, converting them to pseudo-combinational counterparts, preparation of the checkers synthesized from verification assertions and specifying the environment in terms of valid input stimuli for the pseudo-combinational circuit. As a result, the faults detected by each individual checker will be calculated.

Second, the number of checkers within the set will be minimized by applying the checker optimization step. As a starting point is the fault detection characteristics for each individual checker as well as their weights in terms of silicon area. Further, a heuristic minimization method is applied resulting in a minimal selection of checkers to achieve a target fault coverage level. The minimization technique is based on a divide-and-conquer approach of partitioning the checkers' fault table into independent clusters. This approach is very effective as the checkers devised for different modules normally do not have overlapping fault sets.

Third, and optional, step of the methodology includes devising additional checkers from temporal assertions for modules that do not achieve 100% fault detection. For these checkers the formal qualification step described above is not possible and traditional fault injection experiments are carried out by a sequential fault simulation tool included to the framework. Finally, the checkers are to be complemented by the functional test.

#### 3.2 State-of-the-art

Online detection of errors in logic is a thoroughly studied research area. Traditional Triple-Modular Redundancy (TMR) and duplication based approaches are too costly in terms of multiplying the area and correspondingly the power consumption. An alternative to minimize this overhead is the selective TMR that identifies Single Event Upset (SEU) sensitive sub-circuits that are to be protected [Tut1].

In addition, there exists a variety of solutions based on coding techniques such as Berger [Tut2] or Bose-Lin [Tut3] codes. In many works the coding techniques are combined with synthesis [Tut4, Tut5]. The approaches suffer from significant area overhead to the design to be checked.

Concurrent on-line built-in self-test techniques such as Built-In Concurrent Self-Test (BICST) [Tut6] and Reduced Observation Width Replication (ROWR) [Tut7] provide high fault coverage at low area overhead but only consider a limited subset of pre-computed test vectors. Hence these approaches are likely to miss faults occurring in a normal circuit operation.

Several alternatives based on checkers that do not require modification of the circuit under test have been developed. Creating checkers automatically based on logic implications derived from the circuit structure [Tut8] is feasible but suffers from low fault coverage and high area overhead, often exceeding the duplex solutions. On the other hand, deriving checkers from functional assertions, or reusing verification assertions, is similarly known to yield low coverage of structural faults as it is difficult to correlate functional coverage to structural one [Tut9].

Many previous works have focused on addressing faults in the control logic of NoC routers. In [Tut16], Yu et al. have addressed fault tolerance for NoC topologies and proposed an error control method for detecting transient errors in routing logic implemented using Logic-Based Distributed Routing (LBDR) mechanism and its extension for high-radix topologies, LBDRhr. The proposed error control method utilizes the inherent information redundancy (IIR) to reduce the error control overhead. However, the method does not guarantee full fault coverage.

Authors of [Tut17] have presented a method for online error detection and diagnosis of NoC switches. The proposed method deals with routing faults that cause packets to be forwarded to unintended output ports. Regarding modeling routing faults in switches, a high-level fault model has been introduced in this work. The fault coverage is measured only at the functional level and there is no estimates on correlation to gate-level fault coverage.

In order to deliver correctness guarantees for the complete network, Parikh et al. have proposed a network-level detection and recovery solution ForEVeR [Tut14] that monitors the traffic in the NoC and protects it against functional bugs that were not detected during design time. To this end, ForEVeR augments the baseline NoC with a lightweight checker network that alerts destination nodes of incoming packets ahead of time and is used for the recovery process. The approach suffers from extremely high latency. Only 30% of the faults will be detected during the first clock cycle by the approach.

The work in [Tut15] proposes checkers synthesized from a set of 32 verification assertions. The checkers detect most of the injected faults. The faults that are not covered correspond to non-catastrophic failures. The work proposed in [Tut15] is not automated and lacks the completeness and minimization aspects present in BASTION.

In [Tut18] a hybrid method is introduced for synthesis of fault-secure NoC switches utilizing error detecting codes for the data path (data flits) and a concurrent error detection structure for dealing with faults not covered by the flit encoding (using multiple parity trees). However, the work still results in more than 50% area overhead.

The use of embedded test configurations for testing the datapath of NoC routers has been proposed in [Tut19], with design-for-testability structures included in [Tut20] and built-in self-test application in [Tut21]. However,

all the mentioned approaches are targeting the global network and not a concrete router. Furthermore, only off-line test scenarios have been considered in [Tut19, Tut20, Tut21].

BASTION exceeds the existing state-of-the-art in fault tolerant router design by proposing:

- a framework for formal checker qualification. The underlying approach is complete, i.e. it allows proving the absence or presence of true misses by the checkers. In addition, it provides minimal fault detection latency due to the fact that the circuit is transformed into a pseudo-combinational one and therefore only checkers with a single clock cycle latency are considered.

- automated minimization of checkers. The formal qualification of the combinational checkers provides the fault detection capabilities for them. These, along with the checker area requirements are applied in an automated minimization process resulting in a minimal area overhead checker solution under certain fault coverage constraints.

- complementing the resulting checkers with temporal checkers and functional test. This enables combining best of both worlds. In the case of NoC control part, where embedded test packet based approaches have proven inefficient, low area concurrent checkers are applied. On the other hand, in the datapath, the functional test yields full fault coverage whereas error correcting codes would be expensive.

Experimental results on a realistic NoC router design demonstrate the efficiency of the proposed approach.

# 3.3 The Concept of Concurrent Checkers

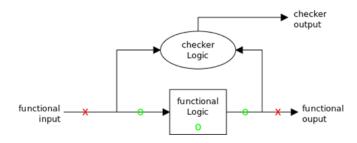

Fig. 1 presents the role of concurrent on-line checkers in detecting faults within a circuit. In addition to the original circuit (functional logic), a set of checkers (checker logic) will be connected to functional inputs/outputs of the circuit. These checkers are derived based on functional assertions obtained from relationships between variables corresponding to inputs and outputs of the circuit. The checker logic targets the faults at lines at the inputs of each gate within the functional logic (marked by green circles). The lines at the functional outputs succeeding the checker inputs (marked by a red cross) cannot be detected by the checker. In addition, the checkers are not targeting the faults at functional inputs preceding checker inputs, since the checker may not detect that the input value has been altered by a fault (such functional input lines are also marked by a red cross in Fig. 3-1). In BASTION, the concurrent on-line checkers target Single Event Upsets (SEUs) and permanent stuck-at faults caused by aging (e.g. BTI).

Figure 3-1. The concept of concurrent checking

Given a fault at a line within the functional logic and a set of input stimuli, four possible scenarios may occur:

Case 1: Fault occurs at an internal line and is visible at functional output(s) and checker logic flags a violation. The term *True Detection* is used to describe this situation, since a critical fault is effectively detected by the checker.

Case 2: Fault occurs at an internal line but is not visible at primary output(s). Checker catches the fault and flags a violation. The term False Positive is used to describe this situation. False positive is not harmful because

an error is flagged which did not have any effect. However, it has negative impact on design's performance because normally it causes re-execution of the task.

Case 3: Fault occurs at internal line but is not visible at primary output(s) and the checker logic does not detect the violation. The term *Benign Miss* is used to describe this situation. Benign miss shows correct operation by the checker.

Case 4: Fault occurs at internal node and is visible at primary output(s). Checker does not detect violation. The term *True Miss* is used to describe this situation, which is the worst possible case. True miss means that the fault propagates to the functional outputs and onwards to the system. However, the system has no information that a critical fault has occurred.

Traditionally, in order to evaluate the fault detection quality of the checkers, *fault injection* has been applied. Fault injection refers to injecting faults into a circuit at a certain time step and simulating it with the input stimuli to see whether any functional output of the circuit changes and whether any of the checker output fires. Due to the fact that it is generally impossible to inject and simulate all the faults at each circuit line at each time step, a statistically significant sample of random faults would normally be injected and simulated.

However, in BASTION a methodology is proposed which is based on automated extraction of a pseudo-combinational circuit out of the original functional logic by breaking the flipflops and converting them to pseudo primary inputs and pseudo primary outputs. Further, an exhaustive test for the extracted circuit is fed through a filtering tool in order to derive the complete valid set of input stimuli which will serve as the environment for checker evaluation. This means that in BASTION, full formal qualification of the combinational checkers with all possible stimuli and faults can be obtained.

Let D be the number of true detections, X be the number of benign misses, F be the set of false positives and W be the number of true misses over all the injection runs. In order to evaluate the fault detection capabilities of the checkers we define the metrics of Fault Coverage (FC), Checkers' Efficiency Index (CEI) and False Positive Ratio (FPR) as follows.

$$FC = \frac{D+X}{D+X+W} \tag{1}$$

$$CEI = \frac{D}{D + W} \tag{2}$$

$$FPR = \frac{F}{F + X} \tag{3}$$

Here, FC shows the probability of the checkers behaving correctly over all possible fault cases, CEI shows the probability of checkers ability to detect critical faults whereas FPR reports the ratio of false positives over all the cases a fault did not propagate to circuit outputs. The mentioned three metrics are calculated for checkers by the automated checker qualification framework proposed in BASTION.

# 3.4 Framework and Methodology

This Section presents the framework for fault tolerant NoC router design that has been developed as an extension of the Turbo Tester test framework [Tut10]. The proposed methodology of combining concurrent checkers with functional test consists of three main steps:

- Checkers' qualification and minimization (combinational checkers);

- Checkers' evaluation by fault injection (temporal checkers);

- Fault simulation of the functional test.

In the following, these steps are explained in more detail.

Report on reuse adaptation, and integration of embedded instruments

#### 3.4.1 Checker Qualification and Minimization

Fig. 3-2 presents the qualification and minimization flow for the checkers. The flow starts with synthesizing the checkers from a set of combinational assertions. Thereafter, a pseudo-combinational circuit will be extracted from the circuit of the design under checking. The pseudo-combinational circuit is derived out of the original circuit by breaking the flipflops and converting them to pseudo primary inputs and pseudo primary outputs. Note, that at this point additional checkers that also describe relations on the pseudo primary inputs/outputs may be added to the checker suite in order to increase the fault coverage.

Subsequently, the checkers' qualification environment is created by generating exhaustive test stimuli for the extracted pseudo-combinational circuit. This stimuli are fed through a filtering tool that selects only the stimuli that correspond to functionally valid inputs of the circuit. As a result, the complete valid set of input stimuli that will serve as the environment for checkers' qualification is obtained.

Figure 3-2. Checkers' qualification and minimization flow

The obtained environment, pseudo-combinational circuit and synthesized checkers are applied to fault free simulation. The simulation calculates fault free values for all the lines within the circuit. Additionally, if any of the checkers fires during fault-free simulation it refers either to a bug in the checker or an incorrect environment.

If none of the checkers is firing in the fault-free mode then checkers' qualification takes place. The tool injects faults to all the lines within the circuit one-by-one and this step is repeated for each input vector. As a result, the overall fault detection capabilities for the set of checkers, in terms of FC, CEI and FPR metrics will be calculated. In addition, each individual checker will be weighted by summing up the total number of true detections by the checker.

The weighting information will then be exploited in minimizing the number of checkers, eventually allowing to outline a trade-off between the fault coverage, and the area overhead due to the introduction of checker logic.

# 3.4.2 Checkers' Evaluation by Fault Injection

There are cases when a module under checking cannot be handled by the combinational checker qualification and minimization approach. For example the module may have a large number of inputs so that the set of generated valid input stimuli would be too large (e.g. datapath modules) and/or the fault coverage reached by the combinational checkers is too low.

In those cases, the checkers are to be evaluated by traditional fault injection. Here a test bench is created for the design and the circuit with the checkers is simulated by a sequential fault simulator with a sufficiently large random sample of faults injected into the circuit. In BASTION, all the datapath checkers and the FIFO checkers were evaluated using this approach.

#### 3.4.3 Fault Simulation of the Functional Test

Finally, the stuck-at fault coverage of the functional test for the NoC router is measured by a fault simulator belonging to the framework. As experimental results show, full fault coverage for the datapath with the test application time of 196 clock cycles is achieved.

#### 3.5 Experimental Results

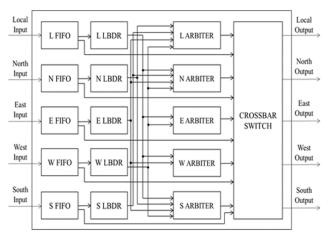

Fig. 3-3 demonstrates the high-level overview of a 5-port 2D NoC router that we have chosen as a target architecture for applying the checkers. The router consists of a datapath and a control part. The datapath is composed of input buffers (implemented as FIFO), one for each input port, a crossbar switch and an output buffer for each output port. The control part contains routing units, arbiters and FIFO control. For the routing unit of our target architecture, we have opted for Logic-Based Distributed Routing (LBDR) [Tut13], which is considered as a scalable solution compared to routing tables. As an arbiter, round-robin arbitration was implemented.

Figure 3-3. High level architecture of the NoC router

#### 3.5.1 Checker Qualification/Minimization for LBDR/Arbiter

The pseudo-combinational circuit for ELBDR has 11 input bits, as mentioned in the previous section, thus the exhaustive set of stimuli presents  $2^{11}$ =2,048. A filtering scheme based on the following statements was devised:

- if input buffer's empty signal is high, any other input bit is meaningless, and therefore any value is allowed for it;

- if the incoming flit is a header, the destination address has to be valid according to the XY routing and turns restrictions;

- if the incoming flit is a body or tail flit, the previous output values must be valid, they must follow a one-hot fashion, according to XY routing.

This allowed to obtain a valid and complete set of stimuli consisting of 1536 vectors, which forms 75% of the exhaustive set. The run-time for generating the stimuli was 2 seconds. (All the experiments were carried out on an Asus ux32vd-r4002v computer with a 1.9 GHz Intel Core i7-3517U processor and 10 GB RAM.) Table 3-1 lists the obtained minimized set of three checkers for the LBDR. Reducing the set of checkers to the three most significant ones allows to limit the area overhead to 78.57% over the ELBDR circuit, far lower than 185.71% imposed by the initial non-minimized set of checkers, while the CEI and FC remain at 100%.

Table 3-1: A minimized list of checkers for the LBDR

|   | Checkers for Routing Logic (LDBR) |                                                                                                                                                                                    |  |  |

|---|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1 | Valid LBDR<br>output              | If there is a request to the routing logic (the corresponding input buffer is not empty), LBDR has to compute at least one valid output direction (according to XY routing).       |  |  |

| 2 | No LBDR<br>output                 | If no flit arrives (the corresponding input buffer is empty), all the output port signals of LBDR should remain zero.                                                              |  |  |

| 3 | Single<br>LBDR<br>output          | If the corresponding input buffer is not empty (there is a request to LBDR), because of using XY routing, at most only one output port signal of the LBDR logic can become active. |  |  |

Similarly, Table 3-2 lists the minimized set of two checkers for the Arbiter that was obtained from an initial set of 28 verification checkers by applying the checker qualification and minimization framework.

Table 3-2: A minimized list of checkers for the Arbiter

| Ch | Checkers for Arbiter logic |                             |  |

|----|----------------------------|-----------------------------|--|

| 4  | Valid Grant                | If there is a request from  |  |

|    | output                     | LBDR, arbiter has to assert |  |

|    |                            | at least one of the grant   |  |

|   |                             | signals for the corresponding output direction.                    |

|---|-----------------------------|--------------------------------------------------------------------|

| 5 | Invalid<br>arbiter<br>State | State variable of the arbiter FSM has to respect one-hot encoding. |

# 3.5.2 Fault Injection Experiments for the FIFO

Table 3-3 lists the set of 8 checkers generated from the verification assertions for the FIFO control part. The checkers were evaluated by the fault injection tool of the framework. A set of input stimuli for the FIFO was devised, aiming to cover all the possible situations for the control logic. The following conditions were considered in the pattern generation procedure:

- reset condition;

- filling the FIFO, followed by reading up to empty condition;

- smooth traffic condition, i.e. concurrent writing and reading operations, avoiding the FIFO to get full;

- idle condition, i.e. write and read enable signals low, during reading and writing operations, in different conditions of fulfillment of the buffer.

100% CEI and FC were achieved on the control part of the FIFO, considering the patterns derived from the previously listed conditions, amounting to 134. Run time for the experiment was 0.06 s. No false positives were encountered in this experiment.

Table 3-3: Checkers for the FIFO Control Part

| Che | Checkers for FIFO control part        |                                                                                                                                                                    |  |

|-----|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6   | Reset                                 | Whenever reset goes high, at the next clock cycle empty flag should be high (reading and writing pointer are reset to the same value).                             |  |

| 7   | Flags<br>checkers                     | Empty and full flags should never be high at the same time. Whenever the defining condition occurs, the corresponding flag should go high at the next clock cycle. |  |

| 8   | One-hot pointers checkers             | Reading and writing pointers have to respect one-hot encoding.                                                                                                     |  |

| 9   | Registers<br>enable<br>DMR<br>checker | Duplication and comparison for the logic enabling the writing operation in data registers.                                                                         |  |

| 10 | Reading<br>pointer<br>update<br>checker 1 | Whenever read enable is high and the FIFO is not empty, at the next clock cycle the reading pointer should be updated.               |

|----|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 11 | Reading<br>pointer<br>update<br>checker 2 | If either read enable is low<br>or the FIFOis empty, at the<br>next clock cycle the<br>reading pointer should<br>preserve its value. |

| 12 | Writing<br>pointer<br>update<br>checker 1 | Whenever write enable is high and the FIFO is not full, at the next clock cycle the writing pointer should be updated.               |

| 13 | Writing pointer update checker 2          | If either write enable is low<br>or the FIFO is full, at the<br>next clock cycle the<br>writing pointer should<br>preserve it value. |

Table 3-4 lists the set of 3 additional checkers which were included in order to achieve the full fault coverage after fault injection experiments for the control part identified uncovered faults in the interconnections of control part modules.

**Table 3-4: Control Part Infrastructure Checkers**

|    | Control Part Infrastructure Checkers |                               |  |  |  |

|----|--------------------------------------|-------------------------------|--|--|--|

| 14 | FIFOs read                           | Logic producing read          |  |  |  |

|    | enable                               | enable signals for the        |  |  |  |

|    | DMR                                  | FIFOs (5 OR gates) is         |  |  |  |

|    | checker                              | duplicated, then real and     |  |  |  |

|    |                                      | duplicated outputs are        |  |  |  |

|    |                                      | compared.                     |  |  |  |

| 15 | Output                               | Logic producing enable        |  |  |  |

|    | registers                            | signals for the output        |  |  |  |

|    | enable                               | registers (5 OR gates) is     |  |  |  |

|    | DMR                                  | duplicated, then real and     |  |  |  |

|    | checker                              | duplicated outputs are        |  |  |  |

|    |                                      | compared.                     |  |  |  |

| 16 | Flit type                            | Flit type field of a flit has |  |  |  |

|    | LBDR                                 | to respect                    |  |  |  |

|    | error                                | one-hot encoding.             |  |  |  |

# 3.5.3 Checkers for the Datapath

In order to fully cover the faults in the NoC datapath two types of concurrent checkers were introduced (listed in Table 3-5). First, for each input port an even parity bit is included, whereas each output port has a checker

evaluating the even parity. Second, since fault injection experiments for the whole router identified undetected faults within the crossbar multiplexers, dedicated checkers for the crossbar were devised.

Table 3-5: Checkers for the NoC Datapath

| Dat | Datapath Checkers |                             |  |  |  |

|-----|-------------------|-----------------------------|--|--|--|

| 17  | Even parity       | An even parity bit is       |  |  |  |

|     | checker           | computed and                |  |  |  |

|     |                   | added to data entering each |  |  |  |

|     |                   | input                       |  |  |  |

|     |                   | port, which is later        |  |  |  |

|     |                   | evaluated before            |  |  |  |

|     |                   | data leaves the router      |  |  |  |

|     |                   | through any of              |  |  |  |

|     |                   | the output ports.           |  |  |  |

| 18  | Crossbar          | Crossbar MUXs are           |  |  |  |

|     | checker           | duplicated, then            |  |  |  |

|     |                   | real and duplicated outputs |  |  |  |

|     |                   | are                         |  |  |  |

|     |                   | compared.                   |  |  |  |

# 3.5.4 Putting It All Together

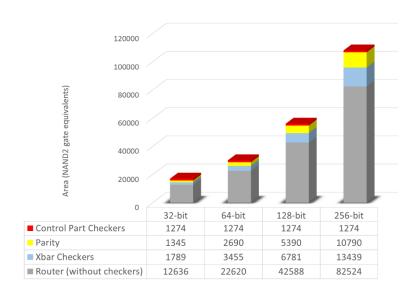

Fig. 3-4 reports the area overhead required by the checkers for routers of varying bitwidth (from 32 bits to 256 bits). It can be observed from the Figure that the required area for the control part checkers stays constant while the overhead area of datapath checkers (parity and crossbar) grow proportionally to the router size.

Figure 3-4. Area consumption for different datawidhts

The same trend is revealed in Table 3-6. It can be seen that if datapath checkers are included then the required area overhead would be in the range of 31-35%. Whereas, the control part checker circuitry demands significantly less area, especially for larger bitwidths.

Table 3-6: Overhead Area for Different Datawidths

|                         | 32-bit | 64-bit | 128-bit | 256-bit |

|-------------------------|--------|--------|---------|---------|

| Router (w/o checkers)   | 12636  | 22620  | 42588   | 82524   |

| Control part checkers   | 1274   | 1274   | 1274    | 1274    |

| Xbar Checkers           | 1789   | 3455   | 6781    | 13439   |

| Parity                  | 1345   | 2690   | 5390    | 10790   |

| Area overhead           |        |        |         |         |

| (contr. p. checkers), % | 10.08  | 5.63   | 2.99    | 1.54    |

| Area overhead           |        |        |         |         |

| (all checkers), %       | 34.88  | 32.80  | 31.57   | 30.90   |

However, when combining the control part checkers with the functional test presented in Section 4, full fault coverage for the NoC router can be achieved with a minor area overhead. As it has been shown by experiments in [Tut21] a functional test of length K=196 clock cycles will achieve FC=100% within the NoC router datapath. Thus, combining the concurrent checkers for the control with functional test results in a cost-effective solution.

#### 3.6 Section Conclusions

We have developed a framework for formal qualification of checkers and for minimizing the overhead area with the given fault coverage constraints. The goal is to achieve low-latency, low area overhead checkers for network on chip routers. In addition, we propose complementing the concurrent checkers with functional test to be applied as a periodic routine during the idle periods in router operation.

The framework together with the corresponding methodology has been successfully applied to a realistic case-study of a fault tolerant NoC router design. The case study shows that combining concurrent routers with functional test allows reducing the area overhead of the checkers from 31-35% down to 1.5-10% without sacrificing the fault coverage.

# 4 Fault Extraction in Self-Reconfiguring IEEE 1687 Networks

#### 4.1 Introduction

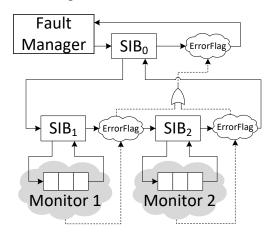

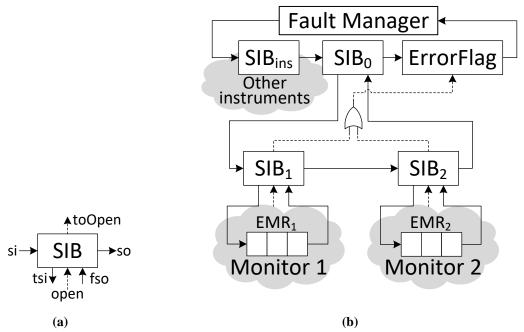

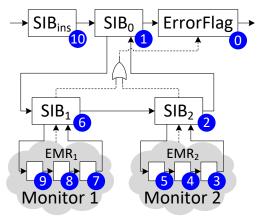

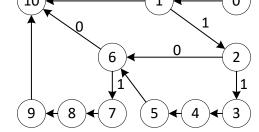

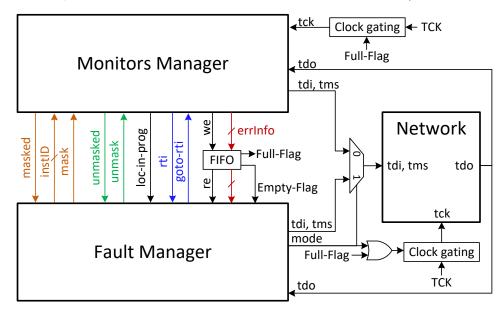

The advances in semiconductor technology have enabled production of integrated circuits (ICs) with very small transistors. As smaller transistors are more sensitive to environmental conditions such as radiation or voltage and temperature fluctuations, it has become crucial to address reliability by handling errors that occur when the IC is in operation [Bo05]. One way to address reliability issues is to embed instruments capable of detecting errors [Su07]. Such instruments can be connected via a fault monitoring network to a fault manager that makes decisions based on the collected error data. In this article, we consider two types of latency in the fault monitoring network:

- fault detection time: the time interval between detection of an error by a monitoring instrument and when the fault manager gets aware of presence of errors in the system, and

- *fault localization time*: the time it takes between detection of fault(s) by the fault manager and when the fault manager identifies the faulty resource(s) and extracts the error code(s) reported by the respective monitoring instrument(s).

It is important that the latency in a fault monitoring network is kept low, as the earlier the fault manager identifies the faulty resources, the faster it launches recovery actions. Moreover, the latency should be deterministic to let designers of a system better assess its reliability.