#### INFORMATION AND COMMUNICATION TECHNOLOGIES

#### COORDINATION AND SUPPORT ACTION

## **EUROSOI+**

# **European Platform for Low-Power Applications on Silicon-On-Insulator Technology**

Grant Agreement no 216373

## D2.2 Monthly Publication of Electronic Newsletter Collecting the Main Advances of SOI Technology

(Updated Version 30/06/11)

Due date of deliverable: 30-06-2011 Actual submission date: 30-06-2011

Start date of project: 01-01-2008 Duration: 42 months

Project coordinator: Prof. Francisco Gámiz, UGR

Project coordinator organisation: University of Granada, Spain Rev.1

| Project co-funded by the European Commission within the Seventh Framework Programme (FP7) |                                                                                       |   |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|--|

| Dissemination Level                                                                       |                                                                                       |   |  |

| PU                                                                                        | Public                                                                                | X |  |

| PP                                                                                        | Restricted to other programme participants (including the Commission Services)        |   |  |

| RE                                                                                        | Restricted to a group specified by the consortium (including the Commission Services) |   |  |

| CO                                                                                        | Confidential, only for members of the consortium (including the Commission Services)  |   |  |

## **Table of contents**

| 1 Introduction                                | 3 |

|-----------------------------------------------|---|

|                                               |   |

| 2 EUROSOI Newsletters (June 2008 — June 2011) | 4 |

#### 1.- Introduction.

The EUROSOI Newsletter was born in June 2008 following the efforts that the EUROSOI network is making to improve its work and with the dedication that has been shown thus far. The aim of this monthly publication is to collect and summarize the main advances and achievements of the SOI technology.

The Newsletter is organized in different sections covering a wide variety of topics such as international SOI events, industrial news, workshop announcements, outstanding features... hence showing the progress and steps forward of the network, whose ultimate goal is to become an open platform for all the SOI community. During these past months the EUROSOI Newsletter has become a cornerstone of the network since it has been in most cases the best stand from which the call for cooperation and development of SOI material have been performed.

In a network there is nothing more important than keeping in touch with colleagues, and we are very proud to state that our Newsletter is reinforcing every month the idea of converging efforts that allows each of us to become aware of the great capacity to succeed we all share.

# **EUROSOI Newsletters**

(June 2008 — June 2011)

THEMATIC NETWORK ON SILICON ON INSULATOR TECHNOLOGY, CIRCUITS.

# EUROSOI

# Newsletter

VOLUME I

#### IN THIS NUMBER:

**Editorial** 1-4

**EUROSOI+** fundings for exchanges

Emerging materials on the Roadmap for silicon-based IC systems

**AMD** unveils three chips for embedded systems

AMD Launches 2 **World's First** x86 Triple-**Core Proces**sors

Honeywell **Announces New High Temperature Analog Silicon** Chip

**Timing not** right for 450mm

**EUROSOI 2009 3** Workshop

**IBM Energy-Efficient Ser**vers

Calendar

## **EDITORIAL**

Francisco Gámiz Professor Univ. Granada (Spain)

Ten years ago, Prof. Sorin Cristoloveanu provided me with the opportunity to convene the European Siliconon-Insulator community in Granada. That was the beginning of a very long friendship. As a tireless scientist, a great pioneer and a man with a view to the future. Prof. Cristoloveanu thought it was the right moment to do something about SOI. Silicon bulk technology was approaching its limits and SOI technology was identified by the International Semiconductor Industry as a good candidate for the following years. Wideranging efforts to research this technology had been made since the sixties in labs all over Europe, even when it was thought that SOI technology was no more than a niche for some romantic and over-optimistic "troubadours".

With the city of Granada and its Alhambra palace as witnesses, we organised, in October 2000, a rather informal and lively meeting, the main objective of which was to discuss the place of SOI technology in Europe. Many key players in the European SOI scene have joined us since then: Prof. Denis Flandre, Prof. Cor Claeys, Prof. Jean-Pierre Colinge, Dr. Carlos Mazuré and many others. It was the first time the word EUROSOI entered our minds. After two days of fruitful discussion, the following conclusions were drawn: a) The posi-

tion of European industry with regard to SOI/SOS technology was weak, in spite of the fact that more than 20 research groups (from academia and research labs all over Europe) were successfully working on SOI technology with a very broad scope, from materials to final user applications; b) The main reason for this was the wide gap between industry and research centres with regard to SOI; c) There existed many commercial applications (RF, wireless communications, high temperature, etc.) where European industry could have a dominant position if the appropriate technology were provided. d) It was necessary to take advantage of the previous experience of research groups and to join forces to maximise the synergy between individual skills, thus achieving the best global results.

In order to improve the situation, it was necessary to work towards a European initiative aimed at organising the existing research work on SOI topics and supporting all the actions that might guide the European semiconductor industry to a dominant position in SOI-based applications. This was the birth of the EUROSOI network, with the sponsorship and support of the European Commission.

JUNE, 2008

Now, after several years of intense work and networking, the situation is different to that of those early days. In 2003, the European Commission supported the creation of a European Network on Silicon on Insulator Technology, Devices and Circuits, whose main goal was to create a discussion forum for the exchange of ideas and results on the topic of Silicon-On-Insulator technologies in Europe, and to facilitate the synergy between research groups which would enable the use of Silicon-On-Insulator (SOI) technology as an effective tool to push the limits of CMOS and prepare for post-CMOS.

(continues on page 4)

#### **ANNOUNCEMENT**

EUROSOI+ fundings for exchanges aimed at scientists in order to enhance collaborations and information exchange.

EUROSOI+ will fund exchanges in terms of travelling and research visits for scientists (students and senior scientists) in order to enhance collaborations and information exchange. Priority will be given to visits involving an industrial partner to allow a better integration of the European industry in the Network.

Applications must be received

before June 15th, including a short CV, an invitation letter from the institution to be visited and a comprehensive description of the visit (purpose, destination, duration, budget, etc). Further information can be found at the EUROSOI web site http://www.eurosoi.org.

#### **NEWS**

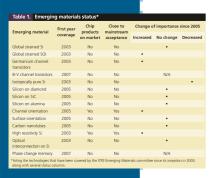

## Emerging materials on the Roadmap for silicon-based IC systems

Emerging materials status

In general, emerging materials will augment silicon transistor technology by providing enhanced speed, lower-power consumption, improved heat dissipation, improved memory capacity/data retention, or added RF/analog functionality while maintaining the large scale integration capability of CMOS. The augmentation of the silicon starting material need not be entirely siliconbased as long as CMOS system improvement is the end goal. As an example, the integration of III-V compound optoelectronics on silicon (Si) for enhanced bandwidth for I/Olimited CMOS technologies would be considered an emerging material application.

The definition of emerging materials is as follows: novel starting materials, structures, and processing methodologies that will enable anticipated roadmap requirements and enhance silicon-based CMOS technology.

The International Technology Roadmap for Semiconductors (ITRS) Emer-

ging Materials Committee has now tracked technologies for close to four years. In that time, some technologies have demonstrated progress towards mainstream applications (i.e., have moved beyond 'emerging' status); some technologies have continued to stay active but have not moved into mainstream applications; and some technologies have shown some loss of momentum.

[Source: Solid State Technology]

#### **NEWS**

## AMD unveils three chips for embedded systems

"The latest chips will make it easier for system designers to use their existing AM2 board designs for single core chips",

AMD said.

Advanced Micro Devices has launched three dual-core processors for embedded systems that span entry-level networked storage systems to telecommunication products, digital signage, and point-of-sale, gaming, and kiosk systems.

The AMD Athlon X2 dualcore processors, models 3400e, 3600+, and 4200+, run at low-power envelopes of 22 watts for the 3400e and 35 watts for the other two products. The latest chips are AM2 socket-compatible, which will make it easier for system designers to use their existing AM2 board designs for single-core chips, AMD said.

The processors are designed to be paired with the AMD M690E chipset. They also can be combined with Broadcom chipsets, including the HT-2100 and HT-1000. The new products are expected to ship in the second quarter and will

have a five-year life cycle.

Along with the new chips, AMD unveiled a reference design kit for the Storage Bridge Bay 2.0 specification based on the AMD Athlon processor. The SBB defines mechanical, electrical, and low-level enclosure management requirements for a slot that supports storage controllers from a variety of independent hardware and system vendors.

[Source: EE Times]

#### NFWS

## AMD Launches World's First x86 Triple-Core Processors

AMD announced the availability of AMD Phenom<sup>TM</sup> X3 8000 series triple-core processors, providing gamers and digital media enthusiasts with exceptional performance at mainstream price points.

AMD Phenom X3 processors are designed to improve multi-threaded application performance over dual-core processors at the same clock speed.

As the world's only triplecore x86 processor, AMD Phenom X3 processors bring multi-core technology to a broader audience in search of desktop PCs that easily handle today's digital entertainment workloads.

"In 2007, AMD committed to delivering AMD Phenom triple-core processors in Q I 2008 and today the company makes good on that promise," said Bob Brewer, "AMD understands that today's PC applications are best accelerated with a range of multi-core products from quad- to tripleto dual-core processors, and that's why we now deliver the broadest multi-core desktop lineup in the industry."

[Source: AMD]

## Honeywell Announces New High Temperature Analog Silicon Chip for Aerospace and Deep Drilling

#### **Operations**

# Honeywell

Honeywell announced that its Aerospace business has unveiled a new high temperature Silicon On Insulator electronic component with dualapplications in the aerospace and oil industries.

The chip can withstand high temperatures and be used in aircraft engines or in deep drilling operations to enhance the nation's energy supply. It was designed and developed as part of Honeywell's diverse suite of aerospace and industrial electronics.

"The aerospace and oil and natural gas industries each require high performance components that operate over wide temperature ranges," said Brian Link, Business Director, Honeywell Defense and Space. "Honeywell's Silicon On Insulator technology is critical for instrumentation and sensor measurements in these environments. The dual precision chip will be used in high temperature zones on jet engines for instrumentation

and control, as well as operating in temperatures up to 225 degrees C and at depths exceeding 20,000 feet in deep drilling operations.

Honeywell's high temperature electronics improve system reliability and help to reduce operators' equipment downtime and weight.

Honeywell's new high temperature dual precision operational chip model HTOP01 was developed with several industrial partners as part of the U.S. Department of Energy's Deep Trek Program.

[Source: PRNewswire]

#### **NEWS**

## Timing not right for 450mm, says AMD's Grose

Speaking at The ConFab in Las Vegas, AMD's Doug Grose said that the timing is not right for a transition to 450mm wafers, and suggested that the concept of the industry historically moving to a new wafer size every ten years was flawed.

Describing the present macroeconomic picture as "pretty bleak," Grose gave a nod to the cost that equipment and material suppliers must carry in making a wafer size change a reality.

"Distribution of profit across our industry is really not equitable.

We all know that we can't create shareholder value without the equipment and software and materials suppliers and neither can they," Grose said. "So what sense does it really make to pursue an industry strategy that's not really a win-win for everybody? The last thing in the world we need right now is to starve our suppliers. That's obviously like shooting ourselves in the foot."

Grose estimated that 4% of the industry's 25%-20% annual gains in productivity really come from increased wafer size. The rest

comes from smaller die sizes, process improvements and obviously improved yields, defect density, etc. "The cost to the industry of driving to get that 4% a year is going to be very, very large. It seems inevitable we're going to have to make that move because the benefits are significant," he said, and asked: "But when, and how do we get the most from 450mm once we do make that move?"

[Source: Solid State Technology]

"what sense does it really make to pursue an industry strategy that's not really a winwin for everybody?", said Grose

#### **EUROSOI NEWS**

## First Announcement of the EUROSOI Workshop 2009

A year on, as is tradition since 2005, and for the fifth consecutive time within the framework of the EUROSOI Network, a new edition of the EUROSOI Workshop will take place next January. Next year 2009 event will be held in Chalmers, Sweden.

EUROSOI Workshop is an international forum to promote interaction and exchanges between research groups and industrial partners involved in SOI activities all over the world.

EUROSOI covers recent progress in SOI technologies and will be of interest to materials and device scientists, as well as to process, circuits and applications oriented engineers.

Complete information about the 2009 Workshop will soon be avai-

lable at the EUROSOI web site http://www.eurosoi.org

We are just at the beginning of this exciting stage.

The challenges are many and the road not easy

## **EDITORIAL** (cont.)

Today, the EUROSOI network comprises more than 30 partners from all over Europe, with expertise in all fields of SOI technology. The EU-ROSOI network has already made possible the achievement of a large part of this objective by successfully organising and bringing to fruition during the last three years a significant number of events such as the EUROSOI roadmap and state of the art documents, workshops, training events and scientific exchan-

In the framework of the new FP7, a new project, EURO-SOI+ has been launched, started on January 1st 2008. The first goal of the new project is the upgrading and maintenance of this important forum, providing updated versions of the State-of-the-Art report and Roadmap, facilitating scientific exchanges between partners, organising works-

hops and later, using it as a launch-pad for other important objectives:

- •To create a durable European School of SOI Technology.

- •To foster and co-ordinate the initiatives and activities required to successfully face up to some of the challenges identified and listed in the EUROSOI Roadmap.

- •To co-ordinate the development of a research-dedicated platform in order to address circuit design aspects, focusing on the advantages of SOI for Low Power applications. In two to three years, this platform will provide, through its integration in EUROPRACTI-CE, prototyping and Multi-Project-Wafers (MPW) in SOI open to European research groups and Fabless Semiconductor companies (SMEs) using the LETI SOI process.

We are just at the beginning

of this exciting stage. The challenges are many and the road not easy, but with the help of all of you, I am sure we will be successful, and this will also mean success in rejuvenating the old Europe.

This is the first of what I hope will be a long series of EURO-SOI Newsletters. Periodically this short publication will collect brief announcements and links to advances in SOI technology all over the world. Here, you will also find the steps forward, activities and progress of our/your EURO-SOI Network, whose ultimate goal is to become an open platform for all our people, the SOI people. To this end, I sincerely invite all of you to contribute in developing this publication.

I wish you an interesting and fruitful SOI adventure. Good luck

#### **NEWS**

## IBM Unveils Three Energy-Efficient Servers Powered by Quad-Core AMD

## Opteron<sup>TM</sup> Processors

AMD announced growing industry support for the Quad-Core AMD Opteron  $^{\text{TM}}$ processor among global OEMs continues with IBM's launch of three updated System x<sup>™</sup> servers. Designed to address customer priorities such as energy efficiency, performance, scalability, and virtualization, the Quad-Core AMD Opteron processorbased servers from IBM offer an exceptional power-efficient platform for today's most demanding datacenters.

"Quad-Core AMD Opteron processor-based servers deliver energy-efficiency even in the context of satisfying IBM's most demanding highperformance computing solutions," said Randy Allen, senior vice president, Computing Solutions Group, AMD. "Datacenter managers are increasingly seeking a balance of performance, energyefficiency, and advanced virtualization functionality in order to optimize server resources amidst skyrocketing power, cooling and space costs. The Quad-Core AMD Opteron processor is at the forefront of addressing this new real-world definition of datacenter performance."

"IBM continues to deliver innovation and choice in the x86 market with today's introduction of System x servers based on AMD's new Quad-Core processors," said James Northington, vice president, IBM System x. "The new System x3755 allows clients to grow the system along with their business, affordably scaling from the standard 2 socket system to 3 and 4 socket configurations while delivering industry leading price and performance."

[Source: AMD]

Thematic network on silicon on insulator technology, devices and circuits.

Mail: eurosoi@ugr.es

The EUROSOI network embraces a broad range of research areas related to Silicon-On-Insulator technology (from materials to enduser electronic applications in traditionally strong European industrial sectors such as automotive, communications, space). EURO-SOI aims at federating the existing research work on SOI topics and at providing an appropriate communication channel between academic groups and industrial production centres.

# **CALENDAR**

#### - MIGAS International Summer School

Autrans-Grenoble, France. June 28th - July 4th, 2008

- European School On Nanosciences & Nanotechnologies

Grenoble, France.

August 24th - September 13th, 2008

- Third SINANO Device Modeling Summer School

Bertinoro, Italy.

September 1st - 5th, 2008

- 38th European Solid State Device Research Conference and 34th European Solid State Circuits Conference

Edinburgh, United Kingdom.

September 15th - 19th, 2008

- 2008 IEEE International SOI Conference

Hudson River Valley

New York, USA

October 6th - 9th, 2008

THEMATIC NETWORK ON SILICON ON INSULATOR TECHNOLOGY, DEVICES AND CIRCUITS.

# EUROSOI

Newsletter

JULY, 2008

#### VOLUME II

# IN THIS NUMBER:

Global Industry I Survey of SOI

Lecturers List | I | Elaboration

SOI survey 2 analysis

Intel explores 3 floating-body cells on SOI

Selete Achieves 3 5 GHz Pulses on Silicon Photonics IC

EUROSOI 2009 3 Workshop

CISSOID new 4

Logic Family

MIGAS 4 Summer School

Calendar 5

#### **NEWS**

#### GLOBAL INDUSTRY SURVEY RESULTS REFLECT STRONG INTEREST

#### IN SOLFOR LOW POWER AT MAINSTREAM TECHNOLOGY NODES

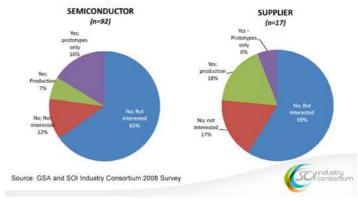

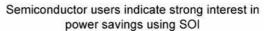

The Global Semiconductor Alliance (GSA), an organization focused on accelerating the growth of the global semiconductor industry, and the SOI Industry Consortium, a group of leading companies throughout the electronics industry focused on accelerating silicon-oninsulator (SOI) innovation into broad markets, have announced the completion of a global study focused on SOI.

Over 100 semiconductor companies involved in the design of integrated circuits responded to the survey about their needs and perceptions of SOI. Eightyseven percent of respondents indicated that they are interested in evaluating or are already using SOI, particularly for power savings at mainstream technology nodes starting with 90 nanometers. The survey also

confirms the need to educate the market on available solutions, methodology and training across the global ecosystem, points that are being addressed by the SOI Industry Consortium.

"We are pleased to field the

study which will gauge perceptions of semiconductor companies on SOI technology," said Jodi Shelton, GSA co-founder and executive director. "The collaboration on this survey with the SOI Industry Consortium provides us with a platform

## Have you ever designed, supported or manufactured SOI chips?

87% of all respondents are interested or have used SOI

#### **EUROSOI ANNOUNCEMENT**

## Distinguished Lecturers list elaboration

EUROSOI+ is now elaborating a complete list comprised by experts in the

SOI field (fabrication, materials, devices, circuits, simulation, etc). This list will be specially useful to prepare all the training events in the next EUROSOI+ events.

See the EUROSOI web site for downloading the file that must be filled out and sent back before July 9th.

Do not hesitate to include yourself if you are considered as an expert in any specific SOI topic.

You can also:

- I.- Include people that do not belong to the EUROSOI network or currently working out of Europe

- Widely broadcast this announcement to other colleagues out of the network.

from which we can determine industry education for the global community on SOI potential alternatives and benefits."

"The results of the study show that there is an interest in SOI throughout the greater chip design, manufacturing and electronics community," notes Horacio Mendez, executive director of the SOI Industry Consortium. "Respondents indicate that one of the main reasons they're looking at SOI is to solve low-power challenges."

[Source: SOI industry consortium & GSA]

#### **NEWS ANALYSIS**

## Semiconductor companies eye SOI advantages and obstacles

"The SOI

Consortium is

actively working to

resolve all of the

issues that survey

respondents cited

as obstacles",

Méndez said.

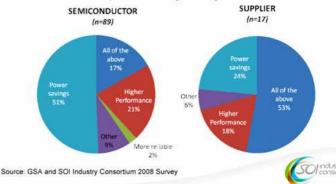

Fabless semiconductor suppliers are interested in silicon-on-insulator (SOI) because the technology allows power savings, but they remain concerned about costs, lack of silicon intellectual property (IP), and availability of EDA tools, according to a survey conducted by the Global Semiconductor Alliance (GSA) in cooperation with the SOI Consortium. The survey identified obstacles that must be overcome for wider SOI adoption.

The survey, available now on the GSA web site, compiled responses from 110 industry respondents holding positions such as CEO, CTO, director of engineering, and vice president of engineering. 94 are from semiconductor suppliers, design services providers, and systems companies. While several IDMs are represented, most of the semiconductor suppliers are fabless. 16 respondents are from supplier companies including IP, EDA, wafer foundries, equipment providers, and back-end service providers.

On the plus side, the survey found that 23 percent of respondents already use SOI. Another 64 percent don't use it today but are "interested." Power savings is seen as the most significant advantage, with many respondents willing to accept a higher total product cost to save power. Respondents expressed interest in SOI at conventional process nodes, such as 90 nm and 65 nm, in addition to advanced process nodes.

On the other hand, some respondents cited cost and lack of design knowledge as obstacles to SOI adoption. 56 percent were unsure whether their EDA tools are ready for SOI, and 12 percent said they are not, even though SOI advoca-

tes say that no significant tool changes are needed. Nearly half of the respondents noted that SOI intellectual property (IP) libraries are still inadequate or completely missing from the design flow today.

SOI, which electrically insulates the silicon active layer from the underlying substrate, has been adopted primarily by IDMs and used in fairly narrow niches such as high-end CPUs, and high-voltage and radiation-hard applications. The SOI Consortium is working to build an IP, EDA and foundry ecosystem that would

# What is the biggest potential advantage of using SOI for your business?

#### What is missing in your design flow for SOI?

## IP topped the list for both users and suppliers

broaden the adoption of SOI and bring it into the IC design mainstream.

The SOI Consortium is "actively working" to resolve all of the issues that survey respondents cited as obstacles, Mendez said. One approach is education. Mendez said that the consortium is organizing worldwide tutorials that show designers how to work with SOI. "There's a history effect," he said. "It's not tricky, it's just different. In a half day or so we can bring people up to speed."

[Source: SCDsource]

## Intel explores floating-body cells on SOI

At the 2008 Symposium on VLSI Technology in Hawaii, Intel Corp. revisited its research on floating-

body cells (FBCs) for advanced cache designs in microprocessors.

The big question is whether Intel is finally endorsing silicon-on-insulator (SOI) technology, as the company will describe the world's smallest FBC-based planar device on SOI for possible use at the 15-nm node. In related paper, Intel is also expected to describe new adaptive circuit techniques for SRAM cache cells. Both technologies are in R&D and still in the lab, it was noted

Waiting in the wings in the race towards

FBCs--or sometimes called floating-body RAMs (FB-RAMs)--is rival Advanced Micro Devices Inc. (AMD). Two years ago, AMD licensed an embedded FBC technology from Innovative Silicon Inc. (ISI).

For years, FBC has been touted as an alternative to conventional cache memory, because current capacitor-based technology is running out of gas. FBC is a candidate for increased memory density, compared to the standard six transistor (6T) cache memory that is used on all microprocessors today.

"In a standard DRAM, there is a capacitor and a transistor," according to ISI. "The capacitor stores the logic state, I or 0, and the transistor provides the rest of the circuitry access to the capacitor. To read a

DRAM memory cell, the transistor is turned on and the charge on the capacitor is allowed to flow onto a bitline, creating a small voltage which can then be detected."

Jeff Lewis, vice president of marketing at ISI (Santa Clara, Calif.), warned that there are some major issues cropping up with the capacitor in DRAMs, prompting the need for a new architecture. "Capacitor scaling is becoming almost impossible," Lewis said in a recent interview at the Design Automation Conference (DAC) in Anaheim, California.

[Source: EE Times]

#### **NEWS**

### Selete Achieves 5 GHz Pulses on Silicon Photonics IC

Optical interconnects using an optical fiber and on-chip light guide are being developed as interconnects in servers, circuit boards, and on silicon chips, leveraging advantages such as higher speed transmission and lower power consumption. To that end, the Selete (Tsukuba, Japan) consortium said it has succeeded in transmitting a 5 GHz pulse waveform through a 4 mm light guide produced on a silicon IC. The consortium made the announcement at the recent Selete Symposium 2008.

The light guide serves as an optical interconnect using silicon as the base material, SiON as the core light guide, and SiO2 for the cladding layer. It connects to a light-emitting diode (LED) or laser diode made of a compound semiconductor. A Schottky barrier diode with a silver electrode is used as the photodetector. The light guide layer is produced on a silicon on insulator (SOI) wafer that is attached to the wafer holding the logic circuits, both with face-to-face electrodes.

Connections between the light-guide chip and logic IC are created with a gold-tin (Au-Sn) alloy, which allows for alignment of both electrodes. A previous proposal included optical connections between an optical interconnect wafer and circuit wafer, but that approach was deemed

unrealistic because of the difficulty of aligning both light guides.

In the technology developed by Selete, bump electrodes on the silicon wafer are connected to bumps on a light guide wafer, then the silicon substrate of the wafer with the light guides is etched off. The light guide consists of a SiON layer with a refractive index that is slightly higher than the surrounding SiO2 cladding layer. The refractive index of the silicon layer is ~40% higher than that of SiO2. The silicon core has a higher transmission loss of 1-3 dB/cm, compared with 0.2-0.3 dB/cm for a SiON core.

[Source: Semiconductor International]

#### **EUROSOI NEWS**

## First Call and Web site now available for the EUROSOI 2009 Workshop

EUROSOI Workshop is an international forum to promote interaction and exchanges between research groups and industrial partners involved in SOI activities all over the world. Following the lively experience of the previous meetings in Granada (2005), Grenoble (2006), Leuven (2007) and Cork 2008, EUROSOI 2009 will be held at Chalmers, Göteborg. It

will include oral and poster sessions, outstanding keynote presentations, a training course, a social program as well as ample room for informal discussions. EURO-SOI covers recent progress in SOI technologies and will be of interest to materials and device scientists, as well as to process, circuits and application-oriented engineers.

Information about the 2009 Workshop is now available at the Workshop web site

http://chalmers2009.eurosoi.org

Abstract submission and registration will be available in October.

#### **CHALMERS**

## CISSOID introduce a new High Temperature Logic Family

CISSOID is a Fabless Semiconductor company, leader in High Cissoid Temperature

> Electronics. They develop and sell Integrated Circuits (IC) designed for the highest reliability in the widest range of temperatures. Their products will operate at least from -55° C to +225°C. They have been tested from -200°C to +300°C. The reliability of CISSOID products is based on long years of experience in silicon technologies, design for reliability, assembly techniques and test.

CISSOID products are com-

monly used under extreme conditions and harsh environments, for example in demanding Oil&Gas, Aerospace and Automotive applications.

They enable exploitation of deep oil resources, energy savings in aircrafts and automobiles, optimal exploitation of geothermal resources, etc.

CISSOID proposes a portfolio of High Temperature standard products, such as Voltage Regulators, Voltage References, Clock Generators & Timers, Analog-to-Digital Converters, Amplifiers, High-Voltage MOSFET's and Drivers. Custom solutions can also be developed as an Application Specific Monolithic IC (ASIC) or as a Hybrid multichip assembly solution.

Most of CISSOID's products are built on Silicon-on-Insulator (SOI), a fabrication process that offers tremendous advantages for High Temperature operation and high levels of radiation (Rad-Hard products). Cissoid's products inherit over 20 years of R&D activities in the field of SOI and was the very first company to exploit this technology.

[Source: CISSOID]

#### **EVENTS**

## **MIGAS International Summer School**

This school is addressed to PhD students,

engineers and researchers coming both from the university and from industry of the semiconductors. Through a program based on lessons given by the best international scientists, the participants are given the opportunity of improving their knowledge on state of the art and future nanodevices.

Each session is focused on a different theme, and is managed by a different Scientific

Chair. This year, for its 11th session, MIGAS'08 has been focused on Nanoscale CMOS and Si-based Beyond CMOS Nanodevices.

The scientific programme for this edition was:

- ·Advanced materials, technology and characterization methods for nanoscale CMOS.

- •Novel CMOS architectures.

- •Beyond-CMOS Nanodevices.

- •Innovative Memories.

This year the selected venue was Autrans, a reknown resort, dedicated to alpine and cross-country skiing in winter, and to tourism in summer, located in the Regional Natural Park of the Vercors mountains, 30 km away from Grenoble.

Thematic network on silicon on insulator technology, devices and circuits.

If you want to contribute to the EUROSOI Newsletter, you can email us with any outstanding event, announcement or news

Mail: eurosoi@ugr.es

The EUROSOI network embraces a broad range of research areas related to Silicon-On-Insulator technology (from materials to enduser electronic applications in traditionally strong European industrial sectors such as automotive, communications, space). EURO-SOI aims at federating the existing research work on SOI topics and at providing an appropriate communication channel between academic groups and industrial production centres.

# **CALENDAR**

- MIGAS International Summer School

Autrans-Grenoble, France. June 28th - July 4th, 2008

- European School On Nanosciences & Nanotechnologies

Grenoble, France.

August 24th - September 13th, 2008

- Third SINANO Device Modeling Summer School

Bertinoro, Italy.

September 1st - 5th, 2008

- 38th European Solid State Device Research Conference and 34th European Solid State Circuits Conference

Edinburgh, United Kingdom. September 15th - 19th, 2008 - 2008 IEEE International SOI Conference

Hudson River Valley New York, USA

October 6th - 9th, 2008

- EUROSOI 2009 Workshop

Chalmers University of Technology

Göteborg, Sweden

January 19th - 21st, 2009

http://chalmers2009.eurosoi.org

THEMATIC NETWORK INSULATOR TECHNOLOGY, DEVICES AND

VOLUME III

IN THIS NUMBER:

**E**ditorial

**EUROSOI+** fundings for exchanges

Soitec ultrathin 2 **SOI** wafers

**Nvidia** joins **SOI** Industry Consortium

European School On Nanosciences & Nanotechnologies

First EUROSOI 3 Working **Group Meeting**

**SOI** Inventory elaboration

**EUROSOI 2009 3** Workshop

**Short Course** on Circuit Design

Calendar 5

## **EDITORIAL**

Sorin Cristoloveanu IMEP, Grenoble (France)

About 8 years ago, I was asking myself a number of questions:

- •How prominent will the SOI technology be in the future landscape of the microelectronics?

- •How good are we Europeans in SOI?

- •How many are we all together?

- •Are we collaborators or just competitors?

- •What is the quantitative rate and qualitative impact of the European papers at international conferences, and in particular at the IEEE SOI Conference?

- •Is there any SOI bridge somewhere in Europe?

- •Is there any serious competitor for SOITEC in the arena of SOI wafer fabrication?

- •Why the European industry is so shy and does not go into the SOI chip business?

- •Why then are LETI and IMEC developing such wonderful technologies?

Over a memorable diner in Granada, Paco Gamiz double checked my calculations. They looked accurate. We asked further verification by our good SOI friends: Olivier (Faynot), Denis (Flandre), Steve (Hall), Bruno (Ghyselen), Stefan (Bengtsson), Francis (Balestra), Jean-Pierre (Colinge... from US) and many others (a bottle of wine for everybody I

missed). Anyway, they all confirmed.

The conclusion was straightforward: we need to initiate a European SOI conference. Actually, 'resuscitate' rather than 'initiate'. A European SOI Workshop had been organized already, 2-3 times in Grenoble, in the 80's. It dried out because nobody wished to take the relay in a discipline which, at that time, looked more like a wonderful speculation.

We decided to call this event EuroSOI. Then, Paco said "This is good, as good as any good tapas can be. But just tapas is not enough, we need meat." A few seconds later, the idea of European SOI network emerged. Paco took care of the rest.

We wanted to design a network with whatever ingredients a network can carry. We got in contact with all European SOI groups and the returns rated between positive and enthusiastic. Then we asked benediction

from Brussels and you know by now the rest of the story. The EuroSOI network started officially a couple of years later.

AUGUST, 2008

EuroSOI workshops were organized yearly with reasonable audience, good papers and, even more importantly, a positive gradient in quality. Selected papers were published in extensive versions in Solid-State Electronics. Since the network performed and well, the European Union Commission gave us a 'plus' and accepted to help us to continue. This is how we became, early this year, EURO-SOI+.

We did lots of useful things, at technical and human interaction levels. More can be done and will come next. After reviewing the past and the future, I feel that SOI is like 'Return to Forever'. The problem is that these brilliant musicians do not have a clue about SOI. Why don't we invite them at Euro-SOI?

## Proposals of Scientific

## Exchange Visits funded by EUROSOI+ approved

At the end of May, and in the hopes that this initiative -in addition to increasing the mobility possibilities of scientists will result in an enhancement of collaborations and information exchange, EUROSOI+ launched fundings for scientific exchanges and research visits.

Once the evaluation process finished, and considering that the applications received fulfilled the requirements, the Management Board of EUROSOI decided to approve all of them.

**ANNOUNCEMENT**

Further information and results can be found at the EUROSOI web site http:// www.eurosoi.org.

"The ultrathin SOI

layers may permit

a back gate

underneath the

channel", André-

lacques said.

technologists to create

planar structures with

#### NEWS

## Soitec Ready With Ultrathin SOI Wafers

#### Soited

Soitec (Bernin, France) announced at SEMI-CON West that it has

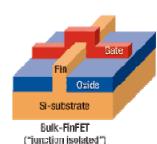

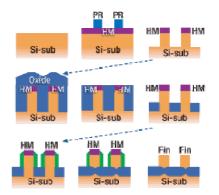

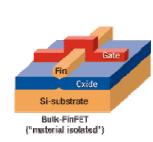

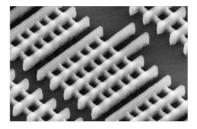

qualified silicon on insulator (SOI) wafers with ultrathin buried oxide (BOX) and silicon layers. The SOI wafers — named XUT+ to describe the ultrathin top silicon and BOX layers — are aimed at both partially depleted (PD) and fully depleted (FD) devices, including multi-gate transistor architectures, such as finFET and trigate, that may play a role at 22 nm and beyond.

CEO André-Jacques Auberton-Hervé said, "The very thin oxide layer allows backside control [of the channel], which is important for limiting the threshold voltage variability. That is a necessity for embedded SRAMs in particular because the threshold variability is being affected by the difficulty in controlling the number of dopants inside the channel. Even one atom can affect the threshold voltage," he pointed out.

The ultrathin SOI layers may permit technologists to create planar structures with a back gate underneath the channel, providing many of the advantages of finFETs while pre-

serving the easier-tomanufacture planar structure, he said.

Also, the thin BOX is required for the SOI-based floating body cell (FBC) memories being developed by Toshiba Corp. (Tokyo), Intel Corp. (Santa Clara, Calif.) and others. At the recent 2008 Symposium on VLSI Technology in Honolulu, Intel researchers presented research on a FBC memory for embedded cache on microprocessors.

[Source: Semiconductor International]

#### **NEWS**

## Nvidia Joins SOI Industry Consortium

Nvidia Corp., the world's largest supplier of graphics processing units, has

joined the SOI Industry Consortium. Joining the organization may mean that the fabless developer of semiconductors is looking forward to design chips that will be made using silicon-on-insulator technology.

"Nvidia is pleased to join the SOI consortium. We are looking forward in participating on the advancement of such an innovative technology and its applications to future products," said John Chen, vice president of technology and foundry operations at Nvidia.

Even though Nvidia is a fabless developer, hence, does not operate its own fabs, it is tremendously interested in rapid development of chip manufacturing technologies and design tools so that to be in position to continue creating leading-edge graphics processing units as well as other chips.

The SOI Industry Consortium, which was formed in October 2007 by a group of companies from across the electronics industry, is aimed at accelerating silicon-on-insulator innovation into broad markets by promoting the benefits of SOI technology and reducing the barriers to adoption.

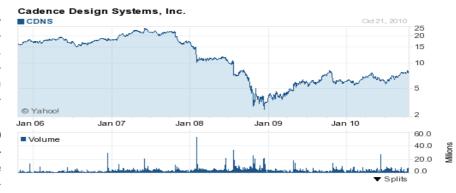

Nvidia brings the SOI Consor-

tium membership to twenty three companies. Other members include: AMD, Applied Materials, ARM, Cadence Design Systems, CEA-Léti, Chartered Semiconductor Manufacturing, Freescale Semiconductor, IBM, Innovative Silicon, KLA-Tencor, Lam Research, Magma Design, Samsung, Semico, Soitec, SEH Europe, STMicroelectronics, Synopsys, TSMC, Tyndall Institute, UCL and UMC.

The SOI Industry Consortium is open to any company, organization or academic institution with an interest in SOI.

[Source: X-bit labs]

Joining the organization may mean that Nvidia is looking forward to design chips that will be made using silicon-on-insulator technology.

VOLUME III PAGE 3

#### **EVENTS**

## European School On Nanosciences & Nanotechnologies

The fifth session of this European school, which will be held this year in Grenoble (France), will begin the fourth week of this month and will last until September 13th.

This 3 weeks course is aimed at providing training for graduate students, postdoctoral and junior scientists from European universities and laboratories in the field of NANOSCIENCES and NANOTECHNOLOGIES in Physics, Biology and Chemistry.

The academic and practical courses cover the elaboration, functioning and characterization of nano-

objects. The program emphasizes the role of laboratory courses (half of the program is devoted to practical work).

The proposed programme is endowed with two key points. The first is interdisciplinarity, since research in Nanoscience demands a combination of various skills in physics, chemistry and biology. Learning the basic knowledge necessary to communicate with other scientific communities is a determining ingredient to create new nano-objects and to connect them to the macroscopic world.

The second point emphasises the role of laboratory courses. In general, summer schools do not address this issue which is, however, of fundamental importance both for basic science and for applications.

The program is structured to highlight the fundamental and technological advances in Nanoelectronics and at the interface between Physics and Biology.

The two sessions will run in parallel but they will share common lectures and praticals.

#### **EUROSOI NEWS**

## First EUROSOI Working Group Meeting

One of the important goals of EUROSOI+ is to boost the exchanges of information about the Fully Depleted SOI Technology developed by LETI (which makes reference to devices that are fabricated on ultra-thin SOI films and coupled with high-K and metal gates).

In this framework, EUROSOI planned the organization of three Working Group Meetings, first of which will be held in Grenoble by October or November. The final date and the list of speakers will be conveniently announced through the next volume of this

Newsletter (September) and also through the EUROSOI website.

All EUROSOI+ beneficiaries will attend these meetings and in addition, different experts from the rest of EUROSOI partners and from Industrial Advisory Board members will also be invited.

The global idea is to organize a technical event with several presentations in order to see:

- •What is available today with regard to LETI FDSOI technology?

- •What would be needed to go further?

## ANNOUNCEMENT

## SOI Inventory list elaboration

EUROSOI is currently elaborating an inventory of SOI training material in order to create a database of books, publications, short courses... that could be useful to synthesize the present SOI knowledge.

You may forward to eurosoi@ugr.es any material that you consider to be outstanding or just indispensable.

This call is open to all EUROSOI members as well as to other members from the International SOI Community.

#### **EUROSOI NEWS**

## First Call of the EUROSOI 2009 Workshop

EUROSOI Workshop is an international forum to promote interaction and exchanges between research groups and industrial partners involved in SOI activities all over the world. Following the lively experience of the previous meetings in Granada (2005), Grenoble (2006), Leuven (2007) and Cork 2008, EUROSOI 2009 will be held at Chalmers, Göteborg. It

will include oral and poster sessions, outstanding keynote presentations, a training course, a social program as well as ample room for informal discussions.

EUROSOI covers recent progress in SOI technologies and will be of interest to materials and device scientists, as well as to process, circuits and application-oriented engineers.

Information about the 2009 Workshop is now available at the Workshop web site

http://chalmers2009.eurosoi.org

Abstract submission and registration will be available in October.

#### **EUROSOI NEWS**

## Short course on Circuit Design

It is becoming urgent to involve design people in next future to work using SOI devices and SOI technology Last January and in the framework of the EUROSOI Workshop held in Cork, it was organized a first short course dedicated to Multi-Gate Silicon on Insulator Technology. The Short Course Lectures were given by world-leading experts and focus on the opportunities offered by Multi-Gate FETs and on the challenges they pose in the field of fabrication, device physics and circuit design.

And now a second short course is being prepared to be held during the EUROSOI 2009 Workshop in Göteborg. One of the main conclusions

of the Workshop held in Cork was that it is becoming urgent to involve design people in next future to work using SOI devices and SOI technology. As a consequence, this second Short Course in Chalmers will be devoted to Circuit Design on SOI substrates.

A final list of lecturers will be announced in September.

The importance and relevance of design is clearly a matter of consideration as can be seen for example in the last number of the Advanced Substrate News which devotes several articles to SOI Design written

by important figures such as Remy Pottier, Kevin Kranen, Tony Bonaccio or Michael White.

Thematic network on silicon on insulator technology, devices and circuits.

If you want to contribute to the EUROSOI Newsletter, you can email us with any outstanding event, announcement or news

Mail: eurosoi@ugr.es

The EUROSOI network embraces a broad range of research areas related to Silicon-On-Insulator technology (from materials to enduser electronic applications in traditionally strong European industrial sectors such as automotive, communications, space). EURO-SOI aims at federating the existing research work on SOI topics and at providing an appropriate communication channel between academic groups and industrial production centres.

# **CALENDAR**

- European School On Nanosciences & Nanotechnologies

Grenoble, France.

August 24th - September 13th, 2008

- Third SINANO Device Modeling Summer School

Bertinoro, Italy.

September 1st - 5th, 2008

- 38th European Solid State Device Research Conference and 34th European Solid State Circuits Conference

Edinburgh, United Kingdom.

September 15th - 19th, 2008

- 2008 IEEE International SOI Conference

Hudson River Valley

New York, USA

October 6th - 9th, 2008

- First EUROSOI Working Group Meeting

Grenoble, France

October-November, 2008

- EUROSOI 2009 Workshop

Chalmers University of Technology

Göteborg, Sweden

January 19th - 21st, 2009

http://chalmers2009.eurosoi.org

THEMATIC NETWORK ON SILICON ON INSULATOR TECHNOLOGY, DEVICES AND CIRCUITS.

SEPTEMBER, 2008

VOLUME IV

# IN THIS NUMBER:

'Pretouch' wireless energy

SOI Inventory

SOI Market 2 Analysis

Symmid Semi- 2 conductor joins SOI Industry Consortium

SINANO Sum- 3 mer School

First EUROSOI 3

Working

Group Meeting

ESSDERC-ESSCIRC Conferences

EUROSOI 2009 3 Workshop

Diversity in 4

MEMS Processing

Short Course 4 on Circuit Design

2008 EURO-PRACTICE Workshop

Calendar 5

## HIGHLIGHT NEWS

## 'Pretouch,' wireless energy: Intel

CTO surveys tech future

brating its 40th anniversary in 2008, and Intel CTO

Justin Rattner devoted his keynote address at the Intel Developer

Forum on Aug. 21st to "what the next 40 years of technology might

look like."

"I'm addressing how we expect to see the gap between human intelligence and machine intelligence close over the next 40 years," said Rattner.

Intel commissioned futurist Ray Kurzweil to describe in a video presentation the quickening pace of technology that "may go exponential in the next few years -- where technology is literally advancing on a moment-by-moment basis." Rattner predicted that CMOS devices would not run out of steam until device designers

switched from using electronic charges to encode information to something like the spin of individual electrons -- an advance Rattner said remains in the distant future.

"If you are using charge to represent information, then CMOS is the most efficient architecture," said Rattner. "So our nearterm focus is on improvements [in] processing."

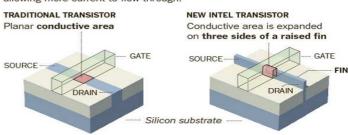

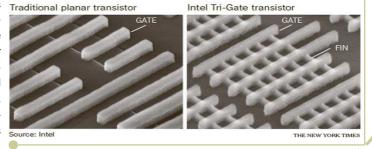

Rather than burying circuitry in bulk silicon, Intel said it is progressing with the development of its Tri-gate transistor, a surface device that wraps a 3-D, high-K metal gate around a vertical thin-film channel, which Rattner said the company might turn to at features sizes below 32 nm.

"The important thing is that all these vertical structures will be on the surface, no longer being built in the bulk," said Rattner. "Once you are on the surface, you could even add III-V materials" like the indium phosphide material Intel uses for its silicon lasers. Beyond CMOS, Rattner predicted that the amount of charge stored for each bit would become so small as device sizes shrink that a new representation for information will be needed -- something besides charge.

"Will future electronic devices be charge-based like they are today for our CMOS technologies, or are they going to rely on some other quantum property like spin? Or might they use some sort of molecular technology where we use molecules to perform the logic function?" Rattner asked.

The Intel CTO also predicted that devices might be possible over the next 40 years that would give robots the ability to behave more like humans. Some devices could endow robots with unique abilities that humans don't have, such as the robotic sense called "pretouch."

Pre-touch "gives robotic hands the ability to sense an object before it touches it," said Rattner. "This is the kind of sense that fish have: Sharks can do it and eels can do it, but if we ever had it as humans we've long since lost that capability."

**ANNOUNCEMENT**

## SOI Inventory list

## elaboration still in progress

EUROSOI is currently elaborating an inventory of SOI training material in order to create a database of books, publications, short courses... that could be useful to synthesize the present SOI knowledge.

You may forward any material that you consider to be outstan-

ding or just indispensable.

This call is open to all EURO-SOI members as well as to other members from the International SOI Community.

[Source: EETimes]

#### **NEWS**

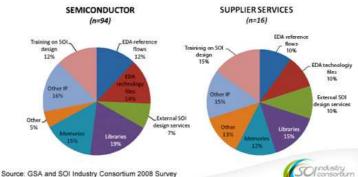

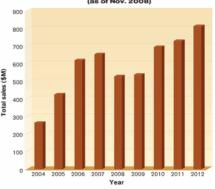

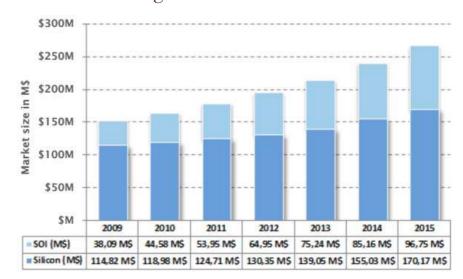

## Market for SOI to reach \$1.1B by 2012, VLSI Research

### reports

Although 2008

sales of SOI are

expected to be

slightly down

from 2007, the

following years

will see doubledigit growths.

Following the general trend of the semiconductor manufacturing ecosystem, sales of SOI (silicon on insulator) technology slowed in 2007 to a 6% year-over-year revenue increase at \$654 million. The single-digit growth pales in comparison to the 46% and greater growth in each of the three previous years, according to to Santa Clara, Califbased VLSI Research Inc. The market research company pointed out that Soitec continues to be the leading force in SOI with a 67% worldwide market

share, followed by number two player Shin Etsu Handotai, which licenses Soitec's Smart Cut technology for the production of its thin SOI wafers.

In 2007, SOI wafers comprised approximately 1.4% of total silicon demand, in terms of area, which is nearly three times what it was in 2002, and since SOI technology is primarily used in high-end consumer devices, demand can be unpredictable, especially when consumer disposable income diminishes. However, VLSI noted that

the market as a whole is very healthy and has been growing at a compounded annual growth rate (CAGR) of 36% for the past three years.

Growth of SOI technology is driven by major semiconductor manufacturing node transitions, and since it acts as a technological enabler, SOI becomes the solution because of its ability to create less complicated isolation structures on a circuit, resulting in higher-end devices can be built with each new node transition using SOI, VLSI said

While 2008 sales of SOI are expected to be slightly down from 2007, the following years will see double-digit growths stimulated by the 45-nm transition by existing SOI users as well as potential new customers.

[Source: Electronic News]

**NFWS**

## THE SOI INDUSTRY CONSORTIUM WELCOMES A KEY IP

## **SERVICES PROVIDER**

Symmid

Semiconductor and

partners see SOI

technology as key to

low-power solutions

in 45nm and smaller

geometries.

SST symmidsemi

The SOI Industry Consortium announced at the end of August that Symmid Semiconductor Technology (SST), based in Silicon Valley, California, a provider of ASIC design services and intellectual property (IP) porting, has joined the organization as a technical member. With the addition of SST, the SOI Industry Consortium now comprises 24 leading companies from across the electronics

industry covering a spectrum of users, enablers, suppliers and manufacturers. This new addition complements the IP focus of the SOI Industry Consortium.

SST, which is a technology partner for leading foundries, focuses primarily on system-on-chips (SoCs) with the most stringent performance, power and area requirements. The company is also a design partner of Arrow's Custom Logic Solutions (CLS) Group, one of North America's broadest custom logic solutions

providers.

"Symmid Semiconductor Technology foresees increased interest in SOI technology for low-power SoC designs. We are excited about our participation in the SOI consortium and we plan to contribute to the momentum of SOI adoption through enablement of IP development and porting," said Alex Parshad, CEO of Symmid Semiconductor.

[Source: SOI Industry Consortium]

VOLUME IV PAGE 3

#### **EVENTS**

## Third SINANO Device Modeling Summer School

The third summer school on

"Semiconductor Device Modeling and Simulation" was held at the beginning of this month (September 1st-5th) at the Summer School facility of the University of Bologna, located in Bertinoro, a picturesque medieval village.

The SINANO Summer School was held in 2005 and 2006 in the framework of the SINANO European Network of Excellence, and is currently continued under the auspices of the new NANOSIL Network of Excellence and of the Integrated Project PULLNANO, two European research initiatives bringing together the top European Universities, Research Institutes and Com-

panies with expertise in advanced Nano-CMOS technology, devices and simulation.

This school consists of a comprehensive set of classes aimed at doctoral level researchers from both industry and academia, taught by world's leading experts in the fields of device modelling and characterization via a program consisting of lectures, tutorials and advanced discussion groups.

The aim of this Summer School was to further enhance the knowledge of PhD students and postdoctoral researchers in the advanced modeling, simulation and characterization techniques amenable to conventional and novel nano-CMOS devi-

ces.

The 5 days program of the School were dedicated to the following topics:

- •Prospects for further development of CMOS technology

- •Transport models for device simulation

- Experimental electrical device characterization

- Analytical and compact models

- Post CMOS devices

- •Silicon technology for photo-voltaic energy conversion

#### **EUROSOI NEWS**

## First EUROSOI Working Group Meeting

One of the important goals of EUROSOI+ is to boost the exchanges of information about the Fully Depleted SOI Technology developed by LETI (which makes reference to devices that are fabricated on ultra-thin SOI films and coupled with high-K and metal gates).

In this framework, EUROSOI planned the organization of three Working Group Meetings, first of which will be held on November 17th-18th in Grenoble. The lecturers participating in this first edition are F. Gámiz, O. Faynot, S. Cristoloveanu, F. Andrieu, A. Ase-

nov and D. Bol.

The global idea is to organize a technical event with several presentations in order to see:

- •What is available today with regard to LETI FDSOI technology?

- •What would be needed to go further?

The announcement of this meeting can be also found visiting the EU-ROSOI website http://www.eurosoi.org

#### **CONFERENCES**

#### **ESSDERC-ESSCIRC Conferences**

The aim of the ESSDERC conference is to provide an annual European forum for

the presentation and discussion of recent advances in solid-state devices and technologies. ESSDERC and its sister conference ESSCIRC, which deals with solid-state circuits, are jointly organised.

The conferences are held this year in Edinburgh, Scotland, from 15-19 September.

For more information and programmes visit the ESSDERC-ESSCIRC web site http://www.essderc.org

#### **EUROSOI NEWS**

## Fifth EUROSOI Workshop

EUROSOI Workshop is an international forum to promote interaction and exchanges between research groups and industrial partners involved in SOI activities all over the world. Following the lively experience of the previous meetings in Granada (2005), Grenoble (2006), Leuven (2007) and Cork 2008, EUROSOI 2009 will be held at Chalmers, Göteborg. It

will include oral and poster sessions, outstanding keynote presentations, a training course, a social program as well as ample room for informal discussions.

EUROSOI covers recent progress in SOI technologies and will be of interest to materials and device scientists, as well as to process, circuits and application-oriented engineers. Information about abstract submissions and registrations will be announced in the next volume of the EUROSOI Newsletter (October)

For further information and important dates take a look at http://chalmers2009.eurosoi.org

#### **CHALMERS**

#### **FEATURE**

## **Diversity in MEMS Processing**

Diversity is good, but is more diversity better? Diversity enables a species to survive, it weeds out dead-end developments, and it's a source of seemingly infinite improvement. So is more better? Not always, at least from a processing/production point of view. Let's look at MEMS: how many processes already exist or are proposed as production technologies? Does every MEMS product have its own technology as some believe? Is it good to have such diversity in MEMS processing? Is the MEMS world becoming more or less diversified in terms of technology? To find answers to these questions, over 110 MEMS processes from established MEMS suppliers, start ups, universities, etc. have been analyzed. Surprisingly, from all these products only a few (7) can be regarded as product/company unique. The rest can be more or less easily divided into standardized

process techniques.

So what are the differences between these processes? You don't need much to make a MEMS device: a freehanging structure, a construct to detect the movement of the free-hanging part, and, as always, some electronics. To make a free-hanging structure you need a suitable material: a structural layer and a process to remove the material around that layer (sacrificial etching). If material is removed from the substrate,

(sacrificial etching). If material is removed from the substrate, the process is called bulk micromachining (BMM), and if deposited layers are removed, the process is called surface micromachining (SMM).

The process you will choose is of course very much product-based. Pressure sensors are still mainly created using

BMM, accelerometers and gyroscopes by polysiliconbased SMM (or low-temperature alternatives), RF MEMS products by metal SMM, and microphones by dielectric-based SMM. If you decide to build a micropump with MEMS technologies, using multi-stack wafers structured with BMM is the technology of choice.

Industrial MEMS Process Flows

[Source: R&D Magazine]

#### **EUROSOI NEWS**

## Short course on Circuit Design

For the beginning of

2009 a second short

course is being

prepared to be held

during the

EUROSOI

Workshop in

A second short course like the one celebrated last year in the framework of the EUROSOI Workshop held in Cork is being prepared to be held during the EUROSOI 2009 Workshop in Göteborg.

One of the main conclusions of the Workshop held in Cork was that it is becoming urgent to involve design people in next future to work using SOI devices and SOI technology. As a consequence, this second Short Course in Chalmers will be devoted to Circuit Design on SOI substrates.

A final list of lecturers will be available in mid-september and announced in the following number of this Newsletter.

#### **EVENTS**

## 2008 EUROPRACTICE Workshop

The "Europractice" brand has become synonymous with high quality Microelectronics and Microsystems services in Europe.

The Europractice Workshop is an ideal opportunity to meet and exchange ideas with colleagues from different European service oriented projects. This year the workshop was held at IMEC, Leuven (Belgium) September 4th and arranged to cover the following topics:

- •Overview of Europractice service projects, showing how multiple projects are working together to provide an overall service.

- •Update from each EC service projects: what's new, services offered, success stories etc.

- •Discussion: identify best practice and learn from the experiences of other EC projects, how projects can work together, define actions for moving forward.

**G**öteborg

Thematic network on silicon on insulator technology, devices and circuits.

If you want to contribute to the EUROSOI Newsletter, you can email us with any outstanding event, announcement or news

Mail: eurosoi@ugr.es

The EUROSOI network embraces a broad range of research areas related to Silicon-On-Insulator technology (from materials to enduser electronic applications in traditionally strong European industrial sectors such as automotive, communications, space). EURO-SOI aims at federating the existing research work on SOI topics and at providing an appropriate communication channel between academic groups and industrial production centres.

# CALENDAR

# - European School On Nanosciences & Nanotechnologies

Grenoble, France.

August 24th - September 13th, 2008

## - Third SINANO Device Modeling Summer School

Bertinoro, Italy.

September 1st - 5th, 2008

#### -2008 EUROPRACTICE Workshop

Leuven, Belgium.

September 4th, 2008

#### - 38th European Solid State Device Research Conference and 34th European Solid State Circuits Conference

Edinburgh, United Kingdom.

September 15th - 19th, 2008

#### - 2008 IEEE International SOI Conference

Hudson River Valley

New York, USA

October 6th - 9th, 2008

#### - First EUROSOI Working Group Meeting

Grenoble, France

November 17th-18th, 2008

#### - EUROSOI 2009 Workshop

Chalmers University of Technology

Göteborg, Sweden

January 19th - 21st, 2009

http://chalmers2009.eurosoi.org

## - 39th European Solid State Device Research Conference and 35th European Solid State Circuits Conference

Athens, Greece.

September 15th - 19th, 2009

THEMATIC NETWORK INSULATOR TECHNOLOGY, CIRCUITS.

OCTOBER, 2008

VOLUME

#### IN THIS NUMBER:

The Foundry Company crea-

Outstanding Announcements

SOI Implemen- 2 tation Guide

2008 IEEE International SOI Conference

First FDSOI tutorial of the **EUROSOI Net**work

Visionary Rump 3 Session

First SOI Indus- 3 try Consortium Event

Second Call for 3 the **EUROSOI** 2009 Workshop

Calendar

## HIGHLIGHT NEWS

## AMD and Advanced Technology Investment Company of Abu Dhabi to Create New Leading-Edge Semiconductor Manufacturing Company

MD and the

Advanced

Technology Investment Company (ATIC) of Abu Dhabi announced the creation of a U.S.-

headquartered, leading-edge semiconductor manufacturing company to address growing demand for independent, leading-edge foundry production capabilities. The new global company, to be temporarily called "The Foundry Company", will serve this need by combining advanced process technology, industry-leading manufacturing facilities and aggressive plans to expand its global capacity footprint. At the same time, the Mubadala Development Company will increase its current investment in AMD to 19.3 percent on a fully diluted basis.

AMD will contribute to The Foundry Company its manufacturing facilities, including two fabrication facilities in Dresden, Germany, as well as related assets and intellectual property rights. ATIC will invest \$2.1 billion to purchase its stake in The Foundry Company, of which it will invest \$1.4 billion directly in the new entity and the remainder will be paid to AMD to purchase additional shares in The Foundry Company. The Foundry Company will also assume approximately \$1.2 billion of AMD's existing debt. ATIC has committed additional equity funding to The Foundry Company of a minimum of \$3.6

billion and up to \$6.0 billion over the next five years to fund the expansion of The Foundry Company's chip-making capacity beyond the manufacturing facilities initially contributed by AMD. These funds will be used by The Foundry Company to (i) proceed with capacity expansion at its fabs in Dresden, Germany, including an upgrade of one of its fabs to a state-of-the-art facility, and (ii) begin construction on a new stateof-the-art facility in Saratoga County, New York, subject to the transfer of previously-approved New York State incentives. The New York facility is expected to create more than 1,400 direct jobs, and, through its operation, to generate an additional 5,000 jobs in the region. Once operational, the New York facility will be the only independently-managed, leading-edge semiconductor manufacturing foundry in the United Sta-

The Board of Directors of The Foundry Company will be equally divided between representatives of AMD and ATIC. AMD will own 44.4 percent and ATIC will own 55.6 percent of The Foundry Company's fully-converted common stock upon its formation.

"Today is a landmark day for AMD, creating a financially stronger company with a tightened focus," said Dirk Meyer, president and chief executive officer of

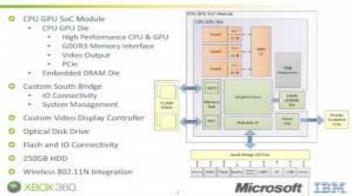

The Foundry Company will join the IBM joint development alliance for both silicon-on-insulator (SOI) and bulk silicon through the 22nm generation. The alliance consists of a group of leading semiconductor companies collaborating on next generation silicon technologies.

[Source: AMD]

#### **ANNOUNCEMENTS**

## First FDSOI tutorial of the

## EUROSOI Network and Second Call for the Chalmers Workshop

EUROSOI has launched two outstanding announcements for this month.

The first one is the Second Call for the EUROSOI 2009 Workshop and the opening of abstract submission and registration process online.

The second is the first announcement of the FDSOI Tutorial to be held in Grenoble from 17-18 November.

More information on page 3

#### NEW!

## The SOI Industry Consortium launches SOI

## **Implementation Guide**

The SOI

Implementation

Guide features a

series of white

papers and

presentations to

promote a

common

understanding of

the value and

challenges of

The SOI Industry Industry Consor-

focused on accelerating siliconon-insulator (SOI) innovation into broad markets, announced today the availability of the first chapters of its SOI Implementation Guide. The SOI Implementation Guide features a series of white papers and presentations from industry experts on specific topics to promote a common understanding of the value and challenges of SOI.

"Education is key to reducing barriers to adoption. Having easily accessible information is essential to providing the knowledge and expertise needed to inform the industry and eliminating present misconceptions," said Horacio Mendez, executive director of the SOI Industry Consortium. "The ongoing creation of chapters for the SOI Implementation Guide represents great teamwork and individual contributions from the companies and academic and R&D organizations within our consortium."

SOI process technologies have been used to implement high-performance, cutting-edge, custom designs, such as micro-processors, for several process generations. The benefits of SOI demonstrated by these designs – higher performance with the same power consumption, or lower power consumption with the same performance – have made SOI an attractive alternative for more mainstream designs as well.

The SOI Implementation Guide

features subjects such as a met-

hodology for comparing bulk

and SOI process technologies for design teams investigating the potential benefits of SOI. Another chapter addresses the partially depleted SOI circuit design advantages such as improved chip performance and lower power consumption, as well as the design issues raised by the bulk CMOS circuit design community. Other upcoming chapters will cover subjects such as an SOI overview and assessment for Analog and Mixed Signal (including 6 individual chapters on the application of SOI to RF and Analog), SOI cost analysis, FinFets and SOI, SRAM scalability in bulk and SOI, followed by a guide on how to port IP from bulk to SOI.

[Source: SOI Industry Consortium]

#### **CONFERENCES**

## 2008 IEEE International SOI Conference

The IEEE International SOI Conference is the premier meeting of engineers and scientists dedicated to current trends in Silicon-on-Insulator technology and provides a forum for open discussion in all areas of silicon-on-insulator technologies and their applications.

The IEEE Electron Devices Society sponsored the 34th SOI Conference (6 – 9 October, 2008) at the Mohonk Mountain House in the beautiful Hudson River Valley in upstate New York.

The areas of focus in this edition were:

- •SOI device physics and modeling

- •Manufacturability and process integration of soi devices

- •Low-power SOI technology and circuit design infrastructu-

- •SOI circuit applications (highperformance mpu, sram, asic, high-voltage, rf, analog, mixed mode, etc.)

- •SOI double & multiple gate/

vertical channel structures; other novel SOI structures

- •New SOI structures, circuits, and applications (3d integration, displays, microactuators, novel memories, optics, etc.)

- SOI reliability issues (hotcarrier effects, radiation effects, high-temperature effects, etc.)

- •SOI material science/ modification, material characterization, manufacture, and substrate engineering.

- •SOI sensors, MEMS and RFIDs technology and applications

VOLUME V PAGE 3

#### **EVENTS**

### First FDS0I tutorial of the EUROS0I Network

One of the major objective of EU-

ROSOI+ network is to coordinate the elaboration of European platform dedicated to Low Power applications. This platform will use the Fully Depleted SOI technology developed at CEA-LETI. Training on SOI devices and on FDSOI technology is also a strong objective of EUROSOI+. 3 tutorial events will be organized during the project. This first one, organized in Grenoble from I7th-18th November is dedicated to the training of European scientists on Fully Depleted SOI technology.

Well recognized technologists, as well as

international experts on devices and circuit design will train the attendees on SOI specific aspects. Typical topics include:

- (I) Devices physics

- (2) Technology description

- (3) Modeling and circuit design

- (4) Variability issues

- (5) FDSOI platform development status.

The organizing committee is formed by Olivier Faynot (Chair) and Sorin Cristoloveanu (Co-chair). And the steering committee is composed by Francisco Gámiz (U. Granada, SPAIN), Cor Claeys (IMEC,

BELGIUM), Jean-Pierre Colinge (Tyndall, IRELAND), Sorin Cristoloveanu (IMEP, FRANCE), Olof Engström (Chalmers, SWEDEN), Olivier Faynot (CEA-LETI, FRANCE), Denis Flandre (UCL, BEL-GIUM) and Andrés Godoy (U. Granada, SPAIN)

Information about registration and accommodation can be found at the EURO-SOI web site. This tutorial is free of charge for the EUROSOI+ members.

#### **EUROSOI NEWS**

## **Visionary Rump Session**

Session has been arranged. This session will be about "SOI as a fuel injection along the More Moore road" and is Sponsored by the European FP7 Network of Excellence NANOSIL.

The Panel of Speakers will be announced soon through this EUROSOI Newsletter and through the EUROSOI 2009 Workshop website.

#### **EVENTS**

## First SOI Industry Consortium Event

This first SOI Consortium event will take place on No-

vember 11 at the TechMart in Santa Clara, California and it is a chance to learn about all the work that has been accomplished throughout the consortium, as well as to share perspectives and objectives.

The Programme will include:

•A keynote from John Chen, VP, Technology and Foundry Operations at NVIDIA on graphics silicon technology needs and its impact on SOI.

- Methodology breakout sessions presented by members covering subjects such as SOI vs. Bulk future challenges, SOI power, frequency and area considerations, and SOI cost analysis.

- A select press panel and one-onone interviews for members interested.

The announcement of this event can be also found visiting the SOI Consortium website http://www.soiconsortium.org/

#### **EUROSOI NEWS**

## Second Call for the EUROSOI 2009 Workshop

EUROSOI Workshop is an international forum to promote interaction and exchanges between research groups and industrial partners involved in SOI activities all over the world. Following the lively experience of the previous meetings in Granada (2005), Grenoble (2006), Leuven (2007) and Cork 2008, EUROSOI 2009 will be held at Chalmers, Göteborg. It

will include oral and poster sessions, outstanding keynote presentations, a training course, a social program as well as ample room for informal discussions.