#### INFORMATION AND COMMUNICATION TECHNOLOGIES

#### COORDINATION AND SUPPORT ACTION

### **EUROSOI+**

## **European Platform for Low-Power Applications on Silicon-On-Insulator Technology**

Grant Agreement nº 216373

# D4.10 Report on EUROSOI+ Workshop held in Granada, 17-19 January 2011

Due date of deliverable: 30-06-2011 Actual submission date: 30-06-2011

Start date of project: 01-01-2008 Duration: 42 months

Project coordinator: Prof. Francisco Gámiz, UGR

Project coordinator organisation: University of Granada, Spain Rev.1

| Project co-funded by the European Commission within the Seventh Framework Programme (FP7) |                                                                                       |   |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|--|

|                                                                                           | Dissemination Level                                                                   |   |  |

| PU                                                                                        | Public                                                                                | X |  |

| PP                                                                                        | Restricted to other programme participants (including the Commission Services)        |   |  |

| RE                                                                                        | Restricted to a group specified by the consortium (including the Commission Services) |   |  |

| CO                                                                                        | Confidential, only for members of the consortium (including the Commission Services)  |   |  |

## **Table of contents**

| 1 Introduction                                                                                  | 3  |

|-------------------------------------------------------------------------------------------------|----|

| 2 Agenda                                                                                        | 6  |

| 3 Selection of papers to be published in a special issue of the Solid State Electronics Journal | 7  |

| 4 Minutes of the Management Board Meeting held in Granada, on January 17 <sup>th</sup> , 2011   | 9  |

| 5 Conclusions                                                                                   | 17 |

| Annex. Conference Proceedings                                                                   | 19 |

#### 1. Introduction

The Seventh Workshop of the Thematic Network on Silicon on Insulator technology, devices and circuits took place in Parque de las Ciencias, Granada, Spain from January 17<sup>th</sup> to January 19<sup>th</sup>, 2011, organized by Prof. Francisco Gamiz (University of Granada).

EUROSOI is an international forum for promoting high-level scientific research and exchanges between research groups and industrial partners involved in SOI activities all over the world. EUROSOI activities are supported by the European Commission. Following the lively experience of the previous meetings (Granada-2005, Grenoble-2006, Leuven-2007, Cork-2008, Goteborg-2009 and Grenoble 2010), EUROSOI'11 featured oral and poster sessions, keynote presentations, as well as room enough for informal discussions. This year our *leitmotiv* was "The contribution of SOI in the brilliant future of Nanoelectronics". A Special Issue of Solid-State Electronics will contain selected full-length papers.

In addition to the high level technical presentations, EUROSOI workshops are also characterized by their fringing events: in this occasion, a discussion panel (the opinion of the experts), a training course (January 17<sup>th</sup>) and the kick-off meeting of the new NANOTEC network (<a href="http://www.fp7-nanotec.eu">http://www.fp7-nanotec.eu</a>) were organized.

The panel of specialists was moderated by Prof. Francis Balestra (Sinano Institute & Grenoble INP) and and the opinions were aired by Dr. Malgorzata Jurczak (IMEC), Dr. Bruce Doris (IBM, USA), Dr.Olivier Faynot (CEA-LETI), Prof. Massimo Fischetti (UTDallas, USA), Prof. Carl Das (EUROPRACTICE & IMEC) and Dr. Nobuyuki Sugii (LEAP, Japan). The headline of the debate was: "The contribution of SOI technology in the brilliant future of Nanoelectronics"

The tutorial, which was defined by the title "Silicon on Insulator technologies for future electronics", also included Prof. Sigfried Mantl (FZJuelich, Aachen, Germany) to talk about SOI solutions for next technological nodes, Dr. Bruce Doris (IBM TJ Watson Research Center, NY, USA) on the scaling properties of ultrathin fully depleted SOI devices, Prof.Yael Nemirosky (Technion, Israel) on SOI Image sensors, Dr. Nobuyuki Sugii (LEAP, Japan) to speak Low-power applications of SOI technology; Dr. Malgorzata Jurczak (IMEC) introduced a very timely topic: Memories on SOI, and finally Dr. Jean-Marc Fedeli explored other SOI photonics.

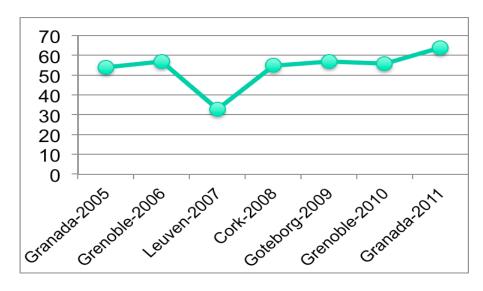

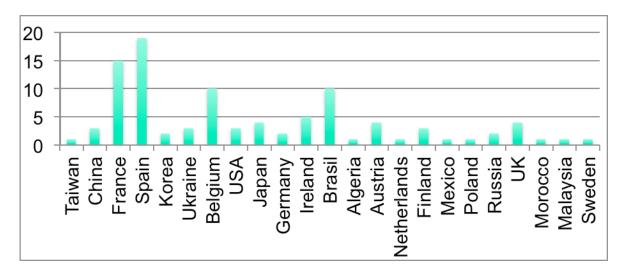

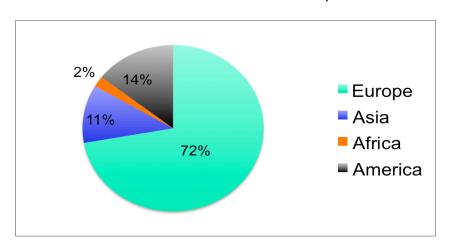

Sixty five (65) papers have been submitted this year and 60 contributions have been selected. Twenty seven (27) contributions were given as oral presentations and thirty three (33) as posters. Many of the contributions had their origin in strong national and international co-operations, born in previous EUROSOI meetings. Our special guests were Dr. Carlos Mazure (SOITEC), Prof. Massimo Fischetti (University of Texas at Dallas, USA), Dr.Carl Das (EUROPRACTICE & IMEC) and Mrs. Gisele Roesems (EU Commission) who kindly accepted to deliver outstanding keynote talks. The following graphs show

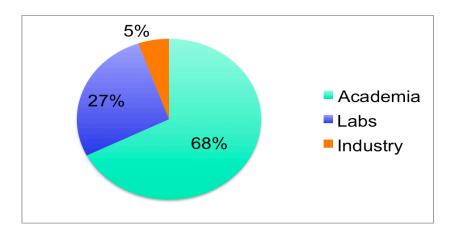

the evolution of the number of accepted contributions in EUROSOI Workshops, and the origin of the participants according to different criteria:

Evolution of contributions in EUROSOI workshops:

Distribution of authors in EUROSOI-2011

Distribution of authors in EUROSOI-2011 per continent:

## Distribution of authors per affiliation:

## 2.- Agenda

|       | Monday,<br>January 17 <sup>th</sup> ,<br>2011 | Tuesday,<br>January 18 <sup>th</sup> ,<br>2011 | Wednesday,<br>January 19 <sup>th</sup> ,<br>2011 |

|-------|-----------------------------------------------|------------------------------------------------|--------------------------------------------------|

| 9-10  | Tutorial:                                     | Session1:                                      | Session5:                                        |

| 10-11 | Silicon on                                    | SOI                                            | Device Physics                                   |

|       | insulator                                     | characterization                               |                                                  |

|       | technologies for                              | Occaiom0:                                      | Consists Co                                      |

|       | future electronics                            | Session2:                                      | Session 6:                                       |

| 11-12 |                                               | Memories                                       | Advanced<br>Simulation                           |

| 12-13 |                                               |                                                | Lunch                                            |

| 12-13 |                                               | Lunch                                          | Lunch                                            |

| 13-14 |                                               | Lunch                                          |                                                  |

| 10-14 |                                               |                                                |                                                  |

| 14-15 |                                               | Session3:                                      | Session7:                                        |

|       |                                               | Multigate                                      | Analog                                           |

| 15-16 |                                               | devices                                        | Performance &                                    |

|       |                                               |                                                | Circuits                                         |

|       |                                               | Visionary                                      | Session8:                                        |

| 16-17 |                                               | Panel Session                                  | SOI Devices                                      |

|       |                                               |                                                |                                                  |

|       | Welcome                                       |                                                |                                                  |

|       | Reception                                     |                                                |                                                  |

| 17-18 | •                                             | Session4:                                      | End of                                           |

| 18-19 |                                               | Posters                                        | EUROSOI 2010                                     |

| 19-20 |                                               |                                                | and EUROSOI+                                     |

|       |                                               | Gala Dinner                                    | Management<br>Board Meeting                      |

## 3.- Selection of papers to be published in Solid State Electronics Journal

|     | Title                                                                                                | Authors                                                                                                                                            |

|-----|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | Role of the Bipolar Junction Transistor in the 40nm PD SOI NMOS Device with the Floating Body Effect | C. H. Chen, J. B. Kuo                                                                                                                              |

| 2.  | GIDL behavior with different TiN metal gate thickness and high-k gate dielectric on MuGFET devices   | M. Galeti, M. Rodrigues, J.A.<br>Martino, N. Collaert, E. Simoen,<br>C. Claeys                                                                     |

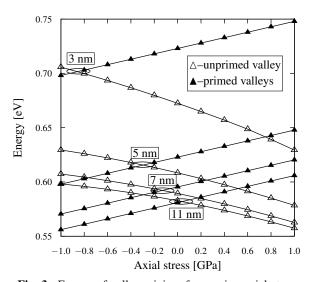

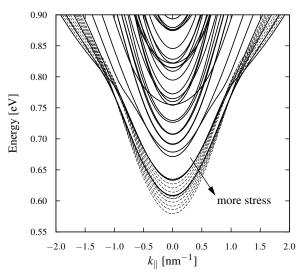

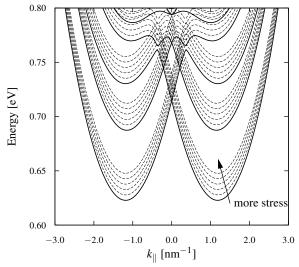

| 3.  | Subband Engineering in n-Type Silicon<br>Nanowires using Strain and Confinement                      | Z. Stanojevic, V. Sverdlov, O.<br>Baumgartner, and H. Kosina                                                                                       |

| 4.  | Quantum computing on silicon-on-insulator structure                                                  | S. Filippov, V. Vyurkov, and A.<br>Orlikovsky                                                                                                      |

| 5.  | Low Frequency Noise Spectroscopy in Advanced nFinFETs                                                | R. Talmat, H. Achour, B. Cretu, J-<br>M. Routoure, A.Benfdila, R.<br>Carin, N. Collaert,<br>A. Mercha, E. Simoen and C.<br>Claeys                  |

| 6.  | Design of Silicon Double Gate Tunnel FETs with Ultra Low Ambipolar Currents                          | Costin Anghel, Andrei<br>Vladimirescu and Amara Amara                                                                                              |

| 7.  | Electron-Hole Bi-Layers in Ultra-Thin SOI-Devices                                                    | S. Laakso, M. Prunnila and J.<br>Ahopelto                                                                                                          |

| 8.  | Reaching sub-32nm nodes: SGSOI optimization                                                          | C. Sampedro,F. Gamiz, L.<br>Donetti, and A. Godoy                                                                                                  |

| 9.  | Ultra-thin body and BOX SOI Analog Figures of Merit                                                  | V. Kilchytska, M.K. Md Arshad, S.<br>Makovejev, S. Olsen, F. Andrieu,<br>O. Faynot,<br>JP. Raskin, D. Flandre                                      |

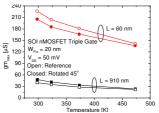

| 10. | Temperature Influence on the Analog<br>Performance of 45° Rotated Triple-Gate nFinFETs               | M. A. Pavanello, M. de Souza, J.<br>A. Martino, E. Simoen and C.<br>Claeys                                                                         |

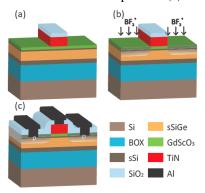

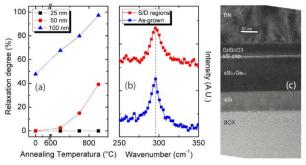

| 11. | TiN/GdScO3/strained Si0.5Ge0.5/SSOI stack for high mobility short channel p-MOSFETs                  | R. A. Minamisawa1, J. M. J.<br>Lopes1, M. Schmidt, E. Durgun<br>Özben1, JM. Hartmann2, D.<br>Buca1,<br>J. Schubert1, Q. T. Zhao1, and S.<br>Mantl1 |

|       | Title                                                                                                        | Authors                                                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

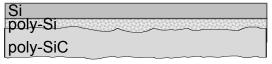

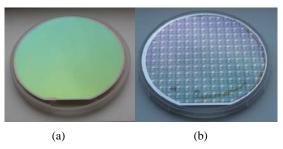

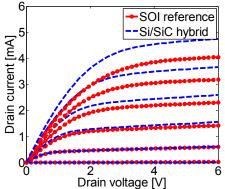

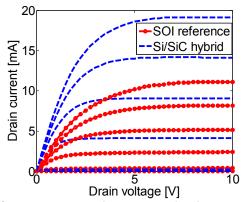

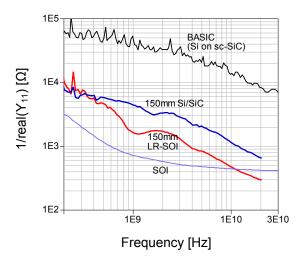

| 1 1ツ  | LDMOS transistors on 150 mm silicon-on-<br>polycrystalline-silicon carbide hybrid substrates                 | S. Lotfi, Ö. Vallin, LG. Li, L.<br>Vestling, H. Norström and J.<br>Olsson                                                                                                                |

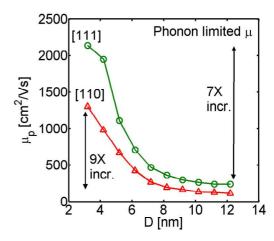

| 13.   | Confinement-Induced Mobility Increase in p-type [110] and [111] Silicon Nanowires                            | Neophytos Neophytou and Hans<br>Kosina                                                                                                                                                   |

| 1 1 1 | A2RAM: Novel dual-body 1T-DRAM cell on ultrathin SOI                                                         | Noel RodriÅLguez1, Francisco<br>GaÅLmiz1, Sorin Cristoloveanu2                                                                                                                           |

| 15.   | Comparison of the switching speed in junctionless and accumolation-mode gate-all-around nanowire transistors | P. Razavi, R. Yan, I. Ferain, N.<br>Dehdashti Akhavan, R. Yu, J.P.<br>Colinge                                                                                                            |

| 16.   | Issues on the Physics of Electronic Transport in<br>10 nm-scale<br>SOIs:How Far Can We Go?                   | M.V.Fischetti                                                                                                                                                                            |

| 17.   | Dispersion of Confined Acoustic Phonons in<br>Ultra-Thin Silicon Membranes.                                  | J. Cuffe, E. Chavez, P-O.<br>Chapuis, E. H. El Boudouti, F.<br>Alzina, D. Dudek, Y. Pennec, B.<br>Djafari-Rouhani, A. Shchepetov,<br>M. Prunnila, J. Ahopelto, C. M.<br>Sotomayor Torres |

## 4.- Minutes of the Management Board Meeting held in Granada, on January 17<sup>th</sup>, 2011

## EUROSOI Management Board Meeting held in Granada, on 17-01-2011

#### Attendees:

Prof. Sorin Cristoloveanu, IMEP, Grenoble

Prof. Cor Claeys, IMEC, Leuven

Prof. Denis Flandre, UCL, Louvain la Neuve

Dr. Carlo Reita, CEA-LETI, CEA, Grenoble

Dr.Olivier Faynot, CEA-LETI, Grenoble

Prof. Andrés Godoy, UGR, Granada

Prof. Francisco Gámiz, UGR, Granada (Co-ordinator)

The fifth management board meeting of EUROSOI+ project (FP7-ICT-2007-216373) was held in Granada, Spain on January 17<sup>th</sup>, 2011, with the following agenda:

- 1.- Welcome.

- 2.- Running Guidelines.

- 3.- Training activities.

- 4.- Scientific Exchange Program.

- 5.- Student Grants.

- 7.- Technological platform. Working plan.

- 8.- Questions and suggestions.

#### 1.- Welcome.

Prof. Francisco Gamiz, Co-ordinator of EUROSOI network, organizer and General Chairman of the 7<sup>th</sup> EUROSOI Workshop welcomed all the attendees to the MB meeting.

#### 2.- Running Guidelines.

Prof. Gámiz, EUROSOI Co-ordinator, thanked all the attendees for being present at the meeting. He summarized the objectives of the project, and highlighted the tasks performed during the first year of EUROSOI+ project. Basically, we have followed the plan of activities detailed in the Annex I of the contract, Description of the Work (DoW). He also informed the MB members, that after this MB meeting, there would be a review meeting with the Commission to be attended by Mrs.Gisele Roesems, Project Officer, and

Prof.Adrian Ionescu from EPFL, Project reviewer, in addition to the members of EUROSOI+.

The agenda of the review meeting was the following:

16:00-16:15. Network status. EUROSOI-2011 (F.Gamiz)

16:15-16:30 Activity report (A.Godoy)

16:30-17:00 EUROSOI technology platform (O.Faynot & C.Reita)

17:00-17:30 Discussion

17:30-18:00 Conclusions

Prof. Gamiz also informed about the meeting to be held on Tuesday, January 18<sup>th</sup>, with Prof.Carl Das from IMEC, coordinator of EUROPRACTICE, with the goal of discussing the possible collaboration/interaction/integration of EUROSOI FD-SOI platform in EUROPRACTICE.

Finally, Prof. Gamiz informed the MB that the Commission finally accepted the extension of three months that we requested in December 2010. Thus, the final duration of the project is 42 months, finishing on June 30<sup>th</sup>, 2011.

#### 3.- Training activities

Two training events were directly organized during the last year:

- "Silicon on Insulator: Materials to Circuit Design " Seville, Spain, September 13th, 2010 (satellite event to ESSDERC-2010, 35 participants)

- ii. "Silicon-on-Insulator technologies for future electronics"

Granada, Spain, January 25th 2011 (Training tutorial previous to EUROSOI-2011 workshop, 115 participants)

In addition, **EUROSOI** has sponsored two important training events during 2010:

- nanoKISS 2010: Korean International Summer School on Nanoelectronics, Daegu, April, 2010

- International SemOl Workshop "Nanoscaled Semiconducto on-Insulator Materials, Sensors and Devices, Kiev, Ukraine, October 2010

As a consequence of the second activity, the following book has been published by Springer:

Prof. J.-P. Colinge

Tyndall National Institute "Lee Maltings"

Tyndall National Institute Tuniversity College

Cork

Inventible Altonal Institute "Lee Maltings"

Tyndall National Institute Tuniversity College

Cork

Inventible Altonal Institute Tuniversity College

Cork

Institute "Lee Maltings"

Tyndall National Institute Tuniversity College

Cork

Institute Tuniversity College

Tonks Tuniversity Coll

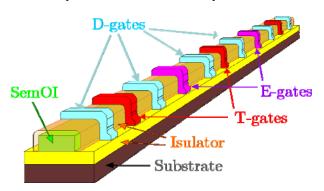

This Book is devoted to the fast evolving field of nanoelectronics, and more particularly to the physics and technology of nanoelectronic devices built on semiconductor-on-insulator (SemOI) substrates. It compiles the results of research work from leading companies and universities in Europe, Russia,

Brazil and Ukraine. Main of the Authors are involved in the NANOSIL Network of Excellence and the Thematic Network on Silicon on Insulator Technology, Devices and Circuits EUROSOI+, both of which are funded by the European Commission under the 7th Framework Program of the European Community.

This Book describes different technologies and approaches used to fabricate Semiconductor-On-Insulator materials, devices and systems. The contributed papers are articulated around four main themes:

- 1. Fabrication of new semiconductor-on-insulator materials

- 2. Physics of modern SemOI devices

- 3. Advanced characterization of SemOI devices

- 4 Sensors and MEMS on SOI.

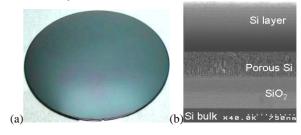

The first chapter is focused on techniques for producing new SemOI materials. The formation of thin germanium-on-insulator films allows one to fabricate a wide variety of devices and constitutes a fundamental step towards the design of monolithic hybrid Si–Ge systems and integrated circuits. SOI wafers on high resistivity substrates can be used for RF and mixed-signal system-on-a chip (SoC) applications. Special substrates employing porous silicon technology allows one to fabricate III–V and column-IV alloy semiconductor films on dielectric substrates. Confined and guided growth of silicon nanoribbons creates new technological opportunities for the fabrication of field-effect transistors and ICs.

The second Chapter is devoted to the physics and electrical properties of novel SemOl devices such as ultrathin-body, fully depleted SOIMOSFETS scaled down to 22 nm and beyond, multigateFinFET devices, nanowire transistors using either lightly doped or highly doped silicon (junctionlessMOSFETs), carbon nanotubes (CNTMOSFETs) and single-electron devices. Novel phenomena such as quantum effects and Coulomb blockade effect occurring in nanoscale devices are described as well.

The third part of the Book focuses on advanced electrical characterization techniques for nanoelectronic devices, such as novel methods for extracting mobility, transconductance and noise.

Finally, the fourth Chapter is devoted to application of SemOI materials for biosensors, chemical sensors and MEMS. The use of SemOI substrates allow for considerable increase of sensitivity of the sensors, as well as for the fabrications of MEMS compatible with CMOS technology.

#### 4.- Scientific Exchange Program

Prof. Andres Godoy reported on the Scientific Exchange Visits performed in 2010, and which are shown in the table below:

#### **EUROSOI + Scientific Visits - 2010**

| ORIGIN<br>(PERSON/AFFILIATION)                                                        | DESTINATION<br>(RESPONSIBLE/AFFILIATION)             | START<br>DATE      | END DATE<br>OR<br>DURATION<br>OF THE<br>VISIT | TOTAL<br>EXPENSES | TOPIC OF THE<br>VISIT                               |

|---------------------------------------------------------------------------------------|------------------------------------------------------|--------------------|-----------------------------------------------|-------------------|-----------------------------------------------------|

| Jean Pierre Raskin /<br>Universite Catholique du<br>Lovain                            | University of Newcastle, UK                          | February,<br>2010  | 4 weeks                                       | 4205,6€           | Electromechanical<br>analysis of Si<br>Nanowires    |

| David Jiménez /<br>Universidad Autónoma<br>de Barcelona                               | Andres Godoy, Universidad de<br>Granada              | March, 2010        | 2 weeks                                       | 2767,1€           | Ferroelectric Gated transistors based on SOI.       |

| Noel Rodriguez, UGR<br>(Spain)                                                        | Dr.Olivier Faynot, CEA-LETI,<br>Grenoble             | June, 2010         | 1 week                                        | 1319,39           | 1T-DRAM<br>memory cells on<br>FD-SOI<br>transistors |

| Youngo Bae, IMEP-<br>MINATEC Grenoble on<br>leave from University of<br>Uiduk (Korea) | Noel Rodriguez Santiago;<br>UGR, Granada             | June, 2010         | 1 week                                        | 1077,91           | Pseudo-MOSFET technique                             |

| Francisco Gamiz, UGR<br>(Spain)                                                       | Prof. Sorin Cristoloveanu,<br>IMEP-MINATEC, Grenoble | July, 2010         | 3 weeks                                       | 3392,99           | 1T-DRAM<br>memory cells on<br>FD-SOI<br>transistors |

| Francisco Garcia, UGR<br>(Spain)                                                      | Prof. Eddy Simoen, IMEC,<br>Leuven                   | September,<br>2010 | 4 weeks                                       | 4793,37           | Simulation of FinFETs                               |

After the visit, each participant has provided to the coordinator a report describing the work developed during the visit. The reports of the visits performed during these reporting periods (M1-M42) have bee used as a basis to elaborate Deliverables D2.3, D2.4 and D2.5.

A total of 17556,40 € have been used to fund the 6 visits (15 weeks) performed along this third reporting period (M27-M36).

A Sixth Call for Proposals of Scientific Visits was launched in November, 2010. These visits will take place in the first semester of 2011. The proposals received are summarized in the table below:

## **EUROSOI** + Scientific Visits - First Semester, 2011

| ORIGIN<br>(PERSON/AFFILIATION)                         | DESTINATION<br>(RESPONSIBLE/AFFILIATION)       | START DATE        | END DATE<br>OR<br>DURATION<br>OF THE<br>VISIT | TENTATIVE<br>BUDGET | TOPIC OF THE<br>VISIT                                                                                   |

|--------------------------------------------------------|------------------------------------------------|-------------------|-----------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|

| Maryline Bawedin,<br>Université Montpellier,<br>France | Francisco Gamiz, UGR (Spain)                   | January, 2011     | 1 week                                        | 1400€               | 2D/3D TCAD<br>simulations of<br>transient effects<br>in SOI 1T-<br>DRAMs.                               |

| Frederic Allibert,<br>SOITEC, Bernin, France           | Francisco Gamiz, UGR (Spain).                  | February,<br>2011 | 1 week                                        | 1400€               | Characterization<br>of ultrathin-BOX<br>silicon on<br>insulator wafers                                  |

| Jose Luis Rodriguez,<br>UGR, Granada, Spain            | Sigfried Mantl, FZJuliech,<br>Aachen, Germany. | March, 2011       | 4 weeks                                       | 5500 €              | Characterization<br>and simulation<br>of Schottky<br>Barrier<br>MOSFETs.                                |

| Noel Rodriguez, UGR,<br>Granada, Spain                 | Frederic Allibert, SOITEC,<br>Bernin, France   | June, 2011        | 1 week                                        | 1400€               | Three-interface pseudo-MOSFET models for the characterization of SOI wafers with ultrathin film and BOX |

The Board approved all the proposals since all of them agreed with the procedure and rules approved in January, 2008

#### 5.- Student Grants

Prof. Gamiz reported that for EUROSOI'2011 fifteen (15) student grants were allocated to the following PhD students:

|    | Student                     | Advisor                                | Institution                                                                    | EUROSOI                                                                                                                                |

|----|-----------------------------|----------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|    | Otadent                     | Advisor                                | mondation                                                                      | presentation                                                                                                                           |

| 1  | Jianhua Zhou                | Prof. S.C. Zhou                        | Chinese Academy of Science                                                     | "Hole Tunneling from<br>Valance Band and Hot-<br>Carrier Induced Hysteresis<br>Effect in 0.13µm Partially<br>Depleted SOI n-MOSFETs"   |

| 2  | Amer El Hajj Diab           | Prof. S.Cristoloveanu                  | IMEP, Grenoble France                                                          | "Low-Frequency Noise in<br>Ultrathin SOI Pseudo-<br>MOSFET: Where is the<br>Noise Coming From?                                         |

| 3  | Dimitri Soussan             | Prof. Marc Bellevile                   | CEA-LETI, Grenoble, Framce                                                     | "65nm Partially Depleted<br>SOI Output Buffer with<br>Active Body-Biasing<br>Control"                                                  |

| 4  | Guillaume<br>Pollissard     | Prof. Denis Flandre                    | UCL, Louvain, Belgium                                                          | A circuit level 65nm node<br>bulk and SOI technologies<br>comparison for analog<br>amplifiers                                          |

| 5  | Rudolf Theoderich<br>Buhler | Prof. Cor Claeys                       | IMEC, Kapeldreef 75, B 3001<br>Leuven, Belgium                                 | Fin Shape Influence on<br>Analog Performance of<br>MuGFETs at Room and at<br>Low Temperature                                           |

| 6  | Mike Schwarz                | Prof. Alexander Kloes                  | University of Applied Sciences<br>Giessen-Friedberg, Germany                   | 2D Analytical Calculation of<br>the Current in Lightly<br>Doped Schottky Barrier<br>Double-Gate MOSFET                                 |

| 7  | Adam Makosiej               | Prof. Andreiç<br>Vladimirescu          | ISEP, Paris, France                                                            | ULP Variability-Insensitive<br>SRAM Design in sub-32nm<br>UTBB FDSOI CMOS                                                              |

| 8  | Ghader Darbandy             | Prof. Benjamin Iñiguez                 | URV, Tarragona, Spain                                                          | Study of Potential High-k<br>Dielectrics for sub 15 nm<br>UTB SOI MOSFETs, Using<br>Analytical Models of the<br>Gate Tunneling Leakage |

| 9  | Nima Dehdashti<br>Akhavan   | Prof.Jean Pierre<br>Colinge            | Tyndall, Cork, Ireland                                                         | Influence of single-atom impurity scattering on quantum transport in silicon nanowire transistor                                       |

| 10 | Talitha Nicoletti           | Prof. Cor Claeys<br>Prof. Joao Martino | IMEC, Kapeldreef 75, Leuven,<br>Belgium and University of Sao<br>Paulo, Brasil | Rotated SOI MuGFETs at<br>High Temperatures                                                                                            |

| 11 | Sara Lotfi                  | Prof. Jorgen Olsson                    | Uppsala University, Sweden                                                     | LDMOS transistors on 150 mm silicon-on-polycrystalline-silicon carbide hybrid substrates                                               |

| 12 | Raul Valin                  | Prof. Antonio Garcia                   | Universidad Santiago<br>Compostela                                             | Multi-Subband Monte Carlo<br>Simulation of Oxide<br>Thickness Fluctuation on<br>SGSOI MOSFETs                                          |

| 13 | SJ. Chang                   | Prof. S.Cristoloveanu                  | IMEP, Grenoble France                                                          | Scaling of SOI FinFlash<br>Memory with Buried<br>Storage ONO Layer (author<br>asks for oral presentation)                              |

| 14 | Francisco Martinez          | Prof. F. Gamiz                         | University of Granada                                                          | Transport mass of holes in ultra-thin DGSOI devices                                                                                    |

| 15 | Jose L. Padilla             | Prof. F.Gamiz                          | University of Granada                                                          | Transport mass of holes in ultra-thin DGSOI devices                                                                                    |

|    | •                           | •                                      |                                                                                |                                                                                                                                        |

The MB agreed to fund all the proposals with a maximum of 750€/each.

#### 6.- Report Upgrading

Prof. Godoy, Leader of WP2 (Networking activities), reminded that according to our Plan of Activities, Upgraded versions of State-of-the-Art report and EUROSOI Roadmap should be delivered for the next review meeting. He mentioned that we already composed preliminary versions of these reports, and that they were distributed for critical reading, and that the final versions are being composed taking into account the inputs of the partners.

#### 7.- Technological platform

Dr. Carlo Reita (LETI) reported that CEA-LETI announced in October, 2010 the launch of an Exploratory MPW (Multi Project Wafers) initiative based on FDSOI (Fully Depleted SOI) 20nm process, opening the access of its 300mm infrastructure to the design community. This MPW offer is partly supported by EUROSOI+ network that gathers the main European academic partners on SOI.

This process will allow Researchers and Engineers to experiment the benefits of SOI on an advanced technology node.

CEA-Leti has has developed both an advanced High-K/Metal Gate FDSOI process and a number of specific design and simulation tools based on industry standard design flow packages. FDSOI technology presents key advantages over conventional bulk technology for future nodes.

The electrostatic integrity of the transistors is ensured by the thinness of the body without the need for extra litho steps, like in the case of FinFETs, or of channel doping. The consequence is a planar technology that exhibits at the same time excellent short channel behaviour and significant improvement of the variability as shown in a number of recent papers.

The basis of LETI technology offer will be the following:

- CMOS transistors with an undoped channel and a silicon film thickness of 6nm

- High-k / Metal Gate stack

- Single threshold voltage (Vth) n- and pMOSFET with balanced Vth of ±0.4V

- Associated Design Kit, including SPICE model (Verilog-A language), model cards extracted from silicon data, p-cells, DRC, LVS, schematic, parasitics

- Design Kit documentation

The first run is scheduled to be launched in September 2011. All details will be available on the CMP website.

#### 8.- Questions and suggestions.

Prof. Gamiz commented to the Board on the need of elaborating a plan for extending EUROSOI activities after the end of the financial support of the Commission.

## **CONCLUSIONS**

The seveth EUROSOI Workshop of the Thematic Network on Silicon on Insulator Technology, Devices and Circuits was held in Granada (Spain) on 17-19 January, 2011 and was focused on recent theoretical, experimental and industrial progress on SOI materials, devices, and circuits. The meeting was attended by more than 120 researchers from labs, universities and industries all over Europe. Sixty (60) accepted contributions were presented and widely discussed, successfully covering SOI topics, such as: i) SOI Materials, Devices and Systems; ii) Modelling and characterization; iii) Simulation; and iv) SOI Circuits and Applications.

This workshop became the appropriate forum to promote interaction and the exchange of information between research groups and industrial partners working in SOI. The main idea of the meeting was that each participant group should communicate their findings, opinions, experiences and conclusions about SOI questions. In this sense, the main workshop's goal is becoming a first step towards preparing future European task forces in SOI (RTD projects, collaborations, etc.)

We also wanted to have the point of view of different specialists coming from Industrial Centers. We had four invited talks given by well-known experts:

- Dr.Gisele Roesems, EU-Commission, Belgium "Nanoelectronics: a bright future?"

- Dr. Carlos Mazure, SOITEC, France "Readiness of FDSOI technology platform: overview"

- Dr. Carl Das, EURORACTICE & IMEC, "EUROPRACTICE: Design and Prototyping Support for European Universities and Research Institutes"

- Prof. Massimo Fischetti, UTDallas, USA, "Issues on the Physics of Electronic Transport in 10 nm-scale SOIs: How Far Can We Go?"

We organized this rather informal and lively meeting, whose main objective was to discuss the situation of SOI technology in Europe. We had people from the EU, Switzerland, Japan, South Korea, Taiwan, China, Brazil, Ukraine, Russia, India, Canada, USA, Israel. There were 45 students. There were 25 industrial participants from SOITEC, IBM, CISSOID, ST, and Infineon.

We also organized a panel discussion chaired by Prof. Francis Balestra from IMEP-MINATEc, and Sinano Institute, Grenoble entitled "The contribution of SOI in the brilliant future of Nanoelectronics" and composed by the following six experts:

- 1. Prof. Massimo Fischetti, University of Texas at Dallas, USA

- 2. Prof.Carl Das, IMEC & EUROPRACTICE, Leuven, Belgium

- 3. Dr. Malgorzata Jurczak, IMEC, Leuven

- 4. Dr. Bruce Doris, IBM, USA

- 5. Dr.Olivier Faynot, CEA-LETI, Grenoble

- 6. Nobuyuki Sugii, Leap, Tokyo, Japan

After the initial explanations, there was a long and live debate among the panellists and the audience. Among the different applications where SOI technology could successes, ultra-low power and mobile applications were selected. Mobile internet and medical applications will create a huge semiconductor business. Memory applications based on SOI technology are not clear at this point, and more research and breakthroughs are necessary. To successfully face these demands, technology will have to provide very low power consumption, high-density memory and computational power. SOI technology provides viable solutions to these challenges thanks to the new substrate materials and device and circuit designs.

However, the main drawbacks are:

- 1. The lack of a large portfolio of Standard Cells Library and available IP for SOI.

- 2. The cost still remains as a major drawback compare to traditional bulk MOSFETs.

Both problems become a barrier to broad adoption of SOI.

In summary, SOI technology has demonstrated a significantly superior device and circuit performance and an extraordinary power reduction compared to standard bulk silicon technology. However, the range of commercial applications that currently use SOI substrates is still reduced. New business opportunities are opening and SOI technology should find its way on them. The final success of these new markets depends on two important tasks to be addressed:

- i) Cost reduction compared to currently available technology.

- ii) Development of a large portfolio of SC libraries and IP for SoC.

The final outcome of this meeting is a consequence of the quality of the contributions and the spirit of friendly cooperation shown by all the contributors. We wish to thank all of them for their effort. We would also like to thank all the people who allowed this meeting to take place, in particular, to the members of the Nanoelectronics Research Group at the University of Granada, to the Rector of the University of Granada, Prof. Gonzalez-Lodeiro, and Parque de las Ciencias de Granada.

A selection of the contributions presented at the Workshop will be published in a special issue of Solid State Electronics Journal devoted to the Seventh Workshop of the Thematic Network of Silicon on Insulator Technology, Devices and Circuits.

# **EUROSOI 2011**

VII Workshop of the Thematic Network on Silicon On Insulator Technology, Devices and Circuits

Conference Proceedings

## **EUROSOI 2011 is Organized by**

**Nanoelectronics Research Group**

Universidad de Granada

Departamento de Electrónica y Tecnología de Computadores

Universidad de Granada

### **EUROSOI 2011 is Sponsored by**

#### **EUROSOI+**

Nanoelectronics Research Group

Nanoelectronics Research Group

Departamento de Electrónica y Tecnología de Computadores Universidad de Granada

Parque de las Ciencias, Andalucía, Granada

**GENIL:** Granada Excellence Network of Innovation Laboratories

**European Union Commission**

Ministerio de Ciencia e Innovación

Junta de Andalucía

**Agilent Technologies**

Soitec

**Hispania PC**

Gateway

#### **General Chairs' Foreword**

There are many fields where SOI technology shows all its potential to circumvent the problems found in bulk technology: i) Shrinking the conventional MOS transistor below the 22nm-node, ii) the continuous demanding for low power consumption in ubiquitous mobile applications, iii) new memory designs, iv) high-temperature and power electronics, and so on. The steady work of the SOI community is demonstrating everyday that this technology can gain a higher portion of the electronic market. However, researchers have to face new challenges. But, the combination of hard work, imagination and creativity will lead us to success. These proceedings are a good example of the above.

At this point, EUROSOI initiative plays its main role: EUROSOI network was born as the meeting point where all these efforts should converge. Since its beginning in Granada (2005) and touring through Grenoble (2006), Leuven (2007), Cork (2008), Chalmers (2009) and Grenoble (2010), the workshop served as the ideal forum for inspiring discussions and to foster strong interactions among specialists in different fields.

Following previous experiences, we have prepared an informal, lively meeting with space for short presentations within a framework of larger discussion sessions. Relevant speakers have been invited to present the state-of the-art in different fields of SOI. Dr. Carlos Mazure, from SOITEC, will open the conference describing the bright future of the FDSOI technology. Then Prof. Max Fischetti, from UTDallas, will take us as far as we can go. Prof. Carl Das, from IMEC, will introduce us in the Europractice network. Last, but not least, Mrs Gisele Roesems, from EU Commission, will talk about the future European research projects in the Nanoelectronics arena, formulating the strategy for the coming years.

A Ramp session entitled "The contribution of SOI in the brilliant future of Nanoelectronics" and chaired by Prof. Francis Balestra, from IMEP, promises to be an exciting brainstorming.

Previous to the Workshop, and following the tradition, we have organized an interesting training course. The lectures are given by six experts covering the areas from technology, memories, imagers, low-power and photonics. It will take place on Monday, January 17th. We would like to highlight the magnificent venue where the Workshop will be held. We are sure that the "Parque de las Ciencias" will create a warm atmosphere prone to the exchange of scientific and technical ideas.

Finally, we would like to thank all the authors for their contributions making the workshop successful. We would also like to acknowledge the dedication of the Organizing and Technical Committees as well as the Workshop Management team for making this meeting possible. Welcome to all the participants coming from so many different places to the charming city of Granada.

Sincerely,

Francisco Gamiz & Andres Godoy EUROSOI-2011 Organizing Committee

#### **Organizing Committee**

Francisco Gámiz Andrés Godoy Carlos Sampedro Noel Rodríguez Juan B. Roldán Luca Donetti José Luis Padilla

## **Steering Committee**

Francisco Gámiz Andrés Godoy Sorin Cristoloveanu Olivier Faynot Jean-Pierre Colinge Olof Engström Cor Claeys Denis Flandre Universidad de Granada, España Universidad de Granada, España IMEP, France CEA-LETI, France Tyndall Institute, Cork, Ireland Chalmers, Sweden IMEC, Belgium UC Louvain, Belgium

### **Program at a Glance**

## **Monday, January 17**<sup>th</sup> Training Course - Gutenberg Hall

| 09:15-09:30 | Introduction and Tutorial Overview         |

|-------------|--------------------------------------------|

| 09:30-10:30 | SOI solutions for next technological nodes |

| 10:30-11:30 | ETSOI Technology                           |

| 11:30-12:00 | Coffee Break                               |

| 12:00-13:00 | CMOS-SOI-MEMS Imagers                      |

| 13:00-15:00 | Lunch                                      |

| 15:00-16:00 | SOI Low-power applications                 |

| 16:00-17:00 | Memories on SOI                            |

| 17:00-17:30 | Coffee Break                               |

| 17:30-18:30 | SOI Photonics                              |

|             |                                            |

| 20:00-21:30 | Welcome Reception - Hotel Nazaries         |

|             |                                            |

### Tuesday, January 18<sup>th</sup> EUROSOI 2011 Workshop - Auditorium

| 08:45-09:00 |     | Conference Welcome                                                 |

|-------------|-----|--------------------------------------------------------------------|

| 09:00-09:40 | 0.1 | Readiness of FDSOI technology platform: overview (Invited)         |

|             |     | Dr. Carlos Mazuré, SOITEC                                          |

|             |     | Chair: Olivier Faynot                                              |

| 09:40-11:00 |     | SESSION 1: SOI CHARACTERIZATION                                    |

|             |     | Chair: Sorin Cristoloveanu                                         |

| 11:00-11:20 |     | Coffee Break                                                       |

| 11:20.12:00 | 0.2 | EUROPRACTICE (Invited)                                             |

|             |     | Dr. Carl Das, IMEC                                                 |

|             |     | Chair: Cor Claeys                                                  |

| 12:00-13:20 |     | SESSION 2: MEMORIES                                                |

|             |     | Chair: Malgorzata Jurczak                                          |

| 13:20-15:00 |     | Lunch                                                              |

| 15:00-16:00 |     | SESSION 3: MULTIGATE DEVICES                                       |

|             |     | Chair: Carlos Mazuré                                               |

| 16:00-17:00 |     | RAMP SESSION:                                                      |

|             |     | The contribution of SOI in the brilliant future of Nanoelectronics |

|             |     | Chair: Francis Balestra                                            |

| 17:00-17:20 |     | Coffee Break                                                       |

|             |     | SESSION 4: POSTER                                                  |

|             |     | Chairs: Carlos Sampedro & Noel Rodríguez                           |

| 17:20-18:30 |     | Oral Presentations                                                 |

| 18:30-19:30 |     | Posters Exhibition with Wine & Cheese                              |

| 20:00       |     | Bus for Gala Dinner                                                |

### Wednesday, January 19<sup>th</sup> EUROSOI 2011 Workshop - Auditorium

| 09:00-09:40 | 0.3 | Issues on the Physics of Electronic Transport in 10 nm-scale SOIs:How Far Can We Go? Prof. Massimo V. Fischetti, UTDallas Chair: Francisco Gámiz |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 09:40-11:00 |     | SESSION 5: Device Physics  Chair: Sigfried Mantl                                                                                                 |

| 11:00-11:20 |     | Coffee Break                                                                                                                                     |

| 11:20-12:00 | 0.4 | Nanoelectronics: a bright future? (Invited)                                                                                                      |

|             |     | Mrs. Gisele Roesems, EU Commission Chair: Andrés Godoy                                                                                           |

| 12:00-13:20 |     | SESSION 6: ADVANCED SIMULATION                                                                                                                   |

|             |     | Chair: Massimo V. Fischetti                                                                                                                      |

| 13:20-15:00 |     | Lunch                                                                                                                                            |

| 15:00-16:20 |     | SESSION 7: ANALOG PERFORMANCE & CIRCUITS                                                                                                         |

|             |     | Chair: João Antonio Martino                                                                                                                      |

| 16:20-16:40 |     | Coffee Break                                                                                                                                     |

| 16:40-18:00 |     | SESSION 8: SOI DEVICES Chair: Jouni Ahopelto                                                                                                     |

|             |     | •                                                                                                                                                |

## **End of EUROSOI 2011**

## **Training Course Program**

## Monday, January 17<sup>th</sup> Gutenberg Hall

| 09:15-09:30 | Introduction and Tutorial Overview<br>Prof. Francisco Gámiz, University of Granada |

|-------------|------------------------------------------------------------------------------------|

| 09:30-10:30 | SOI solutions for next technological nodes Prof. Sigfried Mantl, FZJülich, Germany |

| 10:30-11:30 | ETSOI Technology<br>Dr. Bruce Doris, IBM, USA                                      |

| 11:30-12:00 | Coffee Break                                                                       |

| 12:00-13:00 | CMOS-SOI-MEMS Imagers<br>Prof. Y. Nemirovsky, Technion, Israel                     |

| 13:00-15:00 | Lunch                                                                              |

| 15:00-16:00 | SOI Low-power applications<br>Dr. N. Sugii, LEAP, Japan                            |

| 16:00-17:00 | Memories on SOI<br>Dr.Malgorzata Jurczak, IMEC, Belgium                            |

| 17:00-17:30 | Coffee Break                                                                       |

| 17:30-18:30 | SOI Photonics<br>Dr. Jean Marc Fedeli, LETI, France                                |

| 20:00-21:30 | Welcome Reception<br>Hotel Nazaries                                                |

## **Technical Program Schedule**

## Tuesday, January 18<sup>th</sup> Auditorium

| 08:45-09:00                |     | Conference Welcome                                                                                                                                                                                                                                                      |

|----------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09:00-09:40                | 0.1 | Readiness of FDSOI technology platform: overview (Invited) Dr. Carlos Mazuré, SOITEC Chair: Olivier Faynot                                                                                                                                                              |

|                            |     | SESSION 1: SOI CHARACTERIZATION Chair: Sorin Cristoloveanu                                                                                                                                                                                                              |

| 09:40-10:00                | 1.1 | Role of the Bipolar Junction Transistor in the 40nm PD SOI NMOS<br>Device with the Floating Body Effect<br>C. H. Chen, J. B. Kuo                                                                                                                                        |

| 10:00-10:20                | 1.2 | Low-Frequency Noise in UT-SOI Pseudo-MOSFET: Where is the Noise Coming From?  A. El Hajj Diab, I. Ionica, S. Cristoloveanu, F. Allibert, N. Rodriguez, F. Gamiz, M. Bawedin, Y.H. Bae, J. Chroboczek, G. Ghibaudo                                                       |

| 10:20-10:40                | 1.3 | Impact of mobility variation on Vth extraction by transconductance change and gm/ld methods in advanced SOI MOSFETs T. Rudenko, A. Rudenko, V. Kilchytska, M.K. Md Arshad, J.P. Raskin, A. Nazarov, D. Flandre                                                          |

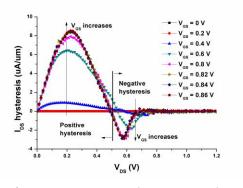

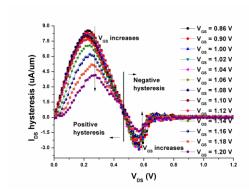

| 10:40-11:00                | 1.4 | Impact of Gate Voltage on Hysteresis Effect in 0.13µm Floating-Body PDSOI n-MOSFETs<br>J. Zhou, S. Cao, C. Gao, S.K. Pang, J.X. Luo, S.C. Zou                                                                                                                           |

| 11:00-11:20                |     |                                                                                                                                                                                                                                                                         |

| 11.00-11.20                |     | Coffee Break                                                                                                                                                                                                                                                            |

| 11:20.12:00                | 0.2 | Coffee Break  EUROPRACTICE (Invited) Dr. Carl Das, IMEC Chair: Cor Claeys  SESSION 2: MEMORIES                                                                                                                                                                          |

|                            | 0.2 | EUROPRACTICE (Invited) Dr. Carl Das, IMEC Chair: Cor Claeys                                                                                                                                                                                                             |

|                            | 2.1 | EUROPRACTICE (Invited) Dr. Carl Das, IMEC Chair: Cor Claeys SESSION 2: MEMORIES                                                                                                                                                                                         |

| 11:20.12:00                |     | EUROPRACTICE (Invited) Dr. Carl Das, IMEC Chair: Cor Claeys  SESSION 2: MEMORIES Chair: Malgorzata Jurczak  A2RAM: Novel dual-body 1T-DRAM cell on ultrathin SOI                                                                                                        |

| 11:20.12:00<br>12:00-12:20 | 2.1 | EUROPRACTICE (Invited) Dr. Carl Das, IMEC Chair: Cor Claeys  SESSION 2: MEMORIES Chair: Malgorzata Jurczak  A2RAM: Novel dual-body 1T-DRAM cell on ultrathin SOI N. Rodríguez, F. Gámiz, S. Cristoloveanu  Scaling of SOI FinFlash Memory with Buried Storage ONO Layer |

| 13:20-15:00 |     | Lunch                                                                                                                                                                                                         |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |     | SESSION 3: MULTIGATE DEVICES Chair: Carlos Mazuré                                                                                                                                                             |

| 15:00-15:20 | 3.1 | Multi-Gate Voltage Selectable Silicon-Nanowire-FETs F. Wessely, T. Krauss, U. Schwalke                                                                                                                        |

| 15:20-15:40 | 3.2 | Comparison of the switching speed in junctionless and accumulation-mode gate-all-around nanowire transistors P. Razavi, R. Yan, I. Ferain, N. Dehdashti Akhavan, R. Yu, J.P. Colinge                          |

| 15:40-16:00 | 3.3 | Fin Shape Influence on Analog Performance of MuGFETs at Room and at Low Temperature<br>R. T. Bühler, J. A. Martino, P. G. D. Agopian, R. Giacomini, E. Simoen, C. Claeys                                      |

| 16:00-17:00 |     | RAMP SESSION:<br>The contribution of SOI in the brilliant future of Nanoelectronics<br>Chair: Francis Balestra                                                                                                |

| 17:00-17:20 |     | Coffee Break                                                                                                                                                                                                  |

|             |     | SESSION 4: POSTER Chairs: Carlos Sampedro & Noel Rodríguez                                                                                                                                                    |

| 17:20-18:30 |     | Oral Presentations                                                                                                                                                                                            |

| 18:30-19:30 |     | Posters Exhibition with Wine & Cheese                                                                                                                                                                         |

|             | 4.1 | Hole Tunneling from Valance Band and Hot-Carrier Induced Hysteresis Effect in 0.13 $\mu$ m Partially Depleted SOI n-MOSFETs J. Zhou, S. K. Pang, S. Cao, S. C. Zou                                            |

|             | 4.2 | Highly Bi-Axially Orientation-Controlled Si Thin Films on Glass<br>Substrates by Double-Line-Beam CW Laser Annealing<br>S.Kuroki, Y. Kawasaki, S. Fujii, K. Kotani, T. Ito                                    |

|             | 4.3 | Extraction of flat-band voltage and parasitic resistance in junctionless MuGFETs A.N. Nazarov, C.W. Lee, A. Kranti, I. Ferain, R. Yan, N. Dehdashti Akhavan, P. Razavi, R. Yu, JP Colinge                     |

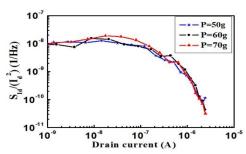

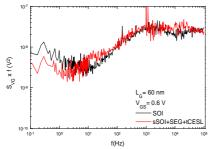

|             | 4.4 | Low Frequency Noise Spectroscopy in Advanced nFinFETs R. Talmat, H. Achour, B. Cretu, J.M. Routoure, A.Benfdila, R. Carin, N. Collaert, A. Mercha, E. Simoen, C. Claeys                                       |

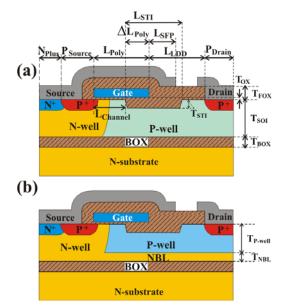

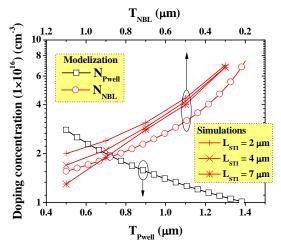

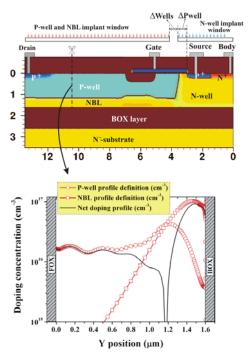

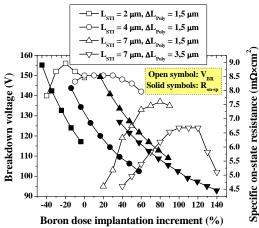

|             | 4.5 | Analysis and Optimization of Lateral Thin-Film Siliconon-Insulator (SOI) PMOS Transistor with an NBL layer in the Drift Region I. Cortés, G. Toulon, F. Morancho, D. Flores, E. Hugonnard-Bruyère, B. Villard |

|             | 4.6 | Ballistic Spin Field-Effect Transistors Built on Silicon Fins<br>D. Osintsev, V. Sverdlov, Z. Stanojevic, A. Makarov, S. Selberherr                                                                           |

|             | 4.7 | Analog Performance of 60 MeV Proton-Irradiated SOI MuGFETs with Different Strain Technologies P.G.D. Agopian, J.A. Martino, D. Kobayashi, M. Poizat, E. Simoen and C. Claeys                                  |

4.8 Simulation of non-standard multilayer 3D SOI-Structures and Microcavities

I.T. Kogut, A.A. Druzhinin, V.I. Holota, V.V. Dovhij

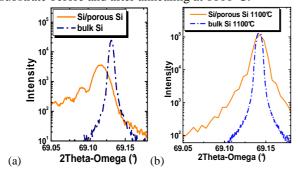

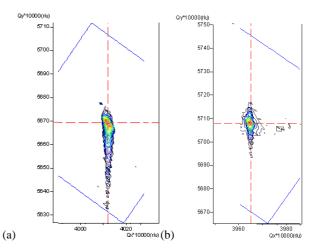

4.9 Strain investigation in Silicon-On-Porous Layer substrates and its evolution upon high temperature thermal treatment

A.S. Stragiera, T. Signamarcheixa, P. Gergauda, T. Salvetata, C. Degueta, M. Lemitib

4.10 Analytical Model for the Threshold Voltage of Junctionless Nanowire Transistors

R. D. Trevisoli, M. A. Pavanello, R. T. Doria, M. de Souza, C. W. Lee, I. Ferain, N. Dehdashti Akhavan, R. Yan, P. Razavi, R. Yu, A. Kranti, J. P. Colinge

4.11 GIDL behavior with different TiN metal gate thickness and high-k gate dielectric on MuGFET devices

M. Galeti, M. Rodrigues, J.A. Martino, N. Collaert, E. Simoen, C. Claeys

- 4.12 Effect of phonon confinement on heat dissipation in ridges P.O. Chapuis, M. Prunnila, A. Shchepetov, L. Schneider, S. Laakso, J. Ahopelto, C.M. Sotomayor Torres

- 4.13 Design of Silicon Double Gate Tunnel FETs with Ultra Low Ambipolar Currents

C. Anghel, A. Vladimirescu, A. Amara

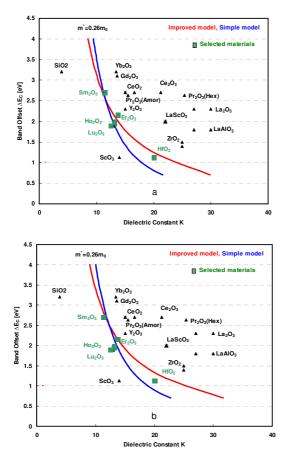

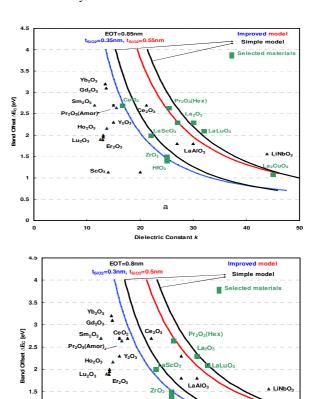

- 4.14 Study of Potential High-k Dielectrics for sub 15 nm UTB SOI MOSFETs, Using Analytical Models of the Gate Tunneling Leakage G. Darbandy, F. Lime, A. Cerdeira, M. Estrada, S.I. Garduño, B. Iñiguez

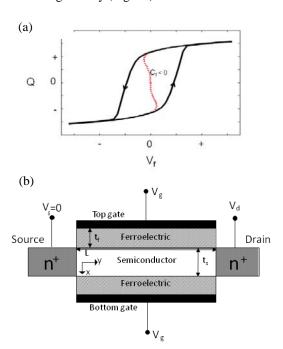

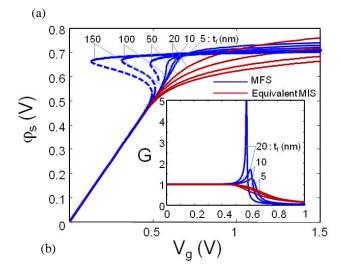

- 4.15 Surface potential amplification model for the negative capacitance double-gate FET

D. Jiménez, E. Miranda, A. Godoy

- 4.16 Influence of single-atom impurity scattering on quantum transport in silicon nanowire transistors

N. Dehdashti Akhavan, I. Ferain, R. Yan, P. Razavi, R. Yu, J.P Colinge

- 4.17 Charging Effects in the MOS Structures with Silicon Nanocrystals Embedded in SiO2

B. Majkusiak, A. Mazurak, A. Kshirsagar, J. Ruzyllo

- 4.18 Rotated SOI MuGFETs at High Temperatures

T. Nicoletti, S. D. dos Santos, L.M. Almeida, J.A. Martino, E. Simeón, C. Claeys

- 4.19 A Short-Channel Analytical Model for Triple-gate and Planar FDSOI Transistors

R. Ritzenthaler, F. Lime, B. Nae, O. Faynot, S. Cristoloveanu, B. Iñiguez

- 4.20 An inversion charge model for n-type and p-type DGMOSFETs accounting for different substrate Orientations

M. Balaguer, J.B. Roldán, L. Donetti, F. Gámiz

- 4.21 An analytical electric potential model for square Gate-All-Around MOSFETs

E. Moreno, J. Roldán, F.G. Ruiz, A. Godoy, D. Barrera, M.J. Ibáñez, F. Gámiz

4.22 OCTO SOI MOSFET: An Evolution of the Diamond to Be Used in the Analog Integrated Circuits

S. Pinillos Gimenez, D. Manha Alati

4.23 A Compact Double-Gate MOSFET Model Consistent with a Multi-Subband Ensemble Monte Carlo Model

M. Cheralathan, C. Sampedro, J.B. Roldán, F. Gámiz, B. Iñiguez

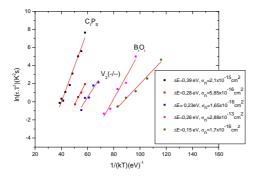

- 4.24 1/f Noise in Strained SGOI MOSFETs

J. Gyani, J. El Husseini, F. Martinez, M. Bawedin, M. Valenza, C. Le Royer, J. F. Damlencourt

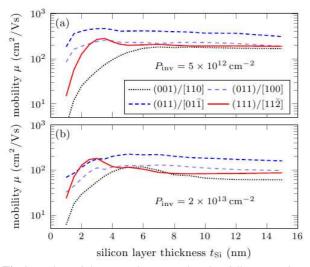

- 4.25 Influence of the orientation and geometry on the Phonon-limited Mobility of Square Silicon Gate-All-Around MOSFETs

I. M. Tienda-Luna, F. G. Ruiz, A. Godoy, F. Gámiz

- 4.26 Subband Engineering in n-Type Silicon Nanowires using Strain and Confinement

Z. Stanojevic, V. Sverdlov, O. Baumgartner, H. Kosina

- 4.27 Quantum computing on silicon-on-insulator structure S. Filippov, V. Vyurkov, A. Orlikovsky

- 4.28 Asymmetric Series Association of SOI MOSFET to Improve the Device Analog Characteristics

I. C. B. Santos, M. de Souza, D. Flandre, M. A. Pavanello

- 4.29 Impact of Mismatch on the Analog Properties of Standard and Graded-Channel SOI nMOSFETs

M. de Souza, D. Flandre, M.A. Pavanello

- 4.30 Insights on Device Performance of SOI MOSFET with 60 nm and 15 nm BOX Thickness

A. Suhaila Mohd Zain, B. Cheng, X. Wang, A. Asenov

- 4.31 Using Diamond SOI nMOSFETs to Improve the Frequency Response of the Analog Integrated Circuits S. Pinillos Gimenez, R. Claser, D. Manha Alati

- 4.32 DFT Simulation of SOI Devices: Semiconductor/Oxide Interfaces

B. Biel, L. Donetti, A. Godoy, F. Gámiz

- 4.33 Multi-Subband Monte Carlo Simulation of Oxide Thickness

Fluctuation on SGSOI MOSFETs

R. Valin, C. Sampedro, N. Seoane, M. Aldegunde, A. Garcia-Loureiro, A. Godoy, and F. Gamiz

- 4.34 Universal relationship between substrate current and history effect in SOI MOSFETs and its importance for physical compact modeling

A. Toda, N. Higashiguchi, K. Ohyama, Y. Shintaku, S. Amakawa, M. Miyake, H. Kikuchihara, M. Miura-Mattausch

20:00 Bus for Gala Dinner

## Wednesday, January 19<sup>th</sup> Auditorium

| 09:00-09:40 | 0.3 | Issues on the Physics of Electronic Transport in 10 nm-scale SOIs:How Far Can We Go? Prof. Massimo V. Fischetti, UTDallas Chair: Francisco Gámiz                                                                                                        |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |     | SESSION 5: Device Physics Chair: Sigfried Mantl                                                                                                                                                                                                         |

| 09:40-10:00 | 5.1 | Confinement-Induced Mobility Increase in p-type [110] and [111]<br>Silicon Nanowires<br>N. Neophytou, H. Kosina                                                                                                                                         |

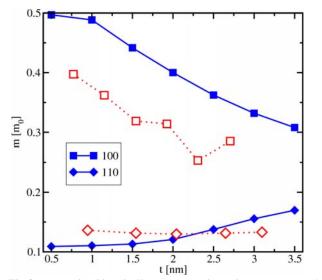

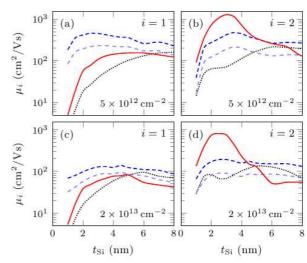

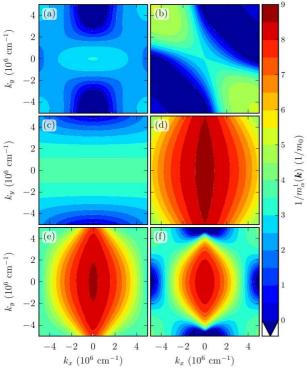

| 10:00-10:20 | 5.2 | Transport mass of holes in ultra-thin DGSOI devices L. Donetti, F. Gámiz, F. Martínez-Carricondo, J.L.Padilla, N.Rodriguez                                                                                                                              |

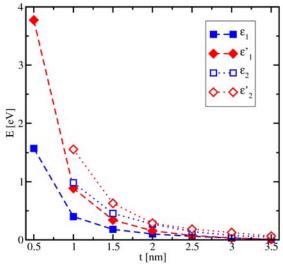

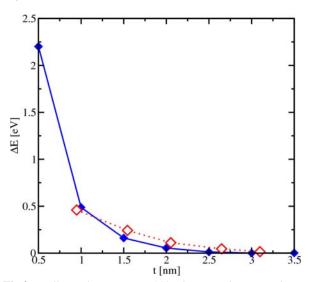

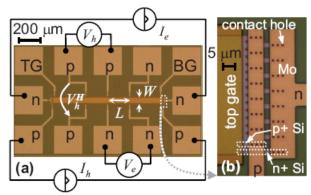

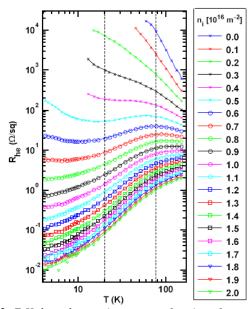

| 10:20-10:40 | 5.3 | Electron-Hole Bi-Layers in Ultra-Thin SOI-Devices<br>S. Laakso, M. Prunnila, J. Ahopelto                                                                                                                                                                |

| 10:40-11:00 | 5.4 | Dispersion of Confined Acoustic Phonons in Ultra-Thin Silicon<br>Membranes<br>J. Cuffe, E. Chavez, P-O. Chapuis, E. H. El Boudouti, F. Alzina, D. Dudek, Y. Pennec, B. Djafari-Rouhani, A. Shchepetov, M. Prunnila, J. Ahopelto, C. M. Sotomayor Torres |

| 11:00-11:20 |     | Coffee Break                                                                                                                                                                                                                                            |

| 11:20-12:00 | 0.4 | Nanoelectronics: a bright future? (Invited) Mrs. Gisele Roesems, EU Commission Chair: Andrés Godoy                                                                                                                                                      |

|             |     | SESSION 6: ADVANCED SIMULATION Chair: Massimo V. Fischetti                                                                                                                                                                                              |

| 12:00-12:20 | 6.1 | Reaching sub-32nm nodes: SGSOI optimization C. Sampedro, F. Gámiz, L.Donetti, A. Godoy                                                                                                                                                                  |

| 12:20-12:40 | 6.2 | 3D Monte Carlo simulations of a 25 nm gate length SOI FinFET using unstructured tetrahedral grids<br>M. Aldegunde, A.J. Garcia-Loureiro, N. Seoane, R. Valin, K. Kalna                                                                                  |

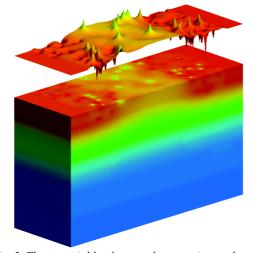

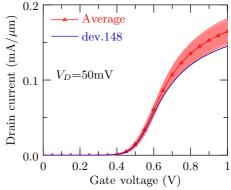

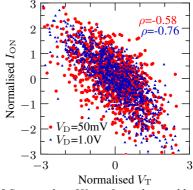

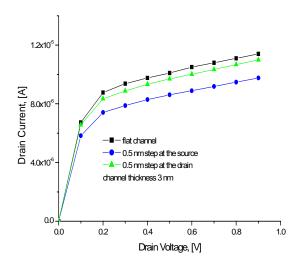

| 12:40-13:00 | 6.3 | Comprehensive Simulation Study of Statistical Variability in 32nm SOI MOSFET<br>N. M. Idris, B. Cheng, A. R. Brown, S. Markov, A. Asenov                                                                                                                |

| 13:00-13:20 | 6.4 | Quantum simulation of an UTB FD SOI FET with channel imperfections V. Vyurkov, I. Semenikhin, A. Orlikovsky                                                                                                                                             |

| 13:30-15:00 |     | Lunch                                                                                                                                                                                                                                                   |

|             |     | SESSION 7: ANALOG PERFORMANCE & CIRCUITS  Chair: João Antonio Martino                                                                                                                                       |

|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:00-15:20 | 7.1 | 65nm Partially Depleted SOI Output Buffer with Active Body-<br>Biasing Control<br>D. Soussan, S. Majcherczak, A. Valentian, M. Belleville                                                                   |

| 15:20-15:40 | 7.2 | A circuit level 65nm node bulk and SOI technologies comparison for analog amplifiers<br>G. Pollissard-Quatremère, D. Flandre                                                                                |

| 15:40-16:00 | 7.3 | Ultra-thin body and BOX SOI Analog Figures of Merit<br>V. Kilchytska, M.K. Md Arshad, S. Makovejev, S. Olsen, F. Andrieu, O. Faynot, J.P. Raskin, D.<br>Flandre                                             |

| 16:00-16:20 | 7.4 | Temperature Influence on the Analog Performance of 450 Rotated Triple-Gate nFinFETs<br>M. A. Pavanello, M. de Souza, J. A. Martino, E. Simoen, C. Claeys                                                    |

| 16:20-16:40 |     | Coffee Break                                                                                                                                                                                                |

|             |     | SESSION 8: SOI DEVICES Chair: Jouni Ahopelto                                                                                                                                                                |

| 16:40-17:00 | 8.1 | TiN/GdScO3/strained Si0.5Ge0.5/SSOI stack for high mobility short channel p-MOSFETs R. A. Minamisawa, J. M. J. Lopes, M. Schmidt, E. Durgun Özben, JM. Hartmann, D. Buca, J. Schubert, Q. T. Zhao, S. Mantl |

| 17:00-17:20 | 8.2 | 2D Analytical Calculation of the Current in Lightly Doped Schottky<br>Barrier DG MOSFET<br>M. Schwarz, A. Kloes, B. Iñíguez                                                                                 |

| 17:20-17:40 | 8.3 | LDMOS transistors on 150 mm silicon-on-polycrystalline-silicon carbide hybrid substrates<br>S. Lotfi, Ö. Vallin, LG. Li, L. Vestling, H. Norström, J. Olsson                                                |

| 17:40-18:00 | 8.4 | Lateral Transient Voltage Suppressor for SOI Technologies<br>J. Urresti, S. Hidalgo, I. Cortés, D. Flores                                                                                                   |

## **End of EUROSOI 2011**

### **Session 1: SOI Characterization**

**Chair: Sorin Cristoloveanu**

## Role of the Bipolar Junction Transistor in the 40nm PD SOI NMOS Device with the Floating Body Effect

C. H. Chen, J. B. Kuo\*

Dept. of Electrical Eng, BL-528, National Taiwan University Roosevelt Rd. Sec 4, Taipei, Taiwan 106-17 \*Currently with Peking University, Shenzhen, China 518055 Email: jbkuo@cc.ee.ntu.edu.tw

Abstract-This paper reports the role of the parasitic bipolar device in the 40nm PD SOI NMOS device with the floating body effect. Using a unique extraction method, the function of the parasitic bipolar device during transient operations could be modeled. During the turn-on transient by imposing a step voltage from 0V to 2V at the gate, the case with a slower rise time shows a faster turn-on in the drain current due to a stronger function of the parasitic bipolar device from smaller displacement currents through the gate oxide, as reflected in the current gain, as verified by the experimentally measured results.

#### I. Introduction

Floating body effect of PD SOI CMOS devices have been studied intensively in the past [1][2]. The parasitic bipolar device in the PD device, which could cause the Kink effect, is difficult to model [3][4]. In fact, the parasitic bipolar device is important for the behavior of the PD SOI CMOS devices. In this paper, using a unique extraction method, the function of the parasitic bipolar device during DC and transient operations could be modeled. In the following section, the test device is described first, followed by the DC and the transient operations and discussion.

#### II. 40nm PD SOI NMOS Device

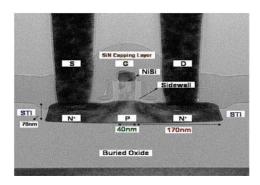

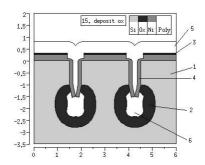

Fig. 1 TEM cross section of the 40nm PD SOI NMOS device under study.

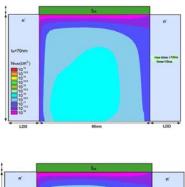

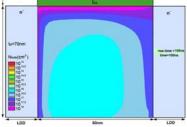

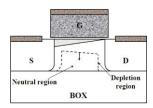

Fig. 1 shows the TEM cross section in the channel length direction of the 40nm PD SOI NMOS device under

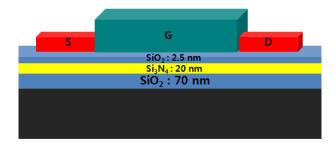

study [3]. The test device has a 70nm thin film doped with a p-type doping density of  $3x10^{18} \text{cm}^{-3}$  above a buried oxide of 145nm and a gate oxide of 1.5nm. A 65nm LDD region doped with an n-type density of  $10^{19} \text{cm}^{-3}$  under a sidewall spacer has been used. A nickel polycide is formed on the top of the gate and a SiN capping layer is deposited over the device. The effective channel length of the device is 40nm. Experimental measurement of the test device and 2D device simulation have been used to carry out the study.

#### III. Transient Operation

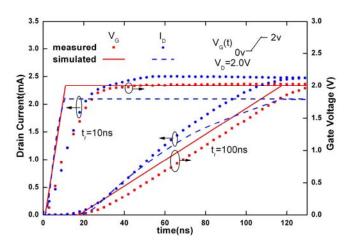

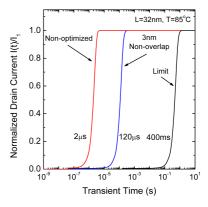

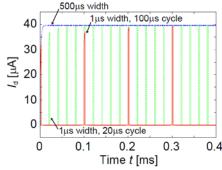

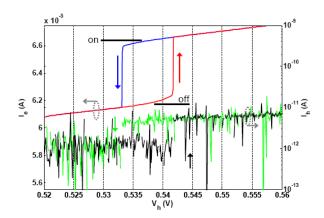

Fig. 2. Drain current of the test device during the turn-on transient by imposing a step voltage from 0V to 2V at the gate based on experimentally measured data and the 2D simulation .

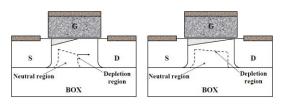

The behavior of the parasitic bipolar device during the transient of the PD SOI NMOS may be quite different from that operating at DC. Fig. 2 shows the drain current of the PD device during the turn-on transient by imposing a step voltage from 0V to 2V at the gate of the test device based on the experimentally measured data and 2D simulation result for the cases with the rise times of 10ns and 100ns. As shown in the figure, with a rise time of 10ns for the gate voltage, the drain current could not reach its peak value at the end of the gate voltage ramp while with a rise time of 100ns, it almost reaches it. The different slew rates of the drain current curves during the ramp up transients between the cases with different rise times may have some implications.

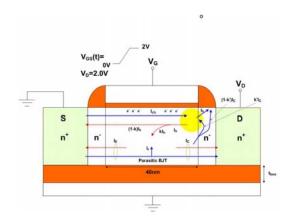

Fig.3.Current conduction mechanism during the turn-on transient by imposing a step voltage from 0V to 2V at the gate of the test device.

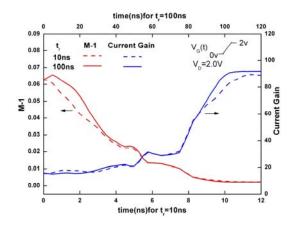

Fig. 4. Multiplication factor (M-1) and current gain of the parasitic bipolar device of the PD SOI NMOS device during the turn-on transient the gate for the cases with the rise times of 10ns and 100ns.

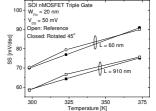

Fig. 3 shows the current conduction mechanism during the turn-on transient by imposing a step voltage from 0V to 2V at the gate of the test device. Different from the DC condition, during the turn-on transient, the drain and the source displacement currents (dQp/dt, dQs/dt) through the gate oxide need to be considered. Taking into account the partitioned charge model (Qs, QD) for the surface channel of the device with the current conduction mechanism described in the DC condition, one may obtain the multiplication factor (M-1) and the current gain of the parasitic bipolar device during the turn-on transient of the test device. Fig. 4 shows the multiplication factor (M-1) considering the impact ionization in the postsaturation region in the lateral channel and the current gain of the parasitic bipolar device of the PD SOI NMOS device during the turn-on transient by imposing a step voltage from 0V to 2V at the gate for the cases with the rise times of 10ns and 100ns based on the 2D simulation result. As shown in the figure, along with the progress of time during the ramp-up period, the multiplication factor (M-1) decreases due to the increase of the gate voltage leading to a smaller post-saturation region. On the other hand, when the gate voltage is small during the initial stage of the ramp-up period, the current gain of the parasitic bipolar device is relatively small, indicating that the parasitic bipolar device is not turned on yet. During the final stage of the gate ramp-up period, the current gain suddenly increases, which implies the turn-on of the parasitic bipolar device. As shown in the solid-lines, for the case with the longer rise time of 100ns, both M-1 and the current gain are larger, which means the impact ionization in the post-saturation region is larger and the parasitic bipolar device functions stronger.