# **WiserBAN**

Project Acronym: WiserBAN

Project Title: Smart miniature low-power wireless microsystem for Body Area Networks

Call: FP7-ICT-2009-5, Collaborative project

**Grant Agreement no.:** 257454

**Project Duration:** 36 months

**Coordinator: CSEM**

#### **Beneficiaries:**

| CSEM Centre Suisse D'Electronique et de Microtechnique SA – CSEM Recherche et Development |            |    |  |  |

|-------------------------------------------------------------------------------------------|------------|----|--|--|

| Commissariat a L'Energie Atomique et aux Energies Alternatives                            | CEA        | FR |  |  |

| Fraunhofer-Gesellschaft zur Foerderung der Angewandten Forschung E.V.                     | FRAUNHOFER | DE |  |  |

| Valtion Teknillinen Tutkimuskeskus                                                        | VTT        | FI |  |  |

| Technische Universitat Berlin                                                             | TUB        | DE |  |  |

| Alma Mater Studiorum-Universita di Bologna                                                | UNIBO      | IT |  |  |

| Sorin CRM SAS                                                                             | SORIN      | FR |  |  |

| EPCOS SAS                                                                                 | EPCOS      | FR |  |  |

| MED-EL Elektromedizinische Geraete GmbH                                                   | MED-EL     | AT |  |  |

| Siemens Audiologische Technik GmbH                                                        | DE-SAT     | DE |  |  |

| Debiotech S.A.                                                                            | DEBIOTECH  | СН |  |  |

| SignalGeneriX Ltd                                                                         | SG         | CY |  |  |

| RTD TALOS Ltd                                                                             | TALOS      | CY |  |  |

# **WiserBAN**

# Smart miniature low-power wireless microsystem for

# **Body Area Networks**

**Deliverable identifier:** D4.2

**Deliverable title:** Characterization & Validation of the 1<sup>st</sup> Base-Band version

Due date of deliverable: M18, February 29, 2012

Actual submission date: M21, May 21, 2012

**Start day of project:** 01/09/2010

**Duration:** 36 months

WP Number: WP 4 BAN MAC/Protocol and data processing

Organization name of lead partner for this deliverable (partner name): CEA

Author(s): L. Ouvry, F. Dehmas, E. Mercier. S. Thuries, M. Maman (CEA), C. Buratti, F. Martelli, R. Rosini, R. Verdone (UNIBO), M-N. Morgan, D. Severac, E. Le Roux (CSEM), K. Michaelides, D. Doumenis (SG)

**Document Status: Delivered**

| Pr | Project funded by the European Commission within the Seventh Framework Programme      |   |  |

|----|---------------------------------------------------------------------------------------|---|--|

|    | Dissemination Level                                                                   |   |  |

| PU | Public                                                                                |   |  |

| PP | Restricted to other programme participants (including the Commission Services)        |   |  |

| RE | Restricted to a group specified by the consortium (including the Commission Services) |   |  |

| СО | Confidential, only for members of the consortium (including the Commission Services)  | х |  |

# **Revision History**

| Version | Date        | Changed page(s) | Cause of change        | Partner     |

|---------|-------------|-----------------|------------------------|-------------|

| V0.1    | Mar 05 2012 |                 | Creation               | CEA         |

| V0.2    | Mar 19 2012 |                 | Section 3 & 5 have     | CEA, SG     |

|         |             |                 | been integrated        |             |

| V0.3    | Mar 21 2012 |                 | Section 6 has been     | Uni Bo, CEA |

|         |             |                 | integrated             |             |

| V0.4    | Mar 27 2012 |                 | Introduction &         | CEA         |

|         |             |                 | conclusion             |             |

| V0.5    | Apr 5 2012  |                 | Modified contribution  | CSEM &      |

|         |             |                 |                        | UNIBO       |

| V0.6    | Apr 9 2012  |                 | Pre-final review       | CSEM        |

| V0.7    | Apr 17 2012 |                 | Latest contributions & | CEA         |

|         |             |                 | improvements           |             |

| V0.8    | Apr 27 2012 |                 | Latest contributions   | CSEM        |

|         |             |                 | from CSEM              |             |

| V0.9    | May 21 2012 |                 | Final review before    | CSEM        |

|         |             |                 | submission             |             |

|         |             |                 |                        | _           |

|         |             |                 |                        | _           |

Disclaimer: The information in this document is subject to change without notice. Company or product names mentioned in this document may be trademarkers or registered trademarks of their respective companies.

# All rights reserved.

The document is proprietary of the WiserBAN consortium members. No copying or distributing, in any form or by any means is allowed without the prior written agreement of the owner of the property rights.

This document reflects the authors' view. The European Community is not liable for any use that may be made of the information contained herein.

# Contents

| C | ontents |                                                                | 4  |

|---|---------|----------------------------------------------------------------|----|

| E | xecutiv | e Summary                                                      | 6  |

| 1 | Intro   | oduction                                                       | 7  |

|   | 1.1     | Goals and methodology                                          | 7  |

|   | 1.2     | Digital system to validate                                     | 7  |

| 2 | Digi    | tal BaseBand validation                                        | 9  |

|   | 2.1     | D-BB implementation for the receiver                           | 9  |

|   |         | D-BB RX test methodology and validation                        |    |

|   | 2.3     | D-BB implementation for the transmitter                        | 20 |

|   | 2.4     | D-BB TX test methodology and validation                        | 25 |

| 3 | Proc    | essor unit validation                                          | 27 |

|   |         | Pre-integration validation                                     |    |

|   |         | Post-integration validation of the functionality               |    |

|   |         | Released package of the processor unit for the FPGA validation |    |

| 4 |         | A implementation                                               |    |

| 4 |         | •                                                              |    |

|   | 4.1     | General architecture                                           | _  |

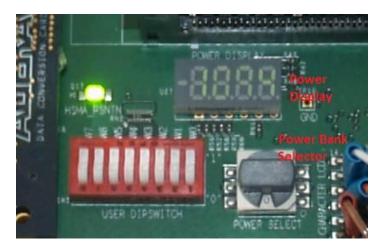

|   | 4.1.1   | Hardware Used                                                  |    |

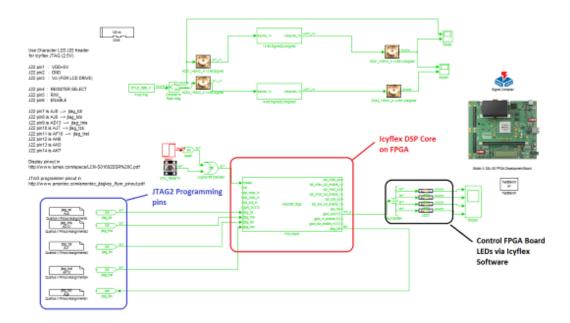

|   | 4.1.2   | Programming the icyflex core into the FPGA                     | 34 |

|   | 4.2     | Methodology for the validation of the SoC complete digital     | 37 |

|   | 4.3     | Results of the FPGA validation                                 | 40 |

|   | 4.3.1   | Synthesized D-BB Rx VHDL Code Validation                       | 41 |

|   | 4.3.2   | Synthesized icyflex VHDL Code Validation                       | 43 |

| 5 | BAN     | specific protocol implementation and validation                | 44 |

|   | 5.1     | General description of the protocol                            | 44 |

|   | 5.2     | Simulation results related to propagation measurements         | 46 |

|   | 5.2.1   | Measurements set                                               | 46 |

|   | 5.2.2   | Simulation settings and scenario                               | 47 |

|   | 5.2.3   | Simulation Results                                             | 49 |

|   | 5.2.4   | Conclusions                                                    | 56 |

|   | 5.3     | BAN Protocol implementation                                    | 57 |

|   | 5.3.1   | The Software Architecture                                      | 57 |

|   | 5.3.2   | The Software Implementation                                    | 66 |

| 6 | Con | clusions             | 68 |

|---|-----|----------------------|----|

| 7 | Ann | nexes                | 69 |

|   | 7.1 | List of Tables       | 69 |

|   | 7.2 | List of Figures      | 70 |

|   | 7.3 | List of references   | 73 |

|   | 7.4 | <b>Ahhreviations</b> | 73 |

# **Executive Summary**

The WiserBAN project will create an ultra-miniature and ultra low-power RF microsystem for wireless Body Area Networks (BAN) targeting primarily wearable and implanted devices for healthcare, biomedical and lifestyle applications.

The proposed research concerns the extreme miniaturization of the BAN with primarily the areas of ultra low-power radio SoC (System on Chip), RF and Low-frequency MEMS, miniature reconfigurable antennas, miniaturized SiP (System in Package), sensor signal processing and flexible communication protocols.

The WiserBAN microsystem will be 50 times smaller than today's radio modules for Personal Area Networks (PAN) solutions, e.g. Bluetooth, that can simply not be embedded in a variety of tiny implants and wearable applications. WiserBAN will thus enable significant take up by the European SME's and industries in healthcare, bio-medical and lifestyle.

WiserBAN will also create a major impact on the quality of life of the European Citizens, in particular for improving the comfort and access to ICT for impaired and disabled people of all ages carrying implants or wearing medical devices, hence reducing the risk of social exclusion.

WP4 will consist in the design, simulation and validation of the digital part of the BAN radio microsystem, which entails the radio transceiver baseband, MAC units (soft & hard), and the sensor data processing unit.

#### About this deliverable D4.2:

This deliverable is the second one of the WP4 within the WiserBAN project, and concerns all the tasks T4.1, T4.2 and T4.3 which are:

• Task 4.1 Reconfigurable Baseband and MAC objectives:

Design and develop both the baseband and the hardware MAC entities to be attached to the smart RF components which WP2 will provide,

Design reconfigurable MAC entities, through reprogramming, for greater flexibility in the applications requirements/constraints that WiserBAN will address.

• Task 4.2 Low Power BAN Protocol objectives:

Design an energy efficient BAN protocol architecture with the support for various applications requirements (variable data-rates, quality-of-service, reliability, priorities, directions of flows, etc.) and the support of coexistence, cooperation and compliance with existing BAN/PAN architectures.

• Task 4.3 Low-power sensor data processing unit objectives:

Develop and integrate a high-performance, low-power, DSP-based unit at the core of the application layer. This DSP-based unit will be in charge of Running the basic MAC protocol (T4.2) and controlling the interfaces with the other system or applicative parts. The application data processed by this unit will be used to feed the MAC layer below it.

It shall link the applications, scenarios, and platform requirements from WP1 to the research done within WP4 on the MAC protocol and the reconfigurable digital baseband. In particular, requirements on the quality of services to comply with the different scenarios shall be analysed from the protocol perspective, taking into account existing standards like Bluetooth Low Energy or IEEE802.15.6. The objective is in a first place to provide solutions as much as possible compliant with standards or to justify proprietary choices.

#### 1 Introduction

# 1.1 Goals and methodology

The D4.2 deliverable goals are:

- To provide characterization and validation results of the digital blocks which have been designed in the scope of the implementation into the WiserBAN SoC.

- To validate the methodology for the validation of the digital blocks and settle a high level of confidence in the developed blocks for an expected successful SoC release.

- To demonstrate the good interoperability of the various blocks designed by the partners in different places.

- To elaborate and validate by simulation a complete protocol including outcomes from around-the-body propagation measurements.

The deliverable content is organized accordingly with sections addressing:

- the VHDL code development for the D-BB Rx and Tx, and for the icyflex DSP processor and associated peripherals,

- the validation of these codes on a high-level simulation platform,

- · the validation of digital part integrated into MPW1 SoC,

- the validation of these codes on a FPGA platform,

- the implementation of the associated protocol taking into account the specific BAN environment.

The different validations described above are covering different parts with different coverage limitations that are explained in respective sections. The limitations are linked to a usual effort-coverage trade off. But finally, the validation must provide a good confidence on digital system integration quality.

# 1.2 Digital system to validate

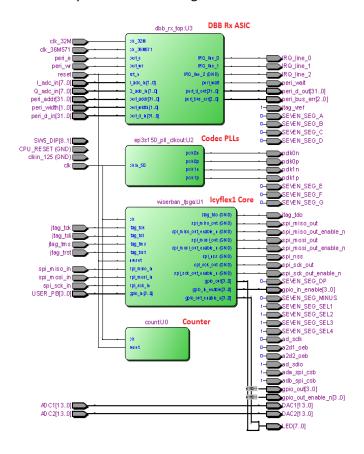

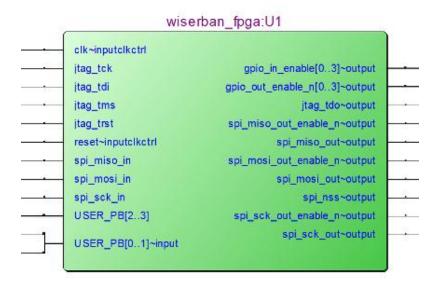

The purpose of section 2 is to introduce from a high-level the architecture of the building blocks described hereafter. They include the D-BB Rx and D-BB Tx, the interface to the icyflex and some elements to build a HW MAC, the icyflex itself and the implementation of the whole onto an FPGA platform, and the context of the related protocols using outcomes from propagation measurements. In this deliverable, characterization elements and validation process resulting from dedicated tests are introduced and detailed.

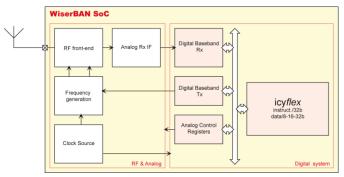

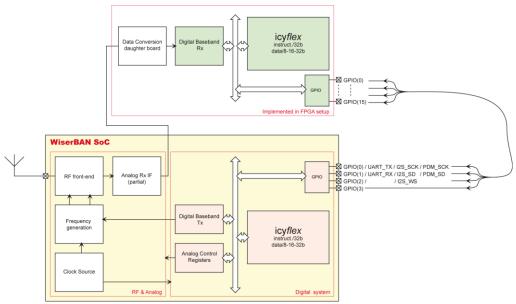

The implementation of the WiserBAN digital system includes the Tx and Rx Digital BaseBand which processes the received signal and manages the low-level protocol elements, the processor which supports the software of application and high-level protocol elements.

Regarding the D-BB Rx, it is composed of many different blocks, derived from the algorithms to down convert the signal to Base-Band, filter it out, and finally demodulate the information. The inputs of this part are made of bits from the Anolog-to-Digital Converter, directly from the analog domain. The outputs are packaged into buffers, registers and are also signals like interrupts in a format which is compatible with the processor. This part has yet not been integrated into the first SoC, so the validation which is provided with here in this deliverable is based on high-level simulations experiencing various scenarii of interest. These simulations are optimized to limit the dead zone, where validation is missing and remaining errors or mismatches may be uncharacterized. This is described in Section 3.

On the D-BB Tx side, a similar approach has also been considered. The inputs come from the processor through registers and the output consists in the modulation of the RF signal by dynamic digital control of the RF synthesizer. Some interrupts are also generated to inform the processor about the status of the transmission. This is described in Section 3.

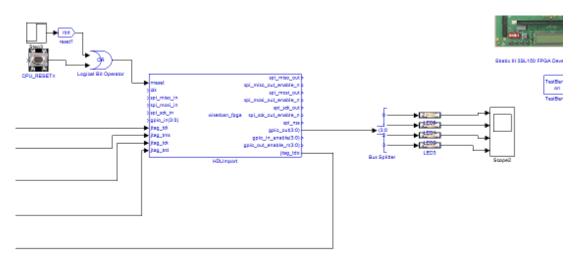

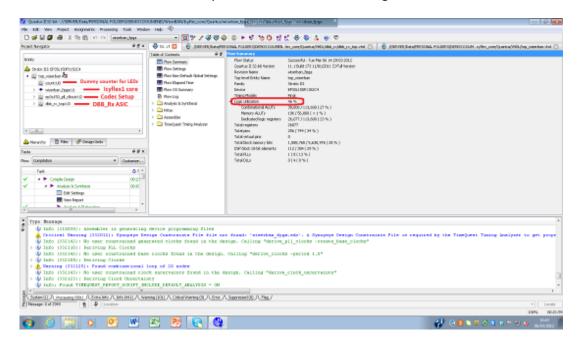

Once the VHDL code has been generated and validated in-depth, it is also possible to consider its implementation on an actual hardware platform like an FPGA. This is done thanks to a specific development which will also be of interest for the implementation of the application software and protocol before the final SoC is ready. Thereby, the correctness of the connectivity between the various blocks — D-BB Rx and Tx, icyflex core, IRQ manager, icyflex bus — can be confirmed in an alternative manner to the simulation one. The implementation of this hardware platform and its use is described in the Section 5.

As above-described, the principle of the characterization and validation of the digital blocks is also applied to the protocol elements. It is based on codes which have been developed taking into account actual conditions related to BAN propagation. First, simulations are carried out to validate the interest of this dedicated protocol, and second its further preliminary implementation onto a hardware target will help to finalize and refine it before it is used into the final WiserBAN module. To this end, the Icycom platform has been chosen as it integrates an icyflex core and an associated RF transceiver (not carrier frequency and data rate compatible). In Section 6 is detailed the implementation of the protocol and its validation on a simulation platform.

# 2 Digital BaseBand validation

This section describes the D-BB Rx and Tx in a straightforward way, and detail the validation methodology as well as the simulation & measurements results obtained using an adequate set of test benches and simulation environment.

## 2.1 D-BB implementation for the receiver

The D-BB Rx has been developed to support the specifications of the WiserBAN protocol. As it considers three different modulation schemes, the D-BB Rx must be flexible enough to enable the reception of all these expected schemes. These three modulation schemes are listed below:

- IEEE802.15.4: a O-QPSK modulation at 2 Mcps and 250 kbps

- BT-LE: a GMSK modulation with a maximum data rate of 1 Mbps

- proprietary 2Mbps: based the O-QPSK modulation of the IEEE802.15.4

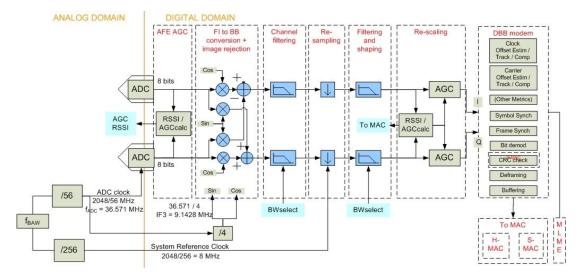

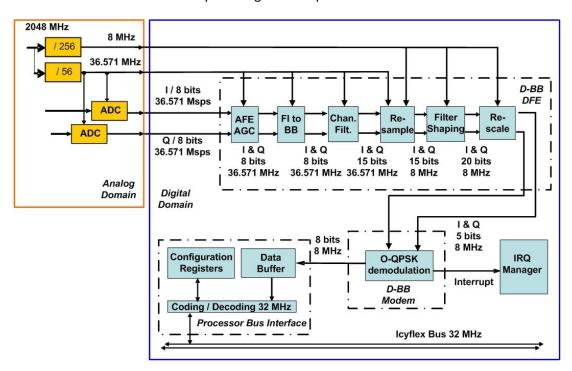

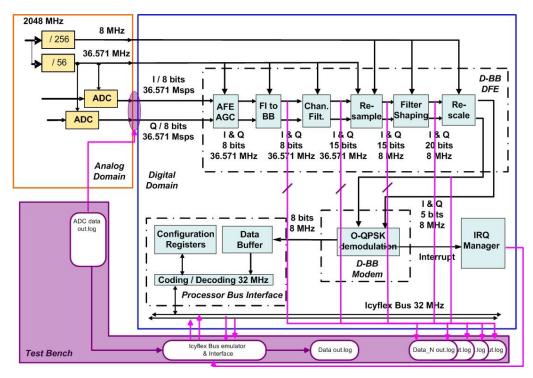

The D-BB Rx follows an analog front-end which process the signal in a BandPass Sampling way. Right before the D-BB Rx, there is an ADC running at 36.571 MHz with a resolution of 8 bits. It converts an IF signal which has been sampled much below the Nyquist criterion (subsampling ratio of 14). The D-BB is split between two main parts. First, a Digital Front-End (D-FE) follows the ADC. It is composed of a modified Weaver cell which mixes the I and Q paths, a low-pass filter, a resampling stage which shift the signal from the 36.571 MHz domain to the 8 MHz one, a low-pass shaping filter. After this D-FE, the signal is processed in the Modem, which realizes the demodulation and data buffering.

In the D-FE, no specific process is done with regards to the expected modulation, except the coefficient choice for the filtering stages (BT-LE is narrower). This D-FE is mostly modulation independent. In the Modem, specific blocks are implemented to address the three various schemes.

Figure 2-1: Synoptic of the full D-BB including the D-FE and the Modem

The overall D-BB is monitored and controlled thanks to configuration registers which are directly connected to the icyflex internal bus. It also provides with Interruptions to enable an easy handling of the communications. These have been designed in relation with the icyflex architecture and use the Interrupt manager of the processor.

Figure 2-2: synoptic of the full-Digital BaseBand

Clocks are provided by the frequency reference based on the 2.048 GHz BAW oscillator. After the signal has been resampled in the D-FE, it is processed by an 8 MHz clock synchronized with the 32 MHz one used in the digital and specifically in the processor.

At the end of the D-BB Rx, the data are buffered in a dedicated buffer which can contain the maximum number of octets specified in a frame - 128 octets.

In addition to this functional architecture of the D-BB Rx, some test modes have been added. They are of three kinds. On one hand, some passive test modes can be used. For instance, the configuration of the blocks can be tuned thanks to the configuration registers. They can be used for instance to fine tune the level of signal which will trigger a synchronization process on the Modem or modify some gain in the chain. Once these parameters have been tested and optimized, they can be documented and the embedded software, using libraries, can set these up, and therefore optimize the functioning of the receiver. The Interrupts signal can also be used as validation and test signal as they propose real-time activation monitoring to known stimuli. On the other hand, active test modes have been implemented to validate the correct functioning of the D-BB Rx, besides try to find out where in the chain any mismatch or issue may be generated. To do so, monitoring the signal at different levels or inject specific signals through registers has been made possible and loop-back techniques employed.

All the D-BB Rx registers are listed below:

| Address                                    | Register                        | R/W | /Size    | Default        | Description                                                               |  |

|--------------------------------------------|---------------------------------|-----|----------|----------------|---------------------------------------------------------------------------|--|

| 0x00 to 0                                  | 0x00 to 0x1F: D-BB_RX registers |     |          |                |                                                                           |  |

| 0x00                                       | DBB_RX_CTRL                     | R/W | 16       | 0x0            | Control register                                                          |  |

| 0x02                                       | DBB_RX_STATUS                   | R   | 16       | 0x0            | DBB_RX status register                                                    |  |

| 0x04                                       | DBB_RX_DEBUG                    | R/W | 8        | 0x0            | Reserved for programmable states enabling internal connections            |  |

| 0x05                                       | DBB_RX_IRQ_ACK                  | R/W | 8        | 0x0            | Interrupt acknowledge register                                            |  |

| 0x06                                       | DBB_RX_IRQ_STATUS               | R   | 16       | 0x0            | Interrupt status register                                                 |  |

| 0x08                                       | DBB_RX_IRQ0_EN                  | R/W | 16       | 0x0            | IRQ0 Interrupt mask register                                              |  |

| 0x0A                                       | DBB_RX_IRQ1_EN                  | R/W | 16       | 0x0            | IRQ1 Interrupt mask register                                              |  |

| 0x0C                                       | DBB_RX_IRQ2_EN                  | R/W | 16       | 0x0            | IRQ2 Interrupt mask register                                              |  |

| 0x0E                                       | DBB_RX_FIFO_RX_THRES            | R/W | 8        | 0x0            | Programmable threshold for the FIFO RX                                    |  |

| 0x10                                       | DBB_RX_FIFO_LOOPBACK_DATA_0     | R/W | 16       | ()x()          | Loopback mode (to DFE or DBB depending mode selected in DBB_RX_CTRL)      |  |

| 0x12                                       | DBB_RX_FIFO_LOOPBACK_DATA_1     | R/W | 16       | ()x()          | Same as DBB_RX_FIFO_LOOPBACK_DATA_1 but generate one pulse in CLK_36M     |  |

| 0x14                                       | DBB_RX_FIFO_RX_DATA             | R   | 32       | ()x()          | DATA from FIFO RX in normal mode (selected in DBB_RX_CTRL)                |  |

| 0x18                                       | DBB_RX_FIFO_LOOPBACK_DUMP       | R   | 32       | ()\(\gamma()\) | Output data dump (from ADC or DFE depending mode selected in DBB_RX_CTRL) |  |

| 0x1C                                       | DBB_RX_VENDOR_ID                | R   | 32       | 0x0            | Vendor ID register                                                        |  |

| 0x20 to 0                                  | 0x2F: D-FE registers            |     | <u>I</u> |                |                                                                           |  |

| 0x20                                       | DBB_RX_DFE_CTRL                 | R/W | 16       | 0x0            | Control register                                                          |  |

| 0x22                                       | DBB_RX_DFE_AFE_AGC_THRES        | R/W | 8        | 0x0            | AFE AGC threshold                                                         |  |

| 0x23                                       | DBB_RX_DFE_RES_AGC_THRES        | R/W | 8        | 0x0            | Rescale AGC threshold                                                     |  |

| 0x24                                       | DBB_RX_DFE_RSSI_DIV             | R/W | 8        | 0x0            | Select averaging value for RSSI                                           |  |

| 0x25                                       | DBB_RX_DFE_RSSI_FRAME           | R/W | 8        | 0x0            | RSSI in the received frame                                                |  |

| 0x26                                       | DBB_RX_DFE_RSSI_VALUE           | R/W | 8        | 0x0            | Current RSSI                                                              |  |

| 0x30 to 0x3F: IEEE802.15.4 modem registers |                                 |     |          |                |                                                                           |  |

| 0x30                                       | DBB_RX_RX1_SFD_WORD             | R/W | 8        | 0xA7           | SFD Byte                                                                  |  |

| 0x31                                       | DBB_RX_RX1_SYNCH                | R/W | 8        | 0x5            | SYNC_TH synchronization detection threshold                               |  |

| 0x32                                       | DBB_RX_RX1_CPT_THRES            | R/W | 8        | 0x6            | -                                                                         |  |

|                                            | 1                               |     |          | Ī              |                                                                           |  |

| 0x33 | DBB_RX_RX1_GAIN_THRES | R/W | 8  | 0x8D | Gain for the RX demodulation algorithm |

|------|-----------------------|-----|----|------|----------------------------------------|

| 0x34 | DBB_RX_RX1_LQI_VALUE  | R   | 8  | 0x0  | Link quality indicator result          |

| 0x35 | DBB_RX_RX1_PHR_VALUE  | R   | 8  | 0x0  | PHR value                              |

| 0x36 | DBB_RX_RX1_CRC_VALUE  | R   | 16 | 0x0  | CRC value                              |

Table 1: D-BB Rx registers

To use the loopback functionality, a specific mode has to be selected. It is then possible, in simulation as with the actual SoC, to inject frames into the D-BB Rx and monitor the output to verify the correct processing in the D-FE as well as in the Modem.

# 2.2 D-BB RX test methodology and validation

The methodology for the validation of the full D-BB Rx is based on being able to stick the behaviour when simulating to the actual behaviour of the final SoC. To do so, the entry points and outcomes of the test process have been limited to the minimum. A test bench is set around the core D-BB Rx VHDL featuring a 2 entry points:

- ADC output / input of D-FE

- icyflex bus

which are fed by input files generated using Matlab, and 2 possible outputs:

- Data buffer: directly readable by the icyflex interface

- Spy block in the test bench: automatically generating files fed with the outputs of each D-BB Rx constituting block

This way, the D-BB Rx is not impacted by the requirements of the test hardware as it uses features already available for the SoC functioning.

From this methodology, several scenarii have been envisioned in simulation to validate the correctness of the whole D-BB Rx. They are all related to test modalities of interest to detect potential sources of non-functioning.

Figure 2-3: test bench interface with the D-BB Rx

The architecture of this test bench allows monitoring the signal on the complete D-BB Rx chain. The signals are stored into files which can be compared to expectation files devised thanks to Matlab.

At the end of the D-BB Rx chain, it is also possible to read the data buffer and get the received, which can then be compared with the original data bytes file used to generate the Matlab log file.

Given this methodology, various test can be carried out. Amongst them, some can be described as functional tests as they are carried out using ideal waveform processed under Matlab. The list below describes these functional tests:

| Name of the test                    | Description                                                                                                                                               |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx/F000_802_15_4_full_decodage      | This validates the whole IEEE802.15.4 modem, for 100 packets fo 20 bytes each at an expected received power of -85 dBm and a CFO of 20 ppm.               |

| rx/F001_dfe_802_15_4_adc_input      | This validates the D-FE only in the normal mode, with a pulse shaping filter set for IEEE802.15.4                                                         |

| rx/F002_dfe_802_15_4_adc_sat_input  | This validates the D-FE only in the normal mode with generated saturated data at the input from the ADC, with a pulse shaping filter set for IEEE802.15.4 |

| rx/F003_dfe_bluetooth_adc_input     | This validates the D-FE only in the normal mode with a pulse shaping filter set for BlueTooth LE 1Mbps                                                    |

| rx/F004_dfe_bluetooth_adc_sat_input | This validates the D-FE only in the normal mode with generated saturated data at the input, with a pulse                                                  |

|                                                   | shaping filter set for BlueTooth LE 1Mbps                                                   |

|---------------------------------------------------|---------------------------------------------------------------------------------------------|

| rx/F005_IRQ _end_frame                            | This validates the interrupt end_frame on IRQ0, IRQ1, IRQ2                                  |

| rx/F006_IRQ_fifo_rx_full                          | This validates the interrupt fifo_rx_full on IRQ0, IRQ1 and IRQ2                            |

| rx/F007_IRQ_fifo_rx_part                          | This validates the interrupt fifo_rx_part on IRQ0, IRQ1 and IRQ2, for DBB_RX_FIFO_THRES = 3 |

| rx/F008_IRQ_fifo_rx_empty                         | This validates the interrupt fifo_rx_empty on IRQ0 and IRQ1                                 |

| rx/F009_IRQ_fifo_rx_underflow                     | This validates in the loopback mode the interrupt fifo_rx_underflow on IRQ0 and IRQ1        |

| rx/F010_IRQ_fifo_rx_overflow                      | This validates the interrupt fifo_rx_overflow on IRQ0                                       |

| rx/F011_IRQ_fifo_adc_overflow                     | This validates in the loopback mode the interrupt fifo_adc_overflow on IRQ0.                |

| rx/F012_IRQ_end_frame_loopback_dfe_input          | This validates in the loopback mode the interrupt end_frame on IRQ0, IRQ1 and IRQ2          |

| rx/F013_IRQ_fifo_rx_full_loopback_ dfe_input      | This validates in the loopback mode the interrupt fifo_rx_full on IRQ0, IRQ1 and IRQ2       |

| rx/F014_IRQ_fifo_rx_part_loopback_ dfe_input      | This validates in the loopback mode the interrupt fifo_rx_part on IRQ0, IRQ1 and IRQ2       |

| rx/F015_IRQ_fifo_rx_empty_loopback_ dfe_input     | This validates in the loopback mode the interrupt fifo_rx_empty on IRQ0, IRQ1 and IRQ2      |

| rx/F016_IRQ_fifo_rx_underflow_loopback_ dfe_input | This validates in the loopback mode the interrupt fifo_rx_underflow on IRQ0 and IRQ1        |

| rx/F017_IRQ_fifo_rx_overflow_loopback_ dfe_input  | This validates in the loopback mode the interrupt fifo_rx_overflow on IRQ0                  |

| rx/F018_RSSI_AFE_AGC_16_RSSI_rescale_AGC_8        | This validates the RSSI value calculated for AFE_AGC at 16 and rescale_AGC at 8             |

| rx/F019_RSSI_AFE_AGC_32_RSSI_rescale_AGC_16       | This validates the RSSI value calculated for AFE_AGC at 32 and rescale_AGC at 16            |

| rx/F020_RSSI_AFE_AGC_64_RSSI_rescale_AGC_32       | This validates the RSSI value calculated for AFE_AGC at 64 and rescale_AGC at 32            |

| rx/F021_RSSI_AFE_AGC_128_RSSI_rescale_AGC_64      | This validates the RSSI value calculated for AFE_AGC at 128 and rescale_AGC at 64           |

| rx/F022_RSSI_AFE_AGC_256_RSSI_rescale_AGC_128     | This validates the RSSI value calculated for AFE_AGC at 256 and rescale_AGC at 128          |

| rx/F023_RSSI_AFE_AGC_512_RSSI_rescale_AGC_256     | This validates the RSSI value calculated for AFE_AGC at 512 and rescale_AGC at 256          |

| rx/F024_RSSI_AFE_AGC_1024_RSSI_rescale_AGC_512    | This validates the RSSI value calculated for AFE_AGC at 1024 and rescale_AGC at 512         |

| rx/F025_RSSI_AFE_AGC_2048_RSSI_rescale_AGC_1024 | This validates the RSSI value calculated for AFE_AGC at                                                         |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|                                                 | 2048 and rescale_AGC at 1024                                                                                    |

|                                                 |                                                                                                                 |

| rx/F026_rescale_AGC_auto_mode                   | This validates the behaviour of the automatic rescale                                                           |

|                                                 | driven by the AGC block                                                                                         |

| rx/F027_loopback_dfe_input                      | This validates the D-FE only in the loopback mode. The                                                          |

| 1/ FO27_IOOPDACK_UIE_IIIPUT                     | input data are coming at the input of the D-FE through                                                          |

|                                                 | the icyflex data bus.                                                                                           |

|                                                 | the reynex data bas.                                                                                            |

| rx/F028_loopback_modem_input                    | This validates the IEEE802.15.4 Modem only in the                                                               |

|                                                 | oopback mode. The input data are coming at the input                                                            |

|                                                 | of the Modem through the icyflex data bus. The                                                                  |

|                                                 | decoded bytes are buffered and read thanks to the                                                               |

|                                                 | fifo_rx_full IT.                                                                                                |

| ry/E029 dump add output                         | This monitors the data directly at the output of the ADC.                                                       |

| rx/F029_dump_adc_output                         | It will be useful to test and characterize the ADC.                                                             |

|                                                 | functioning on the actual SoC implementation                                                                    |

|                                                 | ranctioning on the actual see implementation                                                                    |

| rx/F030_dump_dfe_output                         | This monitors the data directly at the output of the DFE.                                                       |

|                                                 | It will be useful to test and characterize the DFE                                                              |

|                                                 | functioning on the actual SoC implementation                                                                    |

|                                                 |                                                                                                                 |

| rx/F031_loopback_dfe_input_dump_dfe_output      | This monitors the data directly at the output of the DFE                                                        |

|                                                 | while injecting the data stream at its imput. It will be useful to test and characterize the DFE functioning on |

|                                                 | the actual SoC implementation                                                                                   |

|                                                 | the detail 500 implementation                                                                                   |

| rx/F032_swap_cos_I_FI2BB_input                  | This tests the inversion of sign on cosine I path                                                               |

|                                                 |                                                                                                                 |

| rx/F033_swap_sin_I_FI2BB_input                  | This tests the inversion of sign on sine I path                                                                 |

| rx/F034_swap_cos_Q_FI2BB_input                  | This tests the inversion of sign on cosine Q path                                                               |

| ,                                               |                                                                                                                 |

| rx/F035_swap_sin_Q_FI2BB_input                  | This tests the inversion of sign on sine I path                                                                 |

| trace and                                       |                                                                                                                 |

| rx/F036_CRC_normal_mode                         | This validates the CRC functioning. The frame is                                                                |

|                                                 | removed if the CRC is wrong.                                                                                    |

| rx/F037_CRC_debug_mode                          | This validates the CRC functioning. The frame is kept                                                           |

|                                                 | even if the CRC is wrong.                                                                                       |

|                                                 |                                                                                                                 |

| rx/F038_IRQ_dfe_res_agc_sat                     | This valides in the norrmal mode the interrupt                                                                  |

|                                                 | dfe_res_agc_sat on IRQ0, IRQ1 and IRQ2                                                                          |

| /man in it                                      |                                                                                                                 |

| rx/F039_IRQ_dfe_res_agc_sat_loopback_dfe_input  | This valides in the loopback mode the interrupt                                                                 |

|                                                 | dfe_res_agc_sat on IRQ0, IRQ1 and IRQ2                                                                          |

| 1                                               |                                                                                                                 |

Table 2: Functional tests carried out on the D-BB Rx

The first ones are investigating the correctness of the D-FE for the 2 Pulse Matched filter configurations, corresponding to the IEEE802.15.4 and BT-LE versions of the filter.

When loopback is mentioned, the tests verify the correctness of the D-FE and the Modem by injecting the data through the icyflex bus: this verifies at the same time the validity of the bus interface and of the loopback mode.

When the ADC is mentioned, the values of interest are fed thanks to the loopback mode, and read through the icyflex bus. This eases the validation of the ADC, without passing the signal through the D-BB.

Indeed, the target for these tests is to match to output files with the files generated by the algorithms simulated with Matlab. Finally, all these tests described here have been passed successfully and no issue has been found. It also has to be mentioned that most of these tests monitor intermediate files in the chain. These intermediate files also exhibit correct result which validates the overall test bench methodology and secure the porting of the VHDL code to the SoC implementation.

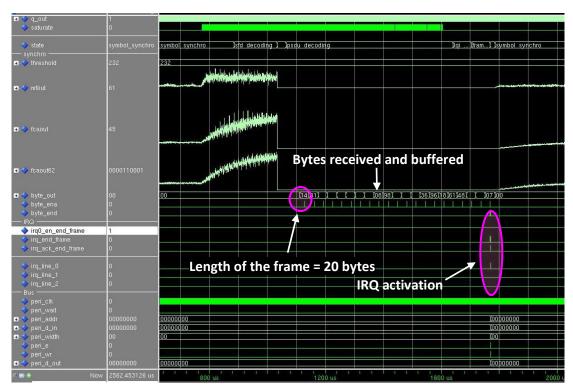

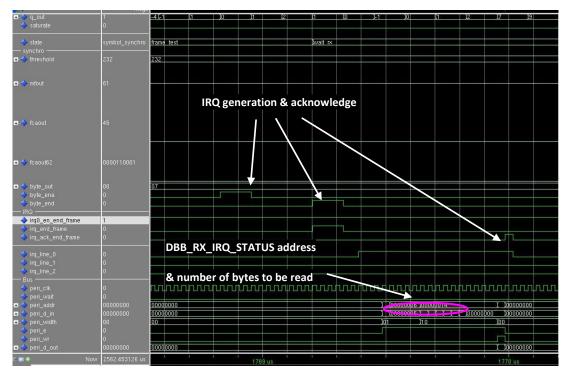

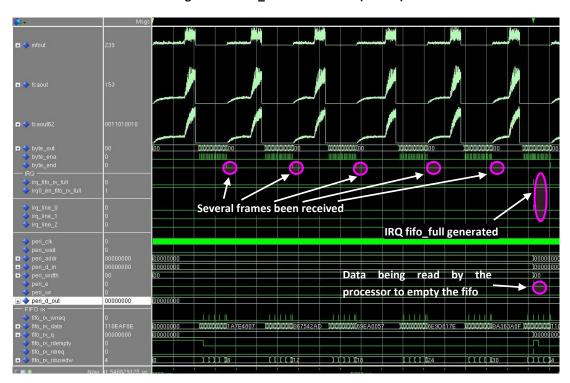

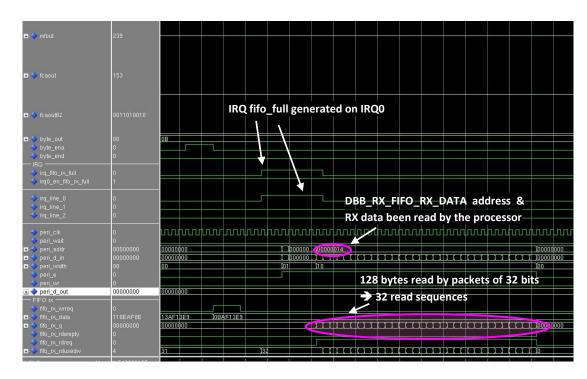

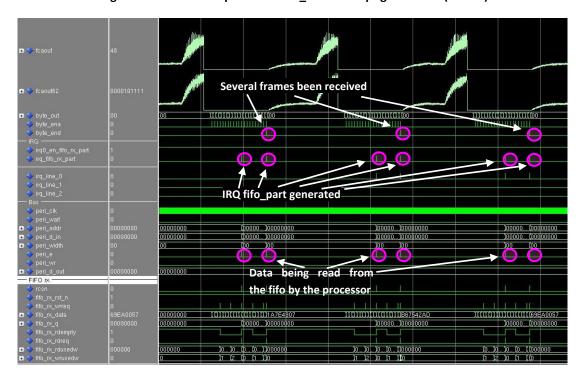

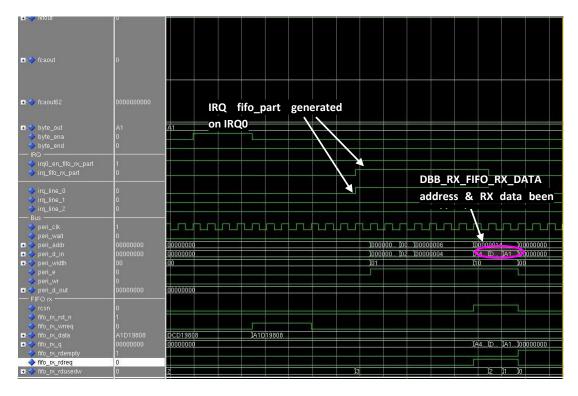

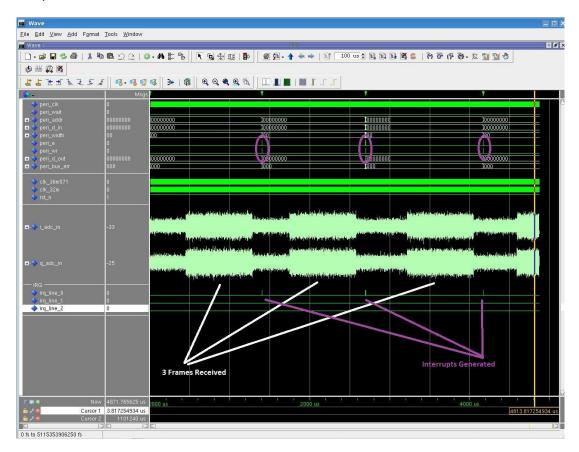

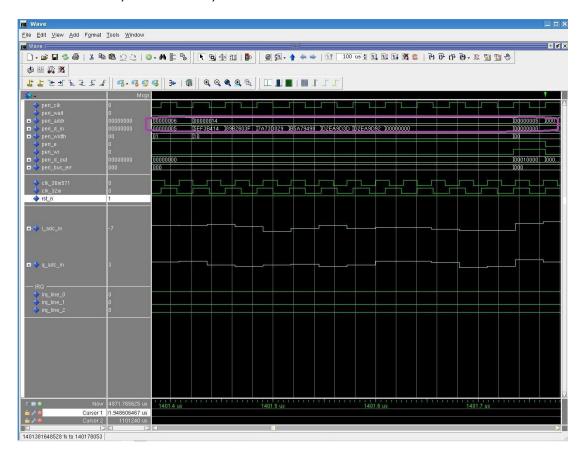

Another feature which is also tested carefully in the previous tests is the interrupt generation one. When generating and simulating the proposed scenario, the activation of interrupts of interest has also been activated. Some screen snapshots of the simulations are presented below to explain how and when the interrupts are generated.

Figure 2-4: frame reception and end\_frame IT generation

Figure 2-5: End\_frame activation ( zoom )

Figure 2-6: Multiple frames reception and generation of fifo\_full interrupt

Figure 2-7: Frame reception and fifo\_full interrupt generation ( zoom )

Figure 2-8: Frame reception and generation of a FIFO partial filling interrupt

Figure 2-9: Frame reception and generation of the fifo\_part IT ( zoom )

These display the correctness of the IT generation process. As explained, all the IT developed with the overall D-BB have been tested and validated when simulating the reception of the frames.

Some performance tests have also been carried out to validate that in real conditions, the frame would be received in a correct manner. As a first step, the robustness to frequency drift has been considered. Due to the long possible received frame, it is mandatory to confirm that the frequency difference between the receiver module and the transmitter will not create an error in the demodulation.

| Name of the test                         | Description                                                                                                                                                                                                            |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx/P000_FRAME80_PHR12780to80ppm_85dbm    | This validates the Compensation of Frequency Offset for IEEE802.15.4, with 80 packets of 127 bytes payload at a received power of -85 dBm, considering 2 ppm steps between 2 packets to finally civer +/-80 ppm drift. |

| rx/P001_FRAME123_PHR5to127_20ppm_85dbm   | This validates the Compensation of Frequency Offset for IEEE802.15.4, for packets of PHR between 5 and 127 bytes, at a received power of -85 dBm, considering 20 ppm drifts.                                           |

| rx/P002_FRAME31_PHR20_80ppm_95dbm        | This validates the correct reception of 31 frames of 20 bytes at an equivalent level of -95 dBm signal with a CFO of 80 ppm for IEEE802.15.4.                                                                          |

| rx/P003_FRAME2_PHR_with_zero_80ppm_85dbm | This validates the correct reception of 2 frames of 0 bytes at an equivalent level of -85 dBm signal with a CFO of 80 ppm for IEEE802.15.4. The purpose is to make sure that no weird                                  |

|                                                  | behaviour happens when sequences of zero is    |

|--------------------------------------------------|------------------------------------------------|

|                                                  | received.                                      |

| rx/P004_RX1_FRAME40_random_PHR_CFO_Prx_test0     | This validates the correct reception of frames |

|                                                  | with random PHR, recoeved signal level, and    |

|                                                  | CFO. 40 packets with a payload between 5 and   |

|                                                  | 127, a power level between -20 and -95 dBm,    |

|                                                  | and a drift between -80 and +80 ppm.           |

| rx/P005_RX1_FRAME40_random_PHR_CFO_Prx_test1     | This validates the correct reception of frames |

|                                                  | with random PHR, recoeved signal level, and    |

|                                                  | CFO. 40 packets with a payload between 5 and   |

|                                                  | 127, a power level between -20 and -95 dBm,    |

|                                                  | and a drift between -80 and +80 ppm.           |

| rx/P006_RX1_FRAME40_random_PHR_CFO_Prx_test2     | This validates the correct reception of frames |

|                                                  | with random PHR, recoeved signal level, and    |

|                                                  | CFO. 40 packets with a payload between 5 and   |

|                                                  | 127, a power level between -20 and -95 dBm,    |

|                                                  | and a drift between -80 and +80 ppm.           |

| rx/P007_RX1_FRAME40_random_PHR_CFO_Prx_test3     | This validates the correct reception of frames |

|                                                  | with random PHR, recoeved signal level, and    |

|                                                  | CFO. 40 packets with a payload between 5 and   |

|                                                  | 127, a power level between -20 and -95 dBm,    |

|                                                  | and a drift between -80 and +80 ppm.           |

| rx/P008_RX1_FRAME50_PHR20_20ppm_variable_spacing | This validates the correct reception of frames |

|                                                  | with random spacing between them. The PHR is   |

|                                                  | 20 bytes and the power level -95 dBm. 50       |

|                                                  | packets are simulated.                         |

Table 3: Performance tests carried out on the D-BB Rx

A Compensation of Frequency Offset has been implemented, and the validation tests have demonstrated that it was not robust enough to support 80 ppm drift. Thereby, the VHDL code has been modified in order to improve this and it can now support more than 80 ppm (or +/- 40 ppm on each side of the RF link). Finally, the test bench has demonstrated that a full 127-byte frame was received correctly even in the case of +/- 80 ppm drifts. It has also been tested in the case of various frame lengths, at the minimum expected power level, with successful results.

The validation of DFE, for all targeted modulations, and demodulation of 802.15.4 as well as interface with the icyflex bus has been performed by simulation. Because the associated digital functionality will be integrated in silicon in MPW2, those validations will be reinforced by measurement before final integration. The validation of remaining demodulations will be performed following the same flow with the addition of a validation by measurement before final integration using the FPGA platform described in chapter 4.

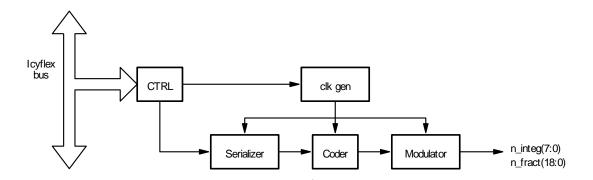

## 2.3 D-BB implementation for the transmitter

The modulation is realized by direct dynamic digital programming of the Tx VCO, running at the output frequency. Basically, the sample rate at the output of the modulator is x8 times the symbol rate, the closed-loop transfer function realizing the interpolation filter. This is enough in practice to get alias below the phase noise of the VCO. An interpolator can be used to increase the alias filtering for low symbol rates.

The D-BB Tx is digital peripheral of the icyflex with associated configuration registers and interface for the data handling via interrupt mechanism.

- FSK modulation,

- Fully programmable data rate by integer sub-multiple of 4Mbit/s,

- Fully programmable modulation index,

- Fully programmable pulse shape (e.g. Gaussian pulse for BT-LE),

- IEEE 802.15.4 bit to chip encoding (possibly disabled),

- Data whitening (PN9 or BT-LE),

- Programmable packet length,

- Programmable CRC (1 to 32 bits) and automatic insertion,

- Automatic preamble and sync word insertion.

Figure 2-10: D-BB Tx block diagram

Note that test functionality has been added from MPW1 to MPW2 to allow a reading by the icyflex of the modulator output sample by sample:

- This will allow the verification of the hardware implementation, by comparison with simulation.

- This also allows the implementation by software of a digital loopback between D-BB Tx and D-BB Rx.

All the D-BB Tx registers are listed below:

| # bit | Name          | Function                                                                                             | Access | Reset |

|-------|---------------|------------------------------------------------------------------------------------------------------|--------|-------|

| 15:14 | Mode          | Select the baseband_tx mode:  00 → Off (also the baseband_tx clk)  01 → Reset  10 → Freeze  11 → Run | R/W    | 0     |

| 13    | en_serializer | if set to 1 enables the serializer                                                                   | R/W    | 0     |

| 12    | last_data     | when the packet handling is not used, this field is used to notify the last data to send.            | R/W    | 0     |

| 11    | en_interp     | if set to 1 enables the interpolator at the                                                          | R/W    | 0     |

|      |             | output                                                                                                                        |     |   |

|------|-------------|-------------------------------------------------------------------------------------------------------------------------------|-----|---|

| 10:9 | word_len    | indicates the word length that is used on the BASEBAND_TX_DATA register:  00 → 8bit  01 → 16 bit  10 → 32 bits  11 → not used | R/W | 0 |

| 7:0  | integer_div | Division factor that fixes the oversampling frequency and hence the data-rate. In practice:  DR=32MHz/(8.(integer_div+1))     | R/W | 0 |

Table 4: BASEBAND\_CONF register

| # bit | Name          | Function                                                                   | Access | Reset |

|-------|---------------|----------------------------------------------------------------------------|--------|-------|

| 15:8  | interp div    | Dvision factor that fixes the interpolator frequency. The frequency can be | R/W    | 0     |

| 15.6  | interp_uiv    | calculated as for the integer_div.                                         | IV, VV | U     |

| 7:4   | mult_mantissa | mantissa of the multiplier in the modulator                                | R/W    | 0     |

| 3:0   | mult_exp      | exponent of the multiplier in the modulator                                | R/W    | 0     |

Table 5: BASEBAND\_TX\_MOD register

| # bit | Name          | Function                                                                                                                                                    | Access | Reset |

|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| 19    | pulse_nsym    | If set to 1, the pulse shape is an odd function.                                                                                                            | R/W    | 0     |

| 18    | symbol_2bit   | if set to 1, a symbol is composed of two bits intead of one.                                                                                                | R/W    | 0     |

| 17    | reserved      | this bit is reserved                                                                                                                                        | R/W    | 0     |

| 16    | reserved      | this bit is reserved                                                                                                                                        | R/W    | 0     |

| 15    | en_dw_btle    | if set to 1, the data whitening specified in the BT-LE standard is used instead of the PN9. Note that the field <i>en_datawhite</i> has also to be set to 1 | R/W    | 0     |

| 14:8  | dw_btle_rst   | this field contains the value that has to be specified in the shift register for the BlueTooth data whitening                                               | R/W    | 0     |

| 7     | en_datawhite  | If set to 1 enables the data whitening                                                                                                                      | R/W    | 0     |

| 6     | diff_coding   | If set to 1 enables the differential encoding                                                                                                               | R/W    | 0     |

| 5     | bit_invert    | If set to 1 enables the bit inversion (1 $\Leftrightarrow$ 0)                                                                                               | R/W    | 0     |

| 4     | reserved      | this bit is reserved                                                                                                                                        | R/W    | 0     |

| 3     | en_802154_l2f | If set to 1 enables the conversion linear => frequency that is needed in order to send an O-QPSK data stream through a direct modulation                    | R/W    | 0     |

| 2     | en_802154_b2c | If set to 1 enables the IEEE 802.15.4 bit to chip conversion                                                                                                | R/W    | 0     |

| 1     | en_manchester | If set to 1 enables the Manchester encoding                                                                                                                 | R/W    | 0     |

| 0     | lsb_first     | If set to 1, the LSB is the first sent bit, the MSB otherwise.                                                                                              | R/W    | 0     |

#### Table 6: BASEBAND\_CODING register

| # bit | Name              | Function                                                                                                      | Access | Reset |

|-------|-------------------|---------------------------------------------------------------------------------------------------------------|--------|-------|

| 7     | en_crc            | If set to 1 enables the CRC calculation and automatic insertion                                               | R/W    | 0     |

| 6:5   | pattern_word_len  | Set the pattern word length.  00 → 8bit  01 → 16 bit  10 → 32 bits  11 → not used                             | R/W    | 0     |

| 4     | en_multiframe     | If set to 1 enables the multi-frame mode (experimental)                                                       | R/W    | 0     |

| 3     | en_address        | If set to 1 enables the automatic address insertion                                                           | R/W    | 0     |

| 2     | en_preamble       | If set to 1 enables the automatic preamble insertion                                                          | R/W    | 0     |

| 1     | en_packet_len_fix | If set to 1, the packet will have a fixed length. The length can be written in the BASEBAND_PKT_LEN register. | R/W    | 0     |

| 0     | en_packet         | If set to 1, enables the packet handler                                                                       | R/W    | 0     |

#### Table 7: BASEBAND\_PKT\_HDL register

| # bit | Name       | Function                                                                                        | Access | Reset |

|-------|------------|-------------------------------------------------------------------------------------------------|--------|-------|

| 13:10 | correction | Signed value that specifies the correction to be added to the packet length                     | R/W    | 0     |

| 9:8   | position   | unsigned value that specifies the position of the packet length inside the payload.             | R/W    | 0     |

| 7:0   | length     | Unsigned value that specifies the length of the packet in case of a fix packet length protocol. | R/W    | 0     |

#### Table 8: BASEBAND\_PKT\_LEN register

| # bit | Name    | Function                       | Access | Reset |

|-------|---------|--------------------------------|--------|-------|

| 31:0  | pattern | Pattern to be send (sync word) | R/W    | 0     |

#### Table 9: BASEBAND\_PATTERN register

| # bit | Name           | Function                                                                                                                                                  | Access | Reset |

|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| 31:0  | crc_polynomial | CRC polynomial. It is coded using the Koopman notation, i.e. the nth bit codes the (n+1) coefficient. Example: $x^{16}+x^{12}+x^5+1 \rightarrow 0x8810$ . | R/W    | 0     |

#### Table 10: BASEBAND\_CRC\_POLY register

| # bit | Name    | Function               | Access | Reset |

|-------|---------|------------------------|--------|-------|

| 31:0  | crc_rst | Reset value of the CRC | R/W    | 0     |

#### Table 11: BASEBAND\_CRC\_RST register

| # bit | Name      | Function           | Access | Reset |

|-------|-----------|--------------------|--------|-------|

| 26:0  | mod_cfreq | Central frequency. | R/W    | 0     |

Table 12: BASEBAND\_MOD\_CFREQ register

| # bit | Name    | Function                                                             | Access | Reset |

|-------|---------|----------------------------------------------------------------------|--------|-------|

| 31:24 | coef_15 | signed value of the 15 <sup>th</sup> coefficient of the pulse shape. | R/W    | 0     |

| 23:16 | coef_14 | signed value of the 14 <sup>th</sup> coefficient of the pulse shape. | R/W    | 0     |

| 15:8  | coef_13 | signed value of the 13 <sup>th</sup> coefficient of the pulse shape. | R/W    | 0     |

| 7:0   | coef_12 | signed value of the 12 <sup>th</sup> coefficient of the pulse shape. | R/W    | 0     |

Table 13: BASEBAND\_PULSE\_SHAPE\_4

| # bit | Name    | Function                                                             | Access | Reset |

|-------|---------|----------------------------------------------------------------------|--------|-------|

| 31:24 | coef_11 | signed value of the 11 <sup>th</sup> coefficient of the pulse shape. | R/W    | 0     |

| 23:16 | coef_10 | signed value of the 10 <sup>th</sup> coefficient of the pulse shape. | R/W    | 0     |

| 15:8  | coef_9  | signed value of the 9 <sup>th</sup> coefficient of the pulse shape.  | R/W    | 0     |

| 7:0   | coef_8  | signed value of the 8 <sup>th</sup> coefficient of the pulse shape.  | R/W    | 0     |

#### Table 14: BASEBAND\_PULSE\_SHAPE\_3

| # bit | Name                                                                       | Function                                                            | Access | Reset |

|-------|----------------------------------------------------------------------------|---------------------------------------------------------------------|--------|-------|

| 31:24 | signed value of the 7 <sup>th</sup> coefficient of the pulse shape.        |                                                                     | R/W    | 0     |

| 23:16 | coef_6                                                                     | signed value of the 6 <sup>th</sup> coefficient of the pulse shape. | R/W    | 0     |

| 15:8  | coef_5                                                                     | signed value of the 5 <sup>th</sup> coefficient of the pulse shape. |        | 0     |

| 7:0   | coef_4 signed value of the 4 <sup>th</sup> coefficient of the pulse shape. |                                                                     | R/W    | 0     |

# Table 15: BASEBAND\_PULSE\_SHAPE\_2

| # bit | Name   | Function                                                            | Access | Reset |  |

|-------|--------|---------------------------------------------------------------------|--------|-------|--|

| 31:24 | coef_3 | Signed value of the 3 <sup>rd</sup> coefficient of the pulse shape. |        |       |  |

| 23:16 | coef_2 | signed value of the 2 <sup>nd</sup> coefficient of the pulse shape. | R/W    | 0     |  |

| 15:8  | coef_1 | signed value of the 1 <sup>st</sup> coefficient of the pulse shape. |        | 0     |  |

| 7:0   |        | signed value of the O <sup>th</sup> coefficient of the              |        |       |  |

#### Table 16: BASEBAND\_PULSE\_SHAPE\_1

| # bit | Name    | Name Function              |     |   |

|-------|---------|----------------------------|-----|---|

| 31:0  | tx_data | Data to be processed by Tx | R/W | 0 |

#### Table 17: BASEBAND\_TX\_DATA register

| # bit | bit Name Function |                                      | Access | Reset |

|-------|-------------------|--------------------------------------|--------|-------|

| 7:0   | address           | Address to be inserted automatically | R/W    | 0     |

Table 18: BASEBAND\_ADDRESS register

| # bit | Name     | Function                              | Access | Reset |

|-------|----------|---------------------------------------|--------|-------|

| 7:0   | preamble | Preamble to be inserted automatically | R/W    | 0     |

Table 19: BASEBAND\_PREAMBLE register

| # bit Name |              | Function                   | Access | Reset |

|------------|--------------|----------------------------|--------|-------|

| 7:0        | preamble_len | Length of the preamble -1. | R/W    | 0     |

Table 20: BASEBAND\_PREAMBLE\_LEN register

## 2.4 D-BB TX test methodology and validation

The D-BB Tx has been benched by digital simulation, with the targeted modulations, with a corresponding D-BB Rx different from the one described in the preceding Section 2.1 and 2.2.

This D-BB Tx has been integrated into the MPW1 SoC. The more interesting validation is then realized by measurement of the modulated output of the SoC, at RF level, for the different targeted modulations.

In addition to the below measurements of continuous transmissions, it would have been also interesting to validate the different frame formats at RF level. This can only be performed by the use of corresponding demodulator with RF input, the more interesting configuration being the use of the Rx analogue chain and demodulator that will be integrated in the SoC.

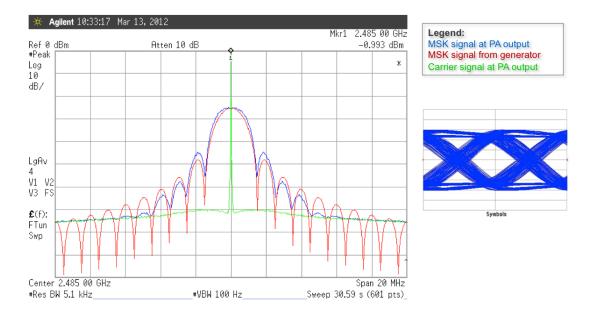

If we consider that the proprietary modulation is equivalent to IEEE802.15.4-2006 modulation without the spreading, both modulation spectrums and eyes correspond to a 2Mbit/s MSK. The below Figure 2-11 displays the output spectrum and eye diagram for continuous 2Mbit/s MSK modulation that corresponds to the BT-LE modulation: the output spectrum is very close to the output spectrum of a generator configured for the same modulation and the eye is widely opened. The close spectrum as well as parasitic spurs are well below the IEEE802.15.4-2006 standard mask.

Figure 2-11: Output spectrum for MSK 2Mbit/s and associated eye diagram (802.15.4)

The below Figure 2-12 displays the output spectrum and eye diagram for continuous 1Mbit/s GMSK modulation that corresponds to the BT-LE modulation: the output spectrum is quite close to the output spectrum of a generator configured for the same modulation and the eye is widely opened. The close spectrum as well as parasitic spurs are well below the BT-LE standard mask.

Figure 2-12: Output spectrum for GMSK 1Mbit/s and associated eye diagram (BT-LE)

The validation of the TD-BB Tx at RF level has then been performed but the addition of a complete loopback with a corresponding receiver would have been desired to validate also the frame formats at RF level in addition to the digital bench: this need to be performed before final integration.

#### 3 Processor unit validation

## 3.1 Pre-integration validation

CSEM has been developing SoCs based on the icyflex processor family since several years already. Those SoCs have been used for the development of numerous applications and demonstrators. The more important validation is then the verification that the integration of the icyflex processor and its peripherals in the WiserBAN SoC has been realized properly. This is performed by running numerous simulations to verify the processor itself and its digital peripherals. These simulations are implemented with software which is executed by the processor at the top level of the digital system. As an example, the boot loader software implanted in the boot ROM has been executed with the top level of the digital system including the RAM, ROM, digital pads, etc. and even behavioral model of external EEPROM (provided by EEPROM manufacturer). So the functionality has been verified with good confidence.

For the implementation into silicon, we verify the results of the synthesis and place & route tools by running additional verifications prior to the implementation into silicon. These verifications include back-annotated simulations and use of formal equivalence checking tools. This gives us a very good level of confidence in the design and has been proven to be sufficient in practice for numerous circuits in the past.

In order to reduce the effort of the developers in individual projects, CSEM provides low-level library and program examples. Some of these programs are used for the pre-integration and post-integration validation of the digital system. They are described in the following section 3.2.

# 3.2 Post-integration validation of the functionality

The organization of the software architecture is divided in several layers. A Hardware Abstraction Layer (HAL) developed by the CEA-Léti hides the detailed control of digital system, using low-level library and features from the CSEM, and provides to the upper layer programmer with a simplified hardware-independent interface. This HAL implements functionality associated to the management of general resources like power consumption, clock tree, miscellaneous parts used by the peripherals listed in the tables below:

| file/folder   | Comment                                               |  |  |  |  |

|---------------|-------------------------------------------------------|--|--|--|--|

| Clock         | Initialization run at startup                         |  |  |  |  |

| DMA           | Misc. library used to initialize a transfer           |  |  |  |  |

| Interrupt     | Used to set the request controller                    |  |  |  |  |

| Mode          | Layer which helps user to change the system frequency |  |  |  |  |

| regops.h      | Misc. Macro definitions                               |  |  |  |  |

| Runtime       | low level definitions                                 |  |  |  |  |

| sys_timer     | common timer used by peripherals                      |  |  |  |  |

| wiserbanv1a.h | WiserBAN register definitions                         |  |  |  |  |

Table 21: Digital peripherals HAL functionality

| Peripheral | Short description                                             |  |  |  |

|------------|---------------------------------------------------------------|--|--|--|

| gpio0      | To configure a GPIO as an input or output or to control/read  |  |  |  |

| Phico      | GPIO pins, user can set any GPIO as interrupt                 |  |  |  |

| i2s0       | half or full duplex transfer protocol                         |  |  |  |

| rtc0       | Timers and interruptible calendar based on the low            |  |  |  |

| rteo       | frequency oscillator. Useful for real time operation          |  |  |  |

| spi0       | Serial interface, most used on wiserbanv1a PCB, to            |  |  |  |

| Spio       | communicate with the FLASH                                    |  |  |  |

| spi0 dma   | Half duplex version of SPI interface, developed to output the |  |  |  |

| spio_uiiia | clock system divided by 2                                     |  |  |  |

| Timer      | Interruptible timer based on the system clock                 |  |  |  |

| timer0     | Interruptible timer based on the system clock                 |  |  |  |

| timer1     | Interruptible timer based on the system clock                 |  |  |  |

| timer2     | Interruptible timer based on the system clock                 |  |  |  |

| timer3     | Interruptible timer based on the system clock                 |  |  |  |

| uart0      | Serial interface, used principally as PC gateway              |  |  |  |

**Table 22: Digital peripherals HAL functionality**

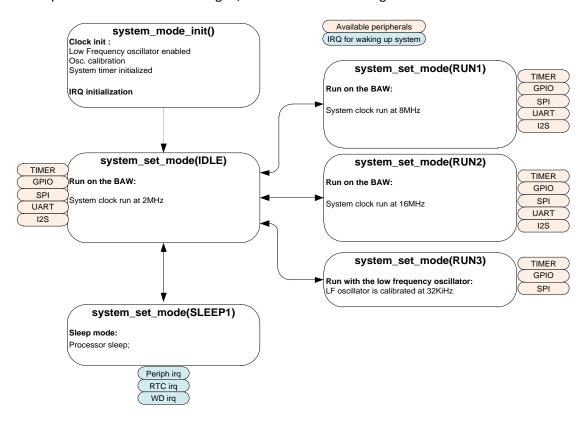

Five operational modes are managed, and described in the Figure 3-1 below:

Figure 3-1: modes of operation

Specific functionalities like interrupts, clock source selection and test modes that are listed in the table below have been validated by software:

| Туре              | Name         | Software name | Status                                      |

|-------------------|--------------|---------------|---------------------------------------------|

| IRQ_LINE          | RQ_DMA       | boot ROM      | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_UART1_0   | test_wiserban | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_UART1_1   | test_wiserban | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_TIMER_0   | test_wiserban | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_TIMER_1   | -             | -                                           |

| IRQ_LINE          | RQ_TIMER_2   | -             | -                                           |

| IRQ_LINE          | RQ_TIMER_3   | -             | -                                           |

| IRQ_LINE          | RQ_GPIO1_0   | -             | -                                           |

| IRQ_LINE          | RQ_GPIO1_1   | -             | -                                           |

| IRQ_LINE          | RQ_GPIO1_2   | -             | -                                           |

| IRQ_LINE          | RQ_GPIO1_3   | test_wiserban | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_RTC_0     | rtc_timer     | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_RTC_1     | rtc_timer     | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_RTC_2     | rtc_timer     | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_RTC_3     | rtc_timer     | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_SPI1_0    | test_wiserban | Signal is correctly mapped                  |

| IRQ_LINE          | RQ_SPI1_1    | -             | -                                           |

| IRQ_LINE          | RQ_I2S1_0    | -             | -                                           |

| IRQ_LINE          | RQ_I2S1_1    | -             | -                                           |

| IRQ_LINE          | RQ_WDTIMER   | -             | -                                           |

| IRQ_LINE          | RQ_BB_0      | -             | -                                           |

| IRQ_LINE          | RQ_BB_1      | -             | -                                           |

| IRQ_LINE          | RQ_ANACTRL_0 | -             | -                                           |

| IRQ_LINE          | RQ_ANACTRL_1 | -             | -                                           |

| IRQ_LINE          | RQ_ANACTRL_3 | -             | -                                           |

| IRQ_LINE          | RQ_ANACTRL_4 | -             | -                                           |

| IRQ_LINE          | RQ_ANACTRL_5 | -             | -                                           |

| IRQ_LINE          | RQ_ANACTRL_6 | -             | -                                           |

| IRQ_LINE          | RQ_ANACTRL_7 | -             | -                                           |

|                   |              |               | Clock is correctly redirected to            |

| MUXINTELLIGENTE   | BAW_OSC      | test_wiserban | the system                                  |

|                   | 2001         |               | Clock is correctly redirected to            |

| MUXINTELLIGENTE   | BAW_OSC/16   | test_wiserban | the system                                  |

| MUXINTELLIGENTE   | CIDEC        | test wiserban | Clock is correctly redirected to the system |

| IVIOAINTELLIGENTE | SILLES       | rest_wisernan | Clock is correctly redirected to            |

| RTC               | SIRES        | rtc_timer     | the rtc                                     |

|                   |              |               | Boot software is launched                   |

| SIGNAL            | NRESET       | -             | correctly after reset                       |

|                   |              |               |                                             |

Table 23: validated specific functionalities

Different program examples, listed in the table below, have also been executed for validation:

| Software | Description |

|----------|-------------|

| Example           | Software provided as model to implement your own application                                      |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| example2          | 2 <sup>nd</sup> software provided as model                                                        |  |  |  |

| prog_flash_dmades | Used to program the flash memory which is loaded at start-<br>up                                  |  |  |  |

| rtc_timer         | An example create to validate the RTC                                                             |  |  |  |

| temp_measure      | Characterization software                                                                         |  |  |  |

| test_wiserban     | used to validate GPIO, TIMER, SPI, IRQ, UART and components present on the characterisation board |  |  |  |

| uart0_com         | used to validate the UART separately                                                              |  |  |  |

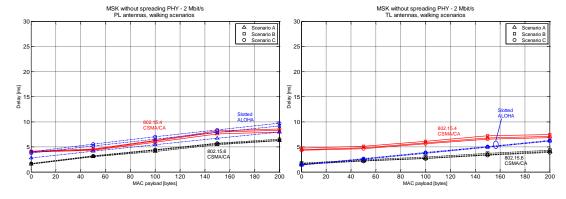

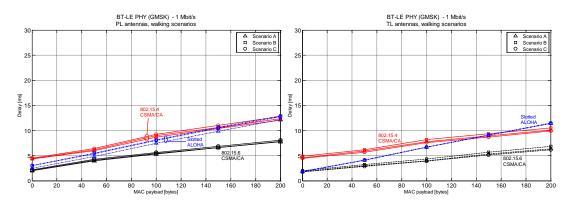

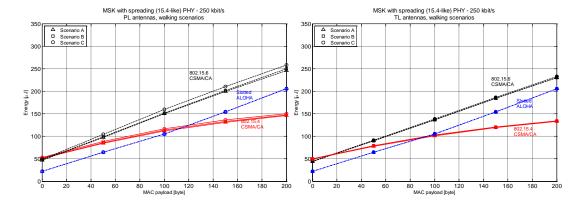

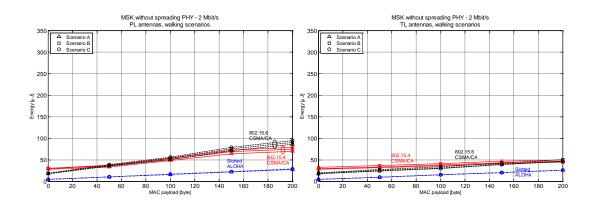

**Table 24: validation programs**

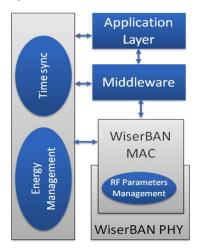

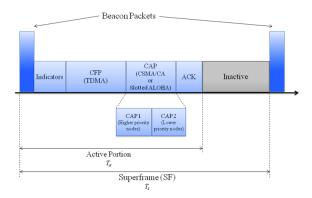

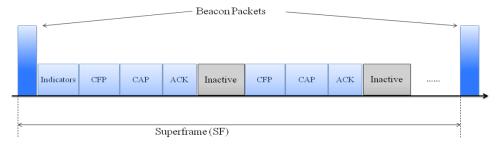

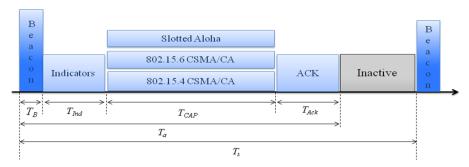

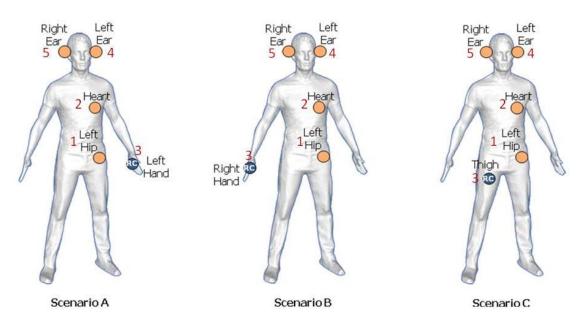

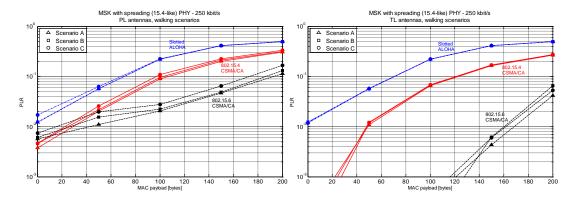

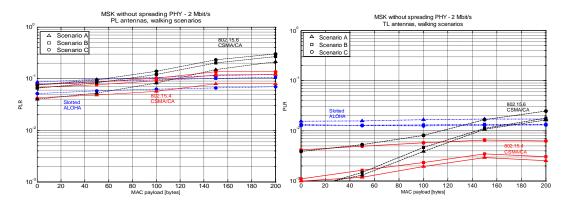

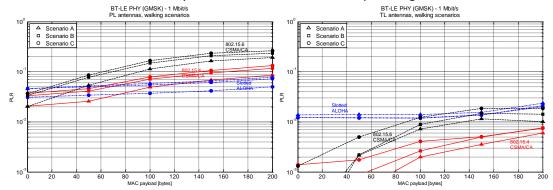

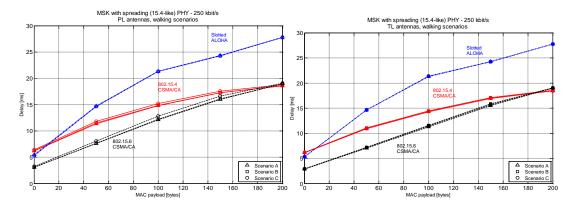

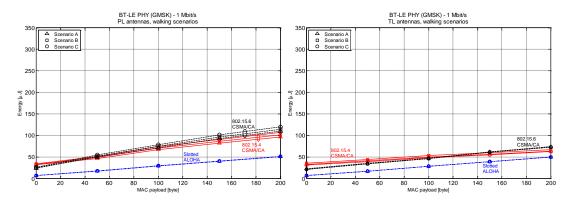

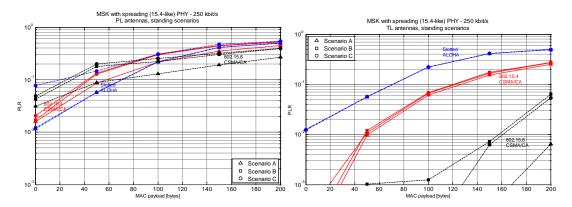

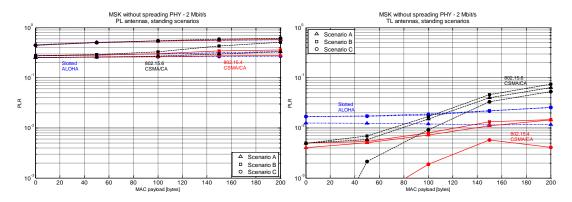

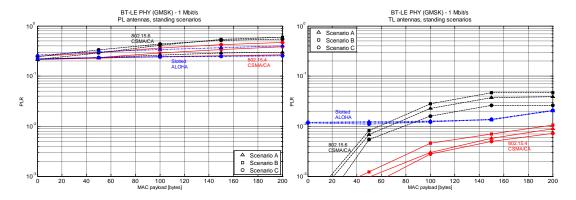

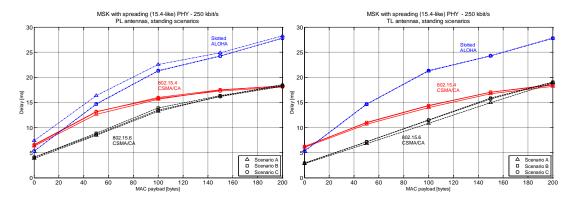

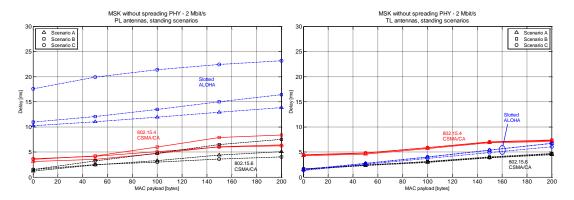

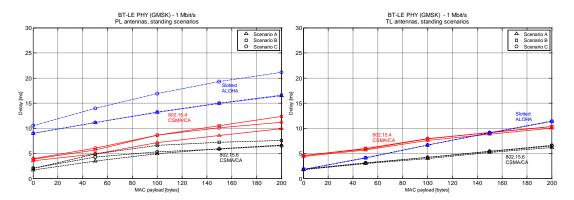

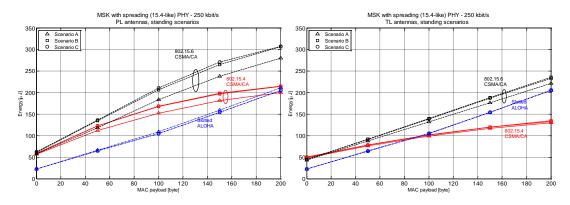

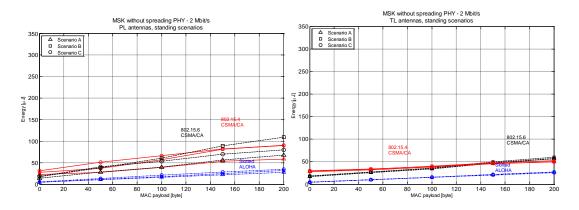

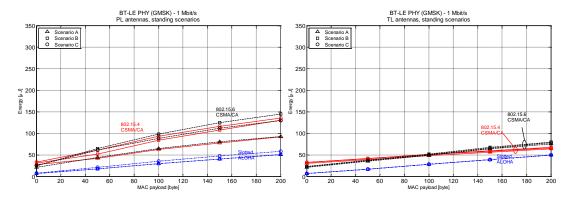

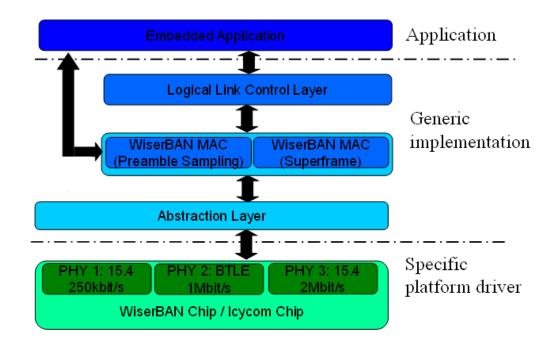

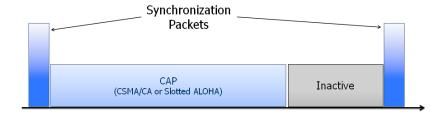

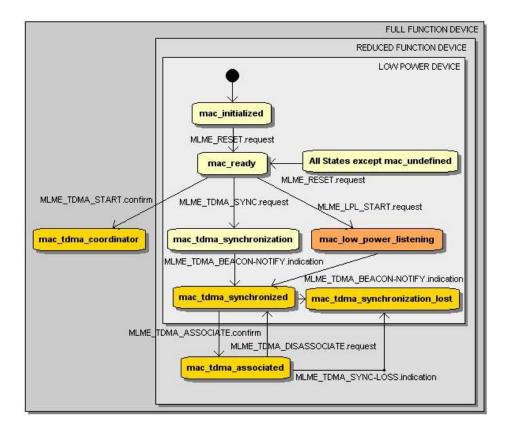

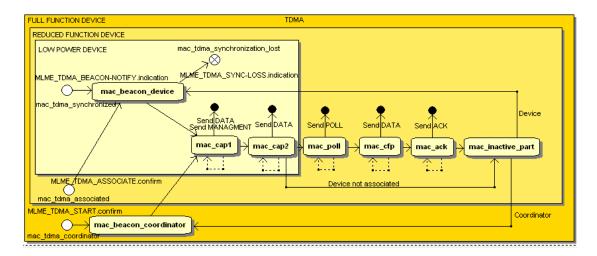

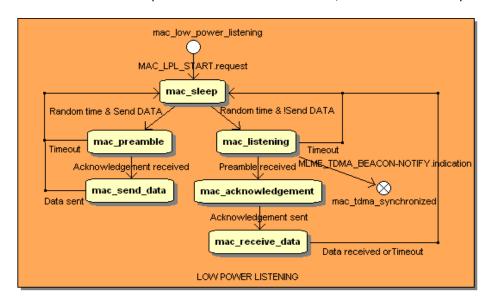

In addition to the functional validation described above, some pass/fail checks have been performed for different clock frequencies and voltage levels to provide with an indication on the safety margin associated to the digital integrated in MPW1 run. The pass/fail checks correspond to the correct execution of the boot loader in ROM that uploads a program in RAM from the external EEPROM and executes this program that writes a 1kW of data with a PN16 and reads it back for verification. The results are summarized in the Figure 3-2 below: