# D3.8 Final report on probabilistic analysis for mixed criticality on multicore Version 1.0

## **Document Information**

| Contract Number      | 611085                                                |  |  |  |  |  |

|----------------------|-------------------------------------------------------|--|--|--|--|--|

| Project Website      | www.proxima-project.eu                                |  |  |  |  |  |

| Contractual Deadline | m36, 30-September-2016                                |  |  |  |  |  |

| Dissemination Level  | PU                                                    |  |  |  |  |  |

| Nature               | R                                                     |  |  |  |  |  |

| Authors              | Liliana Cucu (leading author), Adriana Gogonel, Cris- |  |  |  |  |  |

|                      | tian Maxim, Iain Bate, Benjamin Lesage, David Grif-   |  |  |  |  |  |

|                      | fin, Tullio Vardanega, Enrico Mezzetti, Jaume Abella, |  |  |  |  |  |

|                      | Francisco Cazorla                                     |  |  |  |  |  |

| Contributors         | All partners                                          |  |  |  |  |  |

| Reviewer             | BSC                                                   |  |  |  |  |  |

| Keywords             | Measurement-Based, Probabilistic Timing Analysis,     |  |  |  |  |  |

|                      | Multicore                                             |  |  |  |  |  |

**Notices:** The research leading to these results has received funding from the European Community's Seventh Framework Programme [FP7/2007-2013] under grant agreement no 611085.

© 2015 PROXIMA Consortium Partners. All rights reserved.

## **Change Log**

| Version | Description of change                       |

|---------|---------------------------------------------|

| v1.0    | Initial version released for project review |

|         |                                             |

|         |                                             |

|         |                                             |

|         |                                             |

$D3.8\ Final\ report\ on\ probabilistic\ analysis\ for\ mixed\ criticality\ on\ multicore\ Version\ 1.0$

## **Executive Summary**

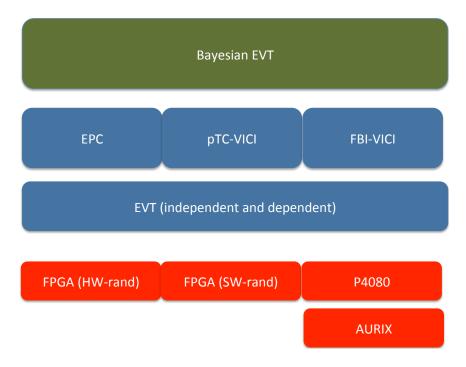

This deliverable presents the final versions of the PROXIMA timing analyses. These timing analyses have been evolving since the beginning of the project up to advanced versions, all integrated today within Rapita tool RVS. The PROXIMA timing analyses are the following:

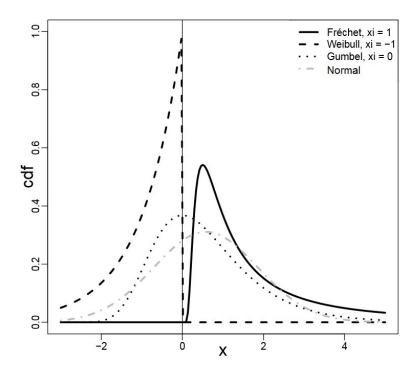

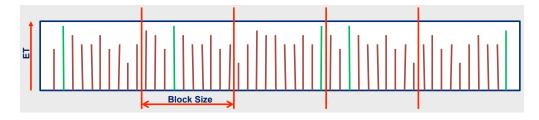

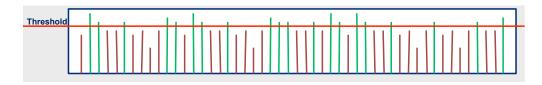

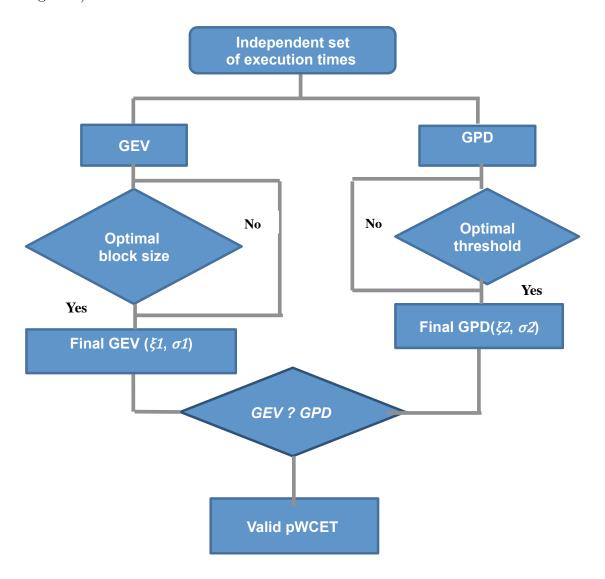

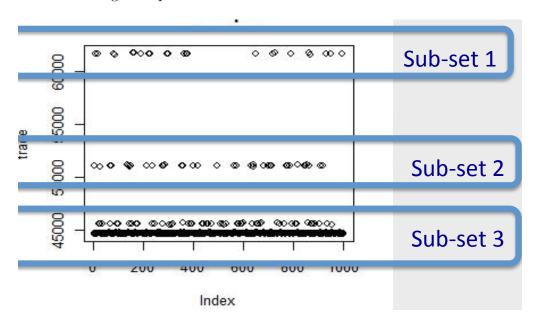

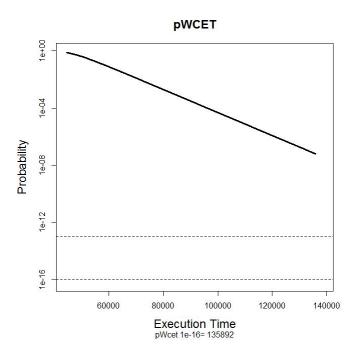

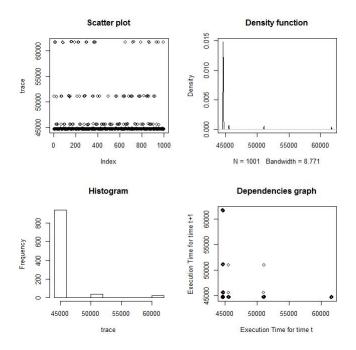

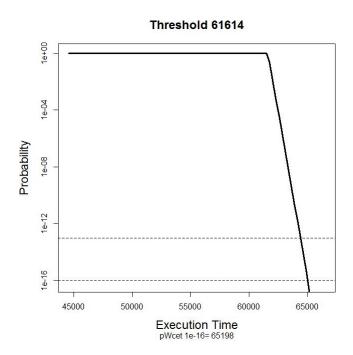

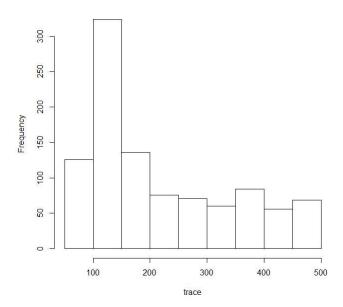

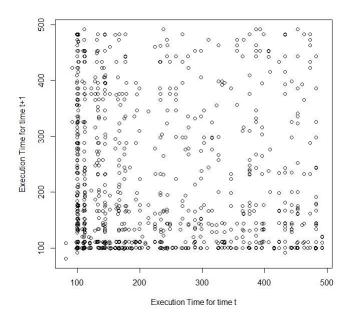

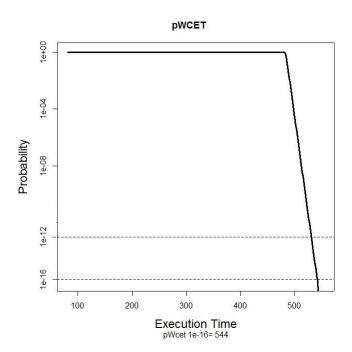

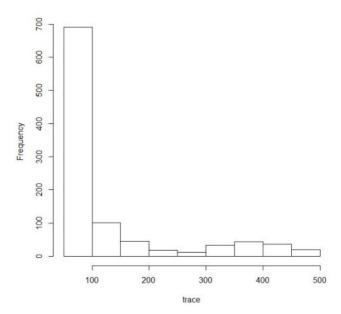

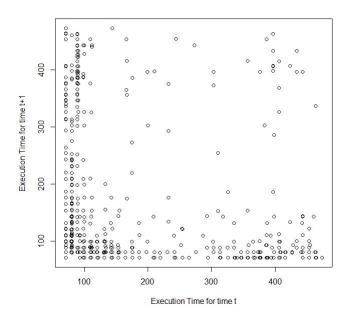

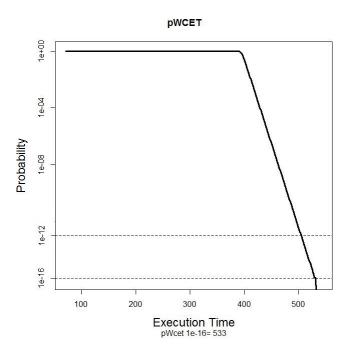

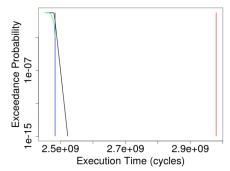

- EVT method represents the utilization of the Extreme value theory within the PROXIMA project. This method is complementary to all methods within the project (EPC, pTC-VICI and FBI-VICI). The method has two main versions: one for independent execution times and a second one for dependent execution times. Each version provides a voting procedure between the two possible versions of the EVT to provide the pWCET estimate. Since D3.4 the main evolutions of the EVT method concerns its adaptability to the PROXIMA use cases. Indeed the statistical tests are requiring appropriate test values and during this period such values have been refined. Moreover the latest version captures the low variability in execution times that some programs may experience. While generally stable, its R implementation does not offer the robustness of an industrial utilization and moving to other implementations is considered as future work.

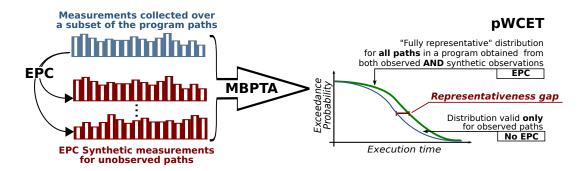

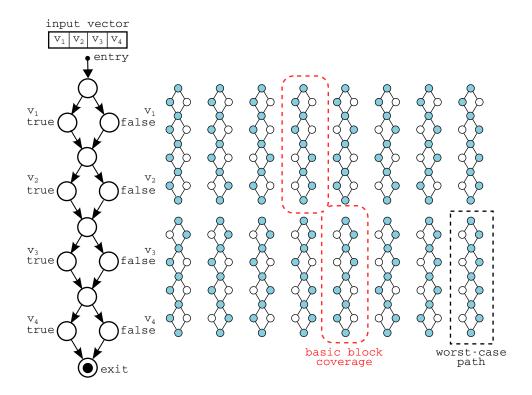

- **EPC** is the solution adopted in PROXIMA to cope with the problem of path representativeness in MBPTA. As it is generally not possible to guarantee that all paths have been triggered at analysis time, the Extended Path Coverage (EPC) aims at automatically generate synthetic observations to complement the set of measurements collected so that to obtain the same effect of full path coverage. Since D3.4, EPC have been ported from an early-stage prototype to a complete set of tools on top of the RVS tool chain. Extensions to the PROXIMA MBPTA tool chain and a set of specific tools have been realized in order to consolidate EPC into a well-defined end-toend process. The current implementation still need some refinements and improvement especially on the infrastructure and exploitable structural information. Nonetheless, EPC has been tailored on the FPGA-HW Rand platform and methods to support EPC trace collection have been consolidated and integrated on top of the industrial-quality tool chain, either on bare-metal or PikeOS. On the FPGA-HWRand, EPC has been successfully applied to industrial case studies. Extension to SW Rand platforms and FPGA-SW Rand in particular seems to be near-at-hand.

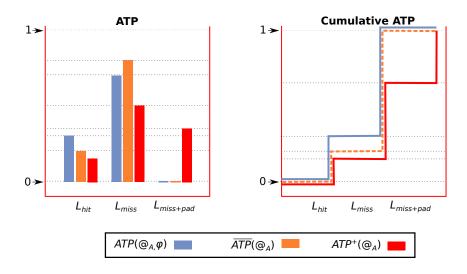

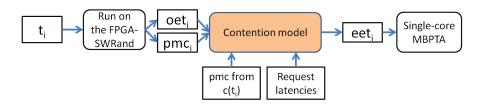

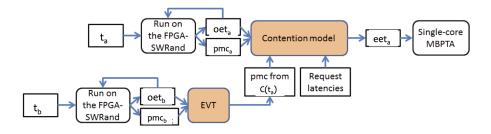

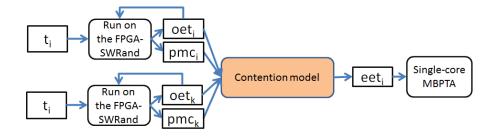

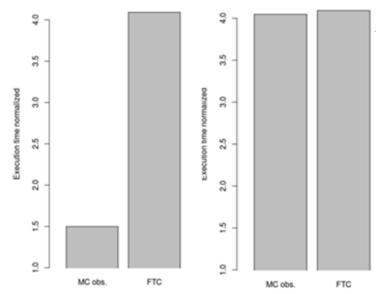

- pTC-VICI is the method used to account for multicore contention on top of the FPGA-SWRand platform. This method builds upon two premises: (i) no assumption can be made on how requests from the different contenders will align in time and hence, whenever a request from another core can create contention, the worst contention for that request is assumed; (ii) pTC-VICI (Partially/Fully Time composable analysis-VICI) allows to budget for a limited number of requests of specific types (with the worst timing alignment) so that an appropriate timing bound is chosen at integration time once contenders are known, or simply the contention allowed by contenders is limited

(in terms of number and type of requests) and this is monitored with Performance Monitoring Counters (PMCs) during operation preventing contenders to exceed their allowed request budgets. The pTC model is fully built upon PMCs measurements so as to match industrial practice. The pTC model has been developed from scratch since m18 where it did not exist, and it was developed to cover the FPGA-SWRand platform, for which no solution was in place to use by the end users' case studies.

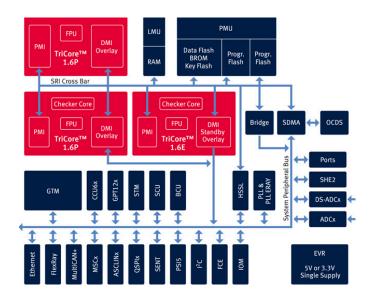

- **FBI-VICI** method is designed to model the effects on a task of a variable amount of interference generated by competing tasks running simultaneously on other cores. VICI analysis has been applied to synthetic benchmarks by academic partners to the AURIX and P4080 platforms. In addition, industrial partners have also applied the analysis to their codebases for these platforms, demonstrating the applicability of this approach. This approach is not restricted to the specific platforms for which it has been devised and integrated (P4080 and AURIX), and it can be potentially ported to other hardware platforms.

## **Contents**

| $\mathbf{E}_{2}$ | xecutiv                                                         | ve Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|

| 1                | Intro                                                           | duction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8                                                                    |  |  |  |  |

| 2                | Extreme value theory - the PROXIMA basis  2.1 Executive summary |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |  |  |  |  |

| 3                | 3.1 H<br>3.2 H<br>3.3 M<br>3.4 A                                | Executive summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20<br>20<br>20<br>23<br>27<br>29                                     |  |  |  |  |

| 4                | 4.1 F<br>4.2 I<br>4.3 M<br>4.4 4<br>4.4 4<br>4.5 M<br>4.4 4     | Executive summary  Description  Main evolutions since M18  4.3.1 Goal and required properties  4.3.2 Request types  4.3.3 Request latency  4.3.4 fTC model  4.3.5 Deterministic pTC (dpTC) solution  4.3.6 Probabilistic pTC (ppTC) solution  Advantages and limitations  Numerical evaluation  4.5.1 fTC  4.5.2 Deterministic pTC (dpTC)  Deterministic pTC (dpTC)  Advantages  Location of the properties of the prope | 33<br>33<br>33<br>37<br>37<br>39<br>40<br>41<br>42<br>44<br>45<br>46 |  |  |  |  |

| 5                | 5.1 H<br>5.2 H<br>5.3 M<br>5.4 A<br>5.5 M                       | Executive Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>48<br>48<br>49<br>51<br>52<br>55                               |  |  |  |  |

| 6                | <b>tems:</b> 6.1 I                                              | abilistic approaches from real-time to mixed-criticality sys-<br>before and after PROXIMA<br>Dependent programs vs. statistical and/or probabilistic (in)dependence<br>The definition of the probabilistic worst case execution time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |  |  |  |  |

| 7  | PROXIMA influence: new open problems for the real-time com- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |

|----|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|    | munity                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |

|    | 7.1                                                         | Classification of programs and processors accepting the Gumbel hy-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |  |  |

|    |                                                             | pothesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62 |  |  |

|    | 7.2                                                         | Representativity of a pWCET estimate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62 |  |  |

|    | 7.3                                                         | Generalizing EPC towards other platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62 |  |  |

|    | 7.4                                                         | Proving whether a sample size contains all relevant information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63 |  |  |

|    | 7.5                                                         | Assessing completely hardware in complex COTS platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63 |  |  |

|    | 7.6                                                         | Contender generation for inter-core interference analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 64 |  |  |

|    | 7.7                                                         | Interference-relevant factor selection with multi-modal distributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64 |  |  |

|    | 7.8                                                         | Integrate inter-core interference analysis in schedulability analysis $% \left( 1\right) =\left( 1\right) \left( 1$ | 64 |  |  |

| A  | crony                                                       | yms and Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66 |  |  |