#### **Public**

**FP7-ICT-2013- 10 (611146) CONTREX**

# Design of embedded mixed-criticality CONTRol systems under consideration of EXtra-functional properties

Project Duration 2013-10-01 – 2016-09-30 Type IP

| <b>C</b> ontrex | WP no. | Deliverable no. | Lead participant |  |

|-----------------|--------|-----------------|------------------|--|

|                 | WP3    | D3.2.3          | EUTH             |  |

# Implementation of execution platform and cloud service models (final)

Prepared by Paolo Azzoni (EUTH)

Issued by **EUTH**

Document Number/Rev. **CONTREX/EUTH/R/D3.2.3/1.0**

Classification CONTREX Public

Submission Date **2016-09-30**

Due Date **2016-09-30**

Project co-funded by the European Commission within the Seventh Framework Programme (2007-2013)

© Copyright 2016 OFFIS e.V., STMicroelectronics srl., GMV Aerospace and Defence SA, Vodafone Automotive SpA, Eurotech SPA, Intecs SPA, iXtronics GmbH, EDALab srl, Docea Power, Politecnico di Milano, Politecnico di Torino, Universidad de Cantabria, Kungliga Tekniska Hoegskolan, European Electronic Chips & Systems design Initiative, ST-Polito Societa' consortile a r.l., Intel Corporation SAS.

This document may be copied freely for use in the public domain. Sections of it may be copied provided that acknowledgement is given of this original work. No responsibility is assumed by CONTREX or its members for any application or design, nor for any infringements of patents or rights of others which may result from the use of this document.

## **History of Changes**

| ED.       | REV. | DATE       | PAGES | REASON FOR CHANGES          |

|-----------|------|------------|-------|-----------------------------|

| EUTH      | 0.1  | 2016-09-02 | 48    | Initial version             |

| OFFIS     | 0.2  | 2016-09-14 | 56    | Update OFFIS contribution   |

| POLIMI    | 0.3  | 2016-09-23 | 58    | Update PoliMi contributions |

| EUTH      | 0.4  | 2016-09-28 | 58    | EUTH update                 |

| INTEL     | 0.5  | 2016-09-28 | 57    | INTEL update                |

| EDALAB    | 0.6  | 2016-09-29 | 57    | EDALab update               |

| ST        | 0.7  | 2016-09-30 | 63    | ST update                   |

| ST-POLITO | 0.8  | 2016-09-30 | 94    | ST-Polito update            |

| IX        | 0.9  | 2016-09-30 | 97    | iXtronics update            |

| EUTH      | 1.0  | 2016-09-30 | 97    | Final release               |

### **Contents**

| 1 | Intr          | oduction                                        | 4  |  |  |  |

|---|---------------|-------------------------------------------------|----|--|--|--|

| 2 | The           | e execution platform description                |    |  |  |  |

|   | 2.1           | iNemo-M1                                        |    |  |  |  |

|   | 2.2           | SecSoc                                          | 7  |  |  |  |

|   | 2.3           | Zynq                                            | 9  |  |  |  |

|   | 2.4           | EUTH Minigateway                                |    |  |  |  |

| 3 | The           | e cloud service abstraction                     |    |  |  |  |

|   | 3.1           | Device to cloud                                 | 17 |  |  |  |

|   | 3.2           | Cloud service abstraction                       | 22 |  |  |  |

| 4 | Ser           | vices definition and characterization           | 28 |  |  |  |

|   | 4.1           | Open Virtual Platform used in use-cases 1 and 3 | 28 |  |  |  |

|   | 4.2           | Extension of OVP scenario with SystemC models   | 31 |  |  |  |

|   | 4.3           | Use-case 1: Unmanned Aerial Vehicle             | 33 |  |  |  |

|   | 4.4           | Use-case 2: Automotive Telematics               | 38 |  |  |  |

|   | 4.5           | Use-case 3: Ethernet Over Radio Systems         | 91 |  |  |  |

| 5 | Ext           | ra-functional-aware runtime management analysis | 92 |  |  |  |

| 6 | Coo           | de optimisation algorithms                      | 94 |  |  |  |

| 7 | Conclusions97 |                                                 |    |  |  |  |

| 8 | References    |                                                 |    |  |  |  |

#### 1 Introduction

This deliverable describes the final implementation of the execution platform and of the cloud service layer. It focuses on the description of the hardware nodes composing the execution platform and on the cloud platform, the core element of the cloud services implementation. For each use case, the deliverable provides more details about the services definition and characterization, previously outlined in deliverable D3.2.2. UC1 and UC3 are based on OVP simulation environment, while the device-to-cloud paradigm, which combines the execution platform and the cloud service layer, represents the technological baseline for UC2 scenario. Finally, the deliverable describes the adopted models and tools, outlining their relations with the runtime environment management and with the extra functional properties monitoring.

#### 2 The execution platform description

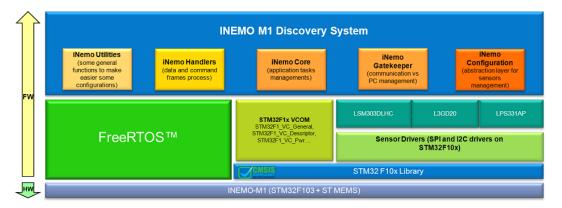

#### 2.1 iNemo-M1

The INEMO-M1 is a 9-degrees-of-freedom system-on-board (SoB), combining the latest advances in ST MEMS-based technology with the powerful computational core of theSTM32 family. The INEMO-M1 platform has been designed to target miniaturization, flexibility, low power consumption and cost effectiveness to provide a high-performance and versatile module suitable for a wide range of applications.

Figure 1. The iNEMO-M1 SOB from STMicroelectronics

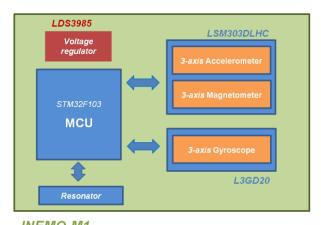

INEMO-M1 embeds the 6-axis digital e-compass module LSM303DLHC, the 3-axis digital gyroscope L3GD20 and the STM32F103REY6 high-density performance line ARM-based32-bit microcontroller.

The INEMO-M1 exploits the wide set of peripherals supported by the STM32F103REY6 in order to offer maximum flexibility in communication. Thanks to this wide set of communication peripherals and its extremely reduced dimensions, the INEMO-M1 can be directly integrated into a large variety of advanced motion-sensing platforms allowing simplification of the platform itself and increasing performance by distributing system intelligence.

The INEMO-M1 may be used in combination with ST's leading edge sensor fusion software to seamlessly implement high-performance 9-degrees-of-freedom applications.

INEMO-M1

Figure 2. iNEMO-M1 functional block diagram

It can operate with an externally regulated power supply in the range of 2.4 V- 3.6 V or, by using the on board LDS3985M33R voltage regulator, it could be supplied by an external voltage in the range of 3.6 up to 6 V.

#### 2.1.1 iNEMO M1 - STM32F103 MCU

The STM32F103REY6 high-density performance line microcontroller is the computational core of the INEMO-M1 module: it operates as the system coordinator for the onboard sensors and the several communication interfaces.

It is based on ARM Cortex<sup>TM</sup>-M3 processor core, the latest generation of ARM processors for embedded systems. With its 72 MHz maximum frequency, a 512-Kbyte embedded Flash and a 64-Kbyte SRAM accessed (read/write) at CPU clock speed with 0 wait states, it is suitable for storing programs and data.

Exploiting the features of the MCU, the INEMO-M1 offers a wide set of peripherals and functions such as 12-bit ADCs, DAC, general-purpose 16-bit timers plus PWM timers, I2C, SPI, I2S, USART, USB and CAN, that enable different operative conditions and several communication options, making the module a flexible solution for effortless orientation estimation and motion-tracking in embedded applications.

#### 2.1.2 iNEMO-M1 Sensors

The INEMO-M1 embeds two sensors: the LSM303DLHC, 3-axis accelerometer and 3-axis magnetometer in one single package, and the 3-axis digital gyroscope L3GD20.

The e-compass module LSM303DLHC is a system-in-package featuring a 3D digital linear acceleration sensor and a 3D digital magnetic sensor. The accelerometer has full scales of  $\pm 2g/\pm 4g/\pm 8g/\pm 16g$  and the magnetometer has full scales of  $1.3/\pm 1.9/\pm 2.5/\pm 4.0/\pm 4.7/\pm 5.6/\pm 8.1$  gauss. All full scales available are selectable by the user. The L3GD20 is a low-power digital gyroscope able to sense the angular rate on the three axes. It has a full scale of  $\pm 250/\pm 500/\pm 2000$ .

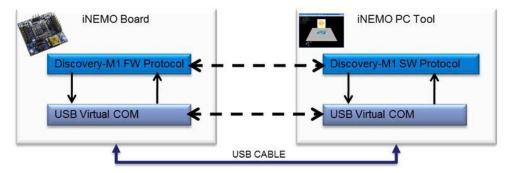

#### 2.1.3 Discovery M1 application board

The Discovery M1 opens the INEMO-M1 ecosystem to the worldwide developer community. It offers a means to explore and evaluate the INEMO-M1, providing complete access to all the benefits of the first 9-axis system-on-board (SoB) in the iNEMO® module family. The accelerometer, gyroscope, magnetometer and ARM® Cortex<sup>TM</sup>-M3 32-bit MCU are fully accessible to the user firmware, enabling the implementation of complex and versatile inertial applications in fields such as robotics, personal navigation, gaming, and wearable sensors for healthcare/fitness or sport kinetics.

Figure 3. Discovery M1 evaluation board

The pin-out of the two on-board connectors offers immediate access to all of the communication interfaces and peripherals of the INEMO-M1.

#### 2.1.4 Discovery M1 Key Features

- Two power supply options: through the USB bus or from one of two external supply voltages, VEXT (from 3.6 to 6 V) or D\_VDD (from 2.4 V to 3.3 V)

- INEMO-M1: 9-axis SoB, 13x13x2 mm size factor

- LPS331AP: MEMS pressure sensor 260-1260 mbar absolute digital output barometer

- INEMO-M1 pinout available on two double connectors

- SWD connector for programming and debugging.

- Two pushbuttons (reset and user)

- Two LEDs: user LED, power-on LED

- RoHS compliant

#### 2.1.5 Software development kit

A software package has been developed to fully support the application design activity on iNEMO platform, including a Software Development Kit for sensors configuration and the source code of Kalman filter algorithm implementation for attitude angles reconstruction based on data measured by integrated inertial motion MEMS sensors.

A list of provided software tools and firmware libraries is detailed below:

- A GUI (Graphical User Interface) to exploit the Discovery M1 board features and display the sensor data

- An SDK (Software Development Kit) to develop personalized PC applications

- A Compass application demo

- A 3D Cube demo to show the AHRS (Attitude Heading Reference System) capability of iNEMO Engine Lite

- A complete set of firmware libraries to manage the INEMO-M1 on-board sensors

- A firmware framework based on FreeRTOS<sup>TM</sup>

#### 2.2 SecSoc

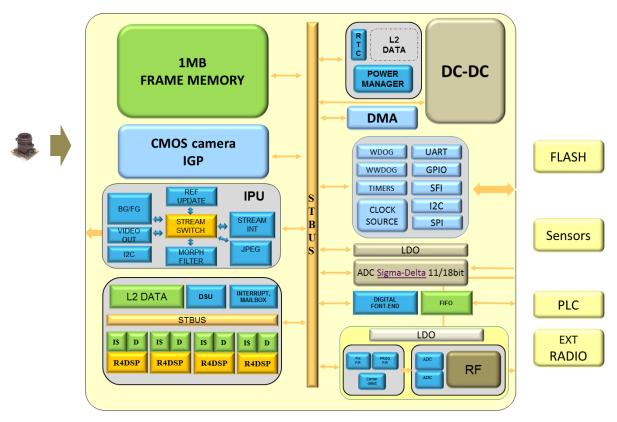

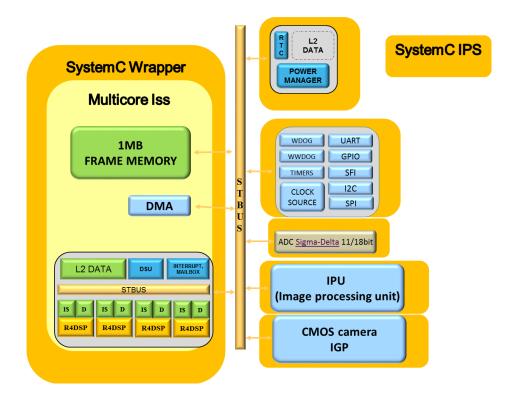

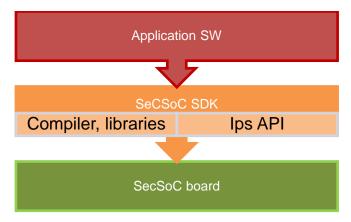

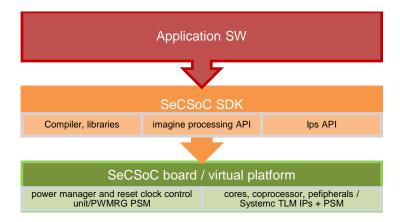

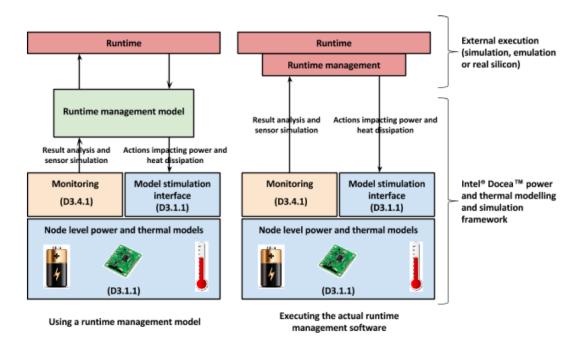

STM provides a SoC specifically intended for image processing captured by a low-power CMOS camera. The architecture of the SoC (shown in Figure 4) extends the typical structure of a high-end microcontroller with specific modules for image processing, ultra-low power

analog modules, and power island and clock gating capabilities. The SoC is based on the multi-core R4MP processor.

Figure 4: SeCSoC architecture.

Figure 5: SeCSoC board.

The board that has been provided has a size similar to a credit card, and it includes two vga sensors, optional sensors connectors, usb, spi, uart, jtag host connectivity, a digital stereo microphones and pressure and temperature sensors. The adoption of multi-core technology also in some of the sensing units allows for an improved management of extra-functional aspects

such as power consumption, execution time, quality of service, security and reliability. The proprietary cores can be programmed through a development toolchain (gcc+GNU binutils based) released by ST. Moreover, peripheral library APIs are available.

#### 2.3 Zynq

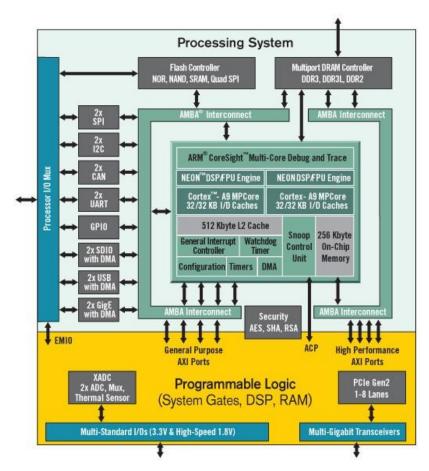

The Xilinx Zynq-7000 family is a rich System on Chip (SoC) which combines a heterogeneous ARM Cortex-A9 MPCore and a programmable logic that is realized through an FPGA part in the chip. Thus, the chips of the Zynq-7000 family are representing an all programmable SoC with highest flexibility in programming the hardware, software and the inputs and outputs, which makes them interesting for a wide range in on-chip design space exploration.

Figure 6: Overview of Zynq-7000 architecture.

Figure 6 shows a rough overview of the SoC's architecture. At the top of the figure the processing system is presented with its ARM dual core in the center surrounded by the AMBA interconnect. This interconnect defines the connections to the I/O interfaces, the Flash and DRAM controllers as well as to the programmable logic. The hardware I/O interfaces can be configured and connected to pins by the user. While the programmable logic is also tied to the AMBA interconnect the ability to build further interfaces is given to the user. There is also the possibility to use the programmable logic to instantiate other IP cores, e.g. softcores, DSPs, etc. With the SDIO or flash interface it is possible to boot a Linux kernel or other operating systems on the ARM cores as well as loading bit streams and applications for the programmable logic. These possibilities make the Zynq-7000 family to a very powerful platform which has been be used for use-case 1.

#### 2.3.1 Evaluation board selection

Within CONTREX no new PCB for the targeted controller will be designed. Instead, an existing board has been chosen to be used within the use cases. Figure 7 shows the industrial board which has been used for the multi-rotor system in use-case 1. The board occupies one ynq 7020, which operates at up to 766MHz for the ARM dual core and that offers 85k logic cells within the programmable logic. This version of the SoC can be used with the free WebPACK license of the Xilinx tools. Next to the Zynq the 40x50mm industrial board contains 1GB DDR3 RAM and offers access to 152 I/O ports for the programmable logic as well as 14 MIOs (Multiplexed I/Os) of the processing system. This industrial board has been put on a carrier board which provides the hardware interfaces for the connection to the other components of the multi-rotor system.

Figure 7: Industrial board TE0720-02-2IF from Trenz Electronic [2]

# 2.3.2 Run-time power management and resource management capabilities of selected platform

In the context of CONTREX the Zynq provides mechanisms for run-time power management as well as for resource management capabilities.

Regarding power management, one of these capabilities is the dynamic frequency scaling (DFS). This feature of the processing systems gives the availability to control the frequency of the ARM dual core or the programmable logic. Together with an external voltage regulator which is configurable on the fly by the operating system it would be possible to realize a system with dynamic voltage and frequency scaling (DVFS). The same method can be used for the external DDR RAM or peripherals. It is also possible to shut down the unused clocks for saving power. If an asymmetric processing of the ARM cores is used, it is possible to use CPU hotplug. With this feature it is possible to bring up or shut down the secondary processor core if it is or is not needed at the time. A wake up of a core can be done by an interrupt for example.

Regarding resource management, a Linux kernel has been used on the ARM cores offering Linux control groups including the subsystems *cpu*, *cpuset*, *memory*, and *cpuacct*. Thus, it should fulfil all requirements of the Barbeque Open Source Project[3] that is envisioned to be used in the project.

#### 2.4 EUTH Minigateway

The EUTH Minigateway is a compact size device designed to support M2M (Machine to Machine) applications where low cost, low power, performances and communications capabilities are required. It has been conceived as an industrial grade smart device that provides full support to Kura framework for M2M systems integration in industrial and automotive applications. The device has been designed to be RoHS compliant and to satisfy the following standards: CE, FCC, IC, J1455, UL.

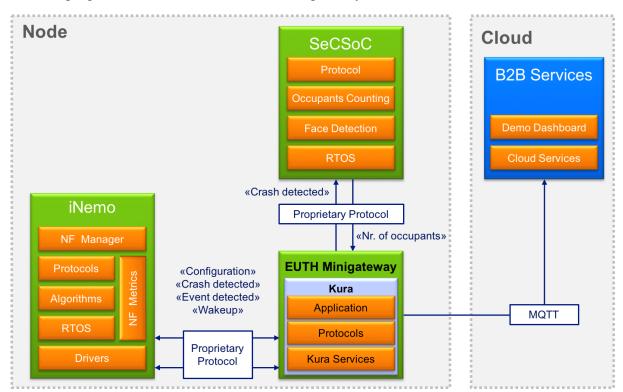

The Minigateway is a component of the execution platform adopted for the Automotive use case (UC2). In this context it acts as a bridge between the "sensing" units installed in the car and the cloud platform: the iNemo detects crashes and sends the related information to the Minigateway that, in turns, controls the SecSoc for the photos acquisition/elaboration. Finally, the Minigateway uploads the data on the cloud platform. The first release of the UC2 demonstrator has been based on the first set of EUTH Minigateway prototypes, while the final version is based on the second release of the Minigateway, already introduced in D4.2.1. The following figure illustrates the role of the Minigateway in the UC2 demonstrator.

Figure 8: EUTH Minigateway in the UC2 demonstrator.

The EUTH Minigateway is based on a powerful ARM8 microprocessor, high speed DDR3 RAM, Flash Memory and a rich set of communications interfaces. An expansion connector supports additional peripherals such as LCD display, keyboard, A/D interfaces and much more.

The device is supported by a broad range of operating systems, but in the UC2 context the selected operating system is POKY Linux, which is part of the Yocto Project. Yocto is an open source collaboration project that provides templates, tools and methods to simplify the creation of custom Linux-based systems for embedded products, regardless of the hardware architecture. (https://www.yoctoproject.org/).

The following figure shows the board of the ETH Minigateway.

Figure 9: The industrial board of the Minigateway from Eurotech.

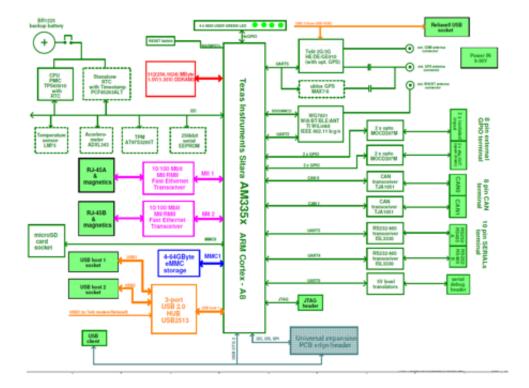

The functional architecture of the Minigateway is illustrated in the following block diagram.

Figure 10: The functional architecture of the Minigateway.

The CPU is an integrated system-on-a-chip microprocessor for high-performance, low-power portable handheld and handset devices, the TI AM335X, an ARM Cortex A8 from Texas Instruments. It incorporates on-the-fly voltage and frequency scaling and sophisticated power management. The characteristics of this system on a chip, its power consumption and thermal

profiles make the AM335X a good solution for an Automotive context. I.e., this low power device does not require a heat sink for temperatures up to 70°C (85°C for the industrial variant). The Minigateway uses an internal real time clock (RTC) to store the date and time and provides power management events. The real time clock is mapped into the Linux operating system and can be read or written using standard Linux utilities. An internal watchdog timer, from the AM335x CPU, can be used to protect against erroneous software.

The board supports two types of memories:

- Up to 512MB resident NAND FLASH disk containing:

- o Boot loader: Uboot to boot embedded Linux

- Embedded Linux

- Application images.

- Up to 512MB of DDR3 SDRAM for system memory. Additionally, the unit can support a microSD and various USB storage devices.

The AM335x processor contains an integrated LCD display controller, which can be used to control and on-board LCD Display.

Considering the role and functionalities required by UC2 it is important to provide a rich set of interfaces and communication channels. The device must be ideally suited for M2M and IoT (Internet of Things) applications, which means connecting sensors, actuators and devices to the enterprise application and services. For this purpose, several interfaces are provided: USB, CAN Bus, Serial Communication Ports, GPIO. Furthermore, the Minigateway must be a connected device and a powerful combination of interfaces for a broad range of communication connectivity applications has been included: Ethernet, Bluetooth, Wifi, GPRS and 3G.

#### 2.4.1 EUTH Reliagate

EUTH is currently orienting the engineering activities to a new modular approach in industrial and automotive service gateway design that extends the features of the Minigateway to a more modular and flexible system. The version 2 of the Minigateway represented the first step in this direction because, e.g., it is already compatible with external cellular modules that increases its communication potentialities. Starting from the Minigateway design, the result of this engineering activity is Reliagate 10-11, a new industrial and automotive multiservice gateway that has been recently included in EUTH products portfolio. The following figure illustrates the Reliagate 10-11 [10] and the ReliaCell [11] cellular module.

The Reliagate is ARM Powered (TI AM335X CPU) with optimum performance for intensive workloads at just 2W. It is IoT Ready, providing a rich set of connectivity options, field bus interface and on-board sensors. It natively supports Kura and it's commercial version ESF [12]. It is an industrial and automotive grade multiservice gateway, with support for a wide operating temperature, a wide range power supply with transient protection and compliancy with several standards: CE, FCC, E-mark, IC 60950-U, RoHS2, REACH, FCC, PTCRB, IP40, MTBF >40000h or 5 years. The Reliagate is globally deployable, because the ReliaCell is a global cellular module with leading carrier pre-certifications.

Figure 11: the final version of Reliagate 10-11.

Figure 12: Reliagate 10-11 rear panel view.

Figure 13: Reliagate 10-11 top view.

Figure 14: EUTH Reliacell cellular module.

#### 2.4.2 EUTH Reliagate Family specification

Following the new modular and flexible design approach, an entire family of multiservice gateways has been introduced in the project portfolio. The following table illustrates the specification of the Reliagate family.

|                     | REGATE-10-11-XX        |                                                                                                                                                      |                                        |                                                                                              |                                |                         |

|---------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------|-------------------------|

| XX=                 |                        | -31 -32 -33                                                                                                                                          |                                        |                                                                                              | -35                            | -36                     |

| PROCESSOR           | CPU                    |                                                                                                                                                      |                                        | 3352 800MHz, 1 core                                                                          |                                |                         |

| MEMORY              | RAM                    | 512MB DDR3                                                                                                                                           |                                        |                                                                                              |                                |                         |

| STORAGE             | Embedded               |                                                                                                                                                      |                                        | 4GB eMMC                                                                                     |                                |                         |

| STORAGE             | Other                  | 1x microSD slot (User Accessible)                                                                                                                    |                                        |                                                                                              |                                |                         |

|                     | Ethernet               | 1x 10/100Mbps 2x 10                                                                                                                                  |                                        | 2x 10/100Mbps                                                                                | 1x<br>10/100Mbps               | 2x 10/100Mbps           |

|                     | USB                    | <ul> <li>2x USB 2.0         (Noise and Surge Protected)</li> <li>1x USB 2.0 for ReliaCELL</li> <li>2x USB 2.0 (Noise and Surge Protected)</li> </ul> |                                        | <ul> <li>2x USB 2.0 (Noise and Surge Protected)</li> <li>1x USB 2.0 for ReliaCELL</li> </ul> |                                |                         |

| I/O INTERFACES      | Serial                 | <ul> <li>2x RS-232/RS-485 (Surge protected, RS-485 termination and fail-safe resistor)</li> <li>1x Serial console TTL</li> </ul>                     |                                        |                                                                                              |                                |                         |

|                     | CAN 2.0B               | No                                                                                                                                                   |                                        | 2x CANBus 100mA v                                                                            | vith 5V power ou               | ıt                      |

|                     | Digital I/O            | <ul> <li>2x Digital Input 5V (TTL), 1KV optoisolated</li> <li>2x Digital Output (50VDC), 10mA sink, 1KHz max switching</li> </ul>                    |                                        |                                                                                              |                                |                         |

|                     | Cellular               | Optional with ReliaCELL 10-20 3G global (integrated)                                                                                                 |                                        | Optional with ReliaCELL 10-20                                                                |                                |                         |

|                     | GPS                    | Optional with ReliaCELL 10-20 Included in 3G module                                                                                                  |                                        | Optional with ReliaCELL 10-20                                                                |                                |                         |

|                     | Wi-Fi / BT             | No 802.11b/g/n + 4.0<br>BLE                                                                                                                          |                                        | No                                                                                           | 802.11b/g/n + 4.0<br>BLE       |                         |

| RADIO<br>INTERFACES | Antennas<br>(external) | No                                                                                                                                                   | 1x SMA     Cellular     1x SMA     GPS | <ul> <li>1x SMA<br/>Cellular</li> <li>1x RP-SMA<br/>Wi-Fi/BT</li> <li>1x SMA GPS</li> </ul>  | No                             | • 1x RP-SMA<br>Wi-Fi/BT |

|                     | SIM Slot               | No 1x microSIM No                                                                                                                                    |                                        |                                                                                              | No                             |                         |

|                     | Ext.<br>Watchdog       | Yes                                                                                                                                                  |                                        |                                                                                              |                                |                         |

|                     | RTC                    | Yes, with user accessible battery                                                                                                                    |                                        |                                                                                              |                                |                         |

|                     | TPM                    | Factory option                                                                                                                                       |                                        |                                                                                              |                                |                         |

|                     | EEPROM                 |                                                                                                                                                      |                                        | 256kbit                                                                                      |                                |                         |

| OTHER               | Sensors                | Temperature Temperature / Accelerometer                                                                                                              |                                        | Temperature                                                                                  | Temperature /<br>Accelerometer |                         |

|                     | LEDs                   | <ul><li>1x Power</li><li>4x Programmable<br/>(2x Green, 2x<br/>Amber)</li></ul>                                                                      | • 1x Power • 1x Power                  |                                                                                              | r<br>rammable (2x Green,       |                         |

|                     | Buttons                | 1x Reset, 1x Programmable                                                                                                                            |                                        |                                                                                              |                                |                         |

| POWER               | Input                  | 9-36VDC (Nominal 24VDC) with transient protection                                                                                                    |                                        |                                                                                              |                                |                         |

|                     |                    | Vehicle Ignition Sense                                                                            |  |  |

|---------------------|--------------------|---------------------------------------------------------------------------------------------------|--|--|

|                     | Consumption        | 2 W (idle)                                                                                        |  |  |

| ENVIRONMENT         | Operating<br>Temp. | -20 to +70°C                                                                                      |  |  |

| ENVIRONMENT         | Storage<br>Temp.   | -40 to +85°C                                                                                      |  |  |

|                     |                    | • CE - EN300 328 (2.4 GHz ISM), EN50371 (EMI), EN301489 (EMC)                                     |  |  |

| CERTIFICATIONS      | Wi-Fi/BT<br>Radio  | • FCC - 15.209 (General RF device), 15.247 & 5.249 (2.4GHz ISM)                                   |  |  |

|                     | Cellular           | <ul> <li>PTCRB</li> <li>FCC PART 22, 24 &amp; 27 and suitable GSM radio certifications</li> </ul> |  |  |

|                     | Ingress            | IP 40                                                                                             |  |  |

|                     | Enclosure          | ABS - Color: aluminum                                                                             |  |  |

| MECHANICAL SOFTWARE | Dimensions         | 140x95x45mm (WxDxH)                                                                               |  |  |

|                     | Weight             | 160 g                                                                                             |  |  |

|                     | Mounting           | Mounting Brackets (Wall, DIN Rail, General Purpose Bracket)                                       |  |  |

|                     | OS                 | Yocto Linux 1.6 - Kernel 3.14                                                                     |  |  |

|                     | SDK                | Yocto-based Eclipse Tooling                                                                       |  |  |

|                     | IoT<br>Framework   | Everyware Software Framework (Java/OSGi)                                                          |  |  |

#### 3 The cloud service abstraction

#### 3.1 Device to cloud

Machine to Machine (M2M) and Internet of Things (IoT) follow a common technological paradigm: intelligent devices, seamlessly connected to the Internet, enable remote services and provide actionable data. The IoT acronym is more adopted in the consumer space while M2M has a stronger industrial connotation. UC2 Automotive scenario can be considered a M2M application.

One of the most important aspects of the "Internet of Things" (IoT) vision is that smart objects communicate effectively with each other and with applications residing in data centers or the cloud.

The concept of the "device to cloud" proposes an end-to-end solution that includes:

- purpose-built hardware, connectivity and embedded device management through a pervasive software framework and a cloud client, running on the devices,

- and a set of machine to machine (M2M) cloud-based services.

The objective of this solution is to deliver actionable data from the field to downstream applications and business processes, dashboards and reports.

The concept of "device to cloud" is fundamental for UC2 scenario and, more in general, for similar contexts because for today's business it is increasingly important to have constant visibility of assets and processes, anytime and anywhere.

The Kura pervasive framework and the cloud platform, proposed in Contrex project, offers the technical building blocks required to assemble distributed systems of devices and sensors which are effectively connected to IT infrastructures. This solution is based on a combination of hardware, firmware, operating systems, programming frameworks that dramatically accelerate the time to market of M2M / IoT projects and enable future potential customers to layer their added-value components on a reliable read-to-use infrastructure.

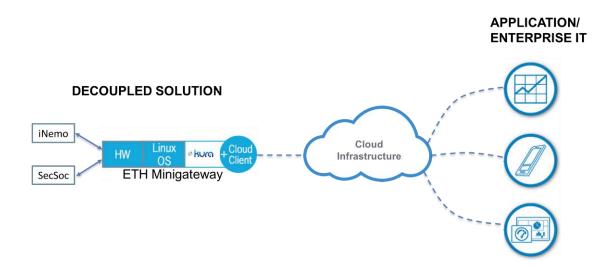

Regarding UC2 use case, a decoupled solution based on the device-to-cloud approach has been adopted: the vehicle ECUs are responsible for data acquisition and are physically connected to a Minigateway and thus to the cloud. The Minigateway acts as a bridge between the ECUs and the cloud and hosts the Kura framework. The following figure illustrates the two "device to cloud" solutions that has been adopted in UC2.

Figure 15: The device to cloud solution adopted in UC2.

#### 3.1.1 Kura software framework

Eurotech's Kura is an inclusive, pervasive and targeted software framework for embedded systems. Kura is a programming environment that wraps the complexity of low level device management with high level constructs. This approach permits simpler and faster programming, with shorter, easier to read code and transparent portability across different hardware platforms.

Kura allows to deliver not only the latest generation pervasive computer hardware platforms, but also all aspects of the required software stack:

- a bootloader/BIOS for hardware platform,

- an operating system,

- a Java Virtual Machine,

- an OSGi application framework,

- and an extensive set of ready-to-use Java Plug-Ins (called bundles) provided for unique platform supplied hardware, network, cellular, and storage applications.

All of these components are "integrated" in Kura and are based on open standards, tools, and implementations. The amount of third party development is greatly reduced, allowing customers to focus on what they do best – writing their business application logic without having to spend man-years developing the software infrastructure and frameworks upon which those applications can run.

#### 3.1.2 The Kura architecture

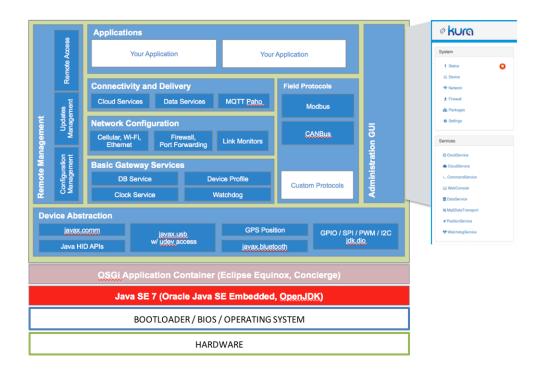

From a functional point of view, the Kura architecture is illustrated in the following figure:

Figure 16: The Kura functional architecture.

Kura has been conceived to support a wide set of hardware devices and the choice of distributing it as an open source project is strategic from this point of view. In the context of the automotive use case (UC2) the adopted hardware is the ETH Minigateway. Many other embedded systems are supported, from industrial embedded systems to popular gateways like the Raspberry Pi or the BeagleBone. The higher-level Kura components are designed to be supported across platforms, independent of board-level differences in the hardware platform. Low-level hardware drivers and components are provided as part of Kura's platform-specific software core.

Bootloader and/or BIOS for each hardware platform are ported and validated by Eurotech as part of the platform-specific software core. The Bootloader/BIOS provides the start-up of the operating system.

With this approach, various operating systems can be ported to the hardware platforms and validated. For the EUTH Minigateway a custom Yocto-based Linux has been selected.

The core technology of Kura is the Java Virtual Machine (JVM). Java runs in a virtual machine runtime environment and thus runs across all operating systems. This allows code reuse between systems and applications following the principle "write once, run anywhere". The Java Native Interface (JNI) provides the hooks for native 'C' code interfaces where custom hardware or performance is required. Kura currently uses the Oracle Java SE Embedded Virtual Machine.

OSGi [13] originally stood for Open Services Gateway initiative and was designed as a services gateway for set-top boxes. Since its introduction ten years ago, it has become broadly adopted by industry as a whole and is now just referred to as "OSGi". OSGi is an Application Framework that provides the environment for running many different applications implemented with a strong component-based SOA oriented model. The OSGi Framework provides a set of

comprehensive and advanced features for installing, starting, stopping, updating, and uninstalling applications dynamically.

Kura runs on OSGi Equinox implementation, from the Eclipse Foundation.

Kura provides the core functionality for getting started with application development using documented APIs. This includes:

- hardware Virtualization (most applications don't care what hardware they are running on. Components are written to operate independently from the hardware platform.).

- Device Configuration Management.

- System Logger (Real-time system logging of debug and runtime information).

- Management of Network Devices (Ethernet, Wi-Fi, Cellular, and Bluetooth).

- IP Networking (DHCP server/client, DNS proxy, Firewall, and Time synchronization).

As project requirements expand beyond the basic Foundation set of bundles, Kura offers targeted vertical market bundles that can provide additional functions and features according to the requirements of the customer. These include a growing set of APIs that are ready to use or to customize for customer applications: location tracking, mobile asset management, Passenger/People Counter, Industrial Protocol (SCADA) Communication (e.g. Modbus, CanBus), MQTT or COAP Publish/Subscribe broker technology, Cloud-based asset and data management infrastructure, etc..

Kura is written around standard Java interface APIs that can be easily incorporated into a specific business application logic. Many standard implementations are available to use as-is, but APIs can be re-implemented according to specific application requirements. It is also possible to decide to add custom sets of bundles that run in addition to Eurotech's growing set of functional bundles.

The Eclipse Integrated Development Environment (IDE) is the dominant application environment in the industry today. The Eclipse IDE provides Kura with all of the tooling required to develop, test, debug, and package application bundles and to deploy these bundles to the Kura environment on every target platform. Eclipse provides a rich set of capabilities for writing applications in Java, C, Javascript/AJAX, and many others. Furthermore, Kura has been released as open source in the context of the Eclipse Development Program.

#### 3.1.3 The Kura Abstraction Layer

The Kura abstraction layer is more than a simple hardware abstraction layer. Kura is a programming environment that wraps the complexity of low-level device management with high level constructs. With this approach the hardware abstraction is just the first level of abstraction of the embedded system: more high-level and application oriented abstraction levels are provided. These levels translate in services that simplify and speed-up the software development: data services, cloud services, configuration services, remote management services, web services, etc.. A rich set of services that abstract the complexity of the embedded system is a key element for the adoption of the "device to cloud" paradigm.

From a development point of view, Kura aims at offering a Java/OSGi-based container for M2M applications running in service gateways. It provides or, when available, aggregates open

source implementations for the most common services needed by M2M applications. Kura components are designed as configurable OSGi Declarative Service exposing service API and raising events. While several Kura components are in pure Java, others are invoked through JNI and have a dependency on the Linux operating system.

Kura is currently providing the following initial set of services:

#### I/O Services

- o Serial port access through javax.comm 2.0 API or OSGi I/O connection.

- o USB access and events through javax.usb, HID API, custom extensions.

- Bluetooth access through javax.bluetooth or OSGi I/O connection.

- o Position Service for GPS information from a NMEA stream.

- o Clock Service for the synchronization of the system clock.

- Kura API for GPIO/PWM/I2C/SPI access.

#### Data Services

- Store and forward functionality for the telemetry data collected by the gateway and published to remote servers.

- Policy-driven publishing system, which abstracts the application developer from the complexity of the network layer and the publishing protocol used. Eclipse Paho and its MQTT client provide the default messaging library used. In addition, support for the Cobra field protocol has been provided.

#### Cloud Services

- Easy to use API layer for M2M application to communicate with a remote server. In addition to simple publish/subscribe, the Cloud Service API simplifies the implementation of more complex interaction flows like request/response or remote resource management.

- o Allow for a single connection to a remote server to be shared across more than one application in the gateway providing the necessary topic partitioning.

#### Configuration Service

Leverage the OSGi specifications Configuration Admin and MetaType to provide a snapshot service to import/export the configuration of all registered services in the container.

#### • Remote Management

Allow for remote management of the M2M applications installed in Kura including their deployment, upgrade and configuration management. The Remote Management service relies on the Configuration Service and the Cloud Service.

#### Networking

o Provide API for introspects and configure the network interfaces available in the gateway like Ethernet, Wifi, and Cellular modems.

#### Watchdog Service

o Register critical components to the Watchdog Service, which forces a system reset through the hardware watchdog when a problem is detected.

#### Web administration interface

Offer a web-based management console running within the Kura container to manage the gateway.

#### 3.2 Cloud service abstraction

The cloud platform is a machine to machine integration platform that simplifies device and data management by connecting distributed devices over secure and reliable cloud services. It is an end-to-end platform that provides an easy path to connect cloud-ready devices to IT systems and/or applications. Once devices are deployed, the cloud platform allows users to connect, configure and manage devices through the lifecycle, from deployment, through maintenance, to retirement. In the context of the Automotive use case (UC2), the devices are the embedded systems installed in the car and the data are the functional and extra functional properties monitored by these devices.

The cloud service abstraction is responsible to provide full control over the embedded systems hardware, software and acquired data with a simple service model. The objective is to completely hide the complex details that stand behind the remote management procedures, remote data acquisition and transmission.

#### 3.2.1 The cloud platform architecture

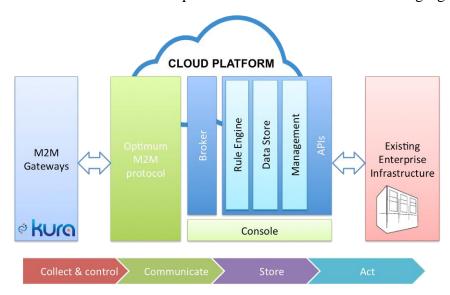

The functional architecture of the cloud platform is described in the following figure:

Figure 17: The architecture of the cloud platform.

The M2M protocol is a fundamental element for the cloud infrastructure and the entire device to cloud system. The protocol represents the "glue" that keeps together the distributed elements (sensors, embedded devices/gateways and cloud) that form the pervasive cloud system. For this reason, the cloud platform supports natively a publish-subscribe message brokering protocol known as MQTT. MQTT is an open standard transport layer, which uses a hierarchical topic namespace and a flexible data payload. MQTT is bandwidth efficient and simple to implement, providing both security and reliability of transport and allowing the decoupling between data producers and application consumers, in a one-to-many message distribution. Considering the historical importance of this telemetry protocol for the industrial world, the platform includes MQTT as a standard data communication feature.

The core technology of cloud platform is the message broker. The broker runs in the cloud and provides an MQTT server into which devices publish their data. MQTT clients may also issue subscriptions for certain topic namespace definitions. When a data payload is published into the cloud on a certain topic, the payload is redistributed to connected clients subscribed to that topic. The subscribe/notify model is the basic concept on which the broker, and indirectly the entire cloud infrastructure, is built.

The Rule engine is one of the core components of the cloud platform. The engine is based on SQL and its role is to process incoming published data, allowing immediate message processing and/or notifications to occur based on user-defined criteria. Statistical rules are applied over the data in real-time. The actions generated by a rule can include e-mail, SMS, or Twitter notification, a field protocol publish event, or a REST API call.

The cloud platform utilizes a non-SQL non-relational database for device data storage. The data is redundant and replicated across geographical regions for maximum reliability. Device/user and data plan details are stored in a separate replicated, redundant SQL database. This solution satisfies the typical requirements of an application that has to manage huge amounts of data (Big Data) but, at the same time, has to integrate with the existing enterprise infrastructure.

The management component of the cloud infrastructure has been introduced to provide a rich set of features for data management, cloud infrastructure management and application development. This component includes: a security layer, a device management, a data management unit, an account management layer, a unit for device configuration administration and a layer for application integration support.

REST APIs provide easy, programmatic access to request or store data from the storage databases and to all the other features of the Cloud platform. The APIs allow you to incorporate the data into another system or to develop custom applications within the existing enterprise infrastructure.

The console provides a graphical user interface that shows all aspects of the cloud account's operation. The administrator account has the responsibility to manage users, devices, data, data plans, and rules definitions through the console. Standard users can be given permissions to view data, as needed.

The cloud platform is designed to provide a "zero configuration" communication architecture, allowing the developer/administrator to focus on developing business application components, without having to worry about device-level programming or complicated data networks. It is a

powerful software framework, leveraging the power and redundancy of cloud computing, open-standard protocols (MQTT, TCP/IP, REST), and strong security.

#### 3.2.2 The cloud service abstraction

The cloud service abstraction is the second level of abstraction introduced by the "device to cloud" approach. This abstraction layer introduces a set of services that simplify, from the cloud, the data collection, device monitoring, data management, account management, etc.. The service abstraction cooperates with Kura to completely hide the complexity of hardware, communications and cloud infrastructure.

#### 3.2.2.1 The cloud service data model

The cloud platform data model allows to describe functional and extra-functional properties in the cloud. The data model builds on the MQTT protocol by adding an open structure to the topic namespace and the message payload. This addition enables real-time analysis of the data stream published by the devices (via Kura) and establishes a control channel to remotely manage the devices with a command and control approach.

The platform introduces two types of topics:

- publish topic,

- control topic.

A publishing topic is used by a device (or application) to publish data into the cloud platform. On the contrary, a control topic is used by the application or the platform to send data to a device, such as for real-time control of physical control outputs.

A generic publishing topic can be represented as follows:

cloudAccountName/assetId/semanticTopic

#### where:

cloudAccountName is the name of the cloud account and is used as a unique identifier that represents a group of devices and users.

assetId is a unique identifier within an account that represents a particular asset. It is a good practice to associate the assetId to a single gateway device and to map it to the Client Identifier (Client ID) as defined in the MQTT specifications. For a gateway, the MAC address of its primary network interface is generally used as the Client ID and Asset ID of that gateway.

semanticTopic is the section of the topic used to further specify information about the application or sensors from which the data has been gathered, using a hierarchical namespace representation. The semanticTopic should be further expanded to provide further levels of topic space that can be subscribed to and queried based on data content. In example it is very useful to identify an application running on the gateway device with an app\_id. Also the management of resources, like sensors, actuators, local files, or configuration options, can be simplified by the use of a resource\_id. Applications manage resources by being able to list them, read the latest value, or update them with a new value. Each resource could be identified by a resource\_id as part of the hierarchical topic.

With this approach, a gateway identified by assetId (client ID) and belonging to accountName can have one of more applications—"app\_id1" and "app\_id2"—running. Each application can manage one or more resources identified by distinct resource id(s).

The control topics can be classified in two categories:

- topics that represents a control channel to the specific device,

- topics that represents a control channel to all the devices belonging to an account.

These two topics are defined respectively as follows:

\$ctrl/accountName/assetId/semanticTopic

or

\$ctrl/accountName/+/semanticTopic

#### where:

\$ctrl is the default part of the control topic and cannot be changed or altered. This prefix distinguishes control topics from data topics used in unsolicited reports, and it marks the associated control messages as transient, not stored in the historical data archive if one is present.

accountName is the name of the account owner.

assetId is a unique ID representing a particular asset (either the application or the sensors from which the data has been gathered).

semanticTopic is the section of the topic used to further specify information about the device or data, using a hierarchical name space representation.

+ is an operator that aggregates all the asset IDs belonging to a specific account (essentially a wildcard character used as a middle element of the topic namespace).

An additional control topic may be used in Rules. It is defined as follows:

\$accountName/rulesAssistant/semanticTopic

#### where:

\$accountName is the name of the account owner.

rulesAssistant is specific to the cloud rules processing

semanticTopic is the section of the topic used to further specify information about the device or data, using a hierarchical name space representation.

When creating a new account in the cloud platform, the account holder is given publish and subscribe rights to the Publish and Control topics for that account. By default, when establishing a new cloud connection, the Cloud Client for Java subscribes to the aforementioned control topics listing for messages that may be addressed to that device.

#### 3.2.2.2 The cloud core service layer

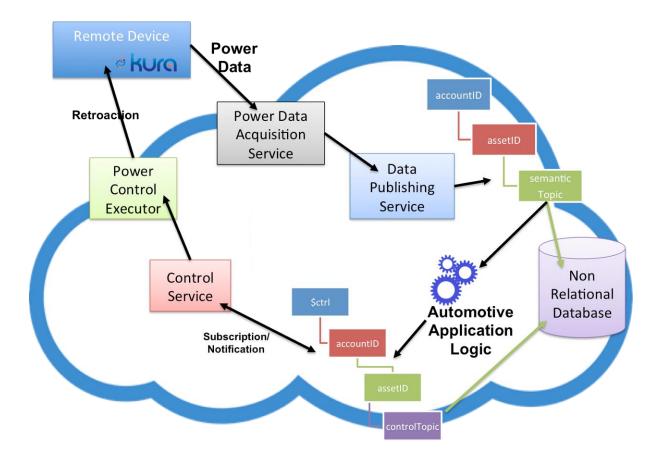

This section illustrates the cloud service abstraction layer, as far as concerned the data acquisition services, data publishing services and control services. These three aspects of the abstraction layer are strictly related to the management of the functional and extra-functional properties and, from the cloud perspective, represent the basic building blocks for the implementation of the automotive use case (UC2). These services represent the core of the cloud service abstraction.

The cloud abstraction layer is based on a publish-subscribe-notify paradigm that allows the separation of data producers and data consumers and the creation of one-to-many message distribution.

The cloud service abstraction layer introduces three types of services:

- data acquisition service,

- data publishing service,

- and control service.

Data acquisition services are intended for data acquisition from the field. Each functional and extra functional property must be described following the data model, illustrated in the previous section, and a specific data acquisition service must be defined and implemented. Focusing on a single property, the role of the data acquisition service is to send the data to the publishing service every time the data changes.

The data acquisition service owns the connection to the remote device (via Kura) and has full control on the connection parameters. The service adopts the field protocol available in the cloud platform (MQTT) to communicate with the remote device. Its design include the description of the field protocol both physical - serial vs I2C vs etc.- and logical - payload format used, frequency of information, etc.. Also the physical connection parameters - serial port, baud rate, or I2C address – can be configured.

Data publishing service is responsible for the information stored at cloud level. This service receives data from the data acquisition services and publish them. Once the data publishing service receive data referring to a specific topic, it filters, aggregates and publishes the received data, updating the corresponding topic. Also for this service a large set of parameters can be configured: triggering thresholds, publishing parameters, topics namespace, QoS, etc.. Publishing service design includes the topics namespace and the payload format used (metrics and payloads).

Finally, the control service is responsible for the actuation of commands (retroactions) on the cloud platform itself and on the remote devices (via Kura). In synthesis, this service receives generic command from the cloud and it dispatches them to a specific control executor that, in turns, is in charge to execute the command. Following the subscribe-notify paradigm, this service subscribes to a certain set of command (control topics) on the cloud. When it is notified about one of these commands, it converts the received control topic in a proper command and sends it to an executor. The control executor, in turns, is a software capable to manage and execute this specific command on the hardware of the remote device (i.e. via Kura the executor is capable to convert a command in a set of electrical signals for the I/O of the remote board). Control executors are bundles that run in the OSGi framework. As for the other core cloud

services, the control service can be configured regarding the enabled commands, the default arguments, the control executor, etc..

The cloud platform adopted in the automotive scenario (UC2) has been implemented following this design pattern. The following figure illustrates a possible implementation for extra-functional properties like the power consumption and the thermal profile of the remote device. Every further domain service follows the same design pattern.

Figure 18: An example of the cloud service abstraction.

The power and thermal functional properties are described in the cloud with a set of specific topics, which represent the reference to the power and thermal information stored in the cloud.

Two specific data acquisition services are introduced, in order to collect the data from the remote devices installed in the car: the power and thermal data acquisition services. Every time these services receive a power or thermal data, they send it to the data publishing service that, according with the application logic, elaborate it, aggregate it and finally publishes the data to the corresponding publishing topic.

A set of control executors has been developed, in order to perform the retroaction activities required by the logic of the automotive application. Every control executor subscribes to specific control topics and, when the cloud notifies it, it executes (via Kura) the code required to manage that particular event. In example, if the thermal status of the remote device is critical, the executor responsible to manage this situation can activate and reduce the frequency of the CPU, shut down certain on-board peripherals, etc..

#### 4 Services definition and characterization

#### 4.1 Open Virtual Platform used in use-cases 1 and 3

Open Virtual Platform<sup>TM</sup> (OVP<sup>TM</sup>) [6][5] by Imperas<sup>TM</sup> provides a complete simulation infrastructure for virtual platforms of embedded systems. OVP<sup>TM</sup> consists of three main components: OVP APIs to build own models and to create extensions for the simulator, a library that contains many open source processor and peripheral models that are free available and OVPsim<sup>TM</sup> which is the simulation kernel to execute these models. The partners of use-cases 1 and 3 use OVP<sup>TM</sup> to create and simulate virtual platforms of their execution platforms. Goal is to extend OVP<sup>TM</sup> by extra-functional models to be able to get timing and power information while simulating the execution platforms. Since OVP<sup>TM</sup> is only a functional simulator it is able to simulate the virtual platforms very fast, but has no accurate timing models for the provided models of processing elements. In that way, also no power models are available for them. However, with the offered APIs it is possible to get basic information about the simulated platforms to implement such models during simulation. Especially the *Innovative Cpu Manager* Interface (ICM) API gives access to the internal state of the simulated virtual platform. As a first step, OFFIS developed a timing model for the model of the Xilinx MicroBlaze, which is available in the OVPTM library, which uses the ICM API. To create an accurate timing model the mainly needed information needed are the executed instructions of the particular processing element. For this, the ICM API offers methods to register callback functions for specific events or memory address areas. One of these callbacks is the fetch callback.

After registering this callback, the committed function pointer "writeCB" is called for every

fetched instruction. Next to the callback function, a pointer to the specific processing element is needed as well as the low and high addresses of the instruction memory. Since the callback function needs to be static, the user is not able to access any non-static elements of its class. To overcome this issue the "icmAddFetchCallback" function has the parameter "userData" to commit any kind of data or class pointer (e.g. "this"). To get the pointer of the needed processing element it can be searched by its plaintext name by another ICM API function.

```

icmProcessorP icmFindProcessorByName(const char *name);

Example:

icmProcessorP cpu = icmFindProcessorByName("top.cpu1");

```

The function is called with a hierarchical name as a string with '.' as separator and returns a pointer to the named processing element. In the example, the whole platform is named "top" and the contained processing element "cpu1". The signature of the callback function is defined by the type "icmMemWatchFn" and is like follows.

```

static void fetchCallback(icmProcessorP processor

, Addr address

, Uns32 bytes

, const void *value

, void *userData

, Addr VA);

```

By using the address of the virtual instruction memory in the host machine and adding the given address offset the fetched operation code of the current instruction can be accessed. This operation code is given as parameter to the MicroBlaze timing model that returns the present system time in processed cycles. For getting the time in seconds, it has to be divided by the configured processor's frequency. For updating the simulation time, the ICM API has a function as well.

```

Bool icmAdvanceTime(icmTime time);

(With: typedef long double icmTime; // Current simulator time in seconds)

```

The simulation time is updated continuously by giving the computed time of the timing model to this function in seconds as a double value after each instruction fetch and timing model call. Because of that, OVP<sup>TM</sup> gets a quasi-cycle accurate behaviour. More information about the timing model is provided in [5].

Next to the used functions for the timing model, the ICM API provides more helpful ones to analyse the current state of the virtual platform. With the following function, it is also possible to get the current simulation time of the virtual platform.

As well as the current counter for executed instructions of each processor model:

```

uint64_t icmGetProcessorICount(icmProcessorP processor);

```

For accessing the processor's registers to get further information about the present state the ICM API has special read and write functions.

In addition, these functions need a pointer to the processing element the register belongs too. The register names can be found in the documentations of the particular virtual processor. The

character buffers are used for getting and setting the register value. Further functions for setting and getting the present program counter of the processing element are available.

If the next instruction is needed the processor pointer and the present program counter can be used to get its address as return value of the following function.

```

Addr icmGetNextInstructionAddress(icmProcessorP processor, Addr thisPC);

```

Like the mentioned fetch callback also callbacks for read and write accesses of memory areas and busses are available.

```

void icmAddReadCallback(icmProcessorP processor

, Addr lowAddr

, Addr highAddr

, icmMemWatchFn writeCB

, void *userData);

void icmAddWriteReadCallback(icmProcessorP processor

, Addr lowAddr

, Addr highAddr

, icmMemWatchFn writeCB

, void *userData);

void icmAddBusReadCallback(icmBusP bus

, icmProcessorP scope

, Addr lowAddr

, Addr highAddr

, icmMemWatchFn writeCB

, void *userData);

void icmAddBusWriteCallback(icmBusP bus

, icmProcessorP scope

, Addr lowAddr

, Addr highAddr

icmMemWatchFn writeCB

void *userData);

```

The usage of these callbacks is in basic the same as of the fetch callback. The observed address range has to be determined and the callback function has to be announced and implemented. In additional the bus callbacks need a reference (as pointer) to the observed bus.

#### 4.2 Extension of OVP scenario with SystemC models

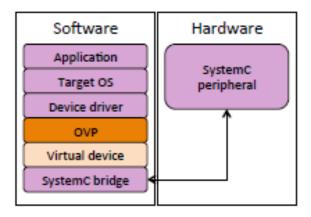

The OVP virtual platform is useful until standard components are used or new components (e.g., peripherals) are implemented by using OVP native API. Unfortunately, most of behavioural models found in the industrial context are written in SystemC and their translation could be time-consuming and error-prone thus limiting the adoption of OVP. OVP provides a mechanism to wrap the CPU model and OVP peripherals into a SystemC design. However, in this project we investigated also another approach.

In this project, the HW/SW co-simulation architecture depicted in Figure 19 is proposed by EDALab [7]. Similarly to the approaches proposed in [8][9], it reflects the traditional operating system based stack where software applications interact with hardware peripherals through device drivers. The target platform, where software applications run, is emulated by using OVP and it is connected to a SystemC hardware peripheral through a virtual device, a SystemC bridge and a device driver for the target operating system. The virtual device, connected to the bus of the virtual platform, acts as an interface between the SystemC simulator and the OVP virtual platforms. The virtual device code depends on the APIs exported by OVP for modelling new devices. The SystemC bridge consists of a set of functions that allow the communication with SystemC. The bridge is compiled as a C library linked to the implementation code of each virtual device, thus it is independent on the selected virtual platform (e.g., it can be the same for both a QEMU-based and an OVP-based architecture). Finally, a device driver must be developed for the target operating system to use the hardware peripheral. Its code is clearly independent on the selected virtual platform and it does not need to be changed when it is moved to the actual platform. This approach allows a rapid interchange from an OVP-based SystemC co-simulation and vice versa, since only the virtual device must be re-coded moving from an OVP virtual platform. Further details about the virtual device and the SystemC bridge are reported in the following. The implementation of the device driver is not reported since it does not depend on the proposed co-simulation architecture, but only on the operating system.

Figure 19 Co-simulation architecture.

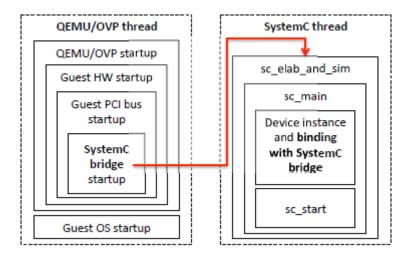

The core of SystemC bridge is a C++ class implementing a singleton design pattern that exposes a set of APIs towards the virtual device for interfacing with SystemC. Moreover, it manages the communication protocol and the synchronization mechanism between OVP and SystemC. Since OVP is written in C, the bridge wraps the SystemC APIs through a set of C functions included in a library which is statically linked to the SystemC runtime library. The OVP virtual platform initially calls a function implemented in the bridge to start the SystemC simulator. Until the SystemC runtime is operative, the virtual platform is blocked to prevent its premature requests to the hardware device. Differently from [8], the SystemC simulator is executed as a

separate thread inside the same process where the OVP simulator is executed (Figure 20), such that the communication between the two worlds is based on shared memory and thread synchronization primitives. This prevents the use of expensive interprocess communication mechanisms (like sockets). Then, the starting routine of the thread launches the SystemC sc\_main() function where the following steps are executed:

- instantiation and initialization of the SystemC device to be connected to the bridge; in particular, input and output ports of the device are registered in the bridge;

- unlocking of the semaphore that is blocking the virtual platform;

- starting of the SystemC simulator.

Figure 20 Start-up of the co-simulation between OVP and SystemC.

A device can be made visible to the OVP virtual platforms by implementing a virtual device. Its implementation depends on the kind of adopted bus. The creation of a virtual device is tightly coupled to the API provided by the virtual platform. The implementation of the virtual device in OVP is split in two parts: the device and the intercepted functions. The device consists of a C application with a standard main function. It first executes a set of initialization activities (SystemC simulation, bus configuration header, bus memory regions); then it connects the bus configuration port (necessary to read the bus configuration header) and the master bus. Finally, it registers some call back functions that are triggered at each read/write operation from/to the bus I/O port regions. The interaction between the SystemC bridge and the virtual device is performed by means of a set of intercepted functions. The Peripheral Simulation Engine intercepts such functions through the Application Binary Interface (ABI), which specifies size, layout and alignment of data types, how an application should make a system call to the operating system, and the calling conventions (how arguments of a function are passed, and how the return value is retrieved). In particular, there is an intercepted function for reading from the SystemC device and one for writing to the SystemC device. Their role consists in calling the corresponding sc\_ioport\_read() and sc\_ioport\_write() of the SystemC bridge.

#### 4.3 Use-case 1: Unmanned Aerial Vehicle

Services in the Unmanned Aerial Vehicle use-case are provided by the Xilinx Zynq platform hardware components, its Board Support Package (BSP) or Hardware Abstraction Layer (HAL), its Operating System Layer, the corresponding virtual platform for simulation, and tools for trace processing to extract and control properties. In CONTREX, these services are used for

- 1. Mapping and implementation of the Mixed-Critical applications on the provided target platform (Xilinx Zynq)

- 2. Introspection and reference for extra-functional traces (e.g. power and temperature over time)

- 3. Control of extra-functional properties (e.g. adaptive QoS, power and temperature management)

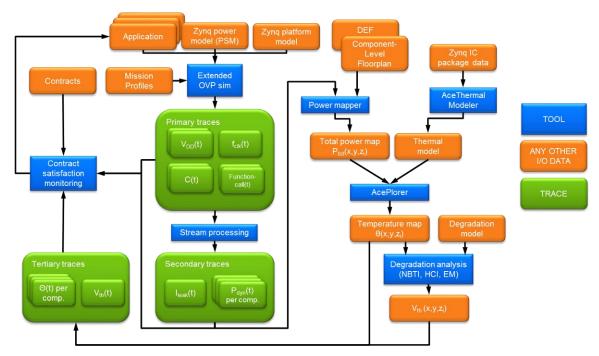

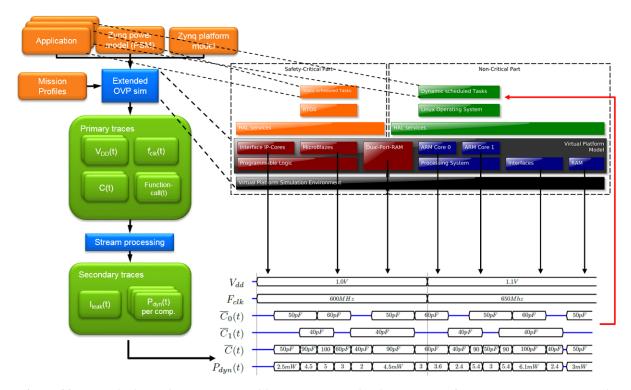

Figure 21: Overall CONTREX power, temperature and degradation analysis flow.

In use-case 1 we want to analyse the extra-functional properties power, timing and temperature of a safety-critical flight control algorithm and a mission-critical payload processing (i.e. high performance image processing) running together on the Xilinx Zynq platform, as described in s section 2.3. As described in D3.1.1, the overall CONTREX power, temperature and degradation analysis flow, as shown in Figure 21, enables tracing extra-functional properties like supply voltage, clock frequency or switched capacity per hardware platform component (processor, memory, bus, peripheral) over time. For establishing a cause and effect relationship, identification of the Application, Task, Function state and its associated context over time need to be traced and associated with the observed extra-functional properties.

Figure 22: Establishing a link and traceability between applications and platform hardware component's extra-functional traces through services.

Figure 22 shows the goal of establishing a link and traceability between applications and platform hardware component's extra functional traces. For enabling a correlation of application activity and status of the platform components with the power over time trace per component, a traceable service model is proposed.

In a first instance, we analysed extra-functional properties on a task level granularity. This can be refined to a function level, if required.

In our service model, an application is represented by a set of periodic and sporadic tasks. Tasks can communicate and synchronize through FIFO and handshake communication channels, called Shared Objects as generalization in the following. We define a finite set of Applications  $A_i$  with

- criticality level Li

- set of Tasks Ti

- set of Shared Objects Si

Each Task tjin T<sub>i</sub> is defined by (P<sub>j</sub>, D<sub>j</sub>, SI<sub>j</sub>, L<sub>j</sub>) with

- period (minimum arrival time) P if periodic task and P =

- deadline D

- ports to Shared Object Interfaces SI in Si.I

- criticality level L

Each Shared Object S<sub>i</sub> consists of

- a set of Interfaces Ii with methods mj in ik in Ii(let Mi be the union of all methods in Ii)

- a set of side effect free Guards Gi

- a set of guarded methods GMi in Mi x Gi

- implementing all interfaces methods Mi

- a shared resource access arbitration policy

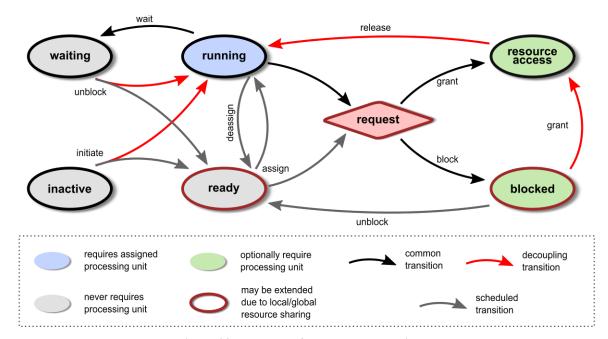

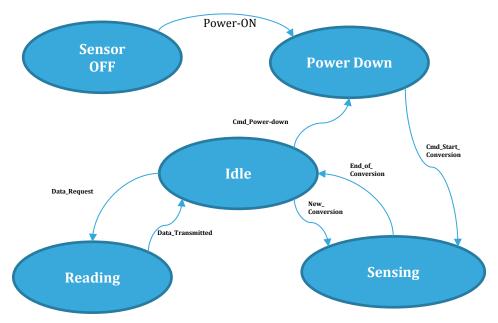

As shown in Figure 23, each task can be in the state inactive (not initially assigned to a processing element), ready (waiting to be executed on a statically or dynamically assigned processing element), running (currently executing on its assigned processing element), waiting (preempted by the task scheduler), blocked (waiting for shared resource access), and resource access (accessing a shared resource). When no application or operating system task is running, an idle task is running on each processing element.

Figure 23: Example of a task state machine.

In our use-case, a task consists of at least one function and/or communication of a task with other tasks or the environment of the system. To align and combine the extra-functional properties per processing unit over time in line with tasks we needed to represent state of each task together with the system time. The overall system time has been provided by the virtual platform simulator's reference time while the current state of the tasks has been represented by an event-system denoting the transition or transition events of the described task state machine.

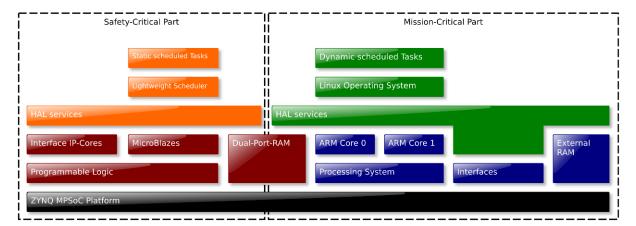

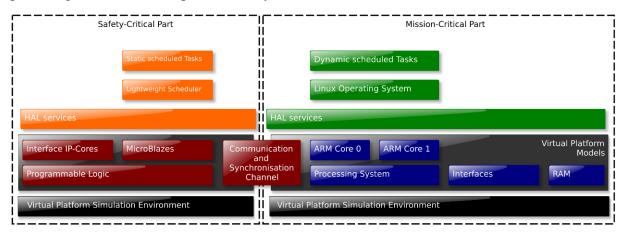

Figure 24 and Figure 25 show the structure of the different layers of the real hardware prototype system and the virtual platform of the Xilinx Zynq. All service layers above the hardware layer are similar (these are the HAL-, OS-/Scheduler- and Task-Layers). The main differences are in the base layers. In the real hardware prototype system we have the actual Xilinx Zynq MPSoC with the Hardware processing elements, memories, communication elements and peripherals either implemented in the ASIC or the FPGA partition. In the virtual platform model, these layers are represented by corresponding OVP simulation models.

Figure 24: Overview of Layers in real system of use-case 1.

Both, the hardware and the virtual platform can be divided into a safety-critical (left side in Figure 24 and Figure 25) and a mission-critical part (right side in Figure 24 and Figure 25). While the safety-critical part computes the flight algorithms, the mission-critical part performs the payload processing, e.g. video processing. As shown in the figures the safety-critical part uses the programmable logic of the MPSoC and the mission-critical part uses the ARM processing system. While we analysed the whole MPSoC we needed the availability of providing services in both parts of the system.

Figure 25: Overview of layers in virtual platform of use-case 1.

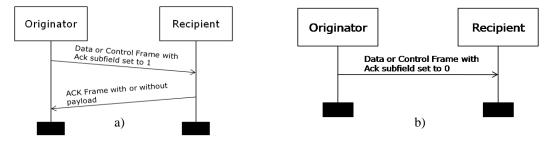

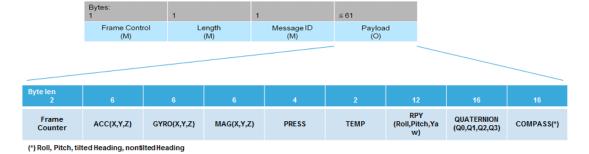

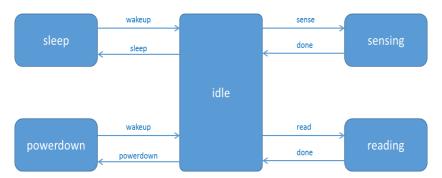

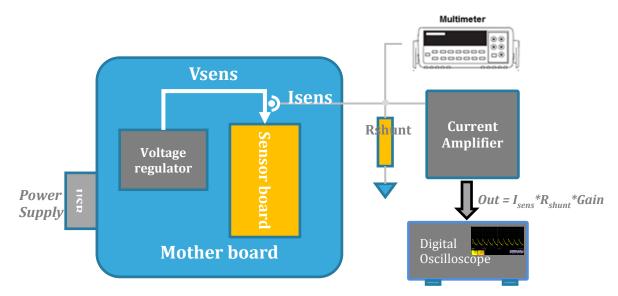

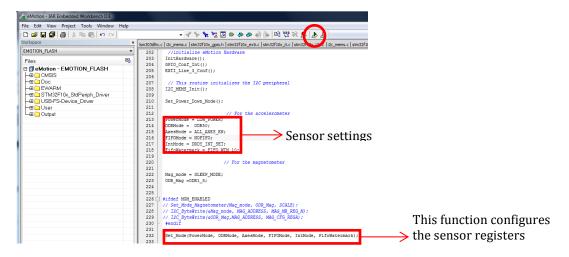

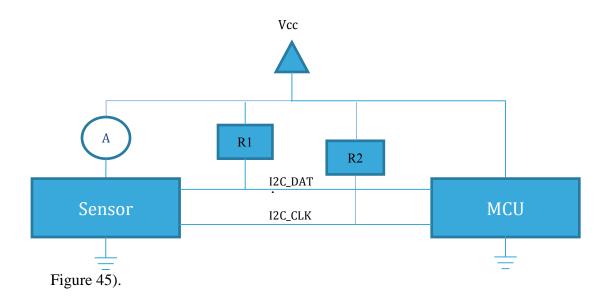

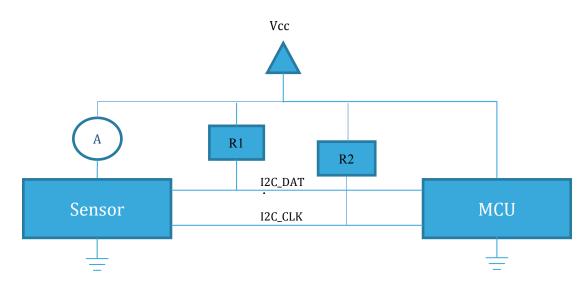

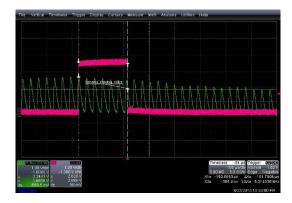

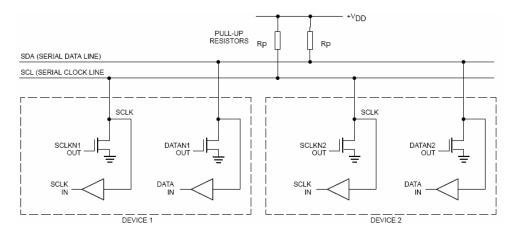

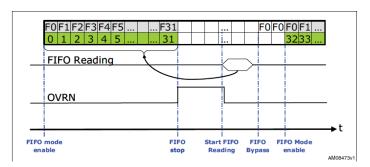

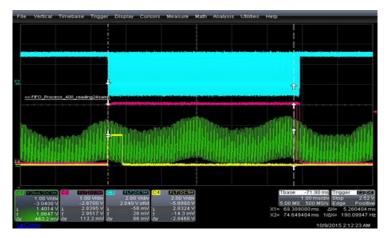

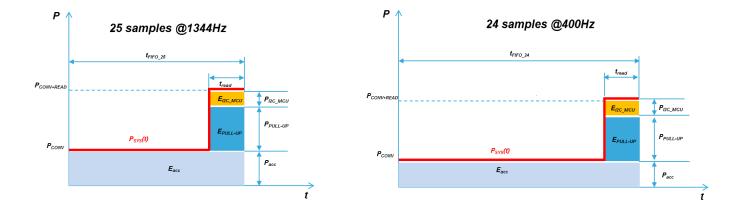

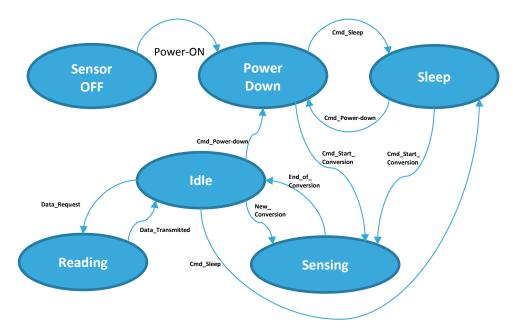

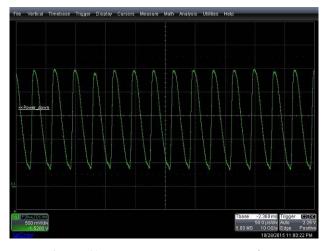

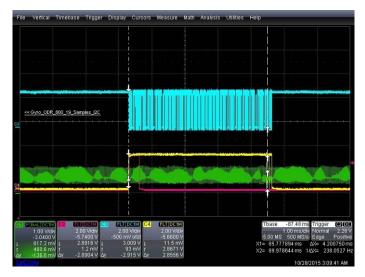

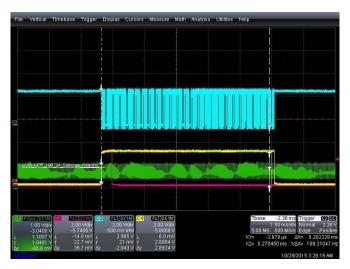

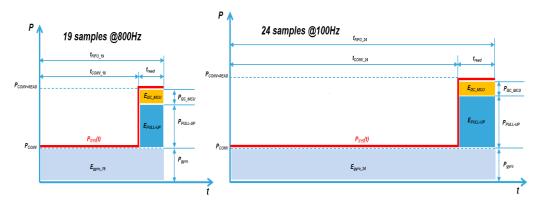

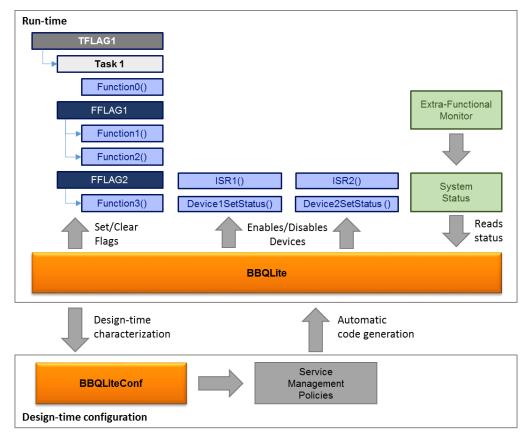

In our first approach for analysing the extra-functional properties on task level we need for each task: start time, end time and also the times of disruption through other tasks or communication and shared resource accesses. Like mentioned before, timers of the processing elements have be used via the HAL services to get the present system time. For getting the present state of a task, a task state machine can be used like shown in Figure 23. The emitted events of the statemachine together with the time can be used to synchronize the tasks and the measurements of the extra-functional properties of the real system. As follows these services are located in the top layer of Figure 24 and Figure 25, where the tasks are located.