#### Public

**FP7-ICT-2013- 10 (611146) CONTREX**

# Design of embedded mixed-criticality CONTRol systems under consideration of EXtra-functional properties

Project Duration 2013-10-01 – 2016-09-30 Type IP

| Cantroy         | WP no. | Deliverable no. | Lead participant |

|-----------------|--------|-----------------|------------------|

| <b>Cont</b> rex | WP6    | D6.3.4          | ECSI             |

# **CONTREX Dissemination Report (Final)**

Prepared by Adam Morawiec (ECSI)

Issued by **ECSI**

Document Number/Rev. **CONTREX/ECSI/R/D6.3.4/1.0**

Classification CONTREX Public

Submission Date **2016-09-30**

Due Date **2016-09-30**

Project co-funded by the European Commission within the Seventh Framework Programme (2007-2013)

© Copyright 2016 OFFIS e.V., STMicroelectronics srl., GMV Aerospace and Defence SA, Vodafone Automotive SpA, Eurotech SPA, Intecs SPA, iXtronics GmbH, EDALab srl, Docea Power, Politecnico di Milano, Politecnico di Torino, Universidad de Cantabria, Kungliga Tekniska Hoegskolan, European Electronic Chips & Systems design Initiative, ST-Polito Societa' consortile a r.l., Intel Corporation SAS.

This document may be copied freely for use in the public domain. Sections of it may be copied provided that acknowledgement is given of this original work. No responsibility is assumed by CONTREX or its members for any application or design, nor for any infringements of patents or rights of others which may result from the use of this document.

# **History of Changes**

| ED.       | REV. | DATE       | PAGES | REASON FOR CHANGES                    |

|-----------|------|------------|-------|---------------------------------------|

| SR        | 0.1  | 2016-09-30 | 26    | Initial version                       |

| KG        | 0.2  | 2016-09-30 | 33    | Added OFFIS contribution              |

| NK        | 0.3  | 2016-09-30 | 35    | KTH updates                           |

| FH        | 0.4  | 2016-09-30 | 42    | UC update                             |

| DQ        | 0.5  | 2016-09-30 | 44    | EDALab update                         |

| JF        | 0.6  | 2016-09-30 | 44    | Intecs update                         |

| KG,<br>AA | 0.7  | 2016-09-30 | 48    | OFFIS and iXtronics update            |

| MP,<br>GP | 0.8  | 2016-09-30 | 51    | POLIMI and POLITO contributions added |

| KG        | 0.9  | 2016-09-30 | 51    | CONTREX website statistics added      |

| KG        | 1.0  | 2016-09-30 | 51    | Final release                         |

# **Contents**

| 1 | Int  | roduction                                                              | 4  |

|---|------|------------------------------------------------------------------------|----|

| 2 | Dis  | ssemination Impact Measures                                            | 5  |

|   | 2.1  | Target Audience                                                        | 5  |

|   | 2.2  | Measures of Efficiency                                                 |    |

| 3 | Co   | nsortium-Level Dissemination Activities                                | 7  |

|   | 3.1  | CONTREX Website                                                        | 7  |

|   | 3.2  | ESLsyn Conference 2015                                                 | 9  |

|   | 3.3  | DAC Workshop 2015: System to Silicon Performance Modeling and Analysis | 10 |

|   | 3.4  | FDL 2015                                                               | 11 |

|   | 3.5  | DASIP 2015                                                             | 12 |

|   | 3.6  | DVCon Europe Conference & Exhibition 2015                              | 13 |

|   | 3.7  | DATE Workshop 2016                                                     | 16 |

|   | 3.8  | DAC Workshop 2016: System to Silicon Performance Modeling and Analysis | 18 |

|   | 3.9  | FDL 2016                                                               | 22 |

|   | 3.10 | CONTREX Book                                                           | 23 |

| 4 | Par  | rtner-Level Dissemination Activities                                   | 25 |

|   | 4.1  | OFFIS                                                                  |    |

|   | 4.2  | STMICROELECTRONICS, ST-I                                               | 31 |

|   | 4.3  | GMV AEROSPACE AND DEFENCE SA UNIPERSONAL                               | 31 |

|   | 4.4  | VODAFONE AUTOMOTIVE                                                    | 31 |

|   | 4.5  | EUROTECH                                                               | 32 |

|   | 4.6  | INTECS                                                                 | 33 |

|   | 4.7  | iXtronics GmbH                                                         | 34 |

|   | 4.8  | EDALab                                                                 | 35 |

|   | 4.9  | INTEL                                                                  | 38 |

|   | 4.10 | POLITECNICO DI MILANO                                                  | 38 |

|   | 4.11 | POLITECNICO DI TORINO                                                  | 42 |

|   | 4.12 | UNIVERSIDAD DE CANTABRIA                                               | 43 |

|   | 4.13 | KUNGLIGA TEKNISKA HOEGSKOLAN                                           | 49 |

|   | 4.14 | ST-POLITO                                                              | 50 |

| 5 | Re   | lations to Other Projects                                              | 51 |

#### 1 Introduction

This document summarizes all dissemination activities that were undertaken by the CONTREX project consortium as a whole and by each individual partner of the consortium in the last period of the project execution (it covers the period from the last dissemination report – period 1).

From the very beginning the CONTREX consortium initiated and carried out dissemination activities that were focused on increasing the visibility of project results, impact the most important standardization activities and industry adoption and in general gaining a world-wide interest about its progress and results.

This second phase was also used to work closely with running R&D projects with similar objectives and to establish common actions with them. Very concrete activities were done together with OpenES, and within the Mixed-Critacality Cluster with PROXIMA and DREAMS projects.

Having the above high-level objectives in mind a common presentations and posters were done at the most prominent conferences in the domain: DATE, FDL, DASIP, ESLsyn to name the most important.

One of the most important activities of CONTREX, in which several partners of the consortium were pro-actively involved was a series of very successful Forum Workshop at the DAC Conference (2014, 2015 and 2016) on System to Silicon Performance Modelling and Analysis. The success of this initiative was proven by the growing participation as well as by the number of top electronic companies' representatives participating to these events.

These initial activities created a very good basis for collaboration with other projects and for establishing relations with the community (research partners and potential industrial customers) of the CONTREX results.

## 2 Dissemination Impact Measures

In order to control the efficiency of all dissemination actions, the consortium has implemented the mechanism enabling to collect progressively the following information on each specific dissemination activity undertaken by the whole consortium or by group of partners or each partner separately. This will contain:

- Event name, authors, dates and place;

- Presentation and paper (pdf, bib);

- Target audience (listed in the Table 1 below)

- Measures of impact are the collected information associated to each scientific publication in order to maintain the traceability of the concerned paper. The measures of impact are listed in Table 2 (below).

This information will enable the consortium to understand impact of each activity, to take corrective actions or improve the dissemination.

#### 2.1 Target Audience

For each dissemination action, the consortium will define the addressed target audience (initially planned and effectively participating in the training) according to the following classification:

| Туре                                     | Domain                        | Main Targets                                                                                     |

|------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------|

| System Companies (Europe, WW)            | Aeronautics /<br>Aerospace    | EADS / Airbus / Astrium / Thales / ThalesAlenia / Selex / GMV                                    |

|                                          | Automotive                    | OEMs                                                                                             |

|                                          | Communication /<br>Networking | Ericsson, NSN, Axis                                                                              |

| Application developers                   | Aeronautics                   | Thales, ThalesAleniaSpace, Astrium                                                               |

| Subsystem Providers (Tier 1, Subsystems) | Aerospace                     | Thales Communication                                                                             |

|                                          | Automotive                    | Bosch, Continental, Valeo, Magneti Marelli, Melexis,                                             |

| Microelectronics                         | All domains                   | ST, Infineon, Intel, Freescale, Renesas                                                          |

| IP/VIP Providers                         | All domains                   | ARM, Imagination, Synopsys IP, Cadence IP                                                        |

| EDA / Tools                              | System / HW / SW              | Magillem, Calypto, Agilent, NEC, Intel<br>CoFluent, Big 3, Mirabilis, Wind River,<br>Green Hills |

| Research                                 | System / HW / SW              | Relevant research / university (all Europe)                                                      |

|                                          |                               |                                                                                                  |

# 2.2 Measures of Efficiency

In order to estimate how useful the dissemination actions were, the CONTREX consortium will provide some measures with each training activity:

| Dissemination<br>Degree                   | Appropriate<br>Means                                              | Measures of Success                                                                       | Qualification                                                                                                           |

|-------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| General<br>awareness                      | Domain-<br>specific<br>conferences                                | # Participants # Contacts established + qualification Follow up after the event / outcome | <ul> <li>Industry / Academia</li> <li>Research, management, engineering</li> <li>Info exchange / Cooperation</li> </ul> |

|                                           | Workshops, seminars                                               | # Participants Participant profile                                                        | <ul> <li>Industry / Academia</li> <li>Industry type, mngmt, engineering, research</li> </ul>                            |

|                                           | Articles                                                          | Publication type<br>Estimated reach<br>Citations                                          | <ul> <li>Conf paper, journal, press article</li> <li>Conf participation, edition</li> </ul>                             |

| Education on concepts / solutions / tools | Training sessions                                                 | # Participants Participant profile Follow-up                                              | <ul><li>Industry:<br/>management/engineering</li><li>Academia</li></ul>                                                 |

|                                           | Training material (e.g. web courses, videos)                      | # Downloads<br>Geographical regions<br>Domains .com, .edu                                 |                                                                                                                         |

|                                           | Hands-on<br>Demos                                                 | # Participants<br>Follow up                                                               | <ul> <li>Industry / Academia</li> <li>Industry type, mngmt, engineering, research</li> </ul>                            |

| Standardisation                           | <ul><li>Cooperation<br/>in std bodies</li><li>Workshops</li></ul> | # Proposals<br>submitted<br># Proposals adopted<br>Workshop success                       | Overall impact of proposal on final standard                                                                            |

| Tool Adoption                             | Delivery /<br>Install<br>Training                                 | # Installations / licenses / users # Trainings # Inquiries / maintenance / applications   | <ul> <li>Usage: evaluation / production test / production, large deployment</li> <li>Interactive / exchange</li> </ul>  |

#### 3 Consortium-Level Dissemination Activities

#### 3.1 CONTREX Website

The CONTREX project website is available at <a href="http://contrex.offis.de">http://contrex.offis.de</a>

Figure 1: Screenshot of the CONTREX website

The Website provides information about the project, project related news, dissemination material, contact information and the required legal information.

The menu website of the website is as follows:

- Main

- Project

- Objectives

- Work Packages

- Consortium

- o News

- Dissemination

- Scientific Publications

- Events

- Deliverables

- Training

- European Mixed-Criticality Cluster

- o Contact

- Imprint

- o Impressum

Access statistics have been collected starting from April 2014.

Figure 2: Number of Sessions over time

Figure 3: Advanced session statistics

|     | Country        | Sessions | % Sessions |

|-----|----------------|----------|------------|

| 1.  | Russia         | 1,697    | 18.51%     |

| 2.  | United States  | 1,694    | 18.48%     |

| 3.  | (not set)      | 964      | 10.52%     |

| 4.  | Germany        | 885      | 9.66%      |

| 5.  | Italy          | 478      | 5.21%      |

| 6.  | United Kingdom | 388      | 4.23%      |

| 7.  | Spain          | 294      | 3.21%      |

| 8.  | France         | 294      | 3.21%      |

| 9.  | China          | 217      | 2.37%      |

| 10. | Japan          | 154      | 1.68%      |

Figure 4: Session breakdown per country

#### 3.2 ESLsyn Conference 2015

**Date & Location**: June 10-11, 2015

San Francisco, CA, USA (co-located with DAC)

**Organizer**: ECSI

The still increasing need for enhanced productivity in designing highly complex electronic systems drives the evolution of design methods beyond the traditional approaches. To cover functional and especially non-functional requirements should be checked on a design model and covered during the design process.

Virtual prototyping, design space exploration and system synthesis with the goal of optimized and functionally correct product implementations are needed for designing both HW and SW parts. The system design teams expect newer and more efficient methods and tools supporting better management of the design complexity and reduction of the design cycle time all together, breaking the trend to compromise on the evaluation of various design implementation options. Designing at higher levels of abstraction is a viable way to better cope with the system design complexity, to verify earlier in the design process and to increase code reuse.

ESLsyn is a forum to discuss automated system design methods that enable efficient modeling of systems to provide the capability to synthesize HW platforms and embedded software with particular aspects related to synthesis. The main aim of the conference is to bring research institutions and industrial partners in the domain of ESL synthesis closer together by informing practitioners of the latest theoretical results, and challenging theoreticians with complex industrial problems. ESLsyn wants to provide a discussion platform for experience exchange between providers of synthesis technology and industry users, but also will be a forum to discuss scientific concepts and paradigms for the future evolution of synthesis methods. It therefore welcomes both academic and industrial participants.

The organizers are grateful to Forrest Brewer, Achim Rettberg, Yuko Hara-Azumi and Benjamin Carrion-Schafer for presenting their keynote and invited talks at ESLsyn 2015.

The organizing committee was also very grateful to the very large group of people that made this all happen: The 27 members of the technical program committee and their sub-reviewers. Finally, ESLsyn enjoyed the valuable support from the IEEE Council on Electronic Design Automation (CEDA).

| Impact Assessmen | Impact Assessment                                                                 |  |  |

|------------------|-----------------------------------------------------------------------------------|--|--|

| Target Audience  | Industry and academia                                                             |  |  |

|                  | Total participation: 24                                                           |  |  |

|                  | Industry: 10                                                                      |  |  |

|                  | University/Research: 14                                                           |  |  |

| Participants     | C-Lab, Calypto, Cornell University, Escuela Técnica Superior de Ingeniería        |  |  |

|                  | Informática, Hella, National University of Computer and Emerging Sciences -       |  |  |

|                  | Lahore, NEC, OFFIS, Politecnico di Torino, Tokyo Institute of Technology, U Lund, |  |  |

|                  | U Oldenburg, UC Santa Barbara, Université Nice Sophia Antipolis, Hong Kong        |  |  |

|                  | Polytechnic University                                                            |  |  |

| Comments         | Presentation of CONTREX technical poster                                          |  |  |

|                  | Discussion around the poster, presenting the standardisation context              |  |  |

# 3.3 DAC Workshop 2015: System to Silicon Performance Modeling and Analysis

**Date & Location**: June 7, 2015 – San Francisco, USA **Organizer**: ECSI

#### **Rationale for this year edition:**

The integration of heterogeneous electronic systems composed of SW and HW requires not only a proper handling of system functionality, but also an appropriate expression and analysis of various extra-functional properties: timing, energy consumption, thermal behavior, reliability, cost and others as well as performance aspects related to caching, non-determinism, probabilistic effects.

The workshop addresses cross-domain aspects related to the design and verification framework covering methodology, interoperable tools, flows, interfaces and standards that enable formalization, specification, annotation and refinement of functional and extrafunctional properties of a system. Special emphasis will be given to formalization and expression of *power*, *temperature*, *reliability*, *degradation and aging*.

Several research and industry efforts address (parts of) the problem. However, there is a need for community-wide cooperation to establish a holistic vision on extra-functional property treatment, and to agree on research and development directions and further on validation of applicable solutions and standardization.

This event will support collaboration between main actors from system and microelectronics industry, EDA and research.

The workshop is inviting submissions of short abstracts industrial and scientific work in progress and practical solution and experiences.

Figure: The System-to-Silicon Performance workshop audience.

| Impact Assessmen | it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target           | System companies, Microelectronics companies, Research centres, Universities,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                  | Standardisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Audience         | Aachen University of Technology, Airbus, Analog Devices, Inc., Broadcom Corporation, Cadence, Carnegie Mellon University, Chapman Consulting, Credit Suisse, CSR, CST AG, D. E. Shaw Research, DOCEA Power, Ecole Centrale de Lyon, EDXACT SA, ETRI, Faraday Technology Corp., FAU Erlangen-Nürnberg, Fraunhofer IIS, Friedrich-Alexander-Universität Erlangen-Nürnberg, Fudan University, Huawei Technologies Co., Ltd., IBM Corporation, Imagination Technologies Ltd., imec, Imperial College London, Infineon Technologies AG, Intel Corporation, iRoc Technologies, L-3 Communications, LEAT/CNRS, Leibniz University of Hannover, LG Electronics, Library Technologies, Inc., MediaTek, Inc., Mentor Graphics Corporation, Microchip Technology, Inc., Micron Technology, Inc., National Security Research Institute, National Taiwan University of Science and Technolo, National Tsing Hua University, NC State University, Northeastern University, NVIDIA Corporation, Olympus, Oracle Corporation, Osaka University, Oticon A/S, Panasonic Corporation, Politecnico di Milano - DEIB, Qualcomm, RWTH Aachen University, Samsung Electronics Co., Ltd., Sasken Communication Technologies Ltd., Semiconductor Manufacturing International Corp., Seoul National University, Silvaco, Sk hynix, Sonics Inc., Spin Transfer Technologies, Stanford University, STMicroelectronics, Synopsys, Inc., Technische Universität München, The Aerospace Corporation, Toshiba Corporation, Trajectory Design Automation Corp., TSMC, TU Dortmund, UC Irvine, University Bremen, University of British Columbia, University of California at San Diego, University of California, Irvine, University of Texas at Austin, University of Virginia, Utah State University, Virginia Tech, Western Digital Corporation, |

| Participation    | <ul> <li>Xilinx, Inc.</li> <li>Participants total: 123 registered, 60+ present constantly in the room</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| profile          | 59% Industry (!)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| prome            | 39% Academia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  | 2% others (e.g. consulting)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Impact           | Presentation of CONTREX approach to the very wide audience, mostly from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  | industry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  | Collaboration with related projects: PAPP, CRAFTERS, OPENES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### 3.4 FDL 2015

**Date & Location**:

September 13-15, 2015 – Barcelona, Spain

**Organization**: ECSI

Forum for Design Languages (FDL) is a well established international forum devoted to dissemination of research results, practical experiences and new ideas in the application of specification, design and verification languages to the design, modeling and verification of integrated circuits, complex hardware/software embedded systems, and mixed-technology systems. Several technical areas have been addressed:

• *UML and MDE for Embedded System Specification & Design (UMES)* – model driven methods, mostly based on the Unified Modeling Language, increasingly support semiformal methods for system level design of complex embedded systems including highly programmable platforms and heterogeneous Systems-on-Chip.

- Language Based System Design (LBSD) addresses language-based modeling and design techniques for simulation, debugging, transformation, and analysis of hardware/software embedded systems.

- Assertion Based Design, Verification & Debug (ABD) welcomes research

contributions, tool demonstrations, reports on standardization activities and effective

applications in all aspects of innovative property expression and processing, with an

emphasis on frontier design levels, verification, automatic synthesis and mechanized

design aids.

- Embedded Analog and Mixed-Signal System Design (EAMS) addresses design, modeling and verification of analog/mixed-signals systems.

Among industrial and academic participants, discussions on CONTREX project occurred during poster sessions and conference special sessions. CONTREX project had an accepted publication at FDL2015 conference, also a project poster was presented to give background information to the attendees on the project approach and results.

CONTREX presented (with the main implication of OFFIS and ECSI) technical posters displayed during the coffee/lunch breaks and during the poster session for discussion with all participants.

| Impact Assessmen | nt                                                                                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Audience  | Academia and industry in system design, microelectronics, embedded systems 50-60 participants HW platform + HdS community: Research partners + Infineon, Bosch, Continental, Cadence, Mentor Graphics, Synopsys      |

| Impact           | Established valuable contacts with industry partners: Continental, NXP, ST, Infineon                                                                                                                                 |

| Comments         | <ul> <li>Several valuable contacts with researchers working on system design methodology and design flows</li> <li>Specific aspects like modelling, verification in the design methodology were addressed</li> </ul> |

#### 3.5 DASIP 2015

#### **Date & Location:**

October 8-10, 2014 – Madrid, Spain September 23-25, 2015 – Cracow, Poland

**Organization**: ECSI

The conference globally addresses the context of hardware design of complex applications for image and control processing, with the goal of presenting the latest results in the domain of design and architectures along several axes: design methods and tools, development platforms, architectures and technologies, use-cases and applications as well as smart sensing systems.

The Special Sessions have the purpose of introducing the DASIP community to relevant and new hot topics that are for sure of great interest for the audience of the conference, such as special arithmetic for signal and image processing, visual scene analysis for multi-core, many-core and hybrid architectures, or just-in-time compilation of architectures for image processing.

The Demo Night presented collaborative projects featuring timely topics on hardware platforms, prototypes, design frameworks, tools and more. We hope the format of demo night, held together with some refreshments, helps to maximize the interaction with the presenters. Also, the program has been defined to cover large number of domains. We also hope that all other sessions, with oral presentations and posters will lead to a large number of exchanges between attendees, helping not only on enhancing knowledge and research skills, but also on improving your links with other groups or individuals.

CONTREX took benefit of the event to present system design methodology relevant to the development of efficient architectures of complex signal and image processing that require analysis of various performance metrics to meet system requirement. Poster has been presented during several poster sessions all over the conference days.

| Impact Assessmer | nt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Audience  | Academia and industry in system design, microelectronics, embedded systems 60-80 participants:  EPFL, INRIA, Technische Universität Darmstadt, Åbo Akademi Universitu, Polytech'Nantes, Technische Universität München, Instituto de Microelectronica de Sevilla, Kalsruhe Institute of Technology, DGIST, Universita di Bologna, Tampere University of Technology, University of Twente, Polytechnique Montréal, Fraunhofer IOSB, Technical University of Denmark, INSA Rennes, AGH University of Science and Technology, Indian Institute of Technology, Bombay, E.T.S.I. INFORMÁTICA, IRISA, Leibniz Universität Hannover, Universaité Bretagne Sud, Université Paris Sud, University of the Basque Country, LIRMM, University of Arkansas, Universita degli Studi di Cagliari, ENSTA-Paristech, AGH University of Science and Technology, Tima Laboratory, Universidad CEU San Pablo, Instituto de Microelectronica de Sevilla, UPV, University of Sassari, Universidade do Porto, Centro de electronica Industrial. |

| Comments         | <ul> <li>Several valuable contacts with researchers working on system design methodology and design flows</li> <li>Specific aspects like performance analysis in the context of design methodology were discussed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# 3.6 DVCon Europe Conference & Exhibition 2015

Nov 11-12, 2015 Munich, Germany Date & Location: November 11-12, 2015

Munich, Germany **Organizer**: ECSI

**DVCon Europe** is a technical conference in Europe targeting the application of standardized languages, tools, and methodologies for the design and verification of electronic systems and integrated circuits. Hosted by <u>Accellera Systems Initiative</u>, the format of DVCon Europe is

similar to the successful <u>DVCon United States</u> conference held for over 20 years in the Silicon Valley.

In order to boost the interest, usage and development of electronic design automation (EDA) and intellectual property (IP) standards in Europe, this highly technical conference is organized to invite industry experts to learn and share best practices on:

- The application of system-level design and verification languages such as SystemC, SystemVerilog or e

- The use of SystemVerilog Assertions (SVA) or the Property Specification Language (PSL)

- Verification methodologies based on the Universal Verification Methodology (UVM)

- IP reuse, automation and integration standards based on IP-XACT

- Low power design and verification using the Unified Power Format (UPF)

General topic areas on Electronic System Level (ESL), Verification & Validation, Analog/Mixed-Signal, IP reuse, Design Automation, and Low Power design and verification, will be highlighted in tutorials, papers, and poster sessions.

With a highly technical focus on System and IC design, verification, and integration, DVCon Europe is a very practical and industry-focused conference on EDA standards and standardization.

Conference attendees are primarily designers of electronic systems, ASICs and FPGAs, as well as those involved in the research, development and application of EDA tools and IP integration.

DVCon Europe 2015 welcomed more than 350 participants, managers and engineers from system and microelectronics industry. Also more than 25 exhibitors were present at the exhibition floor with leading EDA, IP and service providers.

CONTREX had a booth at the DVCon Exhibition together with three other projects in the domain: OpenES, CRAFTERS and PAPP.

| Impact Assessmen      | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target                | System companies, Microelectronics companies, Research centres, Universities, Standardisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Audience              | ABILIS SYSTEMS, ACCELLERA, AEDVICES CONSULTING, AGNISYS, AIRBUS OPERATIONS, AIRBUS OPERATIONS SAS, ALTERA, AMIQ, AMIQ CONSULTING, AMIQ EDA, APPLIEDMICRO, ARM, BOOST VALLEY, BREKER SYSTEMS, CADENCE DESIGN SYSTEMS, CAEN SPA, CATENA RADIO DESIGN, CIRRUS LOGIC, CONTI TEMIC, CONTINENTAL AUTOMOTIVE, CONTINENTAL TEVES, COSIDE, COVERIFY, CREATIVE CHIPS, DIALOG SEMICONDUCTOR, DINI GROUP, DIZAIN-SYNC, DMOS GMBH, DOCEA POWER, DOULOS, ECSI, ERICSSON, ERICSSON AB, EVATRONIX, EXCELLICON, FRAUNHOFER AISEC, FRAUNHOFER IIS/EAS, FREESCALE, FUNDAÇÃO CPQD, HONEYWELL, HTV GMBH, IBM, INFINEON, INOVA SEMICONDUCTORS, INTEL, INTEL IND PVT LTD, ISYST GMBH, KALRAY, MAGILLEM, MAXIM INTEGRATED, MENTOR GRAPHICS, MICRONAS, MICROSEMI, NEST GROUP, NESTECH, NOKIA, NUMERIK JENA GMBH, NXP SEMICONDUCTORS, OFFIS, ONESPIN / EVISION, ONESPIN SOLUTIONS, REAL INTENT / Europelaunch, ROBERT BOSCH GMBH, SEMIFORE, SIAE MICROELETTRONICA, SIEMENS AG, SIEMENS SRL, SOLVERTEC, SPANSION, STMICROELECTRONICS, SYNOPSYS, SYOSIL, TEXAS INSTRUMENTS, TVS, UNIVERSITY OF BREMEN, UNIVERSITY PADERBORN, UNIVERSITY SOUTHAMPTON, VERILAB, VITESSE SEMICONDUCTOR, WAFER SPACE, XILINX, ZIPALOG INC |

| Participation profile | <ul> <li>2014 Participants total:250+, 2015: 350+</li> <li>&gt;90% from industry</li> <li>83 companies represented</li> <li>21 exhibitors in 2014, expected 25+ in 2015</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Impact                | <ul> <li>Presentation of OpeES approach to the very wide audience, mostly from industry</li> <li>Collaboration with related projects: PAPP, CRAFTERS, CONTREX</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### 3.7 DATE Workshop 2016

**Date & Location**: March 14-18, 2016 Dresden, Germany **Organizer**: ECSI

CONTREX organized in cooperation with the related project OpenES the open workshop that enabled to present the advances on technical development on both sides. Also there were presentations of case studies, as well as tool implementations from Magillem and EDAlab.

The last part of the event was devoted to reflect and discuss on possible common continuation of the work that was initiated by CONTREX and OpenES. The conclusion was that definitely serval activities brought very promising resluts, but the community needs to continue the effort to put in place a coherent, complete and deployable solution based on approved standards.

#### CONTREX Dissemination Report (Final)

#### System-Level Power and Temperature Specification, Modelling and Analysis

Organizers: Kim Grüttner (OFFIS, DE), Laurent Maillet-Contoz (STMicroelectronics, FR), Adam Morawiec (ECSI, FR)

With the predicted device, core and multicore scaling, a recent study revealed that regardless of chip organization and topology, multicore scaling is power limited. It has been predicted that at 22 nm, 21% of a fixed-size chip must be powered off, and at eight nm, even more than 50%. A system engineer should be able to plan the power intent and break is down to the different hardware resources. With regard to the software, a system engineer should be aware of any possible cross-application interferences with respect to timing, power and thermal properties, as soon as possible in the design flow. Power and temperature management shall be considered in conjunction with the application needs and platform capabilities. For this reason, power and temperature properties need to be modelled and analyzed at the system level, because they can strongly affect the overall quality of service (performance, battery lifetime) or even cause the system to fail meeting its real-time and safety requirements.

In this talk, we present our perspectives on the integration and usage of power and temperature models in SystemC and IP-XACT. This covers the specification of platform properties (extra-functional model) as well as the dynamic capturing, processing, and extraction of power/temperature information during the simulation. In particular, the following topics will be addressed:

- Modeling of extra-functional properties (especially power and temperature) in executable systemlevel models (ESL models)

- Estimation techniques to build/generate/annotate ESL models with extra-functional properties and extra-functional property models

- Expression of Power Management techniques on ESL

- Specification and monitoring of extra-functional properties

- Integration with relevant standards to support future interoperability of models: SystemC, IP-XACT

- Integration into industrial tools

#### Planned Program:

| 9:00 - 9:15   | Opening and Workshop Overview                                                           |

|---------------|-----------------------------------------------------------------------------------------|

| 9:15 - 10:00  | OpenES Modeling Toolkit                                                                 |

|               | Laurent Maillet-Contoz (STMicroelectronics, France)                                     |

| 10:00 - 10:30 | Case Study: IP-XACT Extensions for Safety-Critical Embedded Systems                     |

|               | Ralph Weissnegger (CISC, Austria)                                                       |

| 10:30 - 11:00 | Coffee Break & Exhibition                                                               |

| 11:00 - 11:30 | Power State Machines: State-based System-level Power Estimation and Modelling           |

|               | Daniel Lorenz (OFFIS, Germany)                                                          |

| 11:30 - 12:00 | From RTL IP to Functional System-Level Models with Extra-Functional Properties          |

|               | Franco Fummi (EDALab, Italy)                                                            |

| 12:00 - 12:30 | IP-XACT Extensions for Extra-functional Properties                                      |

|               | Emmanuel Vaumorin (Magillem, France)                                                    |

| 12:30 - 13:30 | Lunch & Exhibition                                                                      |

| 13:30 - 14:00 | Timed Value Streams: Tracing, Monitoring and Analysis of Extra-functional Properties in |

|               | SystemC                                                                                 |

|               | Kim Grüttner (OFFIS, Germany)                                                           |

| 14:00 - 14:30 | Timed Value Stream-based Power and Temperature Model                                    |

|               | Ralph Görgen (OFFIS, Germany)                                                           |

| 14:30 - 15:00 | Coffee Break & Exhibition                                                               |

| 15:00 - 15:45 | Discussion: Enhance Interoperability of Models and Tools by Upgrading and Extending     |

|               | Existing Open Standards (SystemC TLM, SystemC-AMS, IP-XACT)                             |

| 15:45 - 16:00 | Closing and Concluding Remarks                                                          |

This workshop is supported by the European projects OpenES (<a href="https://www.openes-project.org">https://www.openes-project.org</a>) and CONTREX (<a href="https://contrex.offis.de">https://contrex.offis.de</a>).

| Impact Assessment      |                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Target Audience</b> | DATE audience from industry and academia                                                                                                                                                                                                                                                                                                                                                                              |

| Comments               | <ul> <li>Presentation of CONTREX technical content: keynote, case studies, tool implementation</li> <li>Discussion/alignment with OpenES</li> <li>Event though the event was open to external participation it was a working event between CONTREX and OpenES to better understand the technical solutions proposed by the two projects; a very good technical discussion continued through the entire day</li> </ul> |

### 3.8 DAC Workshop 2016: System to Silicon Performance Modeling and Analysis

**Date & Location**: June 5-9, 2016

Austin, TX, USA **Organizer**: ECSI

#### Rationale

The integration of heterogeneous electronic systems composed of SW and HW requires not only a proper handling of system functionality, but also an appropriate expression and analysis of various extra-functional properties: timing, energy consumption, thermal behavior, reliability, cost and others as well as performance aspects related to caching, nondeterminism, probabilistic effects.

The workshop addresses cross-domain aspects related to the design and verification framework covering methodology, interoperable tools, flows, interfaces and standards that enable formalization, specification, annotation and refinement of functional and extrafunctional properties of a system. Special emphasis will be given to formalization and expression of power, temperature, reliability, degradation and aging.

Several research and industry efforts address (parts of) the problem. However, there is a need for community-wide cooperation to establish a holistic vision on extra-functional property treatment, and to agree on research and development directions and further on validation of applicable solutions and standardization.

This event will support collaboration between main actors from system and microelectronics industry, EDA and research.

The workshop is inviting submissions of short abstracts on industrial and scientific work in progress and practical solution and experiences.

#### **Main topics**

- Extra-functional property modeling (power, temperature, reliability, aging, ...)

- Power and temperature analysis at SoC level: future needs and requirements

- Evolution and extensions of standards like UPF, IP-XACT to express extra-functional properties

- Power and temperature simulation and analysis at system-level

- System level reliability and aging models

- Reliability from transistor to RTL level: e.g. NBTI models including basic physical properties

#### **Workshop Organizers:**

- Laurent Maillet-Contoz, STMicroelectronics, France

- Kim Grüttner, OFFIS, Germany

- Gjalt de Jong, ArchWorks, Belgium

- Adam Morawiec, ECSI, France

#### Organized by R&D Collaborative projects:

#### DAC 2016 Workshop on System-to-Silicon Performance Modeling and Analysis Power, Temperature and Reliability Agenda

9:00 Welcome & Agenda

Adam Morawiec (ECSI, France)

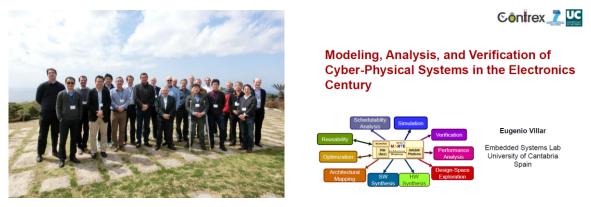

9:15 Keynote 1: System Performance Modeling & Analysis in the Electronics Century

Eugenio Villar (University of Cantabria, Spain)

10:00 Session 1: System-Level Power and Temperature Specification, Modelling and Analysis

1.1 System-level Tracing, Monitoring and Analysis of Extra-Functional Properties

Achim Rettberg, (U Oldenburg & Hella AG, Germany)

1.2 Speed-Up in Design and Evaluation of Safety-Critical Systems based on UML-Profiles and IP-XACT (Case Study / Application Presentation)

Ralph Weissnegger (CISC Semiconductor, Austria)

1.3 Incremental Traceability Framework for Functional and Extra-Functional Properties in Embedded System Design Emmanuel Vaumorin (Magillem Design Services, France)

11:00 Coffee Break

#### 11:15 Keynote 2: Extra-Functional Properties Modelling Environment and Ecosystem

Laurent Maillet-Contoz (STMicroelectronics, France)

#### 12:00 Keynote 3: Generic Multicore Enablement for Effective Programming

Andreas Herkersdorf (Chair for Integrated Systems, Technische Universität München, Germany)

12:45 Lunch

#### 13:30 Keynote 4: Balancing the Effects of Process Variations, Aging, and Application Workload in Multi-Core Systems

Diana Marculescu (Carnegie Mellon University, USA)

#### 14:15 Session 2: Ageing and Variation Effects Prediction

Organizers: Christoph Sohrmann & Roland Jancke (Fraunhofer Institute for Integrated Circuits IIS, Germany)

2. 1 Yield Analysis and Optimization of Full Custom Circuits considering Aging Effects

Michael Pronath (MunEDA, Germany)

2.2 Modeling Short and Long-term Effects of Aging from the Defect to Application Level

Victor M. van Santen, Hyssam Amrouch and Jörg Henkel (Karlsruhe Institute of Technology, Germany)

2.3 NBTI Simulation for Aging of key Characteristics in Analog Circuits

Roland Jancke (Fraunhofer IIS/EAS, Germany)

2.4 Charge Trapping Phenomena in MOSFETS: From Noise to Bias Temperature Instability

Gilson I. Wirth (Universidade Federal do Rio Grande do Sul, Brazil)

#### 15:50 Session 3: Tool Support for Handling Ageing and Variation Prediction

3.1 Aging effects in Automotive Smart Power ICs

Roberto Stella (STMicroelectronics, Italy)

3.2 Modeling of Variability and Aging Effects Across Abstraction Layers

Adrian Evans (iROC Technologies, France)

16:30 End

Organized by R&D Collaborative projects:

| Impact Assessment |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Target Audience   | DAC participants: world-wide industry and academia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| _                 | System, Fab, Fabless, EDA, IP, research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Participation     | 45 registered people                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                   | +70 entering the room                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                   | <ul> <li>Companies &amp; organizations represented:         Ajou University, ARM Ltd., Aurrion Inc., Carnegie Mellon University, CEA LIST,         Cirrus Logic, Inc., Ericsson, Fraunhofer IIS/EAS, Graz University of Technology,         Hella, iRoc Technologies, Karlsruhe Institute of Technology, Leibniz University         of Hannover, LG Electronics, Marvell Semiconductor, Inc., MunEDA GmbH,         Oracle Corporation, Qualcomm Technologies, Inc., Samsung Austin R&amp;D         Center, Samsung Electronics Co., Ltd., Seagate Technology, LLC, Socionext,         Inc., Sony Corp., STMicroelectronics, SuZhou PowerCore Technology,         Synopsys, Inc., Technische Universität München, UFRGS, University of         Cantabria, US Department of Defense (DoD)</li> </ul> |  |