# **REALITY**

# Reliable and Variability tolerant System-on-a-chip Design in More-Moore Technologies

# Contract No 216537

# **Deliverable D7.7**

# Final project report

Editor: Miguel Miranda

Co-author / Acknowledgement: The REALITY Consortium

Status - Version: V1.2

Date: 15/12/2010

Confidentiality Level: Public

ID number: IST-216537-WP7-D7.7

## © Copyright by the REALITY Consortium

### The REALITY Consortium consists of:

| Interuniversity Microelectronics Centre (IMEC vzw) | Prime Contractor | Belgium        |

|----------------------------------------------------|------------------|----------------|

| STMicroelectronics S.R.L. (STM)                    | Contractor       | Italy          |

| Universita Di Bologna (UNIBO)                      | Contractor       | Italy          |

| Katholieke Universiteit Leuven (KUL)               | Contractor       | Belgium        |

| ARM Limited (ARM)                                  | Contractor       | United Kingdom |

| University Of Glasgow (UoG)                        | Contractor       | United Kingdom |

Deliverable D7.7 Page 2 of 2

# 1. Disclaimer

The information in this document is provided as is and no guarantee or warranty is given that the information is fit for any particular purpose. The user thereof uses the information at its sole risk and liability.

# 2. Acknowledgements

# 3. Document revision history

| Date       | Version | Editor/Contributor                                                                                                     | Comments                                                      |

|------------|---------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 17/09/2010 | V0.1    | Miguel Miranda                                                                                                         | First draft                                                   |

| 30/09/2010 | V0.3    | Andrew Brown, Paul Zuber,<br>Ben Geeraerts, Andrea<br>Acquaviva, Yves Laplanche,<br>Giuseppe Desoli                    |                                                               |

| 1/10/2010  | V0.5    | Andrew Brown, Paul Zuber,<br>Ben Geeraerts, Andrea<br>Acquaviva, Yves Laplanche,<br>Giuseppe Desoli, Miguel<br>Miranda | from all partners. Most tables of resources in Section 12 are |

| 2/10/2010  | V0.6    | Miguel Miranda, Andrea<br>Acquaviva                                                                                    | Update from UNIBO and IMEC on table of resources              |

| 3/10/2010  | V0.7    | Miguel Miranda                                                                                                         | Project Management added                                      |

| 5/10/2010  | V0.8    | Yves Laplanche                                                                                                         | ARM's explanation of resources added                          |

| 4/10/2010  | V1.0    |                                                                                                                        | First Final Version                                           |

| 7/10/2010  | V1.1    | Yves Laplanche, Andrea<br>Acquaviva                                                                                    | Updates on table of resources for ARM and UNIBO               |

| 15/12/2010 | V1.2    | Eleonora Medeot, Bruno<br>Jansen                                                                                       | Updates including audit certificates from ARM and UNIBO       |

Deliverable D7.7 Page 3 of 3

#### 4. Preface

The scope and objectives of the REALITY project are :

Development of design techniques, methodologies and methods for real-time guaranteed, energyefficient, robust and adaptive SoCs, including both digital and analogue macro-blocks"

## The Technical Challenges are:

- To deal with increased static variability and static fault rates of devices and interconnects.

- To overcome increased time-dependent dynamic variability and dynamic fault rates.

- To build reliable systems out of unreliable technology while maintaining design productivity.

- To deploy design techniques that allow technology scalable energy efficient SoC systems while guaranteeing real-time performance constraints.

#### Focus Areas of this project are:

- "Analysis techniques" for exploring the design space, and analysis of the system in terms of performance, power and reliability of manufactured instances across a wide spectrum of operating conditions.

- "Solution techniques" which are design time and/or runtime techniques to mitigate impact of reliability issues of integrated circuits, at component, circuit, architecture and system (application software) design.

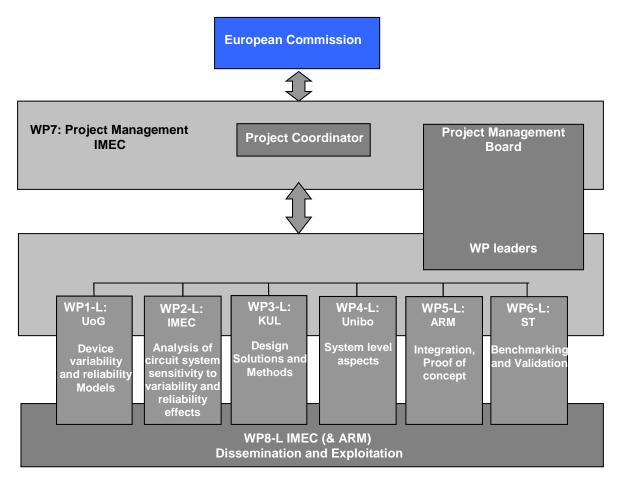

The REALITY project has started its activities in January 2008 and is planned to be completed after 30 months. It is led by Dr. Miguel Miranda of IMEC. The Project Coordinator is Dr. Miguel Miranda from IMEC. Five contractors (STM, ARM, KUL, UoG, UNIBO) participate in the project. The total budget is 2.899 k€

Deliverable D7.7 Page 4 of 4

# 5. Abstract

This report is deliverable D7.7: "Final report". The reporting period covers from M25 until M32. Hence it covers roughly the last semester of project execution after the second review meeting.

Deliverable D7.7 Page 5 of 5

# 6. List of Abbreviations

| REALITY | Reliable and Variability tolerant System-on-a-chip Design in More-Moore |

|---------|-------------------------------------------------------------------------|

|         | Technologies                                                            |

| CAD     | computer aided design                                                   |

| DSP     | digital signal processing                                               |

| HW      | Hardware                                                                |

| IC      | integrated circuit                                                      |

| SoC     | system on chip                                                          |

| SW      | Software                                                                |

|         |                                                                         |

|         |                                                                         |

|         |                                                                         |

Deliverable D7.7 Page 6 of 6

# 7. List of Tables

| Table 1. Flow performance data                                                                                                                                                                                     | 20      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Table 2 Fraction of deadline misses caused by the various policies for different number of tasks for the                                                                                                           | e slice |

| decoding and IDCT functions                                                                                                                                                                                        |         |

| Table 3 Energy consumption for different number of tasks for the slice decoding and IDCT functions                                                                                                                 |         |

| Table 4 List of planned Deliverables for Year 3                                                                                                                                                                    |         |

| Table 5 List of planned Milestones for Year 3                                                                                                                                                                      |         |

| Table 6: Update of the DoW                                                                                                                                                                                         | 36      |

| Table 7: Overview of project meetings                                                                                                                                                                              |         |

| Table 8 List of deliverables submitted to the EC                                                                                                                                                                   | 38      |

| 8. List of Figures                                                                                                                                                                                                 |         |

| Figure 1: Normal probability plot showing the distribution of threshold voltages for different leveral degradation of the p-channel device and the associated shift in $V_T$ from the trap-free device. $V_D$ =-1. | 0V16    |

| Figure 2: Fit of the extracted compact model compared to the original simulation data for the nMOSFET device with no sources of variability.                                                                       |         |

| Figure 3: Distribution of RMS errors. with the number of model parameters reextracted                                                                                                                              | 17      |

| Figure 4. Hybrid statistical timing analysis flow                                                                                                                                                                  | 19      |

| Figure 5. Digital core layout                                                                                                                                                                                      | 19      |

| Figure 6 Different local bit line architectures                                                                                                                                                                    | 22      |

# 9. Table of contents

| 1.         | DISCLAIMER                                                                                                | 2  |

|------------|-----------------------------------------------------------------------------------------------------------|----|

| 2.         | ACKNOWLEDGEMENTS                                                                                          | 2  |

| 3.         | DOCUMENT REVISION HISTORY                                                                                 | 2  |

| 4.         | PREFACE                                                                                                   |    |

| →.<br>5.   | ABSTRACT                                                                                                  |    |

|            | LIST OF ABBREVIATIONS                                                                                     |    |

| 6.<br>–    |                                                                                                           |    |

| 7.         | LIST OF TABLES                                                                                            |    |

| 8.         | LIST OF FIGURES                                                                                           |    |

| 9.         | TABLE OF CONTENTS                                                                                         |    |

| 10.        | DECLARATION BY THE SCIENTIFIC REPRESENTATIVE OF THE PROJECT COORDINATOR                                   | 10 |

| 11.<br>DES | PUBLISHABLE SUMMARY: "RELIABLE AND VARIABILITY TOLERANT SYSTEM-ON-A-C<br>SIGN IN MORE-MOORE TECHNOLOGIES" |    |

| 12.        | WORK PROGRESS AND ACHIEVEMENTS DURING THE PERIOD                                                          | 16 |

| 1:         | 2.1. WP1: Device variability and Reliability Models (WP leader: UoG)                                      |    |

| 12         | 2.2. WP2: System and circuit characterization and sensitivity analysis (WP leader: IMEC)                  | 18 |

|            | 12.2.1. (Task 2.1.1) – Statistical Characterization of Standard Cell Libraries                            |    |

|            | 12.2.2. (Task 2.3) - Hybrid (corner/statistical) Statistical Analysis flow for Digital Blocks             |    |

|            | 12.2.4. (Task 2.5) – Variation Information Format Framework                                               |    |

| 12         | 2.3. WP3: MIXED MODE COUNTERMEASURES (WP LEADER: KUL)                                                     |    |

|            | 2.4. WP4: System level countermeasures (WP leader: UNIBO)                                                 |    |

|            | 2.5. WP5: Design flow, integration, proof of concept (WP leader: ARM)                                     |    |

|            | 2.6. WP6: VALIDATION AND ASSESSMENT OF RESULTS (WP LEADER: ST)                                            |    |

|            | 2.7. WP7: PROJECT MANAGEMENT (WP LEADER: IMEC)                                                            |    |

|            | 2.8. WP8: EXPLOITATION AND DISSEMINATION (WP LEADER: IMEC/ARM)                                            |    |

| 13.        | DELIVERABLES AND MILESTONES TABLES                                                                        |    |

| 14.        | PROJECT MANAGEMENT                                                                                        | 34 |

|            | 4.1. CONSORTIUM MANAGEMENT TASKS AND ACHIEVEMENTS;                                                        | 34 |

| 14         | 4.2. PROBLEMS WHICH HAVE OCCURRED AND HOW THEY WERE SOLVED OR ENVISAGED SOLUTIONS                         |    |

|            | 14.2.1. REALITY Top Risks to date:                                                                        |    |

| 4          | 14.2.2. Changes:                                                                                          | 35 |

|            | 4.3. LIST OF PROJECT MEETINGS, DATES AND VENUES IN YEAR T:                                                |    |

|            | 4.5. IMPACT OF DEVIATIONS MATERIALIZED FROM THE PLANNED MILESTONES AND DELIVERABLES                       |    |

|            | 4.6. Development of the Project website:                                                                  |    |

|            | 4.7. USE OF FOREGROUND AND DISSEMINATION ACTIVITIES DURING THIS PERIOD:                                   |    |

| 14         | 4.8. COORDINATION ACTIVITIES COMMENT - KEY MESSAGE:                                                       | 39 |

| 15.        | EXPLANATION OF THE USE OF THE RESOURCES                                                                   | 39 |

| 1:         | 5.1. ST Microelectronics                                                                                  | 39 |

|            | 5.2. IMEC                                                                                                 |    |

|            | 5.3. University of Glasgow                                                                                |    |

|            | 5.4. Katholieke Universiteit Leuven                                                                       |    |

|            | 5.5. University of Bologna<br>5.6. ARM                                                                    |    |

| 16.        | FINANCIAL STATEMENTS – FORM C AND SUMMARY FINANCIAL REPORT                                                |    |

|            |                                                                                                           |    |

Deliverable D7.7 Page 8 of 8

17. CERTIFICATES.......45

Deliverable D7.7 Page 9 of 9

# PROJECT PERIODIC REPORT

Grant Agreement number: 216537

Project acronym: REALITY

Project title: "Reliable and Variability tolerant System-on-a-chip Design in More-Moore Technologies"

Funding Scheme: Collaborative project (STREP)

Date of latest version of Annex I against which the assessment will be made:

Periodic report:  $1^{st} \Box 2^{nd} \Box 3^{rd} \boxtimes 4^{th} \Box$

Period covered: from 01/01/2010 to 31/08/2010

Name, title and organisation of the scientific representative of the project's coordinator:

Dr. Miguel Miranda Tel: +32 16 281 524

Fax: +32 16 28 1515

E-mail: Miguel.Miranda@imec.be

Project website address: http://www.fp7-reality.eu/

Deliverable D7.7 Page 10 of 10

# 10. Declaration by the scientific representative of the project coordinator

I, as scientific representative of the coordinator of this project and in line with the obligations as stated in Article II.2.3 of the Grant Agreement declare that:

- The attached periodic report represents an accurate description of the work carried out in this project for this reporting period;

- The project has fully achieved its objectives and technical goals for the period;

- The public website is up to date, if applicable.

- To my best knowledge, the financial statements which are being submitted as part of this report are in line with the actual work carried out and are consistent with the report on the resources used for the project and if applicable with the certificate on financial statement.

- All beneficiaries, in particular non-profit public bodies, secondary and higher education establishments, research organisations and SMEs, have declared to have verified their legal status. Any changes have been reported under section 15 (Project Management) in accordance with Article II.3.f of the Grant Agreement.

Name of scientific representative of the Coordinator: Miguel Miranda Corbalan

Date: 17/09/2010

Signature of scientific representative of the Coordinator

Miguel Miranda Principal Scientist TU-SSET-DC - Group

Phone: +32 16 28 15 24 / Fax: +32 16 28 15 15

E-mail: Miguel. Miranda@imec.be

Deliverable D7.7 Page 11 of 11

# 11. Publishable summary: "Reliable and Variability tolerant System-on-a-chip Design in More-Moore Technologies"

# **Project Facts:**

• FP7 Project : European Community funded

• Coordination : IMEC

• Website: www.fp7-reality.eu

• Duration : 30 Months

• Effort: 382 person-months

• Industry: ARM (UK), ST Microelectronics (Italy)

Start date: 1st January 2008

University: Glasgow (UK), Bologna (Italy), Leuven (Belgium)

• Research Centre : IMEC (Belgium)

# Scope:

- Scaling beyond the 32 nm technology

- Tackle the increased variability and changing performance of devices from device unto system level.

Random discrete dopants in a 35 nm MOSFET from the present 90 nm technology node.

# **Challenges:**

- Increased static variability and static fault rates of devices and interconnects.

- Increased time-dependent dynamic variability and dynamic fault rates.

- Build reliable systems out of unreliable technology while maintaining design productivity.

- Deploy design techniques that allow technology scalable energy efficient SoC systems while guaranteeing real-time performance constraints.

# **Proposed solution:**

- System analysis of performance, power, yield and reliability of manufactured instances across a wide spectrum of operating conditions.

- Generally applicable solution techniques to mitigate the impact of reliability issues of integrated circuits, at component, circuit, and architecture and system design.

Deliverable D7.7 Page 12 of 12

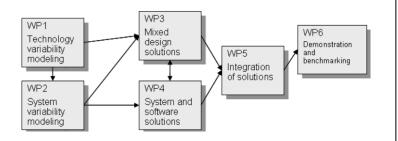

#### WP1: Device variability and Reliability Models (WP leader: UoG)

Having completed the simulation of variability in the 32nm devices including random discrete dopants, line edge roughness and metal gate granularity, this was used as a starting point for investigating reliability issues due to the trapping of electrons and/or holes in defect states in the gate stack during circuit operation. To each fresh device were added additional fixed charges, randomly within the channel, based on the trap sheet density, and a full 3D simulation was performed. Distributions of threshold voltages and  $V_T$  shifts were obtained.

Using the strategy for statistical compact model extraction developed in the project for use with PSP compact models, a statistical library of compact models was created based on the 32nm technology. This can be used for Monte Carlo statistical circuit simulation. An approach based on Principal Component Analysis of the data extracted from the statistical device simulations, which allows correlations between extracted parameters to be maintained, has been developed for on-the-fly calculation of statistical model parameters.

Using the statistical compact models developed for the 45nm technology, including different levels of NBTI/PBTI degradation, a detailed investigation of the effect of statistical variability and reliability on the performance of an SRAM cell was performed.

ARM has used the output of the cell level characterisation from WP5 and WP6 to analyse the difference between the statistical models from the foundry and from UoG available in the project through the variability injectors generated by IMEC.

Deliverable D1.2, due at T0+27, was successfully delivered on time.

#### WP2: System and circuit characterization and sensitivity analysis (WP leader: IMEC)

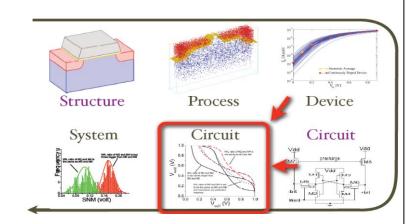

The goal of this WP is to develop advanced methodologies and techniques for statistical analysis. The intention is to read the output of transistor level variability, as provided by WP 1, and to propagate this information all the way from the device level to the product level. The WP also targets developing and fully characterizing a limited standard cell library (50-100 cells) for synthesis and analysis based on restricted design rules for use in WP2, WP3, WP4, and WP5.

Commercial EDA solutions (e.g., fast circuit simulators, SSTA tools, power analysis tools, etc) were reused in the flow wherever possible in combination with Monte Carlo-based simulation techniques in order to guarantee the compatibility with existing electronic design simulation/verification tools and easy adoption by engineers trained to these tools. This was not always possible. Even commercial tools show bugs or are simply inappropriate for particular purposes. This can occur in any area, in particular in the areas of electrical simulation, characterization, statistical characterization, and statistical static timing analysis. Depending on case, new methods were developed and implemented, or commercial vendors were asked to revise their products.

New methods were identified in the areas of standard cell characterization (ST's hybrid flow, imec's VAM, UoG's characterizer), memory characterization (ARM's extreme value theory based memory margining application, imec's MemoryVAM), statistical timing analysis (ST's hybrid flow on the digital level, imec's VAM), as well as system level analysis (VAM).

Also considered in this WP is the strategic aspect of the standardization of the interfaces between different abstraction levels to enable the propagation of variability specific information throughout the design flow. To "lubricate" the flow developed here and applied and integrated in all other work packages, we put in place a standard electronic Information Format (IF) that keeps statistical information and exists parallel to the classical top-down and bottom-up design flows.

All deliverables (D2.3 and D2.4) have been submitted on time.

WP3: Mixed mode countermeasures (WP leader: KUL)

Deliverable D7.7 Page 13 of 13

In work package 3, an advanced reliability simulation technique including process variability in the simulation flow was developed. In order to get a computationally efficient solution, a Response Surface Model (RSM) based simulation technique is proposed. In this approach the vast number of computationally intensive simulations needed to perform a Monte-Carlo analysis, is replaced by the evaluation of an analytical model of the circuit. The focus of this work is not to obtain a highly accurate prediction of yield, but to analyze the spatial and temporal reliability of a circuit in a reasonably short time frame. When compared to direct Monte-Carlo yield simulation, examples indicate this method to have a simulation speedup ranging from 1 to 3 orders of magnitude, without sacrifying accuracy. Additionally, weak spot analysis allows to improve the design or to reduce design margins and to gain extra performance.

Also, with the availability of the 32nm compact models, an extra iteration on the KUL SRAM memory has been done. The reliability simulation framework has been applied to one cell of the KUL memory (full memory analysis is performed by the MemoryVAM). A huge amount of minimal sized cells, of which the functionality of every single one is critical demands big design margins. The most vulnerable parts of a memory were identified to be the cells, the sense amplifiers and the timing. Cell stability can be increased by reducing the cell load capacitance. For this reason, divided bit lines are introduced. Additional advantages include possible speed and energy gains. The impact of NBTI, on the performance of one cell has been simulated as a function of cell voltage. Other improvements include sharing sense amplifiers and usage of a configurable timing circuit to reduce variability effects. Some estimations of the effect of BEOL-variability have been done. At this moment, these variations seem to have a limited effect due to the averaging out for the big wires and the small impact of small wires. A fully functional 1KB SRAM memory with a word length of 32bit was build. The obtained speed was 1GHz. Total write energy was 0.69pJ, read energy was a bit higher: 1.07pJ.

#### WP4: System level countermeasures (WP leader: UNIBO)

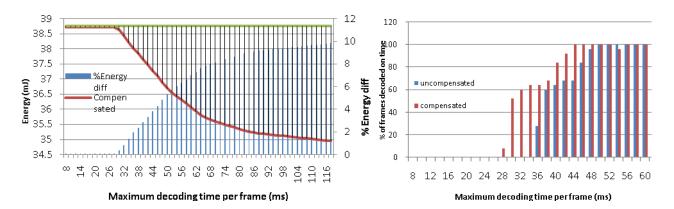

The activity of UNIBO in year 3 has been devoted to the porting and optimization of system level policies to the target platform and validation benchmark. We evaluated the capability of the techniques to compensate the variability impact on application performance. The impact of variability on multicore multimedia platform makes hard to get the a certain QoS from the running software because of the speed variations across the cores, which causes a sub-optimal exploitation of the platform parallelism. Moreover, QoS and power consumption vary from platform to platform.

Thanks to a smart allocation of the workload, it is possible to compensate this impact, obtaining an improvement of the QoS and energy consumption for a given platform as well as an increase of the predictability across many variability affected platforms. System level compensation allows to better guarantee the QoS with respect to a non compensated one. Indeed, a smart workload allocation strategy applied to a variability affected platform, helps reducing the deadline misses and reduces the energy consumption.

During the reporting period, we optimized the workload allocation policies so that they can be applied on-line on a frame-by-frame basis. The optimization was targeted to the reduction of the execution time of the policies, to provide the wanted QoS level with minimum energy, independently form the variability impact on the platform. The techniques have been ported to a relevant industrial case study of a multicore multimedia platform, with a single voltage domain, multiple frequency domain. Since variability causes the cores to be characterized by different speeds, the designer can tune each core to its maximum supported frequency to improve performance. However, now he/she has to handle a heterogeneous platform. This may cause inefficiencies when allocating multitask applications, because the speed heterogeneity lead to a unbalanced allocation. This effect can be compensated by a smart allocation, thanks to which the designer can exploit the advantage of having clocked the system in a heterogeneous way without paying the price of the unbalancing and thus overall leading to a better QoS with respect to a non-compensated platform.

#### WP5: Design flow, integration, proof of concept (WP leader: ARM)

No summary available. These work package activities have been completed during the earlier reporting period.

#### WP6: Validation and assessment of results (WP leader: ST)

This WP reported on the analysis, validation and industrial impact for all of the REALITY outcomes.

The validation and benchmarking revolved around a two pronged strategy based on the leverage of an industrially proven embedded microprocessor design provided by ARM, the ARM926, and an advanced

Deliverable D7.7 Page 14 of 14

multiprocessor based multimedia accelerator platform from STM, the xSTream platform. Much of the project conclusions are gathered in the reports produced by WP6.

For the first time, full scale 3D simulation of statistical variability associated with metal gate granularity and the corresponding metal work function variations has been carried out to clarify the magnitude of statistical variability in 32 nm CMOS transistors with high-k/metal gate stack. In addition, technology has been developed to simulate the statistical aspects of reliability associated with NBTI/PBTI.

Also for a first time, a full statistical characterization of an ARM core has been achieved. A correlation between the timing, leakage and dynamic power has been demonstrated on local (within die) and non-local (above die) variations. The traditional corner analysis could be benchmarked with innovative statistical analysis techniques. Using the ARM core as driver, REALITY has confirmed that the SRAM components are responsible for more than the half of the variations on critical path timing. Much focus has been placed by both state-of-the-art and EDA vendors on the logic while the variability challenges remain in the memories themselves. For that purpose REALITY has been also first in deploying a holistic statistical characterization flow including SRAM analysis variations at and their evolution over time.

REALITY has also for first time evaluated the impact of process variation in SW level metrics showing process variability is not only a concern for HW but for SW as well. It has concluded that variability affecting multi-core multimedia platforms makes it hard to guarantee a certain QoS from the running application's functionality. The speed variations across the cores cause sub-optimal and platform-dependent parallelism. REALITY has developed an approach to compensate this by using a smart allocation of the workload at run-time, hence also at the SW level, and obtaining an improvement of QoS by 20% and energy consumption by 15% while obtaining better platform predictability.

For that purpose, different circuit design techniques for system adaptation have been investigated, among them Adaptive Body Biasing (ABB). REALITY has shown that even though the possible compensation range in speed up due to ABB is significantly reduced compared to the previous node, it remains still available at 32nm. The technique has been validated on the ALU design of the ARM core using specially characterized commercially available libraries.

The xSTream platform was used as a test case for a system level driver and benchmarking environment to develop and validate multitask sw allocation and scheduling policies in the presence of different kinds of variability 'control and measuring knobs'.

To enable the project to obtain trends and projection on real industrial application retrofitted with such sw control stacks, the system platform needed to be an executable model capable of supporting real-time simulation of applications. The system level validation and benchmarking activities carried out in WP6 have resulted in hundreds of simulation trials were a number of parameters were changed by selecting statistical relevant distributions produced by the IP block variability analysis flows. Results were analyzed in terms of multiple objective metrics keeping power consumption, yield, area and cost into account. The final impact analysis carried out in WP6 did not attempt to exhaustively provide a coverage of all of the advantages and drawbacks; but rather identified and highlighted the concrete impact, for example in terms of adoption of the variability characterization flow, variability aware design techniques, sw and hw countermeasures, when applied to pragmatic product like development conditions measured by a choice of objective industrially relevant metrics applied to pragmatic product like development conditions.

Deliverable D7.7 Page 15 of 15

# Objectives for the period 2, Project M24 until M32

The reporting Period 3 covers the project time-schedule M24 until M32, i.e. starting from 1<sup>st</sup> January 2010 until 31st August 2010. This report is a progress report for such period. Also serves a final report.

Description of the performance / research indicators (all targets for Y3 have been met!)

| Description of the                         | periormance / research indi                                                                                                                                                                    | cators (all targets for 13 nave                                                                                  | been met:)                                                                                                                |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| WP                                         | After year 1                                                                                                                                                                                   | After year 2                                                                                                     | At end of project                                                                                                         |

| WP2<br>Circuit to<br>System<br>Variability | Preliminary version of a RDR std. cell library [32nm]. Flow definition and framework set up for variability characterization. Correlated variability energy timing flow definition and set up. | Exploitation of the variability aware modelling flow on the                                                      | Methodology fine tuned. Feedback from benchmarking acknowledged.                                                          |

| WP3<br>Mixed design                        | Description of the variability and reliability analysis methods at circuit level                                                                                                               | Demonstration of the developed method on SRAM and analog circuits                                                | Validation of the developed method                                                                                        |

| WP4<br>Algorithm                           | Software techniques for flexible data and workload allocation for migration (the base flexible RTSM support)                                                                                   | Control algorithms for system level reliability and variability management (exploiting of the base RTSM support) | Porting, optimization and tuning for the target evaluation platform of: (a) the flexible RTSM, (b) the control algorithms |

| WP5<br>Integration                         | Definition of characterization blocks, macrocells, and system level architecture                                                                                                               | Validation and application of methods to macrocells and integration into system                                  | Final system integration, validation feeding into WP6 benchmarking                                                        |

| WP6<br>Benchmarking                        | Identification of relevant industrial applications and associated requirements and evaluation metrics                                                                                          | Definition of the validation plan Benchmarking of block level IPs                                                | Benchmarking of system level platform Evaluation of results and impact according to validation plan criteria              |

Deliverable D7.7 Page 16 of 16

# 12. Work progress and achievements during the period

# 12.1. WP1: Device variability and Reliability Models (WP leader: UoG)

Having completed the simulation of variability in the 32nm devices including random discrete dopants, line edge roughness and metal gate granularity, this can be used as a starting point for investigating reliability issues due to the trapping of electrons and/or holes in defect states in the gate stack during circuit operation. Reliability problems in sub-45 nm technology devices will have a distinct statistical manifestation and the change in the characteristics of any nano-CMOS device during circuit operation will vary depending on the actual position of single or multiple defect charges in the channel region of the transistor. We have carried out a detailed 3D simulation of the statistical distribution of the corresponding changes in device characteristics due to microscopic manifestations of particular device defect configurations.

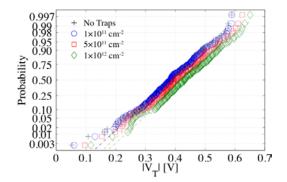

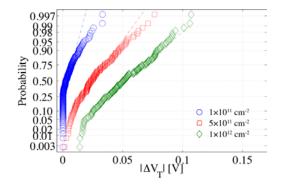

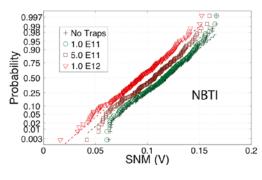

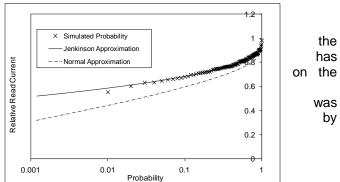

Here we have used the same 3 densities of trapped charge, suggested by IMEC, as with the 45nm device  $(10^{11}\text{cm}^{-2}, 5\times10^{11}\text{cm}^{-2})$  and  $10^{12}\text{cm}^{-2})$ . The starting point is the 200 devices already simulated with all relevant sources of variability. In the statistical simulation of the transistor degradation, to each device was added additional fixed charges, randomly within the channel, based on the sheet density. The 200 devices were then simulated with each of the different trap densities. This additional channel charge will act to increase the absolute threshold voltage, however the shift in  $V_T$  will depend on both the actual number and the location of the original dopant charges, and on the number and location of the additional trapped charges. Figure 1 shows the distribution of  $V_T$  and the shift in  $V_T$  ( $\Delta V_T$ ) as normal probability plots, for the different levels of degradation in the pMOSFET.

It was seen that the shift in  $V_T$  increases with increasing trap density due to the extra negative charge at the interface. For the 45nm devices it was observed that an increasing trap density lead to an increase in  $\sigma V_T$  due to the interaction of the additional charge with the current paths formed in the non-degraded device. The lack of a strong dependence of  $\sigma V_T$  on the trap density in this 32nm case may be due to increased screening of the additional interface charge due to use of a metal gate compared to the poly-silicon gate used in the 45nm technology.

Figure 1: Normal probability plot showing the distribution of threshold voltages for different levels of degradation of the p-channel device and the associated shift in  $V_T$  from the trap-free device.  $V_D$ =-1.0V

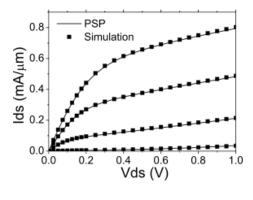

A two-stage direct statistical compact model extraction procedure is applied without any pre-assumption of parameter distribution, correlation or sensitivity. As a result this approach will provide the most accurate representation of the current voltage characteristics obtained from physical 3D simulation or from measurement. In the first stage of the extraction process, a local level parameter extraction strategy is applied to obtain a complete set of PSP parameters for a uniformly doped device with no sources of variability. Figure 2 shows the result of the full parameter extraction for the uniform nMOSFET. Good agreement with the original simulation data from which the models are extracted has been achieved.

In the second stage, using the compact model extracted in stage one as a base, a number of the model parameters are re-extracted to account for the variation between the uniform model and the characteristics of a device affected by statistical variability. Based on the physical analysis of the impact of intrinsic statistical variability on device operation, 7 possible fitting parameters have been identified for re-extraction with PSP. Figure 3 shows the distribution of RMS errors calculated for the extraction of compact models from the

Deliverable D7.7 Page 17 of 17

simulation of 200 devices with statistical variability, and demonstrates how the number of parameters that are re-extracted affects the accuracy of the statistical compact model cards when compared to the original simulation data from which they are extracted.

Using the ensemble of models generated by direct statistical parameter extraction, a statistical compact model library for the 32nm device has been constructed and devices in circuits can be randomly selected from the library during statistical circuit simulation. Although this is the most rigorous method of performing statistical circuit simulation, the available statistical sample size is pre-determined by size of the compact model library. Common practice in Monte Carlo circuit simulation is to generate statistical parameter values on the fly. An approach based on Principal Component Analysis (PCA) of the data extracted from the statistical device simulations, which allows correlations between extracted parameters to be maintained, has been developed.

Using the statistical compact models developed for the 45nm technology, including different levels of NBTI/PBTI degradation, a detailed investigation of the effect of statistical variability and reliability on the performance of an SRAM cell was performed. This showed that when NBTI in the pMOSFETs is considered, increasing trap density leads to a decrease in the static noise margin (Fig. 4). When PBTI in the nMOSFETs is also considered the mean of the SNM does not change but the standard deviation of SNM increases. ARM has used the output of the cell level characterisation from WP5 and WP6 to analyse the difference between the statistical models from the foundry and from UoG available in the project through the variability injectors generated by IMEC.

Figure 2: Fit of the extracted compact model compared to the original simulation data for the nominal nMOSFET device with no sources of variability.

Figure 3: Distribution of RMS errors. with the number of model parameters reextracted.

Figure 4: Normal probability plot of static noise margin for different degradation stages of NBTI

#### Use of resources

| Partner | Planned effort (MM) | Actual effort (MM) |

|---------|---------------------|--------------------|

| UOG     | 6                   | 16.3(*)            |

| IMEC    | 0                   | 0                  |

| UNIBO   | 0                   | 0                  |

| ST      | 0                   | 0                  |

| KUL     | 0                   | 0                  |

| ARM     | 0.8                 | 0.8                |

| TOTAL   | 6.8                 | 17.1               |

(\*) Unforeseen extra time spent on the simulations of n/pbti with the metal gate, particularly looking at unexpected results, meant that extra manpower was required to deal with extraction of compact models, using and refining the new PSP extraction strategy. Additionally, extra work was done to demonstrate the value of our statistical compact models in a full investigation of the effects of statistical reliability issues in SRAM cells. Luckily we were able to resource this within budget due to the favourable exchange rate between the pound and the euro.

Deliverable D7.7 Page 18 of 18

#### 12.2. WP2: System and circuit characterization and sensitivity analysis (WP leader: IMEC)

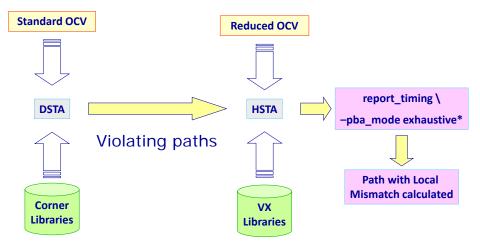

#### 12.2.1. (Task 2.1.1) – Statistical Characterization of Standard Cell Libraries

Local random mismatch will potentially increase design working frequency. Mismatch requires extra margins for skew and pulse width, thus impacting achievable performance. Using larger cell size to reduce mismatch conflicts with tight area and power constraints in advanced nanometer technologies. In the reporting period ST I has developed a local random mismatch-aware Static Timing Analysis (STA) technique that can provide a bridge between traditional Deterministic STA (DSTA) and Statistical Static Timing Analysis (SSTA), in the frame of the Hybrid Statistical Timing Analysis (HSTA) flow concept proposed in Task 2.3. The impact of mismatch was characterized at cell level and used to predict the mismatch impact on paths for digital clock networks within 10% error margin that in absolute terms is within few picoseconds. This mismatch characterization activity was mainly focused on including the mismatch impact in clock-tree network design. The approach can be implemented in current timing analysis tools using inputs from traditional DSTA, to derive advanced (and less pessimistic) margins. It builds on a mainstream DSTA technique and thus is easily implementable in current design flows, and its novelty stems from the compromise on error margins to enable fast implementation time and minimal overheads. The error margins are within acceptable limits.

Silicon-proven industrial models were used to characterize the impact of mismatch. Standard cells were taken from ST 45nm CMOS production library (same technology used for previous activity on statistical characterization), and it was used a realistic interconnect model with the resistance to capacitance ratio extracted from ST industrial 45nm process for routing interconnects to include slew degradation and have a comparable reference of path depth to design size. Realistic clock paths were constructed using automated scripts enforcing clock-tree design rules. The goal of mismatch-aware STA was to predict the statistical  $\mu\pm3\sigma$  (average shift, standard deviation) limits around corner cases.

It was achieved a good level of accuracy through mismatch-aware STA to calculate the impact of mismatch on different parameters in a clock-tree path. Verification using Monte Carlo simulations on different configurations validated this approach, which can be easily implemented in current design flows with small overheads. Therefore, it was established a direct and effective link between the advanced R&D activities carried out in WP2 during the first phase of the project, and a fast industrial exploitation.

In 2010 ARM has invested time on the SSTA characterization of the standard cells libraries. The task started in 2009 lead to an evaluation of the accuracy of the flow. At that time the conclusion of the study had us stop investigations on this flow. Following the latest improvements from our tool provider ARM wanted to analyse a little bit more the potential of a commercially available flow. We are currently trying to put in place a flow to validate the information extracted from higher level designs in order to verify the complete approach.

ARM has also spent some efforts to go on debugging the classical characterization flow in order to adapt it to the needs of the VAM characterization. The team was challenged on the repeatability of the flow. A clean definition of the spice options has to be defined in order for all the characterization to go through with the same simulation condition which is necessary for an accurate comparison of the results. The high number of characterization necessary for one Temperature / Voltage condition also challenged to team on a good robustness of the process in order not to loos time due to high failure rates during the simulations.

In addition the minor improvements in the memory statistical characterization tool have been carried out in parallel with an effort spent to transfer the knowledge generated in the project to other groups in the company leading to an effort increase in this work package.

A memory critical path slice of the memory designed in WP3 was made by K.U.Leuven. As this memory is a complex hierarchically structured circuit, a lot of effort was spend in making sure equivalent load capacitances were added on all levels while still trying to remove as much circuitry as possible in order to decrease simulation time. Testbenches for memory energy, memory delay and hold time were made. These tests were run with MVAM.

Deliverable D7.7 Page 19 of 19

#### 12.2.2. (Task 2.3) - Hybrid (corner/statistical) Statistical Analysis flow for Digital Blocks

Statistical analysis solutions for random within-die (WID) variations (such as the local random mismatch) available today are quite complex for an effective industrial exploitation. Most approaches for WID variations are focused on systematic mismatch, which can be ameliorated by means of manufacturing-driven improvements (regular design, restricted design rules, resolution enhancement techniques). In REALITY ST I demonstrated that Statistical Static Timing Analysis (SSTA) is a good estimator of random WID variations, but in general, it lacks ease of deployment in an industrial environment, and requires a lot of efforts to characterize the statistical libraries. Moreover, it also true that chip designers in an industrial environment, who have to satisfy tough turn-around-time requirements, and have to meet strict time-to-market windows dictated by an increasingly fierce competition, do not want to change the traditional sign-off methodology for timing verification based on DSTA.

Therefore, it is necessary to develop a rapidly deployable solution based on existing and reliable commercial CAD tools and an industrial digital design flow, which also uses industrial models to reduce the impact of random intra-die variations at the cell level. Moreover, it is necessary to define the basic set of process parameters to effectively characterize the standard cell libraries. The objective of this activity (Task 2.3) was to develop a hybrid statistical analysis flow based on commercial DSTA tools and a new technique to consider the impact of random WID variations (i.e., device mismatch characterized in Task 2.1.2). By means of this approach it was possible to analyze the local random variations without using the traditional design margins (based on derating factors) are either pessimistic or risky, as it was demonstrated in WP2. The hybrid flow allows reducing the design margins and removing some pessimism, without changing the digital sign-off flow and methodology. To enable this hybrid flow, new techniques to characterize statistical libraries including the contribution of local device mismatch have been defined in order to avoid running a full Monte Carlo analysis, which is extremely time-consuming.

The Hybrid Statistical Timing Analysis (HSTA) flow developed during the reporting period is outlined in Figure 4.

Figure 4. Hybrid statistical timing analysis flow

This approach was used to evaluate the impact of random mismatch variations on digital designs in ST CMOS045LP (45nm low-power) technology. The trial design considered is a digital core (Figure 5), whose characteristics are the following:

- 200K nets;

- Main clock period (CLK): 2.2ns;

- Highly tuned for high-speed and low-power;

- Representative of CPU's in majority of future ST designs;

- Main clock insertion delay: about 1.3 ns.

2297 setup and 4926 hold path were analyzed. In terms of runtime, overall 1K single path per minute was processed on fast machine. Some relevant flow performance data are reported in Table 1.

Deliverable D7.7 Page 20 of 20

| Table 1. Flow performance da | ıta | da | ce | and | rm | fo | pe | w | lo | F | 1. | le | Tab |

|------------------------------|-----|----|----|-----|----|----|----|---|----|---|----|----|-----|

|------------------------------|-----|----|----|-----|----|----|----|---|----|---|----|----|-----|

|        | Step               | Host           | Runtime |

|--------|--------------------|----------------|---------|

| DSTA   | Import data        | Dual Core Xeon | 1m 14s  |

| DSTA   | Update timing      | 3GHz, 16GB     | 5m 13s  |

| IICT A | Setup (2297 paths) | Quad Core Xeon | 2m 11s  |

| HSTA   | Hold (4926 paths)  | 3.33GHz, 32GB  | 4m 19s  |

The HSTA flow developed and exercised during the reporting period will be used at ST to consider the impact of process variations during timing verification. The preliminary results are quite encouraging, both in terms of reduced pessimism and reduced turn-around-time.

#### 12.2.3. (Task 2.4) – System Level Statistical Analysis

A SoC comprises high-level components such as processors, memories, accelerators, etc. The large majority of SoCs contains well defined register boundaries between any of these high-level components. We have concluded that the statistical critical timing of the SoC is the maximum of the timing of any of its components, and the statistical energy (for dynamic) and power (for leakage) is the sum of their individual energy/power, we can formalize the statistics of the SoC in base of two stochastic properties:

- The Cumulative Density Functions (CDF) of the maximum value of two stochastic variables is the product of their CDF;

- The Probabilistic Density Functions (PDF) of the sum of two stochastic variables is the convolution of their PDF.

The idea was implemented and benchmarked on a wireless processor with good accuracy and excellent runtime results. Having a complete framework for variability impact propagation of correlated timing and power metrics enables the co-exploration of the design and manufacturing space. These can include technology options, like evaluations the impact of high-k metal gates or high/low Vth devices; manufacturing options, like restricted design rules; circuit options, like threshold voltage assignment in MTCMOS libraries or different circuit architectures; architecture options, like memory organization partitioning versus aggregation.

### 12.2.4. (Task 2.5) – Variation Information Format Framework

A key part to "lube" the complexity and density of information of any variability aware design flow is a "Variability Aware Modelling information format" (VAM IF). Thus imec developed a format that considers connections between five levels of abstraction of modelling or simulation. It defines how variability information must be carried from the one level to the other, and was used throughout the WP's of REALITY.

The format accepts data from WP1 in form of injectors. These are additional circuit elements that model the variability of transistors. This can be done for several transistor types, but also differently degraded transistors. The information format is also capable of storing and retrieving variability data on higher levels, such as the ones worked out in WP2, WP3, WP4, and integrated in WP5, like variable standard cells, memory macros, processor parts, processors or systems thereof. Its application layer allows to graphically publish the variability information in several formats. This is used heavily in almost all workpackages, especially WP6.

Use of resources

| Partner | Planned effort (MM) | Actual effort (MM) |

|---------|---------------------|--------------------|

| UOG     | 0                   | 0                  |

| IMEC    | 2.4                 | 2.4                |

| UNIBO   | 0                   | 0                  |

| ST      | 5                   | 5                  |

| KUL     | 0                   | 0(*)               |

| ARM     | 0                   | 4(**)              |

| TOTAL   | 7.4                 | 11.4               |

<sup>(\*)</sup> KUL had a contribution in WP2 in 2010 but that one has been made free of cost to the project (\*\*) An additional effort has been spent on characterization with VAM to adapt our flow to the needs of WP6. What is more in 2009 we have demonstrated that the SSTA characterization of the cell for local variations was failing. We have done some more investigation on this topic after the release of new tools versions. The team has spent some more time in the SRAM characterization transfer to the production groups.

Deliverable D7.7 Page 21 of 21

#### 12.3. WP3: Mixed mode countermeasures (WP leader: KUL)

In this work package, an advanced reliability simulation technique including process variability in the simulation flow was developed. Also, with the availability of the 32nm compact models, an extra iteration on the KUL SRAM memory has been done. The reliability simulation framework has been applied to one cell of the KUL memory (full memory analysis is performed by the MemoryVAM).

#### Efficient variability-aware reliability simulation

In order to get a computationally efficient solution, a Response Surface Model (RSM) based simulation technique is proposed. In this approach the vast number of computationally intensive simulations needed to perform a Monte-Carlo analysis, is replaced by the evaluation of an analytical model of the circuit. The focus of this work is not to obtain a highly accurate prediction of yield, but to analyze the spatial and temporal reliability of a circuit in a reasonably short time frame. To reduce the simulation complexity the set of design of experiments, used to build the RSM, is divided into two parts. First, a screening analysis with linear complexity provides a linear model and eliminates unimportant design parameters. Then, in a second step, a regression analysis is conducted to model significant non-linearities. Finally, as an output, the analysis tool provides:

- An aged version of the circuit netlist.

- A model for the behavior of any circuit performance parameter as a function of process-variability parameters and circuit age.

- The production yield as a function of circuit age.

- The estimated model error and yield error.

- · A list with circuit reliability weak spots.

When compared to direct Monte-Carlo yield simulation, examples indicate this method to have a simulation speedup ranging from 1 to 3 orders of magnitude, without sacrificing accuracy. The simulation results enable a designer to verify whether his/her circuit will behave according to its specifications over the entire product lifetime. Also, weak spot analysis allows to improve the design or to reduce design margins and to gain extra performance.

Table 1: The reliability analysis technique was validated on a set of 7 analog and digital test circuits. Experiments show fast simulation results (under 10 minutes for all test circuits) with good accuracy (<2% error).

|   | #factors/ | $\overline{arepsilon_{ m ols}}$ | $\sigma_{arepsilon,  m ols}$ | $\hat{\sigma}_{arepsilon, \mathrm{ols}}$ | $\frac{\sigma_{\rm p}}{\sigma_{\varepsilon, { m ols}}}$ | Analysis<br>Time |

|---|-----------|---------------------------------|------------------------------|------------------------------------------|---------------------------------------------------------|------------------|

|   | #NRS      | [%]                             | [%]                          | [%]                                      | ο ε,ois                                                 | [min:sec]        |

| 1 | 5/19      | 0.04                            | 0.57                         | 0.65                                     | 45.9                                                    | 1:28             |

| 2 | 14/43     | -0.31                           | 1.44                         | 1.19                                     | 16.2                                                    | 2:32             |

| 3 | 15/53     | -0.09                           | 0.28                         | 0.46                                     | 74.0                                                    | 3:37             |

| 4 | 27/95     | -0.20                           | 0.41                         | 0.40                                     | 47.4                                                    | 4:46             |

| 5 | 35/121    | 0.14                            | 1.30                         | 1.01                                     | 12.6                                                    | 9:09             |

| 6 | 20/61     | 0.01                            | 0.26                         | 0.26                                     | 94.8                                                    | 2:06             |

| 7 | 141/343   | -0.12                           | 0.98                         | 1.10                                     | 22.3                                                    | 9:46             |

[1]: One-stage Amplifier [Gain]

[2]: LC-VCO  $[V_{osc}]$

[3]: Differential Pair Amplifier [Gain]

[4]: Symmetrical OTA [Offset]

[5]: Ring Oscillator [Frequency]

[6]: AND Gate [Fall Time]

[7]: IDAC [Normalized Output Voltage  $(\frac{V_{out}}{BI})$ ]

Design of variability resilient memory blocks

Deliverable D7.7 Page 22 of 22

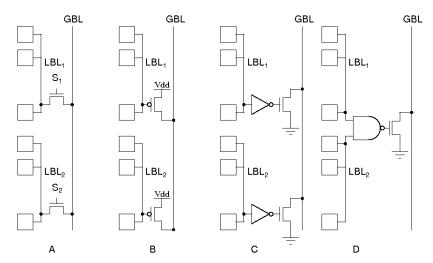

By occupying a major part of the area of current SoCs, memory design is specifically important in the context of variability and reliability. A huge amount of minimal sized cells, of which the functionality of every single one is critical demands big design margins. The most vulnerable parts of a memory were identified to be the cells, the sense amplifiers and the timing.

Cell stability can be increased by reducing the cell load capacitance. For this reason, divided bit lines are introduced. Additional advantages include possible speed and energy gains. A new metric, the transient static noise margin can be used to get a more realistic prediction of the stability. The effect NBTI when increasing the cell voltage has been simulated. It seems to be not negligible, but also not dominant.

Figure 6 Different local bit line architectures

Sharing sense amplifiers result in less variability both due to the reduction in number of SA's as due to the possibility to increase their size with less energy or are penalties.

A configurable timing circuit can be used to counter variability in the timing, but also to adapt the memory control on a die basis to the specific cell and sense amplifier speed thus reducing speed and energy loss due to pessimistic margin design. Low power configurable delay lines were designed for this purpose.

Some estimations of the effect of BEOL-variability have been done. At this moment, these variations do not seem to have a big effect due to the averaging out for the big wires and the small impact of small wires.

A fully functional 1KB SRAM memory with a word length of 32bit was build. Used features include fully divided word lines, divided bit lines, low swing on the global bit lines for read and write, local sense amplifiers, a dynamic x decoder, high threshold voltage cells, shared global sense amplifiers etc. The obtained speed was 1GHz. Total write energy was 0.69pJ, read energy was a bit higher: 1.07pJ.

| Use of | resour | ces |

|--------|--------|-----|

|--------|--------|-----|

| Partner | Planned effort (MM) | Actual effort (MM) |

|---------|---------------------|--------------------|

| UOG     | 0                   | 0                  |

| IMEC    | 0                   | 0                  |

| UNIBO   | 0                   | 0                  |

| ST      | 0                   | 0                  |

| KUL     | 11                  | 10.8               |

| ARM     | 0                   | 0                  |

| TOTAL   | 11                  | 10.8               |

#### 12.4. WP4: System level countermeasures (WP leader: UNIBO)

Deliverable D7.7 Page 23 of 23

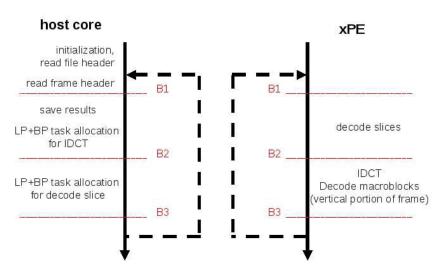

During the reporting period M25-M32 the activity of WP4 was completed in M27. The final deliverable D4.3 was submitted to the EC. In this deliverable UNIBO reported the optimization of the policies on the target platform. The selected benchmark where the optimization has been performed is a multithreaded MPEG2 video decoder, ported to the target platform as part of the activity in WP6 in collaboration with ST.

ST and Unibo have been tuning the SW control algoritms for system level variability management adjusting both the model implementation in the simulation platform and the definition of the SW task scheduling policies to better adapt to the outcomes of the benchmarking campaign performed in WP6. The work has revolved around refinements of the implementation and choice of parameters associated to the BP\_LP and other policies, integration of the performance monitoring blocks parameters validation results (leakage meter, speed meter, temperature sensor), and thermal modelling.

The application is composed of three parts: a control part which scans the current frame, a slice decoding, and an inverse discrete cosine transform (IDCT). There is also a fourth step, performed after the decoding of each frame, associated with the commit of results. We modified the program so that the scan of the current frame is performed by the GPE, the slice decoding and the IDCT can be parallelized and executed on a generic number of xPEs, and the commit of results is performed by the GPE.

The slice decoding and the IDCT have been divided in independent tasks whose number can be equal or greater than the number of xPEs. Regarding the latter case, a dispatcher has been implemented on the host core to schedule the different tasks on the xPEs. To increase performances we further modified the code to execute the commit of the previous frame during the execution of the current frame on the xPEs. The task execution model is shown in Figure XX1, where it is also shown how the task allocation policy, developed in WP4, is applied to the MPEG2 benchmark and optimized.

Figure 7 Task allocation policy applied to the MPEG2 benchmark

More specifically, there are two functions parallelized that are IDCT and decode slice. These two functions generate a number of tasks, which is a parameter. For each of the two functions the task allocation policy (LP+BP) is applied (phases B2 and B3).

The optimization performed on the policy was targeted to make possible the on-line workload allocation on a frame-by-frame basis. In particular, during the processing of a single frame, the policy is applied two times. The first time for the allocation of the tasks performing the parallel slice\_decoding function, and the second time for the allocation of the tasks performing the IDCT function.

Deliverable D7.7 Page 24 of 24

In order to make this possible, we implemented a fast version of the LP algorithm. This allows to reduce the computation time of the LP part of the policy, making it possible to be executed during frame decoding. Another optimization was performed on the BP part of the policy. Here we implemented a new customized version which has the objective of improving the deadline miss rate with respect to the original one. The customized version exploits the information about time constraint, explicitly provided by the application or by the user, to allocate the tasks on the processors. The original implementation of the bin packing algorithm does not take this information into account, while it tries to minimize the exceeding cycles when fitting a task into a core.

We performed our tests on the variability-aware platform simulator developed with ST microelectronics and characterized using the variability models generated by VAM (see D4.3). The results reported in D4.3 have demonstrated firstly that the proposed policy have a negligible run-time overhead and thus it can be applied online. Secondly, they allow to compensate the effect of variability on the quality of service (i.e. number of missed frames) and that they improve reference state-of-the art policies, providing better quality and more predictability across degraded platforms. Finally, the proposed policy achieves this results while minimizing the energy consumption.

Table 2 Fraction of deadline misses caused by the various policies for different number of tasks for the slice decoding and IDCT functions.

|         | RANDOM | RANK FREQ | RANK POWER | LP+BP |

|---------|--------|-----------|------------|-------|

| 4-task  | 1.00   | 0.40      | 0.88       | 0.40  |

| 8-task  | 0.00   | 0.00      | 0.00       | 0.00  |

| 12-task | 0.12   | 0.00      | 0.00       | 0.00  |

Table 3 Energy consumption for different number of tasks for the slice decoding and IDCT functions.

|         | RANDOM | RANK FREQ | RANK POWER | LP+BP |

|---------|--------|-----------|------------|-------|

| 4-task  | 0.69   | 0.50      | 0.62       | 0.50  |

| 8-task  | 0.78   | 0.75      | 0.76       | 0.59  |

| 12-task | 0.77   | 0.75      | 0.75       | 0.55  |

A summary of these results are reported in Table XX1 and XX2. In the rows there are different level of parallelism for each kernel of the MPEG2 application, while on the columns we compared the proposed policy (LP+BP) with competitors (RANK FREQ and RANK POWER) and a random allocation. Figure XX1 reports performance results in terms of deadline misses, while Figure XX2 in terms of energy consumption. It can be seen that LP+BP result in frame misses only with 4 tasks. This result is because of the too low parallelism, indeed all the other policies have the same or worse results. On the other side, the proposed policy consistently reduces the energy consumption.

Use of resources

| Partner | Planned effort (MM) | Actual effort (MM) |

|---------|---------------------|--------------------|

| UOG     | 0                   | 0                  |

| IMEC    | 0                   | 0                  |

| UNIBO   | 0.25                | 7(*)               |

| ST      | 2                   | 2                  |

| KUL     | 0                   | 0                  |

| ARM     | 0                   | 0                  |

| TOTAL   | 2.25                | 9                  |

<sup>(\*)</sup> The actual number of actual MMs effort is for UNIBO higher than initially planned because we used much more junior resources than expected that resulted in more PMs. As a consequence, there is not impact on the budget.

Deliverable D7.7 Page 25 of 25

# 12.5. WP5: Design flow, integration, proof of concept (WP leader: ARM)

No summary available. These work package activities have been completed during the earlier reporting period.

## Use of resources

| Partner | Planned effort (MM) | Actual effort (MM) |

|---------|---------------------|--------------------|

| UOG     | Not Applicable (NA) | NA                 |

| IMEC    | NA                  | NA                 |

| UNIBO   | NA                  | NA                 |

| ST      | NA                  | NA                 |

| KUL     | NA                  | NA                 |

| ARM     | NA                  | NA                 |

| TOTAL   | NA                  | NA                 |

Deliverable D7.7 Page 26 of 26

# 12.6. WP6: Validation and assessment of results (WP leader: ST)

#### Task 6.4:

Although this task completed in the past reporting period, certain results had to be amended and/or augmented from what reported in D6.3. Further simulation and analysis were performed as some of the preconditions on the availability of input data become available as part of the activities in WP2, WP4 and WP6. These additional results were reported and included in D6.4.

In particular in 2010 Imec (free of effort) together with ARM has invested significant effort amending and extending some of the results reported earlier in D6.3 in a clearer and more explicit way. This has involved performing a whole new set of statistical characterization jobs for library characterization (ARM), memory characterization (imec) and processor core characterization (imec). The reason is the block level evaluation report as specified by the validation plan (D6.3) was approved on condition that deficiencies will be corrected in this report. In concrete we have:

- Provided imec's statistical memory characterization tool and supported its use to clarify the sources for ARM's and KUL's memory performance mismatches.

- Performed characterization runs of our tools in validation conditions (e.g., temperature, voltage and process) not reported in D6.3 applicable to the synthesis and analysis of the block-level test vehicle.

- Provided additional characterization runs for an assessment of the variability degradation at the level of the system's building block (ARM926) for the case 0.9C 125C (thus, worst case conditions). We have used strongly aged variability injector models (trap concentration of 1x10<sup>12</sup>cm<sup>-2)</sup> which influences local random variability while process-dependent global variability remains constant. The results point to non notable effects in timing, leakage and/or dynamic energy variability under ageing. We conclude that ageing impact on timing and/or power deviations on the statistical response of the core using high-K metal gate devices is at 32nm negligible.

In addition Imec has in 2010 provided (free of effort) an analysis of project results impact for selected industrial scenarios. In concrete it has quantified the impact of memory variability within a system, concluding that SRAM components are responsible for more than the half of the variations on critical path timing. Hence, Statistical Timing Analysis (SSTA) flows that assume predictable timing response from these components lead to over-optimistic conclusions. Much focus has been placed by both state-of-the-art and EDA vendors on the logic while the variability challenges remain in the memories themselves. For that purpose REALITY has been first in deploying a holistic statistical characterization flow including SRAM analysis.

Of course must be noted that a skilled memory designer is aware of variability and sets additional margins to the device library corners to ensure safe operation and good yield. However, the amount of this extra margins can be quantified using the REALITY approach, whereas the state of the art is based on design adaptations after first silicon feedback. Imec has quantified that the amount of (as always, measured at 3sigma=99.9%) optimism when neglecting the mismatch of the memories is about 7% of the clock period. The TT point is at 93% which means we have to provide 13.5% additional safety margin to capture memory and logic variability (6.5% if we only take logic into account). Hence the different between considering or not variability impact on memories is about 50% for local random variations. In the context of total variation (including the global component), this range becomes 20%.

In WP6 KUL analyzed the impact and reported on research conducted in WP3.1 that resulted in the development of advanced degradation effect models for hot carrier and NBTI transistor reliability phenomena. Also, an efficient simulation method to emulate the impact of time-varying stress on the operation of an analog circuit was proposed. Simulation results on an example circuit indicated how DC-only reliability simulator can result in large errors on lifetime assessment of analog circuits. In WP3.2 an efficient method to include the impact of process variability in the circuit reliability analysis flow was proposed.

Experiments indicated how process variability interacts with time-dependent reliability effects resulting in time-dependent circuit yield. Usage of commercial reliability simulation tools, not including process variability, can therefore result in a large error on the lifetime estimation

During this last period of the project ARM has put a lot of effort generating the necessary Standard Cells data we needed for an interesting characterization of the ARM926. Variations in the voltage conditions, temperature as well as in the type of models have been done in order to fully cover the variability analysis. The following table shows the list of the characterizations performed.

| Voltage / Temperature | Origin of Models | Type of variations | Justifications     |

|-----------------------|------------------|--------------------|--------------------|

| 0.9V 125°C            | UoG - Fresh      | Local and Global*  | Référence          |

| 0.9V 125°C            | Foundry          | Local              | Analyse Difference |

|                       |                  |                    | from Models        |

Deliverable D7.7 Page 27 of 27

| 0.9V 25°C  | UoG - Fresh | Local and Global* | Temperature Effects |

|------------|-------------|-------------------|---------------------|

| 1.1V 125°C | UoG - Fresh | Local and Global* | Voltage Effects     |

| 0.9V 125°C | UoG - Aged  | Local             | Aging Effects       |

| 0.9V -40°C | UoG - Fresh | Local and Global* | Temperature Effects |

| 1.1V 125°C | UoG - Fresh | Local and Global* | Temperature and     |

|            |             |                   | Voltage Effect      |

<sup>\*</sup>Note that since UoG is focused on local variations the information on global variations are extracted from the foundry models.