#### **E3NETWORK**

Energy Efficient E-band transceiver for backhaul of the future networks

# **DELIVERABLE D.2.2**

# Report on the measurements of the E-Band RF /Analogue Front-end Blocks 1

| Contract number: | 317957                                                                  |  |  |  |

|------------------|-------------------------------------------------------------------------|--|--|--|

| Project acronym: | E3NETWORK                                                               |  |  |  |

| Project title:   | Energy Efficient E-Band Transceiver for Backhaul of the Future Networks |  |  |  |

| Deliverable number:  | D2.2         |

|----------------------|--------------|

| Nature:              | R- Report    |

| Dissemination level: | PU           |

| Report date:         | 23 July 2014 |

| Author(s):            | Iñaki Guruceaga, David del Rio, Roc Berenguer, J.F. Sevillano (CEIT) Jose Luis Gonzalez (CEA-Leti) Wojciech Debski (SiR) Cesar Martinez (INCIDE) |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Partners contributed: |                                                                                                                                                  |  |  |  |

| Contact:              | Dr. Roc Berenguer CEIT Paseo Manuel de Lardizabal 15, San Sebastian (Spain) Telephone: +34 943212800 Fax: e-mail: rberenguer@ceit.es             |  |  |  |

The E3NETWORK project was funded by the European Commission under the 7<sup>th</sup> Framework Programme (FP7) –ICT

**Coordinator: CEIT**

# **VERSION CONTROL**

| Version      | Date       | Contributors                                                                                                             | Sections Affected                     |  |

|--------------|------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|

| 1 26/06/2014 |            | R. Berenguer (CEIT)                                                                                                      | Draft version                         |  |

| 2            | 20/07/2014 | D. del Rio (CEIT) R. Berenguer (CEIT) I. Guruceaga (CEIT) J. L. Gonzalez (CEA-Leti) W. Debski (SiR) C. Martinez (INCIDE) | All sections                          |  |

| 3            | 23/07/2014 | D. del Rio (CEIT)<br>J.F. Sevillano (CEIT)                                                                               | Index of acronyms and Section 6 added |  |

# **INDEX**

Due date: 30 June 2014

| 1. | IN  | TROD                | UCTION ······                                                                                  | • 7              |

|----|-----|---------------------|------------------------------------------------------------------------------------------------|------------------|

|    | 1.1 | Descr               | iption of Tx analogue Front-end······                                                          | ٠7               |

|    | 1.2 | Descr               | iption of Rx analogue Front-end ·······                                                        | • 7              |

|    | 1.3 |                     | iption of signal generation block for Tx and Rx ······                                         |                  |

| 2. | T)  | K RESI              | JLTS                                                                                           | . 9              |

|    | 2.1 | Undat               | ed Power Amplifier results······                                                               | . 9              |

|    |     | 1.1.                | Circuit description·····                                                                       | . 9              |

|    |     | 1.2.                | Results                                                                                        | 12               |

|    | 2.2 | Updat               | ed mmW Mixer results······                                                                     | 17               |

|    |     | 2.1.                | Circuit description                                                                            |                  |

|    |     | 2.2.                | Results                                                                                        |                  |

|    | 2.3 | mmW                 | Tx module (mmW mixer & PA) results  Circuit description                                        | 23               |

|    |     | 3.1.<br>3.2.        | Results                                                                                        | 23               |

|    |     |                     | ed IF Mixer results ·····                                                                      |                  |

|    |     | 4.1.                | Circuit description·····                                                                       | 26<br>26         |

|    |     | 4.2.                | Results ·····                                                                                  |                  |

|    | 2.5 | Tx IQ               | Modulator results······                                                                        |                  |

|    | 2.5 | 5.1.                | Circuit description                                                                            | 36               |

|    | 2.5 | 5.2.                | Results                                                                                        | 37               |

| 3. | R   | X SIMU              | JLATION RESULTS ····································                                           | 45               |

|    | 2.4 | lindat              | ed LNA results ······                                                                          | <i>1</i> E       |

|    | 3.1 | - υραατ<br>1.1.     | Circuit description                                                                            | 45<br>45         |

|    | _   | 1.1.                | Results ······                                                                                 |                  |

|    | _   | 1.3.                | Comparison of simulation results with specifications in D1.2.2 ·····                           |                  |

|    | 3.2 | Updat               | ed IFA results······                                                                           | 51               |

|    | -   | 2.1.                | Circuit description                                                                            |                  |

|    | _   | 2.2.                | Results                                                                                        |                  |

|    |     | 2.3.                | Comparison of simulation results with specifications in D1.2.2 ······  Receiver results ······ | 59               |

|    | 3.3 | <b>mmvv</b><br>3.1. | Circuit description                                                                            |                  |

|    |     | 3.1.<br>3.2.        | Results ·····                                                                                  |                  |

|    |     |                     |                                                                                                |                  |

| 4. | SI  | GNAL                | GENERATION RESULTS                                                                             | 66               |

|    | 4.1 | PLL lo              | oop optimization·····                                                                          | 66               |

|    | 4.2 | Updat               | ed IF LO generator results ······                                                              | 69               |

|    | 4.3 | I/Q ge              | nerator ·····                                                                                  | 70               |

|    | 4.4 | Updat               | ed mmW LO generator results·······                                                             | 71               |

|    | 4.5 | mmW                 | LO two tones generator based on a mixer ······                                                 | 74               |

|    | 4.6 | Overa               | Il Signal Generator Results ······                                                             | 76               |

| 5. | D   | AC & A              | ADC RESULTS ······                                                                             | 81               |

|    | 5.1 |                     |                                                                                                |                  |

|    |     | 1.1.                | Circuit description·····                                                                       | <b>ი I</b><br>გ1 |

|    |     | 1.1.                | Results ·····                                                                                  |                  |

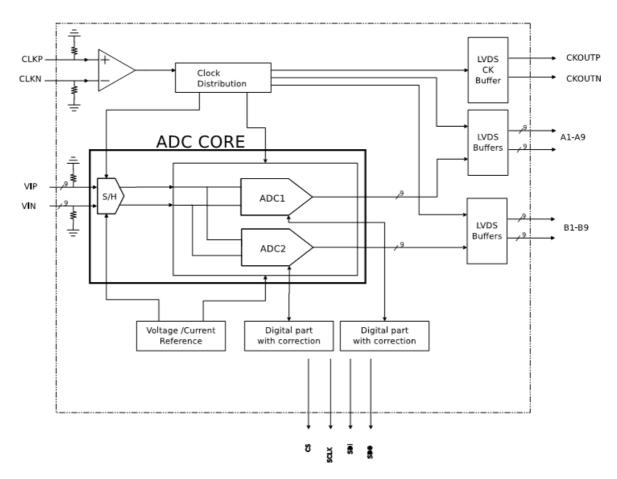

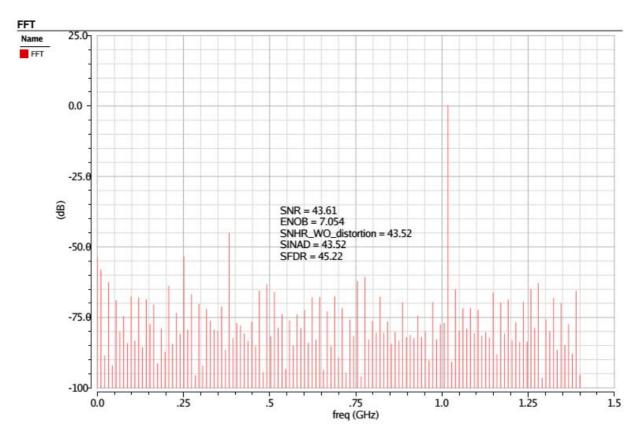

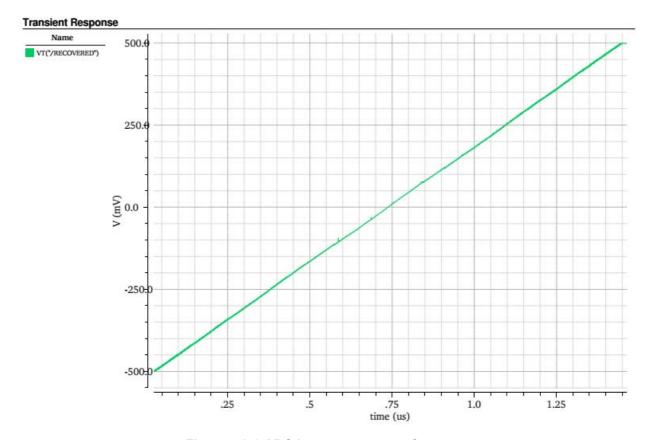

|    | 5.2 | ADC.                |                                                                                                | 87               |

|    | -   |                     | Circuit description                                                                            | 87               |

|    | 5.2 | 2.2.                | Results ····                                                                                   | 88               |

| 6. | S   | YSTEM               | I LEVEL SIMULATION······                                                                       | 91               |

|    | _   |                     |                                                                                                |                  |

| 7. | E   | ARLY | PROTOTYPE OF IF TRANSCEIVER······                                     | 92   |

|----|-----|------|-----------------------------------------------------------------------|------|

|    |     |      | tecture description ······ts ······ts                                 |      |

|    | 7.2 |      |                                                                       |      |

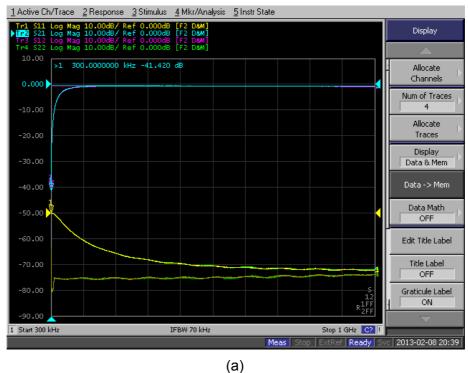

|    | 7.2 | 2.1. | Base Band Low Pass Filters · · · · · · · · · · · · · · · · · · ·      |      |

|    | 7.2 | 2.2. | Base Band Attenuators·····                                            | . 95 |

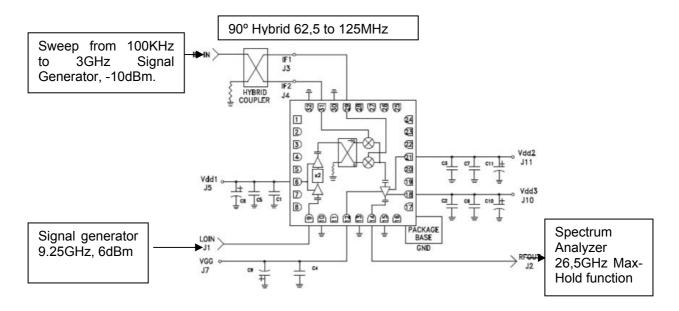

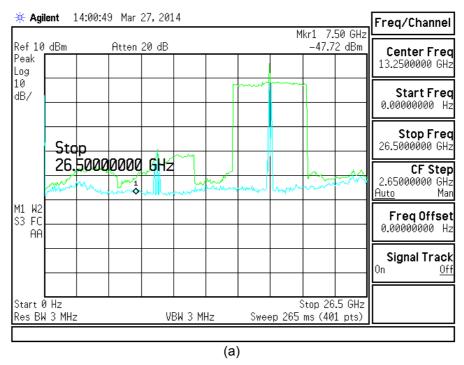

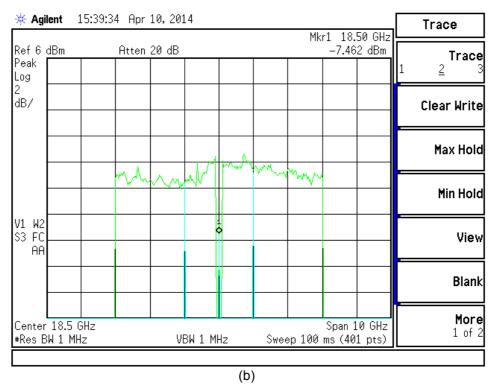

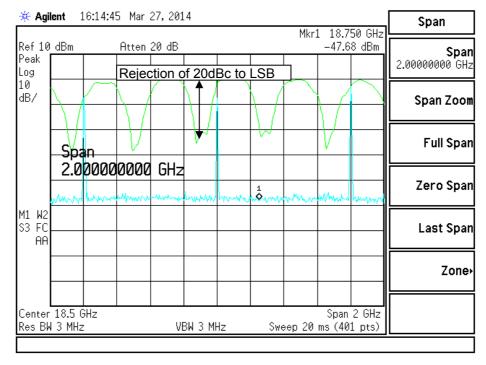

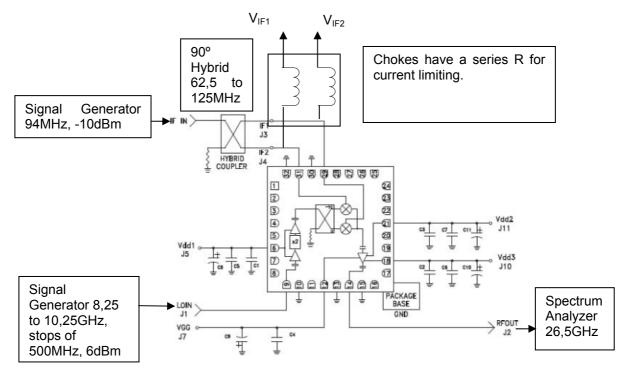

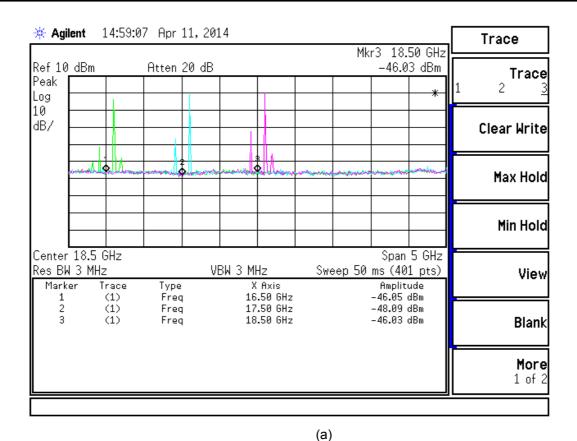

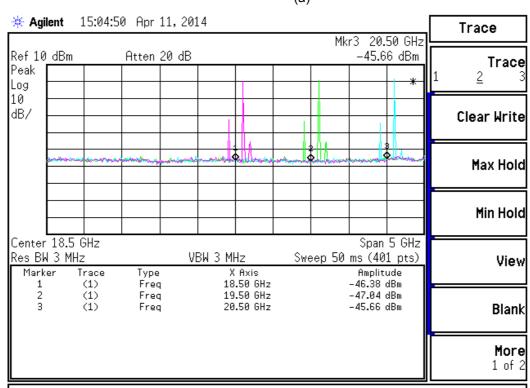

|    | 7.2 | 2.3. | I/Q UPCONVERTER 16 - 21GHz BAND ······                                | . 97 |

|    | 7.2 | 2.4. | 16 to 21GHz Band Pass Filter                                          |      |

|    | 7.2 | 2.5. | 16 to 21GHz Attenuator · · · · · · · · · · · · · · · · · · ·          |      |

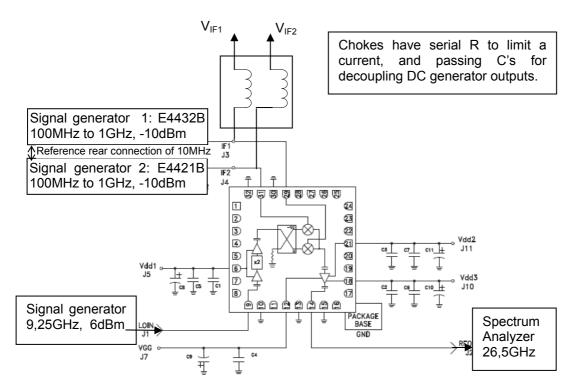

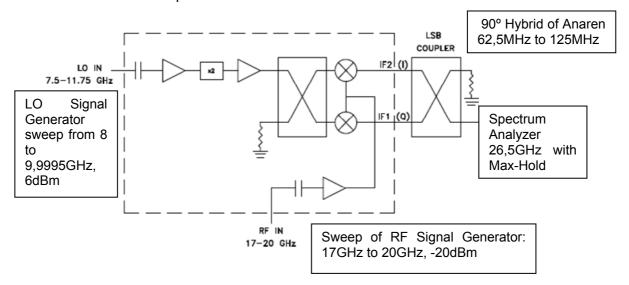

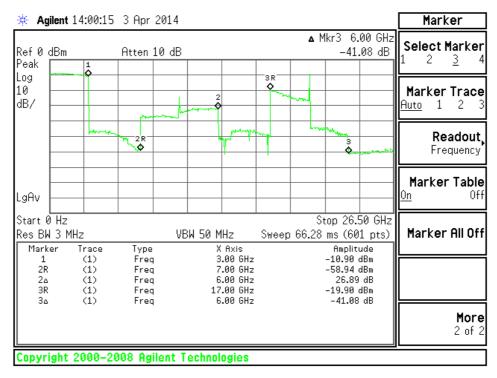

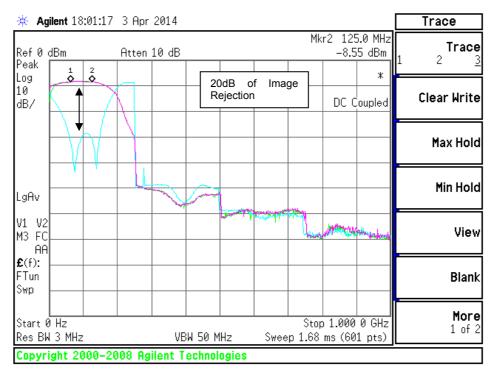

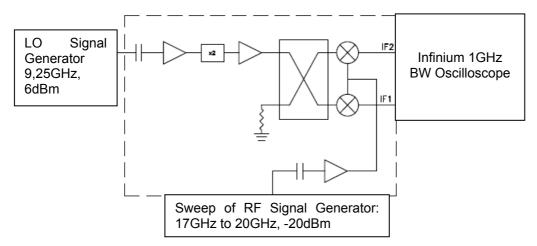

|    | 7.2 | 2.6. | Down-Converter characterization · · · · · · · · · · · · · · · · · · · | 107  |

| 8. | C   | ONCL | USIONS                                                                | 110  |

#### INDEX OF ACRONYMS

- · ADC: Analog to digital converter

- · BGA: Ball grid array

- BW: Bandwidth

- · CE: Common emitter

- · DAC: Digital to analog converter

- DNL: Differential nonlinearity

- EM: Electromagnetic

- . ENOB: Effective number of bits

- ESD: Electrostatic discharge

- FMC: FPGA Mezzanine Card

- FPGA: Field programmable gate array

- · FS: Frequency synthesizer

- · HGM: High gain mode

- I/O: Input / Output

- I/Q: In-phase / Quadrature

- · IF: Intermediate frequency

- IFA: Intermediate frequency amplifier

- ILO: Injection-locked oscillator

- INL: Integral nonlinearity

- IRR: Image rejection ratio

- · LGM: Low gain mode

- LNA: Low-noise amplifier

- LO: Local oscillator

- LVDS: Low-voltage differential signaling

- MDAC: Multiplying digital to analog converter

- mmW: Millimeter wave

- MN: Matching network

- MOM: Metal-Oxide-Metal

- NF: Noise figure

- OCP1dB: Output 1dB compression point

- PA: Power amplifier

- PAE: Power-added efficiency

- · PCB: Printed circuit board

- · PDK: Process design kit

- PFD: Phase frequency detector

- PLL: Phase-locked loop

- PLS: Post layout simulation

- PN: Phase noise

- PTAT: Proportional to absolute temperature

- QAM: Quadrature amplitude modulation

- · Rx: Receiver

- SFDR: Spurious-free dynamic range

- · SINAD: Signal-to-noise and distortion ratio

- SPI: Serial peripheral interface

- Tx: Transmitter

- VCO: Voltage-controlled oscillator

#### **EXECUTIVE SUMMARY**

This document presents simulation results of the re-designed building blocks of the analogue transmitter and receiver front-ends. These results show that most of the specifications of these building blocks in the updated D1.2.2 document are fulfilled. Furthermore, a much lower DC power consumption than in other commercial solutions is observed.

In the transmitter part, the IF I/Q modulator, PA and mmW up-converter mixer have been redesigned. Within the receiver, the LNA, IF amplifier and mmW down-converter mixer have been redesigned. Simulation results of all these blocks are provided within this document. Moreover, simulation results of the re-designed frequency synthesis blocks are presented.

For the converters, a testing platform for the designed digital-to-analogue converter has been built. This document shows the signal integrity analysis performed for this board. Additionally, the designed ADC is described and some simulation results of the ADC presented.

Finally, system simulations have been performed with the specifications updated in D1.2.2. This document shows that the performance of the system keeps fulfilling the required specifications.

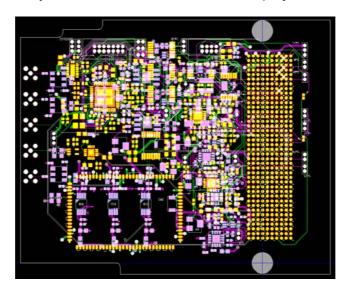

Within WP2, an early prototype of the IF circuitry, based on discrete components, has been designed and implemented. This early prototype includes both the IF I/Q modulator and demodulator. This IF prototype will be employed by WP3 to test their digital base-band processor and the parameter and estimation controller. This document presents measurement results of these early IF prototype.

#### 1. INTRODUCTION

# 1.1 Description of Tx analogue Front-end

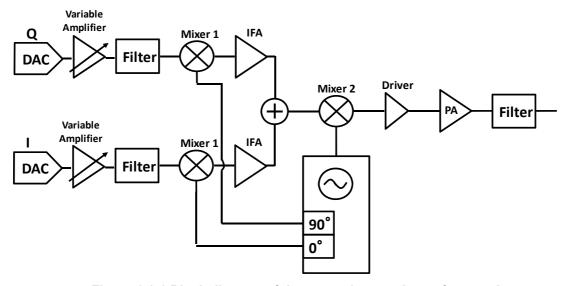

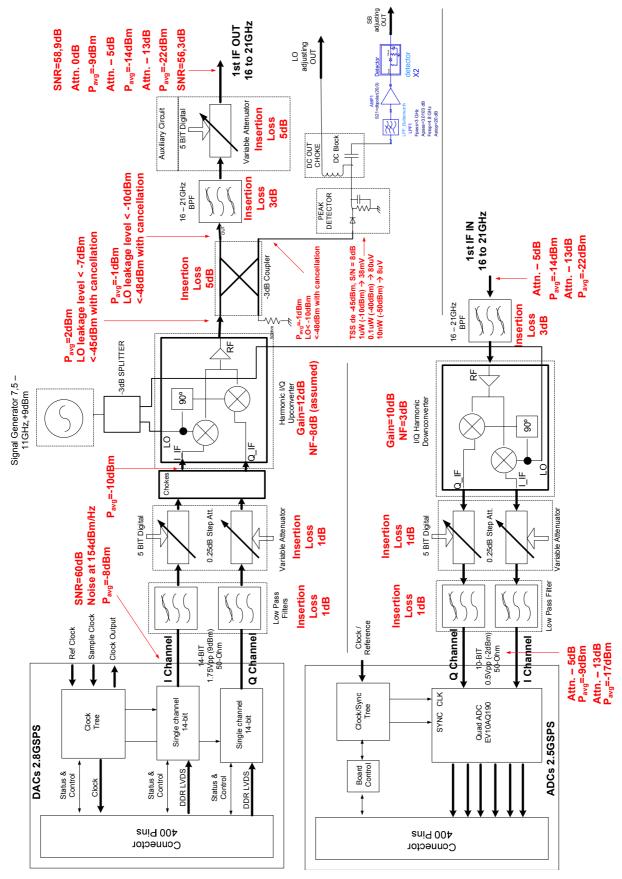

The architecture of the analogue transmitter, with the block diagram shown in Figure 1.1-1 was described in deliverable D2.1. Some of the blocks have been re-designed to fulfil the specifications for the correct system performance. The design and performance of such blocks will be presented over the document.

Figure 1.1-1 Block diagram of the transmitter analogue front-end

# 1.2 Description of Rx analogue Front-end

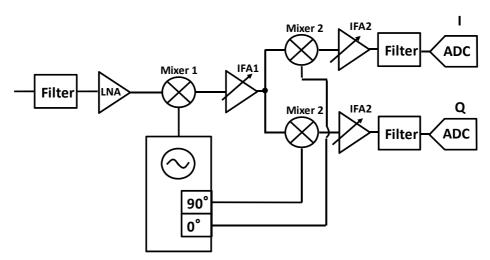

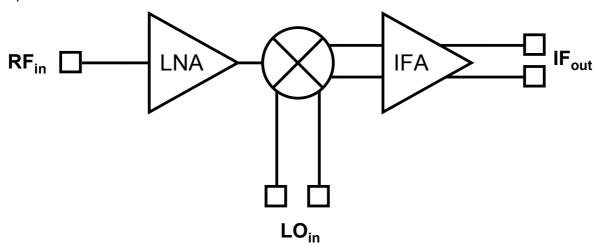

The architecture of the RF-analogue reception chain was presented in deliverable D1.2. Figure 1.2-1 shows the block diagram of the receiver which is a two-stage down-conversion architecture. The parameters of the receiver blocks were defined in the previous project phase and reported in D2.1.

Figure 1.2-1 Block diagram of the receiver analogue front-end

# 1.3 Description of signal generation block for Tx and Rx

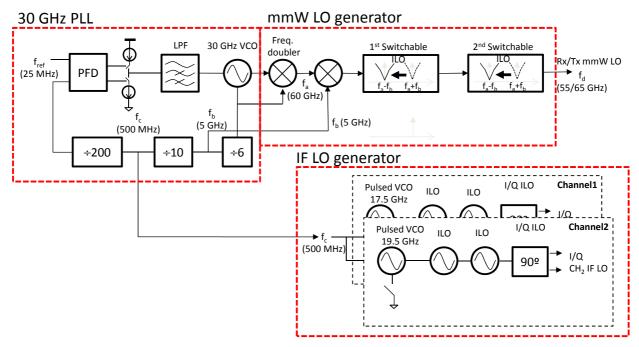

The signal generator block for Tx and Rx is composed of three subsystems: a PLL based on a 30 GHz VCO and a 25 MHz input reference, an IF LO signal generator and a mmW LO signal generator. Its block diagram is shown in Figure 1.3-1.

Figure 1.3-1 Block diagram of the E3Network signal generator block

The mmW LO generator is composed of a frequency doubler to obtain a 60 GHz frequency signal and a mixer that using an intermediate frequency output of the PLL at 5 GHz generates a two tone signal containing the two possible mmW LO frequencies: 55 GHz and 65 GHz. A chain of two switchable ILOs is used to select the desired frequency to be provided to the Tx or the Rx in order to address the lower or upper part of the E-band.

The IF LO generator uses an intermediate frequency of 500 MHz provided by the PLL to generate a multi-harmonic signal containing the desired IF LO frequency. This signal is filtered by a chain of two ILOs and I/Q signals are generated using a wideband poly-phase filter.

Due date: 30 June 2014

#### 2. TX RESULTS

# 2.1 Updated Power Amplifier results

## 2.1.1. Circuit description

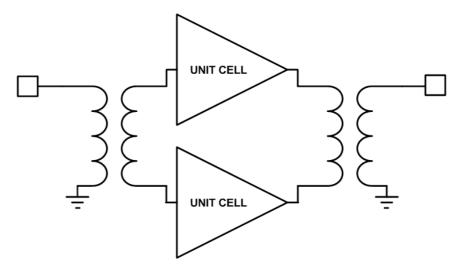

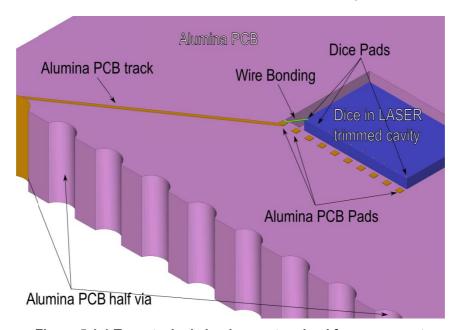

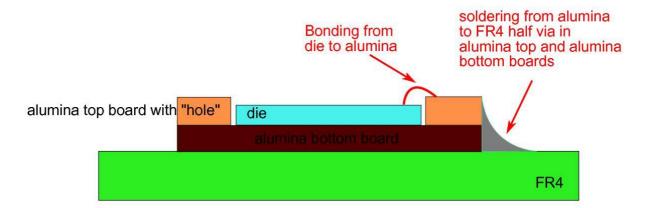

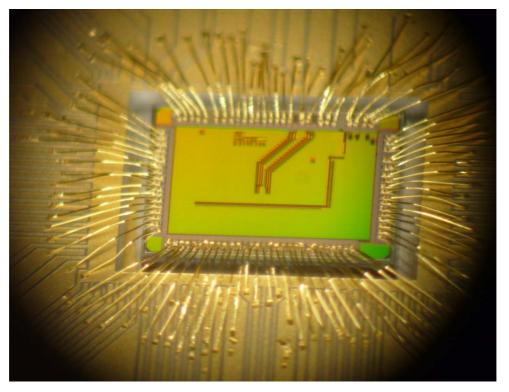

The circuit consists of two identical unit cells, combined at the output using an integrated balun to provide a single-ended output, as shown in Figure 2.1-1. Additionally, a balun is also added at the input, so that on-wafer measurement of the standalone power amplifier (PA) can be performed using a single-ended probe.

Figure 2.1-2 shows the schematic of each of the unit cells, with all the power cells and matching networks. They consist of 5 CE stages in addition to one pre-driver in cascode configuration placed at the input, which provides enough gain to the device and drives it to compression before the previous blocks (such as the up-conversion mixer) compress.

Each power cell is made of very high speed npn bipolar transistors, with bigger emitter areas towards the amplifier output to achieve better power handling capability and smaller sizes at the input to increase the efficiency and to achieve a higher input impedance, thus making the impedance matching easier. The total emitter area of the output stage ( $6^{th}$  stage) is 24  $\mu$ m², which is reduced in 25% at the 5<sup>th</sup> and 4<sup>th</sup> stages. Another reduction of 12.5% is performed for stages 2<sup>nd</sup> and 3<sup>rd</sup>, whereas the transistors of the 1<sup>st</sup> cascode stage have emitter areas of 5.2  $\mu$ m², with a further reduction of 58.5%. These areas are divided into various parallel cells.

Parallel R-C networks are placed at the input of the last 4 CE stages in order to introduce losses at low frequencies and ensure inter-stage stability, which is necessary due to the feedback effect produced by the parasitic capacitances of big transistors. As for the 1<sup>st</sup> CE stage, stability is ensured by placing a  $1K\Omega$  resistor between both differential cells at the output of the driver.

Figure 2.1-1 Block diagram of the PA architecture

Figure 2.1-2 Simplified schematic of each PA unit cell

With regard to the impedance matching, the output balun is designed so that it presents the optimum impedance for maximum output power to the output stage, when a 50  $\Omega$  termination is placed at the output in parallel to the capacitance of the pad. Input matching is achieved using a distributed matching network at the input of the driver, so as to present a 50  $\Omega$  input impedance to a probe connected to the input pad. Inter-stage matching networks are also implemented using distributed elements and are designed to provide gain flatness over the E-Band and enough output compression power, as well as to present low impedances to the bases of the transistors, which is necessary for reliable operation above  $BV_{CEO}$ .

All the transmission lines are implemented as side-shielded microstrip lines, using the top ultrathick metal for the main conductor and stacking the first 2 metals to provide the GND plane. Regarding the capacitors, interdigitated MOM capacitors are constructed using the top thick metals and a GND shield with the first 2 metals, so as to achieve higher Q factors at mm-wave frequencies than with the MOM capacitors provided with the PDK.

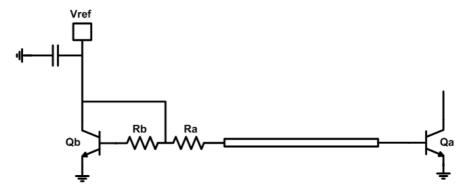

A VCC value of 1.8 V is selected, which provides a balance between safe operation above  $BV_{CE0}$  and enough voltage swing at the output for the required 1dB compression point. The different stages are independently biased using simple PTAT current mirrors, as the one shown in Figure 2.1-3, with a mirror ratio of 15:1 to minimize current consumption and increase the efficiency. Additionally, the resistor Ra is chosen small enough (~30 $\Omega$ ) to allow for safe operation at VCC >  $BV_{CE0}$ , whereas the bias circuit is isolated from the circuit at mm-wave frequencies by using a long transmission line for the connection. VCC and the voltage reference Vref for each stage are set externally in order to compensate for temperature and process variations and to adjust the total gain of the amplifier if necessary.

Figure 2.1-3 Schematic of a PTAT current mirror

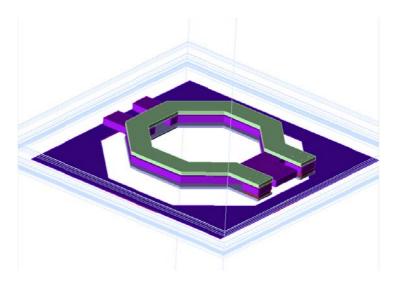

Figure 2.1-4 3D view of the implemented transformer balun

As explained before, an integrated octagonal transformer balun is used to convert the differential output to single ended. Figure 2.1-4 shows its 3D view as introduced in the EM simulator. The primary is implemented using a single turn in M8, whereas the secondary is made using single M7 and AP turns connected in parallel. Thus, the primary is surrounded at both its upper and lower sides by the secondary and the coupling is maximized, whereas the lower turn provides shielding to the primary, which is the turn with a higher current. A balun with the same structure is used at the input for testing purposes.

The final layout of the PA block occupies an area of 1692 x 924  $\mu m^2$  and is shown in Figure 2.1-5. All the path widths and vias are designed to fulfil the electromigration and maximum current limits at 125 °C.

Figure 2.1-5 Layout of the PA, including PADs

#### 2.1.2. Results

All the results presented in this section are based on post-layout simulations, in which the passive structures such as transmission lines, capacitors, baluns and interconnections have been EM simulated using *Agilent Momentum* and the transistors layouts are extracted with the RCc PLS tool included with the PDK.

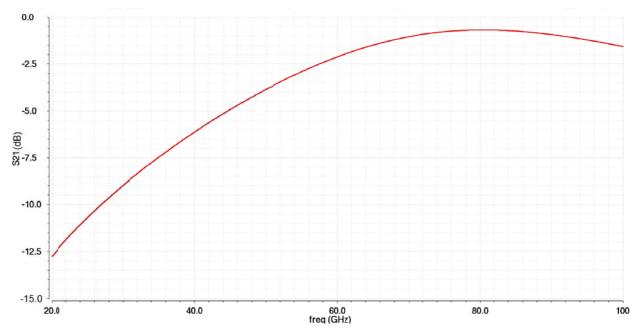

The insertion loss of the output balun has been simulated standalone, and is shown in Figure 2.1-6. As it can be observed, it has a minimum loss of 0.7 dB at the centre of the E-Band and is less than 1.5 dB across the band of interest.

Figure 2.1-6 Simulated insertion loss of the output balun

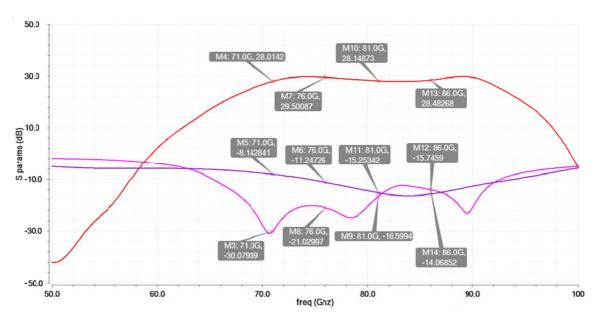

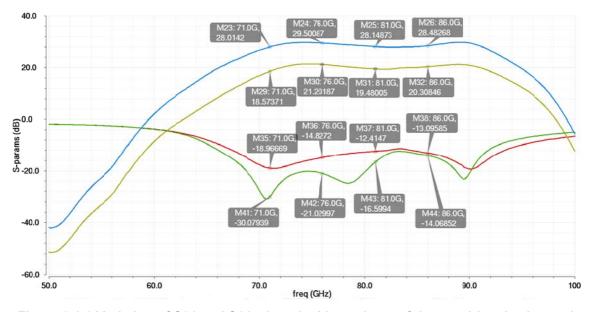

Regarding the complete PA, Figure 2.1-7 shows the simulated S-parameters with the exception of S12, which is <-80dB and, thus, does not fit into the plot. As it can be observed, the S21 parameter has a 3-dB bandwidth of 70 - 91.8 GHz, with a maximum value of 29.8 dB at 89 GHz and a gain flatness better than 1dB across 2 GHz channels. The input matching is better than -10 dB from 65 GHz to 92 GHz and the output matching is better than -10dB from 74 GHz to 94 GHz, with a value better than -8.14 dB at the lower part of the E-Band (71-74 GHz).

In addition, the gain of the PA can be adjusted by changing the bias voltage of the pre-driver. As it is shown in Figure 2.1-8, a variation bigger than 8 dB in the S21 can be achieved, while the input matching is not significantly degraded.

Due date: 30 June 2014

Figure 2.1-7 Simulated S-parameters of the PA

Figure 2.1-8 Variation of S21 and S11 when the bias voltage of the pre-driver is changed

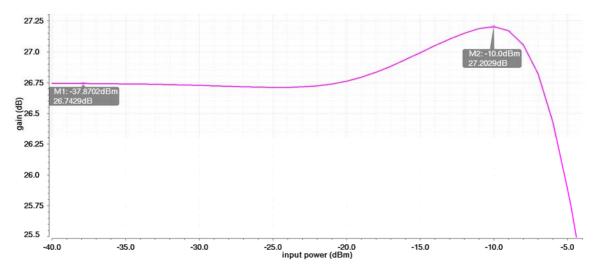

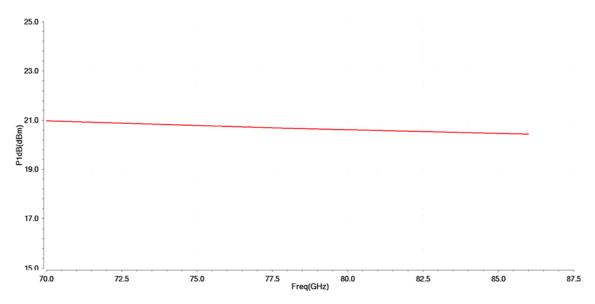

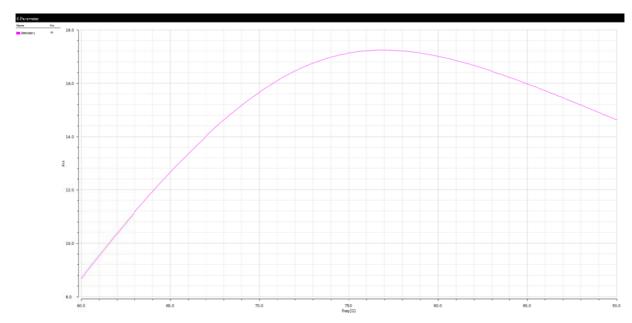

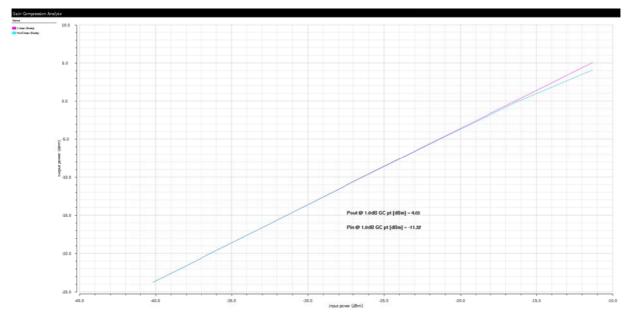

As for the gain compression, Figure 2.1-9 shows the simulated power gain as a function of the input power at 71 GHz. As it can be observed, the gain increases before reaching compression, which pushes the 1dB compression point towards the saturation point (there is only a round 1dB difference between both values). This effect increases the output 1-dB compression point, which is shown in Figure 2.1-10 for the whole band of interest. A maximum value of 21 dBm is obtained at the lowest part of the E-Band, whereas it is bigger than 20.4 dBm at the highest frequencies. 1dB can be added to these values to obtain the saturation point.

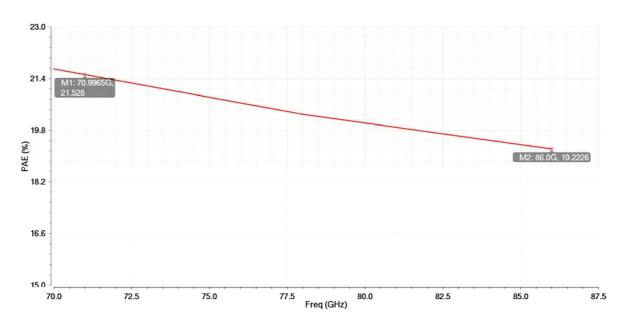

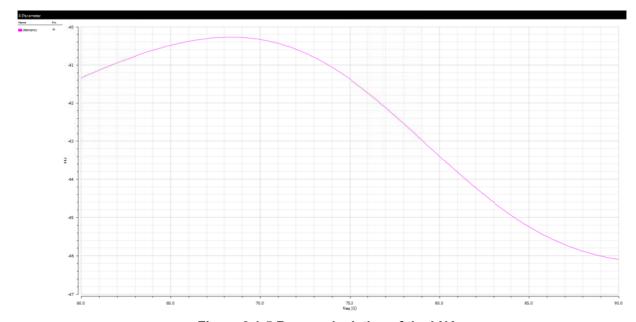

Regarding the efficiency, the PAE is simulated at compression and plotted in Figure 2.1-11. It has a peak value of 21.53 % at 71GHz and a minimum value of 19.22 % at 86 GHz, for the simulated DC power consumption of 575 mW.

Figure 2.1-9 Simulated PA power gain as a function of Pin at 71 GHz

Figure 2.1-10 Simulated OCP1dB of the PA as a function of frequency

Figure 2.1-11 Simulated PAE of the PA at compression as a function of frequency

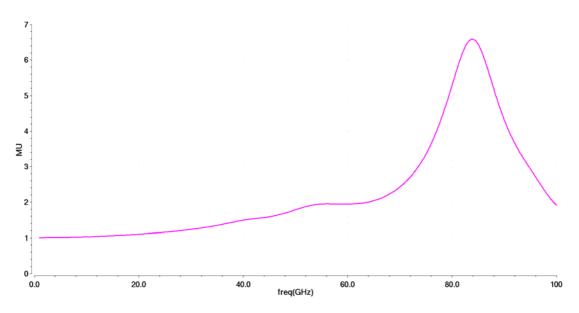

The stability of the PA is also simulated, obtaining the  $\mu$  factor shown in Figure 2.1-12. A  $\mu$  factor bigger than 1 is obtained for all frequencies, which ensures the unconditional stability of the amplifier.

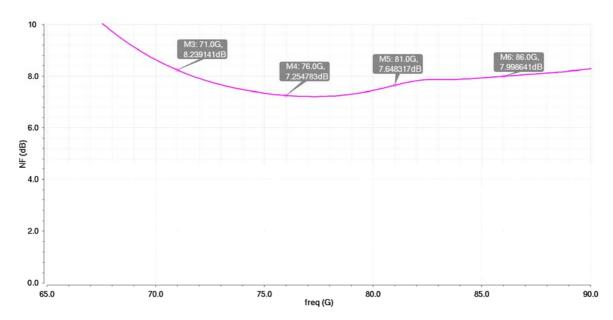

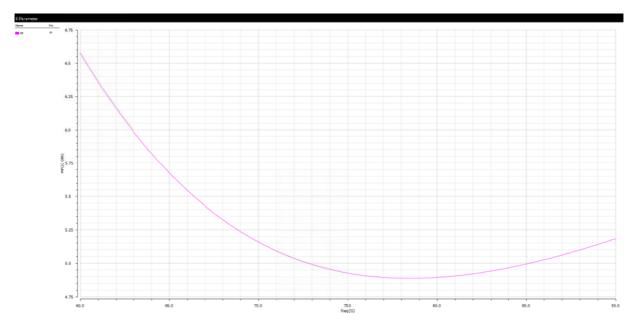

In addition, the noise figure is plotted in Figure 2.1-13, and has a maximum value of 8.24 dB at 71 GHz and a minimum value of 7.25 dB at 76 GHz.

Figure 2.1-12 Simulated  $\mu$  stability factor of the PA as a function of frequency

Figure 2.1-13 Simulated NF of the PA

The main results of the simulations are given and compared with those in deliverable D1.2.2 in Table 2.1-1.

| Parameter   | Min.<br>Value¹ | Max.<br>Value <sup>2</sup> | Spec. in D1.2.2   | Comments        |

|-------------|----------------|----------------------------|-------------------|-----------------|

| 001         |                |                            | 00 15             | 0 (15)          |

| S21         | 28.01 dB       | 29.5 dB                    | 28 dB             | Spec. fulfilled |

| 3-dB BW     | 70 Ghz         | 91.8 GHz                   | 70-76 / 81-86 GHz | Spec. fulfilled |

| S11         | -30 dB         | -12 dB                     | < -10 dB          | Spec. fulfilled |

| P1dB        | 20.4 dBm       | 21 dBm                     | 18 dBm            | Spec. fulfilled |

| DC power    | -              | 575 mW                     | -                 |                 |

| PAE at P1dB | 19.22 %        | 21.53 %                    | -                 |                 |

| NF          | 7.25 dB        | 8.24 dB                    | 8.5 dB            | Spec. fulfilled |

| VCC         | -              | 1.8 V                      | -                 |                 |

| Area        | -              | 1.56 mm <sup>2</sup>       | -                 |                 |

Table 2.1-1 Summary of simulation results for the power amplifier

<sup>1 2</sup> Min. and Max. Values refer to values inside the E-Band (71-76, 81-86 GHz).

# 2.2 Updated mmW Mixer results

## 2.2.1. Circuit description

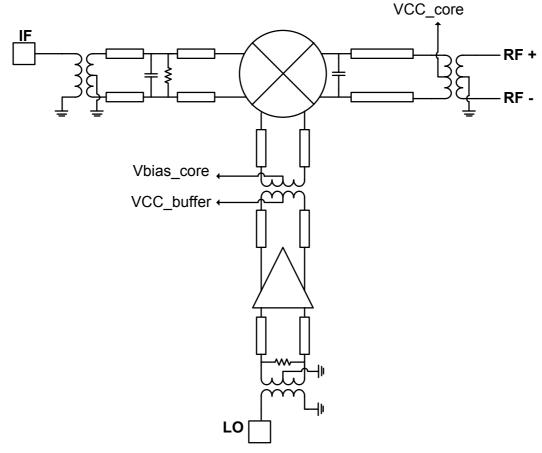

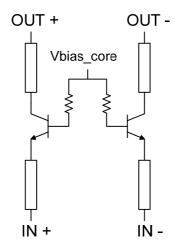

The mm-wave up-converter mixer circuit, shown in Figure 2.2-1, consists of a double-balanced mixer core and a buffer connected at the LO input of the core to drive it with more power than the typically provided by the mm-wave LO (around 0 dBm or less). Centre-tapped transformers are used to electrically isolate the LO and RF ports from the rest of the circuit as well as to provide DC biasing.

Additionally, two more transformer baluns are added to provide single-ended inputs at the IF and LO ports, so that on-wafer measurement can be performed. These ports are also matched to 50  $\Omega$ , taking the PAD capacitances into account. A resistor is used for impedance matching at the LO port, whereas a resistor in parallel with a MOM capacitor provided with the PDK are used for matching the IF input. As for the RF output, it is left differential because it will not be measured standalone but connected to the PA. A 50  $\Omega$  load is expected at this point, which is transformed to the optimum impedance for conversion gain and compression of the mixer by a custom-made MOM capacitor placed in parallel with the transformer.

Figure 2.2-1 Block diagram of the mmW mixer

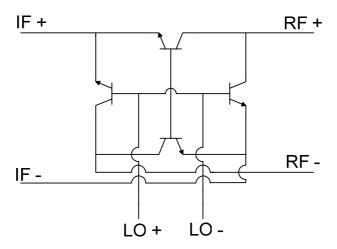

Figure 2.2-2 Schematic of the mmW mixer core

The mixer core is implemented using a double-balanced passive ring architecture, using bipolar transistors for the switching as shown in Figure 2.2-2. A DC voltage of 650 mV is applied to the transistor bases, which helps minimizing conversion losses but still makes the DC current consumption negligible, and a VCC value of 1.4 V is selected. Both DC voltages are applied through the centre taps of the transformers, as explained before.

The schematic of the LO buffer can be seen in Figure 2.2-3. It consists of a differential common-base amplifier, where a bias voltage of 800 mV is applied to the bases through two big resistors. Both the VCC voltage of 1.3V for the collectors and the DC ground path for the emitters are provided using the centre taps of the transformers.

The simulated total DC consumption is 2.4 mW, mostly consumed by the LO buffer. All the DC voltages can be controlled externally, so that temperature and process variations, as well as inaccuracies of the models can to some extent be compensated. This way it is also possible to tune the conversion gain of the mixer and adapt to variations of the power provided by the LO.

Figure 2.2-3 Schematic of the mmW LO buffer

Figure 2.2-4 shows the layout of the described block, with a total area of 0.307 mm<sup>2</sup>.

Figure 2.2-4 Layout of the mmW mixer, including PADs

#### 2.2.2. Results

The same procedure explained in Section 2.1.2 has been followed for the post-layout simulations of the mm-Wave up-converter mixer, and all the simulations assume a power of 0 dBm at the LO port and 50  $\Omega$  load at the RF output.

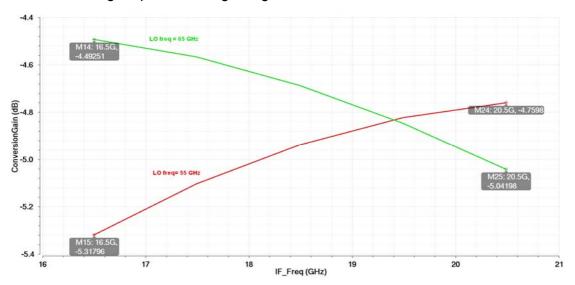

Figure 2.2-5 shows the conversion gain as a function of the IF for LO frequencies of 55 and 65 GHz, which result in output frequencies of 71.5-75.5 GHz and 81.5 – 85.5 GHz. As it can be observed, the gain ranges from -5.32 to -4.76 dB at the lower part of the E-Band and from -4.49 to -5.04 dB at the higher part, resulting in a gain flatness better than 0.6 dB at each sub-band.

Figure 2.2-5 Simulated conversion gain of the mmW mixer for LO frequencies of 55 and 65 GHz

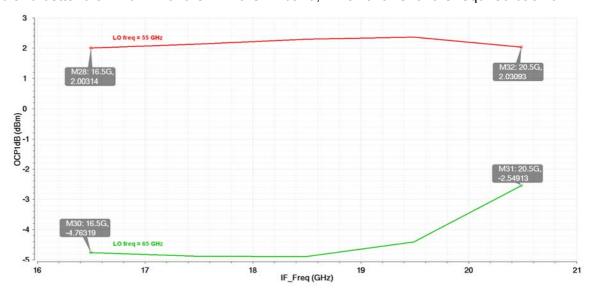

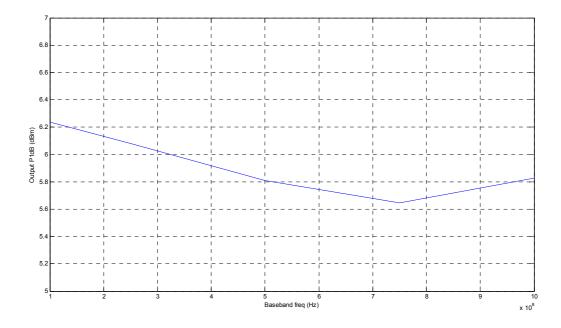

Similarly, the output 1 dB compression point is plotted in Figure 2.2-6 as a function of the IF for LO frequencies of 55 and 65 GHz. As it is shown, it is better than -5 dBm for the 81-86 GHz band and better than 2 dBm for the 71-76 GHz band, which allows for the required back-off.

Figure 2.2-6 Simulated output P1dB of the mmW mixer for LO frequencies of 55 and 65 GHz

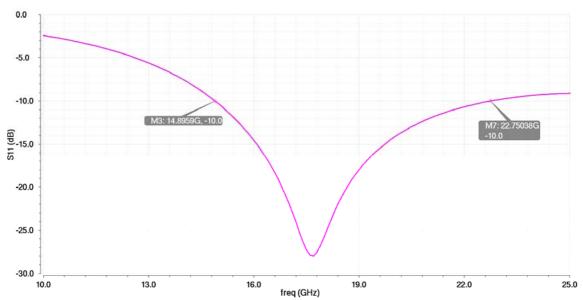

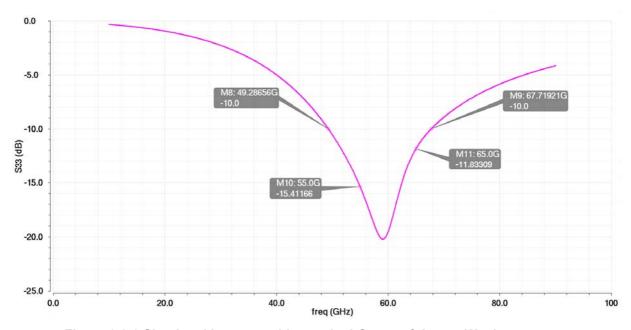

Figure 2.2-7 and Figure 2.2-8 show the reflection coefficients at the IF and LO ports respectively, when a 50  $\Omega$  single-ended port is connected to them. The input matching at these ports is better than -10 dB from 15 to 22.75 GHz at the IF port and from 49.29 to 67.72 GHz at the LO port. The bandwidth of the input matching covers, therefore, the input IF band and the considered LO frequencies of 55 and 65 GHz.

Due date: 30 June 2014

Figure 2.2-7 Simulated input matching at the IF port of the mmW mixer

Figure 2.2-8 Simulated input matching at the LO port of the mmW mixer

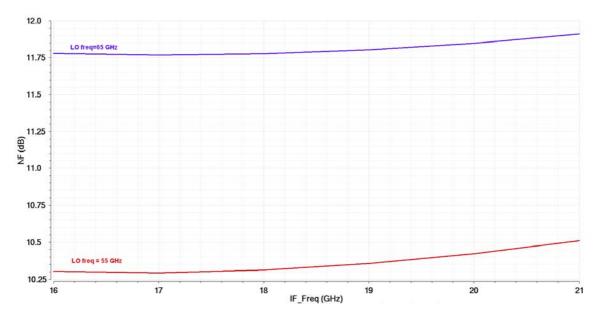

Figure 2.2-9 Simulated noise figure of the mmW mixer for LO frequencies of 55 and 65 GHz

In addition, the NF of the mixer is lower than 10.55 dB at the 71-76 GHz band and lower than 11.9 dB at the 81.86 GHz band, as it can be derived from the plot in Figure 2.2-9.

Table 2.2-1 summarizes the main simulation results and compared them to the specifications of the block.

| Parameter                 | Min. Value | Max.<br>Value         | Spec. in D1.2.2   | Comments                                                             |

|---------------------------|------------|-----------------------|-------------------|----------------------------------------------------------------------|

|                           |            | value                 |                   |                                                                      |

| Conversion Gain           | -5.32 dB   | -4.49 dB              | -8 dB             | A variable attenuator is planned to be included in the next redesign |

| Output bandwidth          | 70 GHz     | 87 GHz                | 70-77 / 80-87 GHz | Spec. fulfilled                                                      |

| IF bandwidth              | 15 GHz     | 21 GHz                | 15-21 GHz         | Spec. fulfilled                                                      |

| LO frequency              | 55 GHz     | 65 GHz                | 55 / 65 GHz       | Spec. fulfilled                                                      |

| Input matching at IF port | -28 dB     | -10 dB                | -                 |                                                                      |

| Input matching at LO port | -20 dB     | -10 dB                | -                 |                                                                      |

| Output P1dB               | -4.8 dBm   | 2.4 dBm               | -5 dBm            | Spec. fulfilled                                                      |

| Noise Figure              | 10.3 dB    | 11.9 dB               | 12 dB             | Spec. fulfilled                                                      |

| DC power                  | -          | 2.4 mW                | -                 |                                                                      |

| Area                      | -          | 0.307 mm <sup>2</sup> | -                 |                                                                      |

Table 2.2-1 Summary of simulation results for the mmW up-conversion mixer

# 2.3 mmW Tx module (mmW mixer & PA) results

## 2.3.1. Circuit description

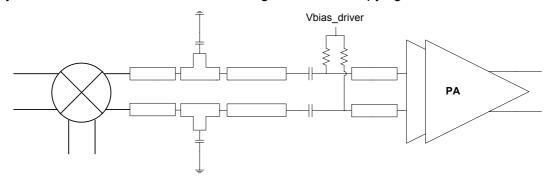

Once the mmW mixer and the PA were designed, they have been integrated in a single circuit, as an approach to the final integrated transmitter. A 50  $\Omega$  differential impedance was chosen for the interface between both blocks due to simplicity reasons.

In order to make the connection, the input balun is removed from the PA input to make it differential and a matching network (MN) is added, as shown in Figure 2.3-1. As in the standalone PA the bias for the 1<sup>st</sup> stage (cascode pre-driver) was applied through the centre tap of the balun, two big resistors are added now to both positive and negative inputs connected to the bias point.

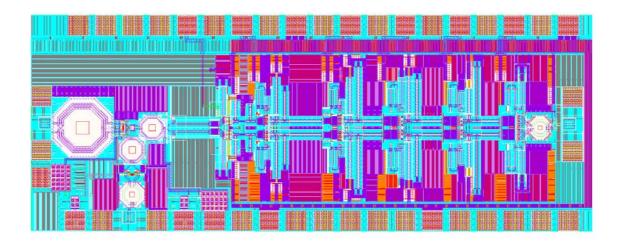

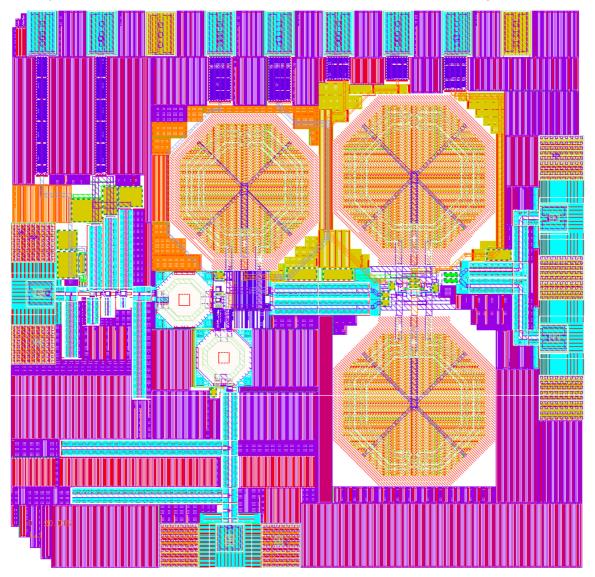

The layout of the circuit can be observed in Figure 2.3-2, occupying an area of 1.627 mm<sup>2</sup>.

Figure 2.3-1 Schematic of the MN between the mmW mixer and the PA

Figure 2.3-2 Layout of the mmW mixer and the PA, including PADs

#### 2.3.2. Results

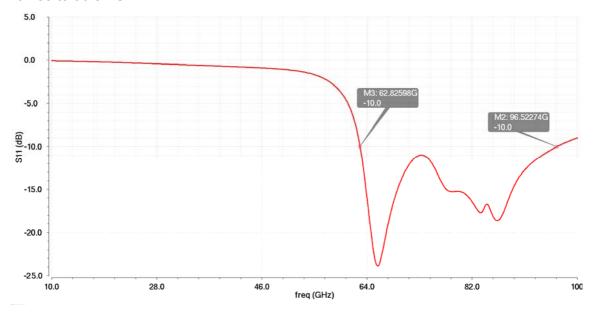

Figure 2.3-3 shows the input matching at the PA differential input, when a 50  $\Omega$  differential port is connected. It is observed that with the designed MN the input matching is better than -10 dB from 62.83 to 96.52 GHz.

Figure 2.3-3 Input matching at the PA differential input

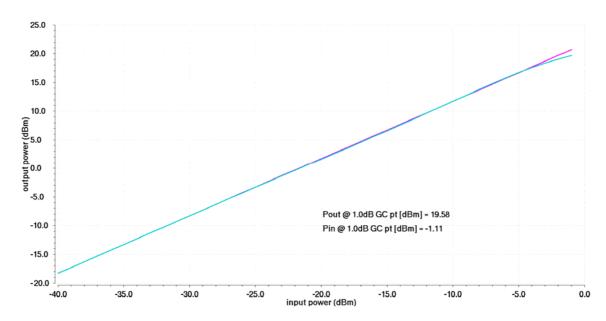

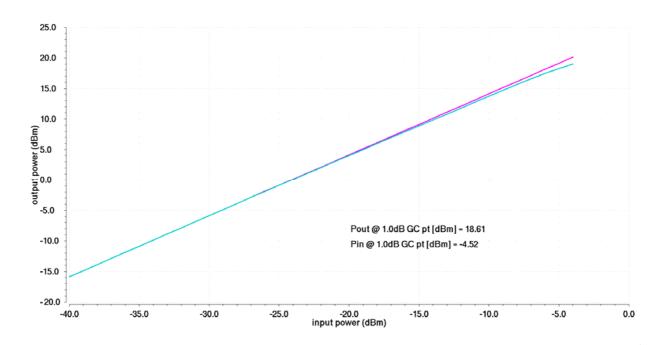

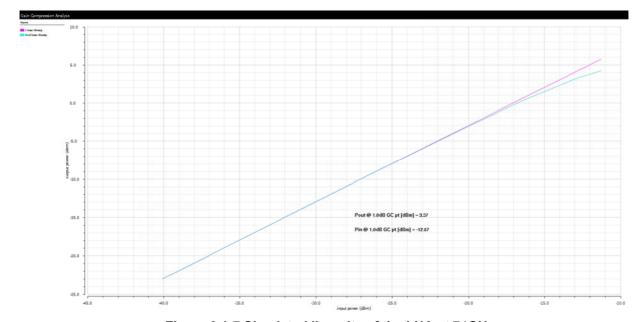

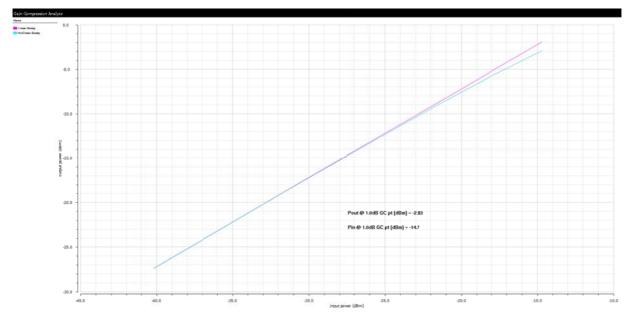

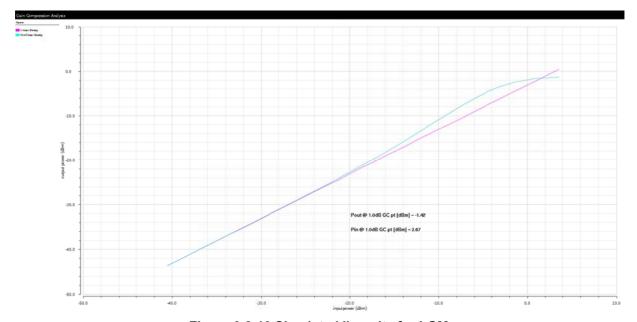

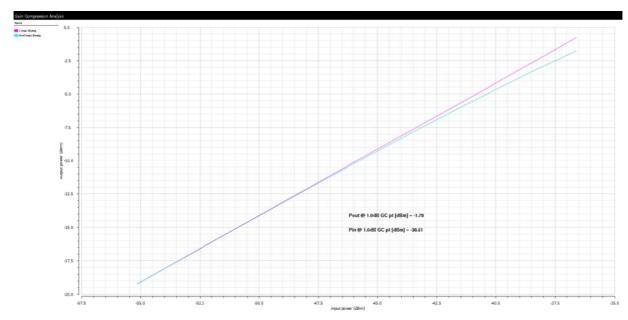

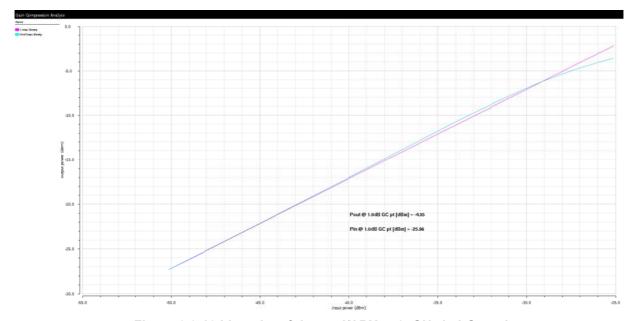

In order to check the behaviour of this circuit, the gain compression curves have been simulated at 2 frequencies: 72 GHz and 82 GHz, and are plotted in Figure 2.3-4 and Figure 2.3-5. It can be seen that the conversion gain is around 22-23 dB, which agrees well with the PA gain and the mixer conversion loss. As far as the output power compression is concerned, values of around 19 dBm are achieved. It can be seen that there is a small degradation when compared to the PA P1dB, but the specification is still fulfilled.

Figure 2.3-4 Gain compression curve of the mmW mixer + PA at 72 GHz

Figure 2.3-5 Gain compression curve of the mmW mixer + PA at 82 GHz

The main simulation results are summarized in Table 2.3-1 and compared to the specifications of the block.

| Parameter       | Min.<br>Value | Max.<br>Value | Spec. in D1.2.2 | Comments                                                           |

|-----------------|---------------|---------------|-----------------|--------------------------------------------------------------------|

| Conversion Gain | 21.69 dB      | 23.13 dB      | 20 dB           | Variable attenuator is planned to be included in the next redesign |

| Output P1dB     | 18.61 dBm     | 19.58 dBm     | 18 dBm          | Spec. fulfilled                                                    |

| DC power        | -             | 558 mW        | -               |                                                                    |

| Area            | -             | 1.627 mm²     | -               |                                                                    |

Table 2.3-1 Summary of simulation results for the mmW Tx module

# 2.4 Updated IF Mixer results

## 2.4.1. Circuit description

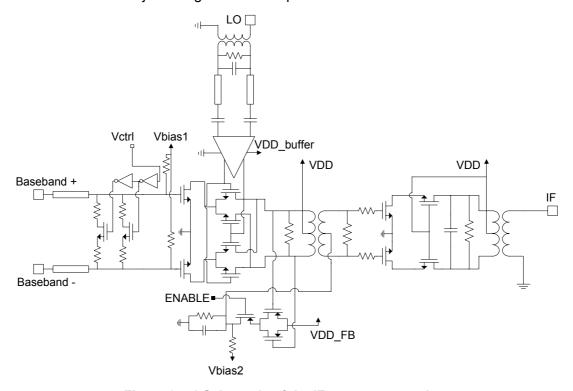

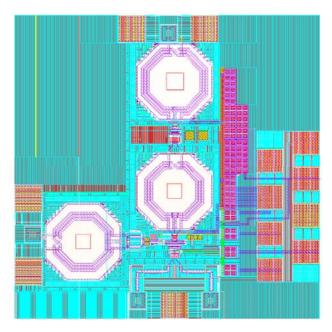

Figure 2.4-1 shows the schematic of the baseband to IF up-converter mixer. It consists of a Gilbert Cell followed by an output stage with cascode configuration, which are coupled using a centre-taped integrated transformer.

As it is shown, the differential input includes a resistive matching network, which can be varied between two different configurations depending on the external balun connected at the input. There is also a LO buffer to drive the mixer with enough power, which is connected to the LO input using a balun for on-wafer testing purposes. This port is matched to 50  $\Omega$  using a RC matching network. A similar procedure is used for the IF port, which is also single-ended for measurement purposes.

Additionally, a linearization loop is placed to increase the output power of the block, as it can be observed in the lower part of the schematic. When enabled, it modifies the bias voltage of the output gain stage depending on the mixer output power, thus increasing its linearity.

The selected VDD is 1.2 V for the mixer core and output stage and 1.5 V for the LO buffer. As for the linearization loop, its VDD can be varied to compensate for temperature and process variations as well as to adjust the gain of the loop.

Figure 2.4-1 Schematic of the IF up-converter mixer

Figure 2.4-2 Layout of the IF up-converter mixer, including PADs

The layout of this block can be observed in Figure 2.4-2, which occupies an area of 0.7 mm<sup>2</sup>.

#### 2.4.2. Results

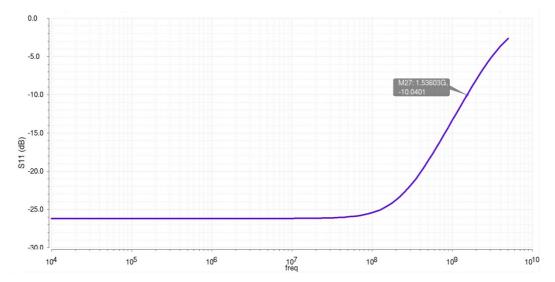

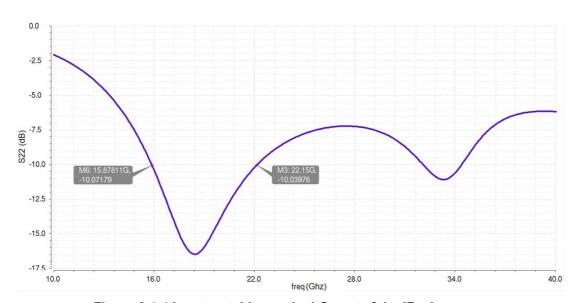

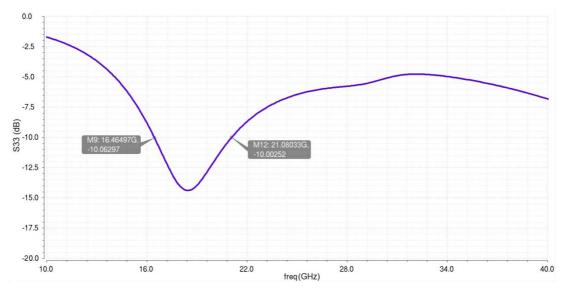

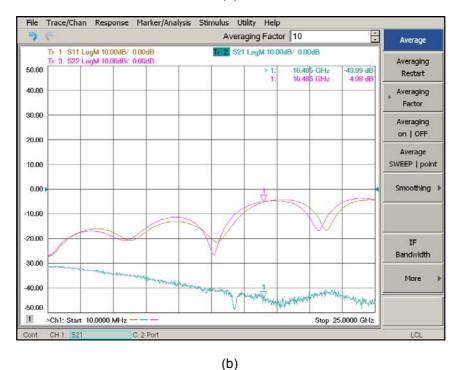

Figure 2.4-3 to Figure 2.4-5 show the matching at the different ports of the IF up-converter mixer. As it can be observed, the S11 parameter at the baseband input port is better than -10 dB up to 1.54 GHz, being -13 dB at 1 GHz. This wide bandwidth behaviour is achieved due to the resistive matching network. As for the LO port, the reflection coefficient is better than -10 dB from 15.88 to 22.15 GHz, which means that it is well matched for the LO frequencies of 17.5 and 19.5 GHz. The output matching of the mixer, shown in the S33 plot, is better than -10 dB from 16.46 to 21.08 GHz, which covers the range of output bandwidth of the different channels.

Figure 2.4-3 Input matching at the input port of the IF mixer

Figure 2.4-4 Input matching at the LO port of the IF mixer

Figure 2.4-5 Output matching of the IF mixer

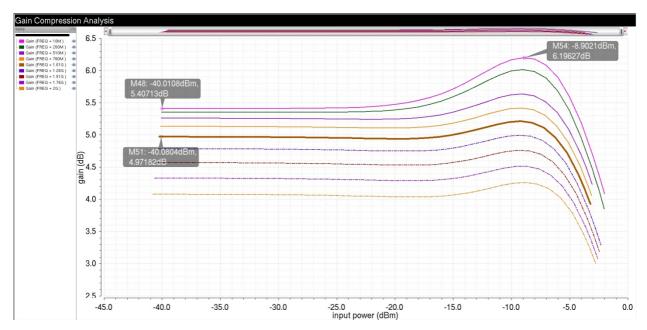

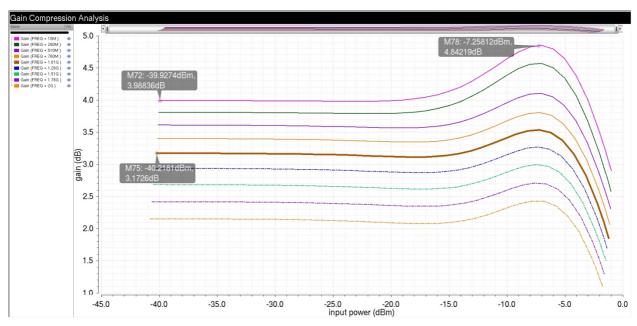

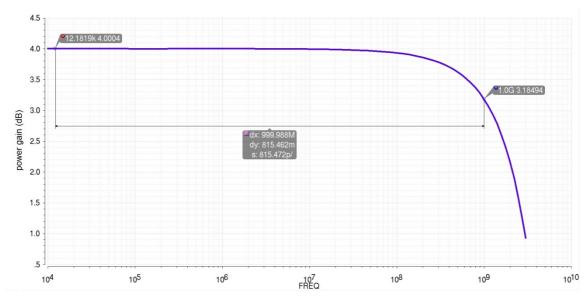

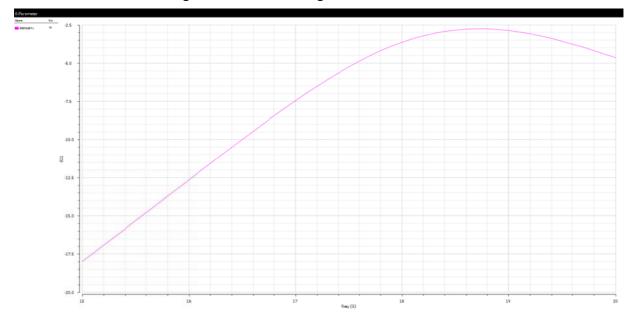

The behaviour of the linearization loop at the LO frequencies of 17.5 and 19.5 GHz can be derived from Figure 2.4-6 and Figure 2.4-7 respectively. It is observed that when the input power is higher than about -15 dBm, the loop increases the gain, thus making the compression point bigger.

Figure 2.4-6 Power gain as a function of the input power for LO freq of 17.5 GHz

Figure 2.4-7 Power gain as a function of the input power for LO freq of 19.5 GHz

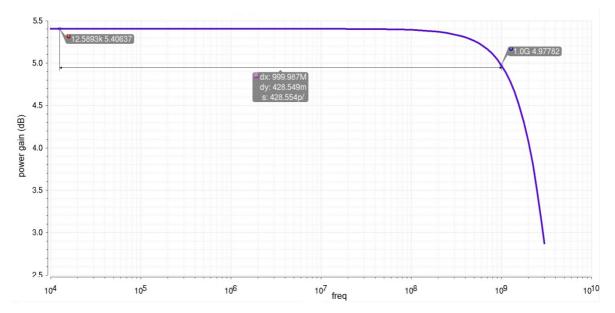

Figure 2.4-8 Power gain as a function of input frequency for LO freq of 17.5 GHz

Figure 2.4-9 Power gain as a function of input frequency for LO freq of 19.5 GHz

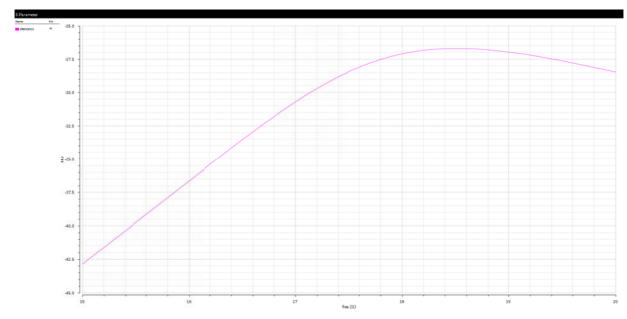

Figure 2.4-8 and Figure 2.4-9 show the power gain as a function of the input baseband frequency for LO frequencies of 17.5 and 19.5 GHz respectively. A maximum value of 5.4 dB is achieved at the 17.5 GHz band, with a decay of less than 0.43 dB at 1 GHz. The gain decreases 3 dB at about 3 GHz, resulting in an output 3-dB bandwidth of around 6 GHz. With regard to the 19.5 GHz channel, the maximum power gain is 4 dB, with a decay of 0.8 dB at 1 GHz. In this case the gain decreases 3 dB at 2 GHz, giving an output 3-dB bandwidth of 4 GHz.

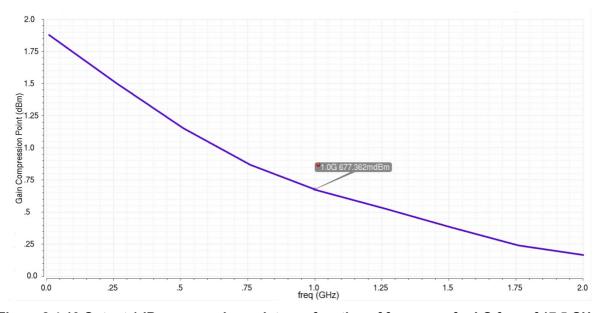

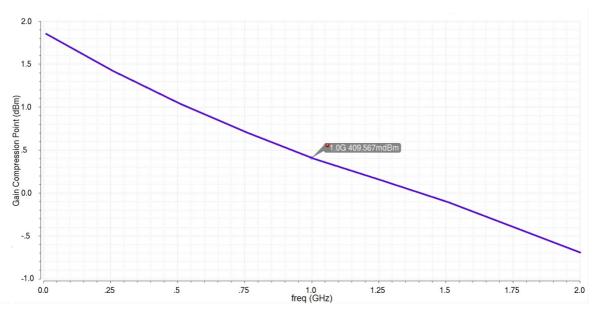

Regarding the 1 dB compression point, Figure 2.4-10 and Figure 2.4-11 show the output-referred P1dB for both channels as a function of the input frequency. A maximum value of 1.85 dBm is observed at the 17.5GHz channel, with a minimum value of 0.67 dBm at 1 GHz input. Similarly, the maximum value is around 1.85 dBm for the 19.5 GHz channel with a minimum value of 0.41 dBm at 1 GHz input.

Figure 2.4-10 Output 1dB compression point as a function of frequency for LO freq of 17.5 GHz

Figure 2.4-11 1dB compression point as a function of frequency for LO freq of 19.5 GHz

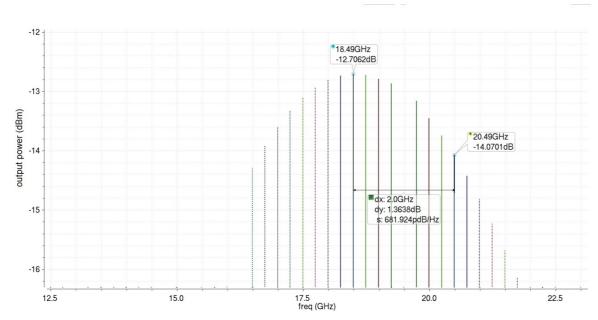

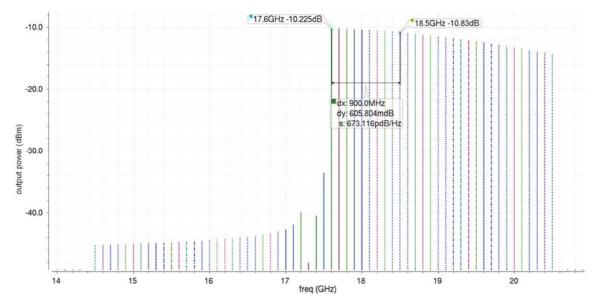

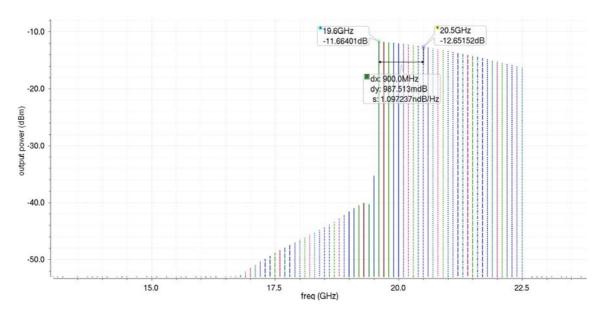

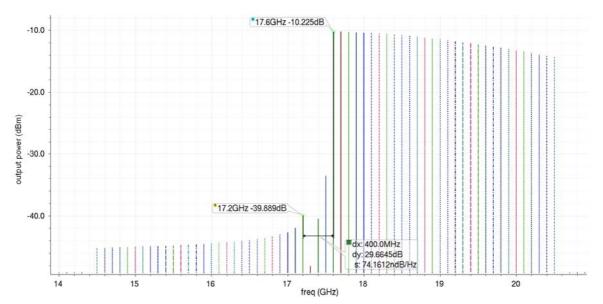

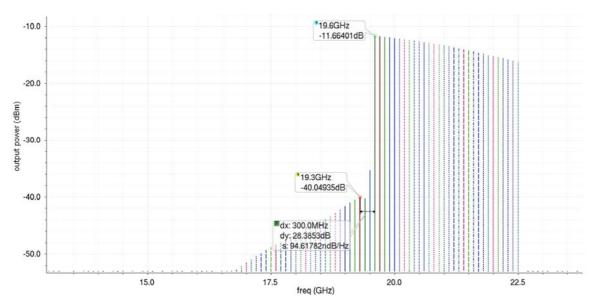

Figure 2.4-12 Output power spectrum for the 17.5 GHz channel

Figure 2.4-13 Output power spectrum for the 19.5 GHz channel

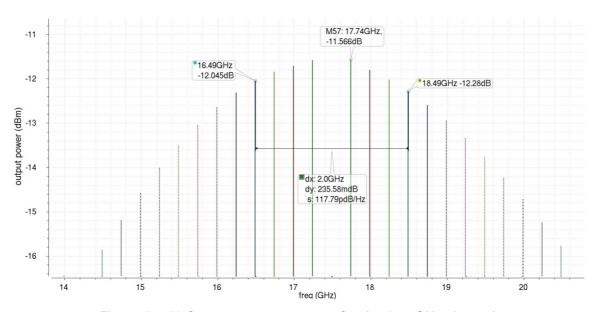

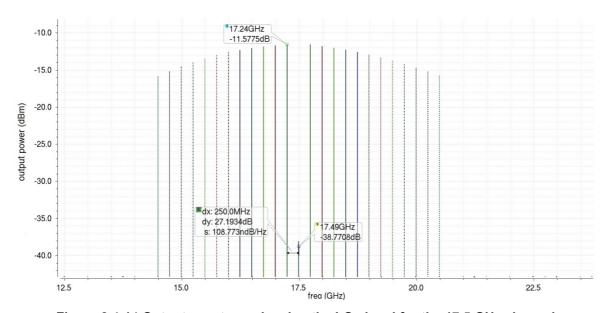

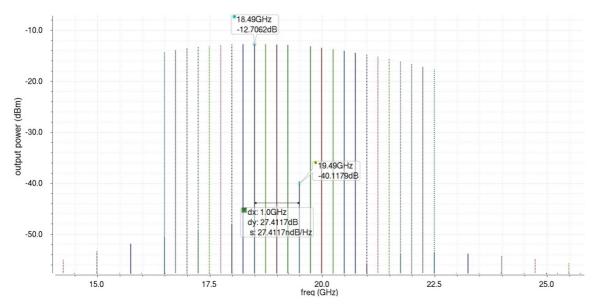

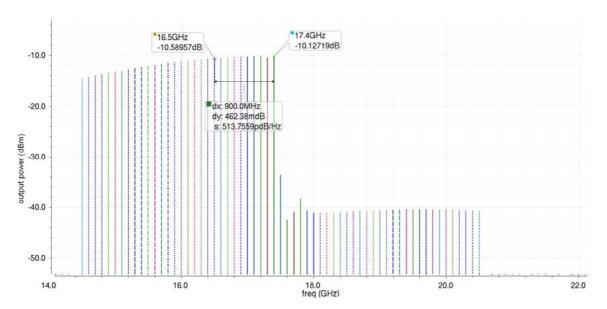

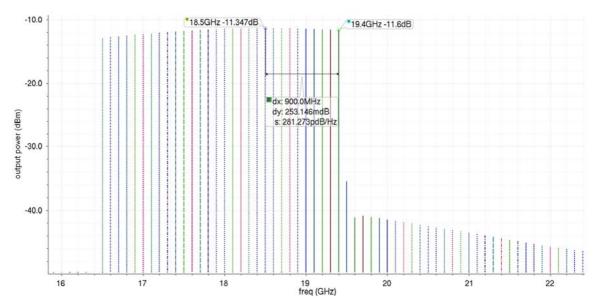

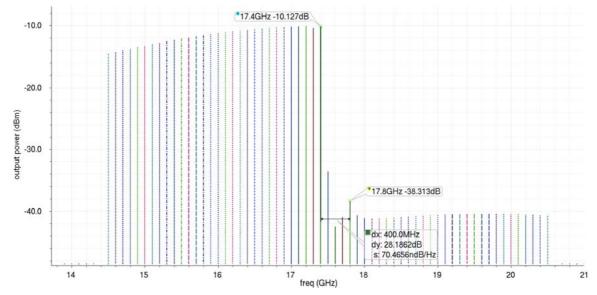

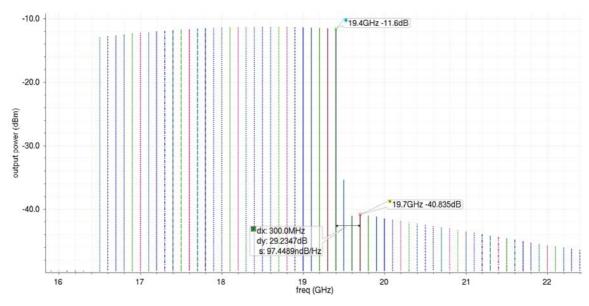

The output power spectrum is shown in Figure 2.4-12 and Figure 2.4-13, for an input power of -17 dBm. A flatness of 0.7 dB can be observed at the 17.5 GHz channel and of 1.37 dB at the 19.5 GHz channel. The LO signal is 27 dBc below the output signal of the mixer for both bands, as shown in Figure 2.4-14 and Figure 2.4-15.

Figure 2.4-14 Output spectrum showing the LO signal for the 17.5 GHz channel

Figure 2.4-15 Output spectrum showing the LO signal for the 19.5 GHz channel

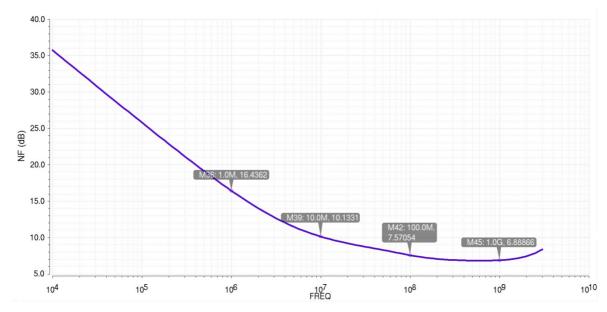

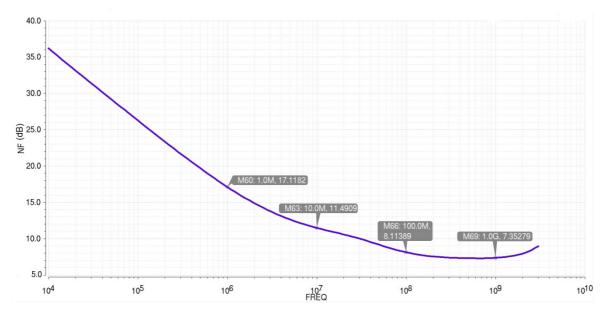

The noise figure of this block is shown in Figure 2.4-16 and Figure 2.4-17 for both channels. It has a minimum value of 6.89 dB at the 17.5 GHz channel and of 7.35 dB at the 19.5 GHz channel. A big increase is observed close to DC due to effects such as flicker noise. The impact of flicker noise is expected to be small due to the employed modulation scheme where signal power close to DC is minimized.

Figure 2.4-16 Noise figure at the 17.5 GHz channel as a function of the input frequency

Figure 2.4-17 Noise figure at the 19.5 GHz channel as a function of the input frequency

The main given simulation results are summarized in Table 2.4-1 and compared to the specifications of the IF up-conversion mixer.

| Parameter                  | Min.<br>Value | Max.<br>Value | Spec. in D1.2.2 | Comments                                                                                          |

|----------------------------|---------------|---------------|-----------------|---------------------------------------------------------------------------------------------------|

| Conversion Gain            | 3.18 dB       | 5.4 dB        | 3 dB            | Spec. fulfilled                                                                                   |

| Output 3dB bandwidth       | 6 GHz         | -             | 6 GHz           | Spec. fulfilled                                                                                   |

| LO frequency               | 17.5 GHz      | 19.5 GHz      | 17.5 / 19.5 GHz | Spec. fulfilled                                                                                   |

| Input matching at BB port  | -26 dB        | -13 dB        | -10 dB          | Spec. fulfilled                                                                                   |

| Input matching at LO port  | -16.5 dB      | <-10 dB       | -10 dB          | Spec. fulfilled                                                                                   |

| Output matching at IF port | -14.5 dB      | -10 dB        | - 10 dB         | Spec. fulfilled                                                                                   |

| Output P1dB                | 0.41 dBm      | 1.85 dBm      | 0 dBm           | Spec. fulfilled                                                                                   |

| LO leakage at IF port      | -40.1 dB      | -38.8 dB      | -36 dB          | Spec. fulfilled                                                                                   |

| Noise Figure               | 6.89 dB       | -             | 10 dB           | Spec. fulfilled; NF increase close to DC is taken into account in the baseband signal generation. |

| DC power                   | -             | 50 mW         | -               |                                                                                                   |

| Area                       | -             | 0.7 mm²       | -               |                                                                                                   |

Table 2.4-1 Summary of simulation results for the IF up-conversion mixer

## 2.5 Tx IQ Modulator results

## 2.5.1. Circuit description

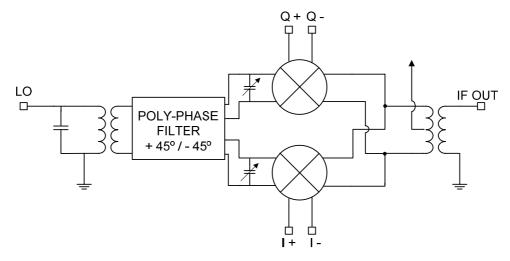

The block diagram of the IQ modulator circuit is shown in Figure 2.5-1. It consists of two IF mixers like the one described in Section 2.4, whose output currents are added using a balun. A single LO signal is used, which is fed into a poly-phase filter to provide 90° phase difference at the in-phase and quadrature mixers. Integrated baluns are used at both LO and IF ports for onwafer testing purposes.

Special care is placed on the layout symmetry, so that no phase difference is introduced into the LO signal of the I and Q channels. The layout of this block can be observed in Figure 2.5-2, with an area of 1.073 mm<sup>2</sup>, including all the PADs.

Figure 2.5-1 Block diagram of the IQ modulator

Figure 2.5-2 Layout of the IQ modulator, including PADs

### 2.5.2. Results

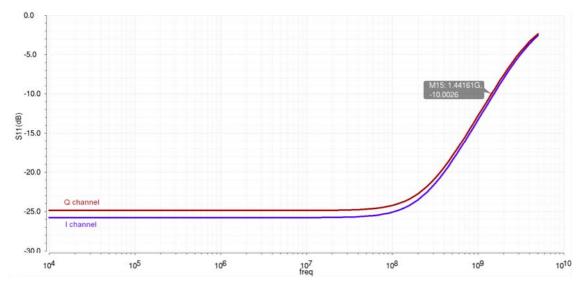

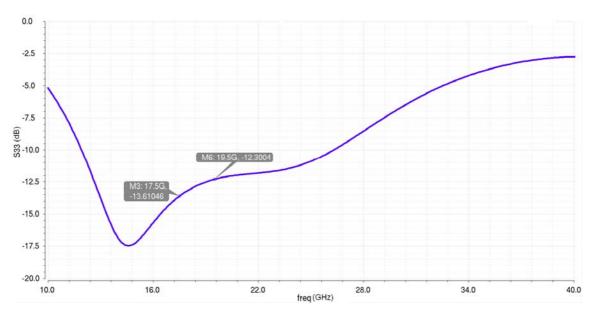

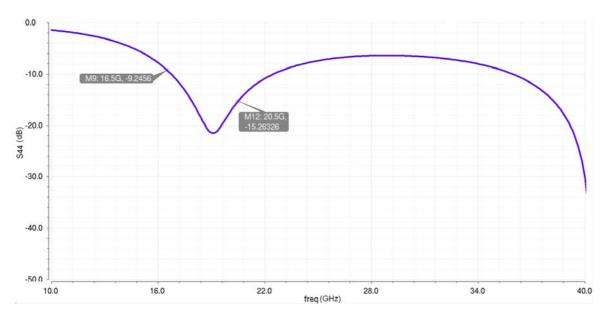

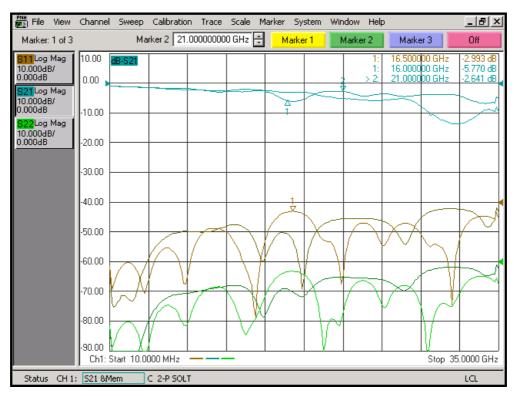

Figure 2.5-3 to Figure 2.5-5 show the matching at the different ports of the IQ modulator. As it is observed, the input matching at the I and Q ports is better than -10 dB up to 1.44 GHz, which is very similar to that reported in Section 2.4.2. The S33 parameter at the LO input is -13.6 dB at 17.5 GHz and -12.3 dB at 19.5 GHz. As for the output of the modulator, it is well matched to 50  $\Omega$  in the band of interest as well, with S44 equal to -9.24 dB at 16.5 GHz and -15.26 dB at 20.5 GHz.

Figure 2.5-3 Input matching at the I and Q ports of the IQ modulator

Figure 2.5-4 Input matching at the LO port of the IQ modulator

Figure 2.5-5 Output matching of the IQ modulator

Figure 2.5-6 and Figure 2.5-7 show the output power spectrum when the same signal is introduced in the I and Q inputs for the 17.5 and 19.5 GHz bands, whereas the behaviour when the signal is introduced with 90° phase difference can be seen in Figure 2.5-8 and Figure 2.5-9. It is observed that the gain flatness is very similar to that reported for the case of a single IF mixer. The rejection of the LO signal can be extracted as well, which is more than 23 dBc below the power of the output signal.

Figure 2.5-6 Output spectrum when the same signal is introduced in I and Q, at 17.5 GHz

Figure 2.5-7 Output spectrum when the same signal is introduced in I and Q, at 19.5 GHz

Figure 2.5-8 Output spectrum when a signal with 90° phase shift is introduced in I and Q, at 17.5GHz

Figure 2.5-9 Output spectrum when a signal with 90° phase shift is introduced in I and Q, at 19.5GHz

Similarly, the rejection of the signal at the image frequency can be extracted from Figure 2.5-10 to Figure 2.5-13. It is observed that the image is more than 28 dBc below the power of the output signal.

Figure 2.5-10 Output spectrum showing the image signal power when same signal is introduced in I and Q, at 17.5 GHz

Figure 2.5-11 Output spectrum showing the image signal power when same signal is introduced in I and Q, at 19.5 GHz

Figure 2.5-12 Output spectrum showing the image signal power when a signal with 90° phase difference is introduced in I and Q, at 17.5 GHz

Figure 2.5-13 Output spectrum showing the image signal power when a signal with 90° phase difference is introduced in I and Q, at 19.5 GHz

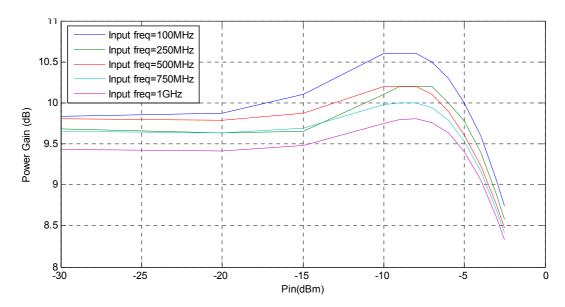

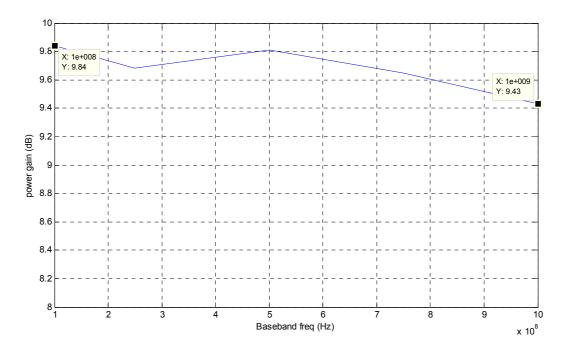

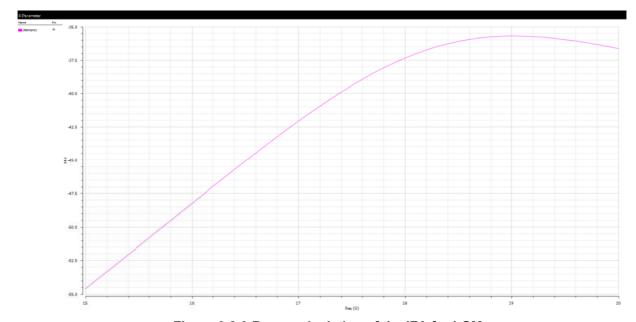

In order to check the gain and compression performance of the IQ modulator compared to that of a single mixer, the power gain as a function of the input power and the input frequency is plotted in Figure 2.5-14 and Figure 2.5-15 for the 17.5 GHz channel, while the output 1 dB compression point is plotted in Figure 2.5-16 as a function of the baseband input frequency. It can be observed that the power gain is between 9.43 dB and 9.84 dB and that the loop behaves similarly to the case of the single mixer. The output P1dB is more than 5.6 dBm across the whole band. These values are higher than those of the single IF up-converter mixer, which agrees with the fact that the currents are added at the output.

Figure 2.5-14 Power gain as a function of the input power for LO frequency of 17.5 GHz

Figure 2.5-15 Power gain as a function of the baseband input frequency for LO frequency of 17.5GHz

Figure 2.5-16 Output P1dB as a function of the baseband input frequency for LO frequency of 17.5GHz

The main simulation results are summarized in Table 2.5-1.

| Parameter                    | Min.<br>Value | Max. Value | Comments                                        |

|------------------------------|---------------|------------|-------------------------------------------------|

| Conversion Gain              | 9.43 dB       | 9.84 dB    | Parameter updated in the table of system values |

| LO frequency                 | 17.5 GHz      | 19.5 GHz   | Spec. fulfilled                                 |

| Input matching at BB port    | -26 dB        | -13 dB     | Spec. fulfilled                                 |

| Input matching at LO port    | -13.61 dB     | -12.3 dB   | Spec. fulfilled                                 |

| Output matching at IF port   | -15.26 dB     | -9.25 dB   | Spec. fulfilled                                 |

| Output P1dB                  | 5.6 dBm       | 6.24 dBm   | Spec. fulfilled                                 |

| LO leakage at IF port        | -23.84 dBc    | -23.38 dBc | Spec. fulfilled                                 |

| Image leakage at the IF port | -29.66 dBc    | -28.19 dBc | Spec. fulfilled                                 |

| DC power                     | -             | 96 mW      |                                                 |

| Area                         | -             | 1.073 mm²  |                                                 |

Table 2.5-1 Summary of simulation results for the IQ modulator

## 3. RX SIMULATION RESULTS

## 3.1 Updated LNA results

## 3.1.1. Circuit description

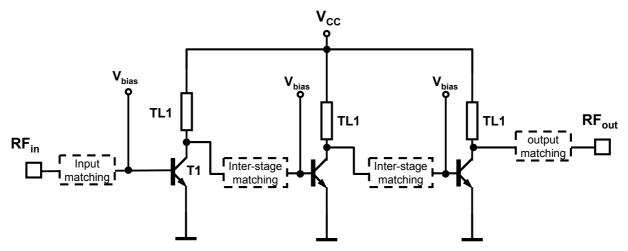

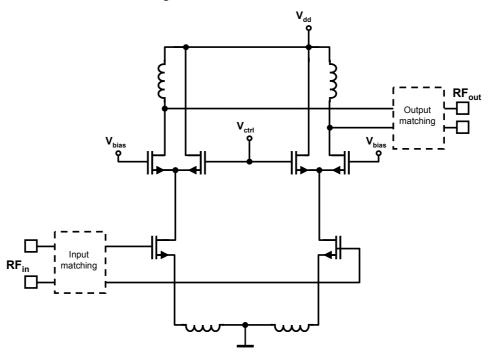

The re-simulation of the LNA designed in the first production run with newest PDK delivered by ST showed performance degradation and redesign was required. In order to fulfil the system specifications a three-stage LNA is required as depicted in Figure 3.1-1. The high frequency of operation allows using transmission lines for input and output matching as well as for the loads of the transistors. The configuration of input and output matching structures is designed to guarantee broadband operation and robust ESD protection simultaneously.

Figure 3.1-1 Schematic of the three-stage LNA

#### 3.1.2. Results

The circuit is built and simulated in Cadence. The passives library provided by CEA has been used, which includes transmission lines and pads, as well as the ST PDK providing all other components.

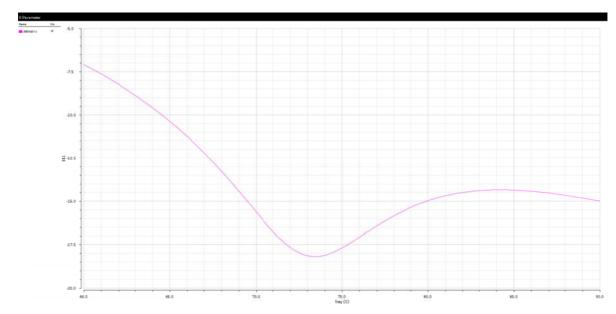

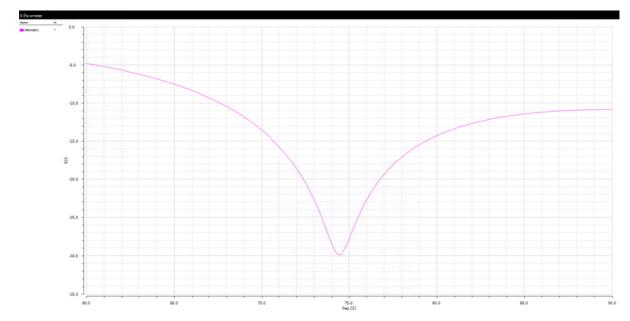

Figure 3.1-2 and Figure 3.1-3 show the input and output matching of the LNA in the frequency band of interest. The input matching is a compromise between best fit for power and noise match. Broadband matching techniques were employed to achieve good match over whole E-band.

Figure 3.1-2 Simulated S11 of the LNA

Figure 3.1-3 Simulated S22 of the LNA

The simulated gain of the LNA is shown in Figure 3.1-4. It achieves 17dB of gain at 77GHz. The gain drops to 16.1dB and 15.5dB at 71GHz and 86GHz respectively. The LNA features reverse isolation better than 40dB in the whole band of interest as depicted in Figure 3.1-5.

Figure 3.1-4 Simulated gain of the LNA

Figure 3.1-5 Reverse isolation of the LNA

The simulated noise figure of the LNA is below 5.1dB in the band of interest as shown in Figure 3.1-6. The linearity of the LNA simulated at 74GHz and 84GHz is depicted in Figure 3.1-7 and Figure 3.1-8, respectively. The LNA reaches compression point for input signal level of -12.7dBm at 74GHz and -11.32dBm at 84GHz.

Figure 3.1-6 Simulated noise figure of the LNA

Figure 3.1-7 Simulated linearity of the LNA at 74GHz

Figure 3.1-8 Simulated linearity of the LNA at 84GHz

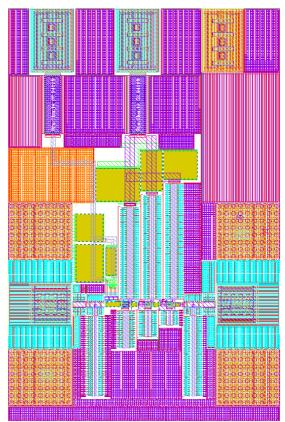

The layout of the LNA occupies an area of  $420x550 \mu m^2$  and is shown in Figure 3.1-9.

Figure 3.1-9 Layout of the LNA

# 3.1.3. Comparison of simulation results with specifications in D1.2.2

Table 3.1-1 shows the comparison between LNA parameters coming from the specification phase and the simulated values.

| Parameter                    | Parameter Simulation Result        |     | Comments                                                                            |

|------------------------------|------------------------------------|-----|-------------------------------------------------------------------------------------|

| RF Output Frequency          | 70GHz - 77GHz and<br>80GHz - 87GHz | YES |                                                                                     |

| RF Output bandwidth          | 7                                  | YES |                                                                                     |

| Input Impedance              | 50 Ω                               | YES |                                                                                     |

| Input match at Fc            | - 14dB                             | YES |                                                                                     |

| Reverse isolation at Fc      | 40dB                               | YES |                                                                                     |

| Power gain                   | 17dB                               | NO  | Gain is 1dB lower than specified, this can be compensated in following stages of RX |

| Output 1dB compression point | -4dBm                              | YES |                                                                                     |

| Noise Figure                 | 5.1dB                              | YES |                                                                                     |

| Gain ripple                  | 0.5dB                              | YES |                                                                                     |

Table 3.1-1 Summary of simulation results for the LNA

# 3.2 Updated IFA results

## 3.2.1. Circuit description

The intermediate frequency amplifier (IFA1) is a single stage fully differential type. It utilizes current-splitting technique to achieve gain control, maintain its input and output return loss in different mode and also maintain the current of LNA in both high gain and low gain mode. The schematic of the IFA is shown in Figure 3.2-1.

Figure 3.2-1 IFA schematic

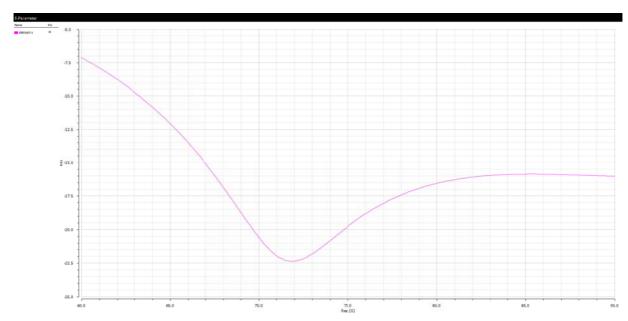

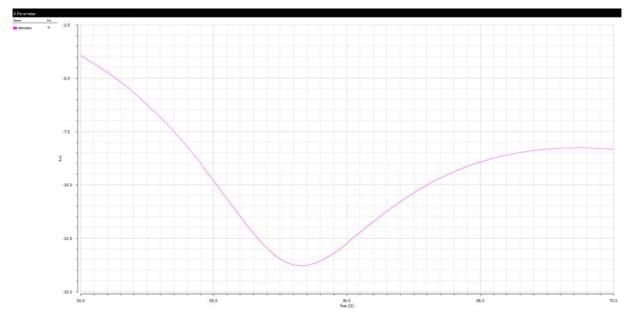

### 3.2.2. Results

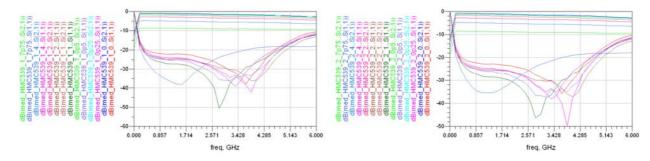

Figure 3.2-2, Figure 3.2-3, Figure 3.2-4 and Figure 3.2-5 show the input and output matching of the IFA in the frequency band of interest for high gain mode (HGM) and low gain mode (LGM), respectively. The input matching as well as the output matching is not severely affected by the gain switching.

Figure 3.2-2 Simulated S11 for HGM

Figure 3.2-3 Simulated S11 for LGM

Figure 3.2-4 Simulated S22 for HGM

Figure 3.2-5 Simulated S22 for LGM

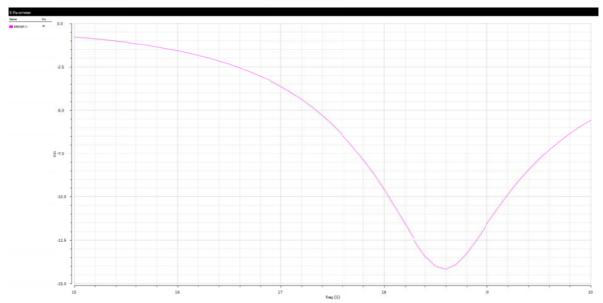

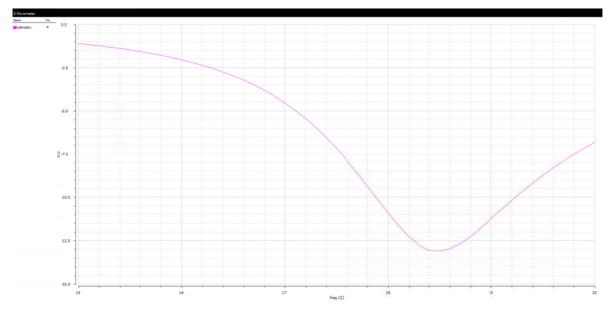

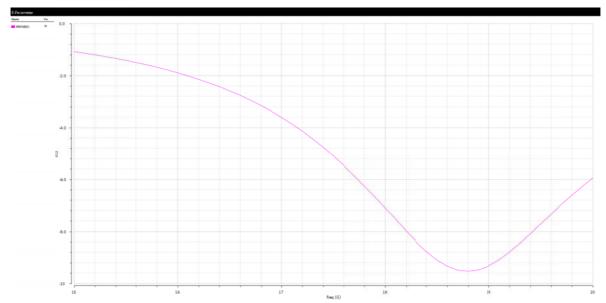

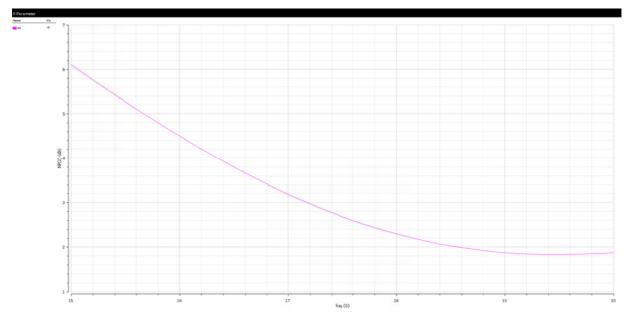

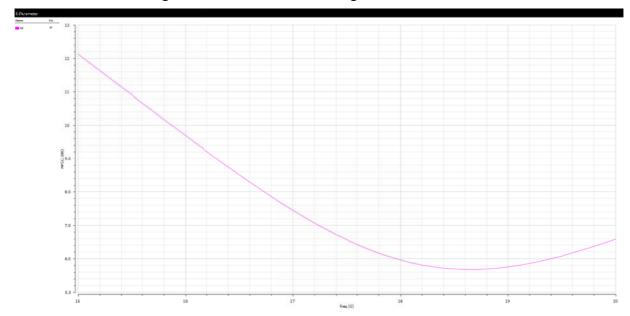

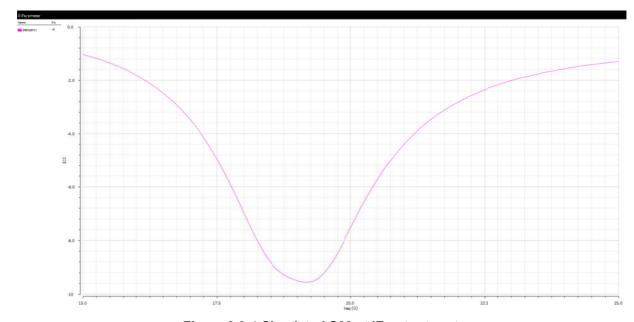

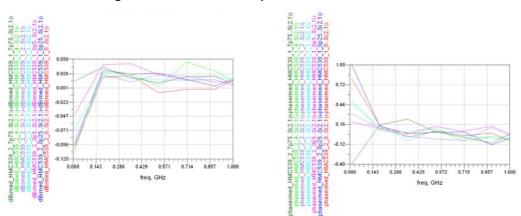

The simulated gain of the IFA is shown in Figure 3.2-6 and Figure 3.2-7. The IFA achieves 12.5dB and -2.5dB of gain at 18.8GHz for high and low gain setting respectively. 3dB bandwidth of the amplifier exhibits 2.2GHz. The IFA features reverse isolation better than 26dB in the whole band of interest as depicted in Figure 3.2-8 and Figure 3.2-9. The simulated noise figure of the IFA is below 3dB over the 3dB bandwidth for HGM (Figure 3.2-10). In LGM the amplifier achieves a noise figure of 7dB as depicted in Figure 3.2-11.

Figure 3.2-6 Simulated gain of the IFA for HGM

Figure 3.2-7 Simulated gain of the IFA for LGM

Figure 3.2-8 Reverse isolation of the IFA for HGM

Figure 3.2-9 Reverse isolation of the IFA for LGM

Figure 3.2-10 Simulated noise figure of the IFA for HGM

Figure 3.2-11 Simulated noise figure of the IFA for LGM

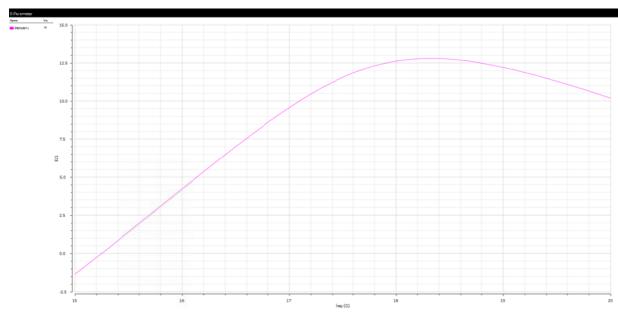

Figure 3.2-12 Simulated linearity for HGM

Figure 3.2-13 Simulated linearity for LGM

The linearity of the IFA simulated at 18.9GHz in HGM and LGM is presented in Figure 3.2-12 and Figure 3.2-13. The IFA reaches 1dB output compression point at output signal level of -2.9dBm for HGM and -1.4dBm for LGM.

The layout of the IFA is shown in Figure 3.2-14. The circuit occupies an area of  $625x900 \ \mu m^2$ .

Figure 3.2-14 Layout of the IFA

# 3.2.3. Comparison of simulation results with specifications in D1.2.2

Table 3.2-1 shows the comparison between IFA parameters coming from the specification phase and the simulated values.

| Parameter                          | Simulation Result | Spec. met? | Comments                                                           |

|------------------------------------|-------------------|------------|--------------------------------------------------------------------|

| IF Input Frequency                 | 16GHz - 21GHz     | NO         | Band switching required – will be implemented in the next redesign |

| RF Output bandwidth                | 7                 | YES        |                                                                    |

| Input Impedance                    | 100 Ω             | YES        |                                                                    |

| Output Impedance                   | 100 Ω             | YES        |                                                                    |

| Input match at Fc                  | - 15dB            | YES        |                                                                    |

| Reverse isolation at Fc            | 26dB              | YES        |                                                                    |

| Power gain (HGM)                   | 12.5dB            | YES        |                                                                    |

| Power gain (LGM)                   | -2.5dB            | NO         | 2.5dB lower than specified. Redesign is needed                     |

| Gain step                          | 10dB              | NO         | Gain step 15dB, can be optimized if required                       |

| Noise Figure (HGM)                 | 3dB               | YES        |                                                                    |

| Noise Figure (LGM)                 | 7dB               | YES        |                                                                    |

| Output 1dB compression point (HGM) | -2.9dBm           | YES        |                                                                    |

| Output 1dB compression point (LGM) | -1.4dBm           | YES        |                                                                    |

Table 3.2-1 Summary of simulation results for the IFA

### 3.3 mmW Receiver results

## 3.3.1. Circuit description

A block diagram of the mmW RX is shown in Figure 3.3-1. It consists of LNA, mixer and IFA. The circuit converts the signals from 70-77GHz and 80-87GHz bands to 16-21GHz IF band. The LO signal will be delivered from external source of 55GHz and 65GHz depending in the input band of operation. The LNA and IFA described in previous sections are slightly modified (only matching structures) to get the best performance in combination with mixer. The mixer implemented here is a standard double-balanced Gilbert cell structure.

Figure 3.3-1 Block diagram of mmW RX

### 3.3.2. Results

Figure 3.3-2, Figure 3.3-3 and Figure 3.3-4 show the matching at all three high frequency ports of the mmW RX in the relevant frequency bands.

Figure 3.3-2 Simulated S11 at RF input port

Figure 3.3-3 Simulated S11 at LO input port

Figure 3.3-4 Simulated S22 at IF output port

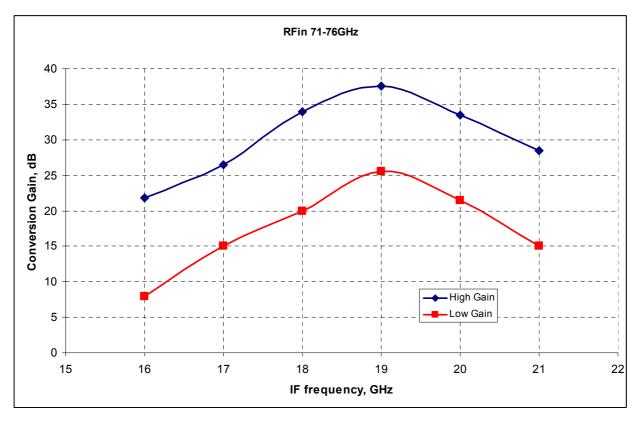

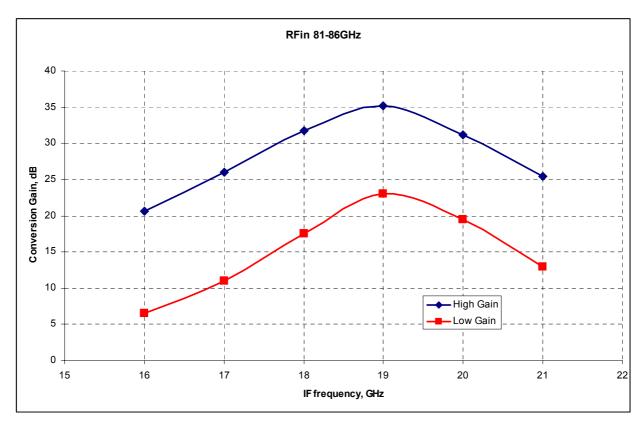

The simulated conversion gain of the mmW RX is shown in Figure 3.3-5 and Figure 3.3-6. The simulation was performed for fixed LO frequency and swept RF input frequency. The mmW RX achieves 37.5dB and 25.5dB of gain for high and low gain modes in the lower part of E-band respectively. Conversion gain values of 35.2dB and 23dB for high and low gain setting are obtained for the upper part of E-band.

Figure 3.3-5 Conversion gain of the mmW RX in HG and LG modes for the lower part of E-band

Figure 3.3-6 Conversion gain of the mmW RX in HG and LG modes for upper part of E-band

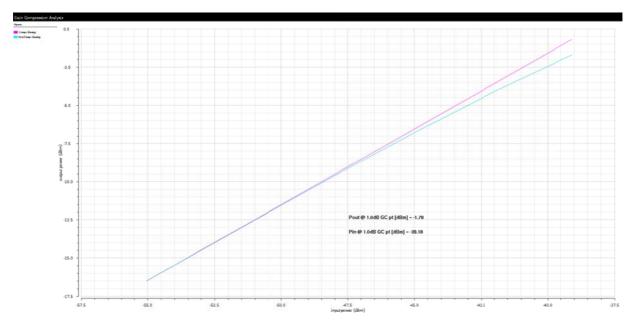

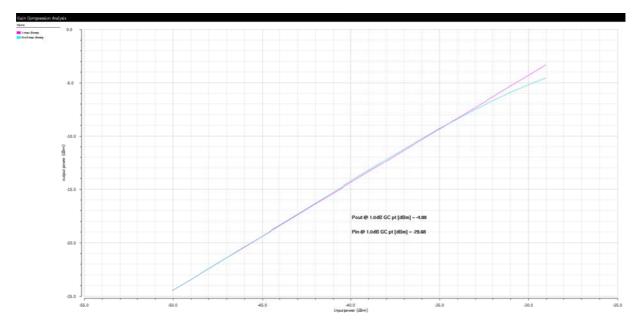

The linearity of the mmW RX simulated at 74GHz in HGM and LGM is presented in Figure 3.3-7 and Figure 3.3-8. 1dB output compression point at input signal level of -39.2dBm for HGM and -29.7dBm for LGM is achieved.

Figure 3.3-7 Linearity of the mmW RX at 74GHz in HG mode

Figure 3.3-8 Linearity of the mmW RX at 74GHz in LG mode

The linearity of the mmW RX simulated at 84GHz in HGM and LGM is depicted in Figure 3.3-9 and Figure 3.3-10. 1dB output compression point at input signal level of -36.6dBm for HGM and -26.9dBm for LGM is achieved.

Figure 3.3-9 Linearity of the mmW RX at 84GHz in HG mode

Figure 3.3-10 Linearity of the mmW RX at 84GHz in LG mode

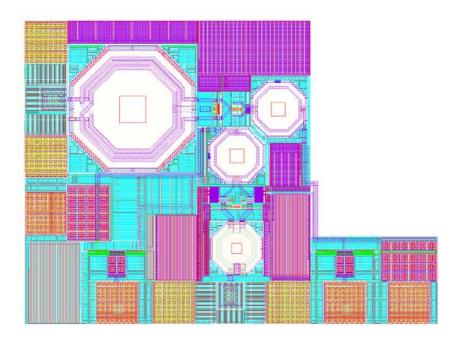

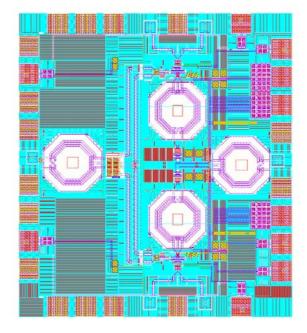

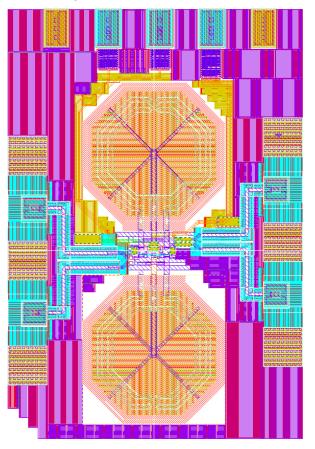

The layout of the receiver occupies an area of 1x1mm<sup>2</sup> and is shown in Figure 3.3-11.

Figure 3.3-11 Layout of mmW RX

### 4. SIGNAL GENERATION RESULTS

## 4.1 PLL loop optimization

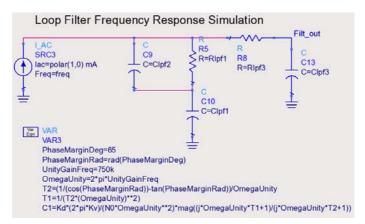

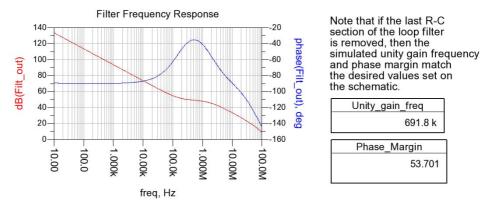

The PLL is based on an integer-N architecture with 2<sup>nd</sup> order loop-filter, shown in next figure.

Figure 4.1-1 PLL loop filter and calculation of the 2<sup>nd</sup> order system components

The filter is simulated alone in an open loop and in closed loop using linearized models for the other components of the PLL. Next figure shows one example of filter characteristic for a specification of cut-off frequency of 750 kHz.

Desired Phase Margin and Unity Gain Frequency, set on schematic.

Loop filter component values, computed on schematic from desired phase margin, unity gain frequency, Kd, Kv, and N0.

| PhaseMarginDeg[0] | UnityGainFreq[0] |  |  |

|-------------------|------------------|--|--|

| 65.00             | 750.0 k          |  |  |

| Clpf3   | Rlpf3   | Clpf1[0] | Clpf2[0] | Rlpf1[0] |

|---------|---------|----------|----------|----------|

| 164.1 f | 28.68 k | 3.174 p  | 164.1 f  | 286.8 k  |

Loop parameter values, set on schematic

| Kd[0]   | Kv[0]   | N0[0]   |  |

|---------|---------|---------|--|

| 7.958 u | 375.0 M | 1.200 k |  |

| Spur_Attenuation |  |  |  |  |  |

|------------------|--|--|--|--|--|

| 54.894           |  |  |  |  |  |

|                  |  |  |  |  |  |

Eqn SpurFreq=25 MHz

Figure 4.1-2 PLL loop filter example

The results shown in Table 4.1-1 correspond to several filter characteristics with cut-off frequency ranging from 100 kHz up to 1/10 of  $f_{REF}$ . Note that the last rows of the table contain capacitor values that are difficult to obtain with external components. These values can be increased by a factor of 10 if the charge pump current is also increased by a factor of 10.

| Spec f <sub>c</sub> | C <sub>3</sub> | R <sub>3</sub> | C <sub>1</sub> | C <sub>2</sub> | R <sub>1</sub> | f <sub>c</sub> | Ph.marg | Spur   |

|---------------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|--------|

| kHz                 | pF             | kΩ             | pF             | pF             | kΩ             | kHz            | degrees | dBc    |

| 100                 | 9.228          | 3.824          | 178.5          | 9.228          | 38.24          | 91.20          | 53.8    | -98.41 |

| 250                 | 1.476          | 9.559          | 28.56          | 1.476          | 95.59          | 229.1          | 53.7    | -76.72 |

| 350                 | 0.753          | 13.38          | 14.57          | 0.753          | 133.8          | 316.2          | 53.8    | -69.57 |

| 500                 | 0.369          | 19.12          | 7.141          | 0.369          | 191.2          | 457.1          | 53.7    | -62.50 |

| 750                 | 0.164          | 28.68          | 3.174          | 0.164          | 286.8          | 691.8          | 53.7    | -54.90 |

| 1000                | 0.093          | 38.24          | 1.785          | 0.093          | 382.4          | 912.0          | 53.8    | -49.70 |

| 2500                | 0.015          | 95.59          | 0.285          | 0.014          | 955.9          | 2291           | 53.7    | -33.71 |

Table 4.1-1 Several loop filer characteristics for  $K_{vco}$  = 375 MHz/V,  $I_{CP}$  = 50  $\mu$ A and  $N_0$  = 1200

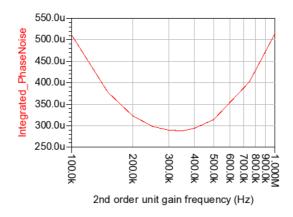

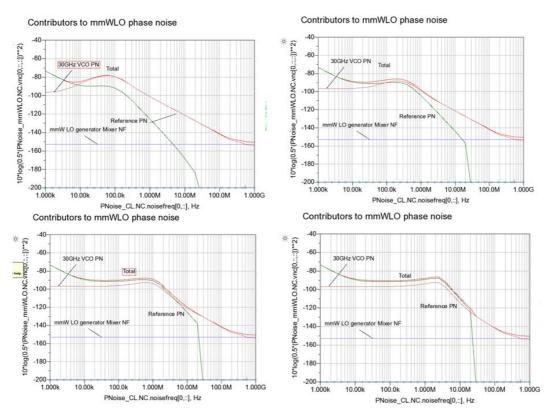

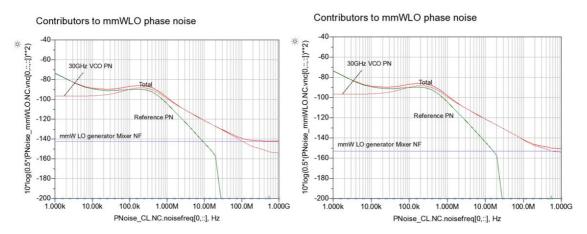

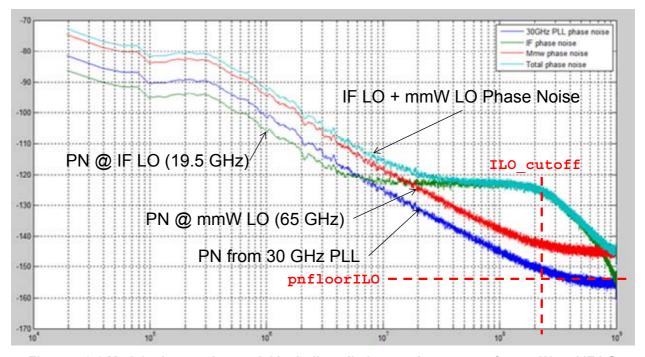

The cut-off frequency of the filter plays an important role in the overall phase-noise characteristic of the FS. The position of the cut-off frequency with respect to the phase noise level of the VCO and the reference determines the relative contribution of each of them to the total phase noise at the output of the PLL. Figure 4.1-3 shows the results of an optimization study where the goal is to minimize the total integrated phase noise. According to this figure, the optimum unit-gain frequency specification for the PLL loop filter is 350 kHz. Table 4.1-2 shows the phase noise data at various offset points for the 65 GHz mmW LO output and Figure 4.1-4 shows the phase noise profiles and the contributors for the same cases.

Figure 4.1-3 Integrated phase noise at the output of the 30 GHz VCO in closed loop for a sweep of specified unity gain frequency parameter

| f <sub>c</sub> | PN @10k | PN @100k | PN@1M   | PN@10M  | PN@1G   |

|----------------|---------|----------|---------|---------|---------|

|                | dBc/Hz  | dBc/Hz   | dBc/Hz  | dBc/Hz  | dBc/Hz  |

| 100 kHz        | -85.08  | -79.31   | -101.10 | -121.31 | -150.52 |

| 350 kHz        | -88.77  | -86.96   | -98.02  | -121.29 | -150.52 |

| 1 MHz          | -88.84  | -90.06   | -88.82  | -119.60 | -150.52 |

| 2.5 MHz        | -88.84  | -90.44   | -87.89  | -108.94 | -150.52 |

Table 4.1-2 Phase noise values of the 65 GHz mmW LO output for  $K_{vco}$  = 375 MHz/V,  $I_{CP}$  = 50  $\mu$ A and  $N_0$  = 1200, Mixer NF=10 dB and various specified unity-gain loop filter frequencies

Figure 4.1-4 Phase noise contributors to the 65 GHz mmW LO output phase noise for increasing filter unity-gain frequency specifications (100 kHz, 350 kHz, 1 MHz and 2 MHz, from left to right and from top to bottom)

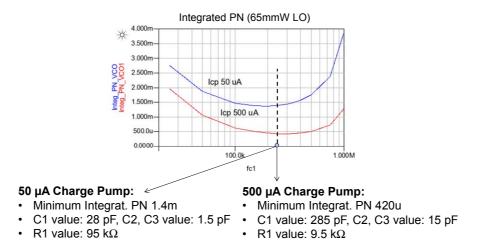

A final study has been performed regarding the loop filter and charge pump components sizing. There is a degree of freedom in the PLL loop design that consists on changing the charge-pump current. If it is multiplied by 10, the capacitor C1 and all the other become multiplied by 10 as well, which results in a reduction by a factor of 10 on the value of the loop filter resistors.

Figure 4.1-5 Impact of CP current and loop-filter resistors on integrated phase noise of the PLL

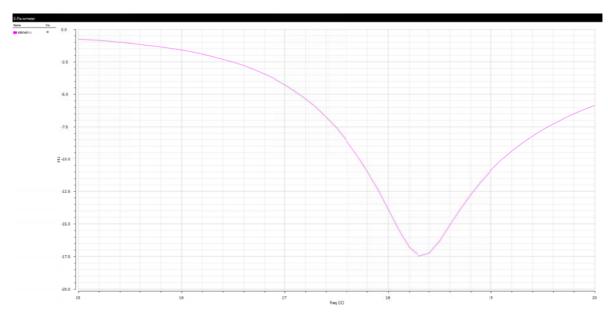

## 4.2 Updated IF LO generator results

The initial phase noise obtained with the previous IF LO generator resulted too high for allowing 64QAM modulation. A redesign of the IF LO generator has been made after identifying the source of the excess phase noise, which corresponded to the noise floor at medium offsets. This noise comes from the multiplication of the noise floor of the shaping circuit that generates the control signals needed to start and stop the pulsed oscillator. These circuits have been redesigned and the noise floor has been reduced from -120 dBc/Hz up to -126 dBc/Hz (DSB phase noise), as shown in Figure 4.2-1 for the 19.5 GHz IF LO frequency case.

Furthermore, the two ILOs have a low-pass characteristic regarding far offset phase noise floor, and contribute to reduce the noise floor for frequency offsets beyond that low-pass cut off frequency. In the case of the ILOs of the IF LO generator, the cut-off frequency offset is of 250 MHz. Since the signal bandwidth is very large, the contribution of the phase noise at far offsets has a significant impact on the Rx and Tx operation. The output level is 1 Vpp at the differential signal found at the output of the 2<sup>nd</sup> ILO (before the 50Ohms buffer of the prototype).

#### Circuit architecture **Pulsed** 500 Sha OSC MHz ping m3 noisefreq=1.000MHz PhN\_ILO2=-104.651 Simulated results (Double Sideband) spec\_var=1.000 Filtering effect of ILOs Output phase noise Excess noise floor Input phase noise (from PLL simulation) added by shaping @ 500 MHz circuitry -180 noisefrea. Hz

Figure 4.2-1 Simulation results of the phase noise characteristics of the IF LO generator of the FS for a specified loop filter unity gain frequency of 350 kHz and LO frequency of 19.5 GHz

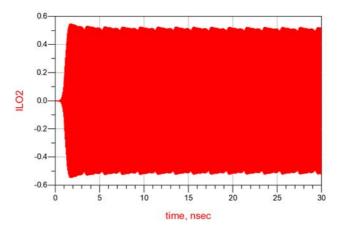

Figure 4.2-2 Output signal of the IF LO generator for LO frequency of 19.5 GHz

### 4.3 I/Q generator

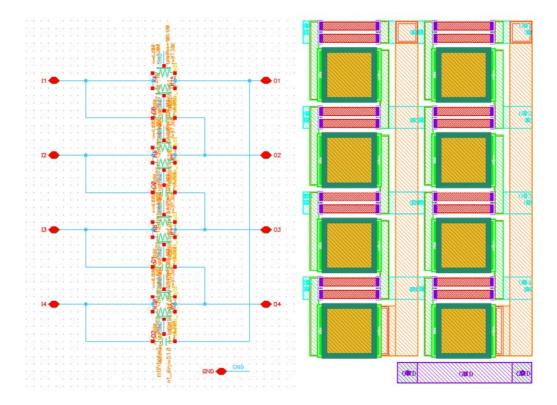

The IF LO generator is completed with a poly-phase filter that generates phase and quadrature differential signals from the input mono-phase differential signal. This circuit will be integrated inside the Tx and Rx, close to the IF mixer. The circuit features a two-stage architecture, based on a basic stage of R-C networks as illustrated in Figure 4.3-1. The layout of the implementation of the two stages is shown next to it.

Figure 4.3-1 Circuit schematic of the basic stage of the poly-phase filter and the layout of the two stages

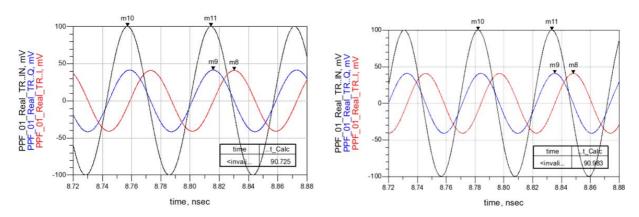

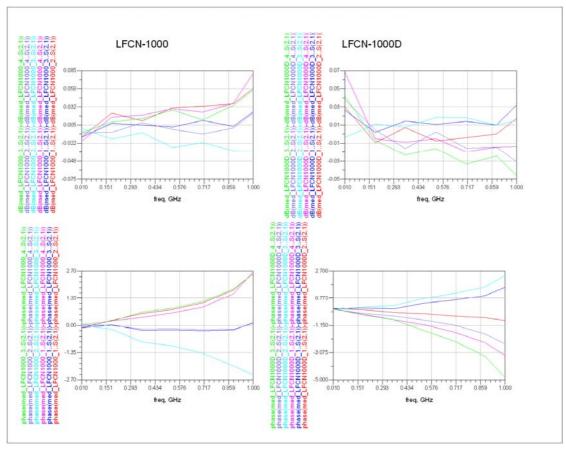

The simulations results for the two LO frequencies corresponding to 2 GHz bandwidth channels are shown below.

Figure 4.3-2 Simulated operation of the I/Q poly-phase generator for 17.5 GHz LO frequency (left) and 19.5 GHz LO frequency (right)

## 4.4 Updated mmW LO generator results

The mmW LO generator block, specifically the programmable selection section based on ILOs has been re-designed to improve the rejection of the non-wanted mmW LO spur and to improve the power consumption. It has been submitted to the  $2^{nd}$  run on BiCMOS55nm technology. Figure 4.4-1 shows the block diagram of the prototype including two ILOs in cascade, a 50  $\Omega$  differential input matching network and a 50  $\Omega$  differential output buffer. The first ILO is loaded by a buffer circuit, shown in Figure 4.4-2 (b). The second ILO is loaded by the same buffer followed by a 50  $\Omega$  stage, shown in Figure 4.4-2 (c).

Figure 4.4-1 Block diagram of the mmW frequency selector section of the mmW LO generator

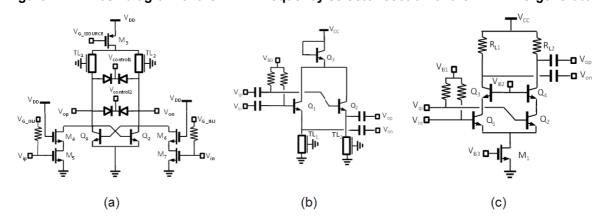

Figure 4.4-2 Schematics of the various circuits composing the mmW LO frequency selector (a) ILO, (b) inter-ILO buffer stage, (c) 50  $\Omega$  output buffer stage

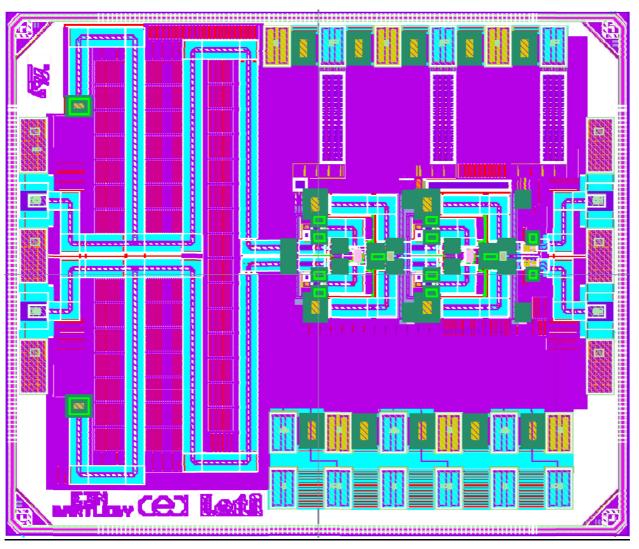

Figure 4.4-3 Layout view of the mmW LO frequency selector prototype

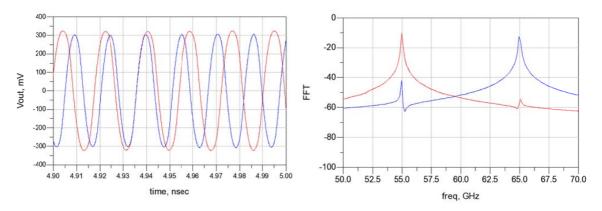

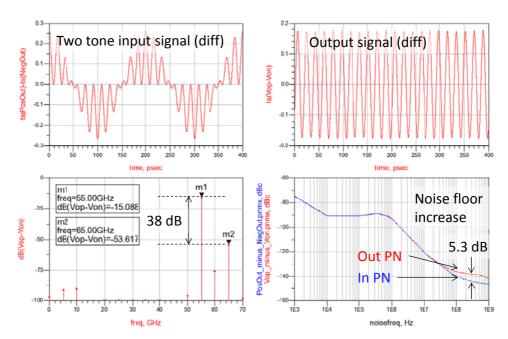

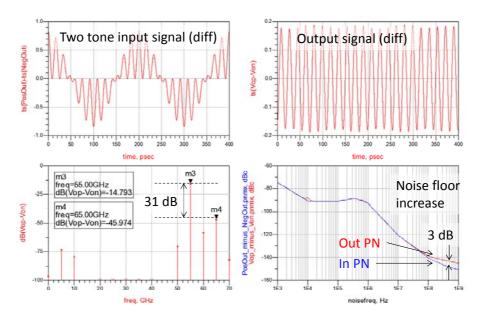

Figure 4.4-4 shows the output signal obtained with a -10 dBm input signal consisting in two tones at 55 GHz and 65 GHz for the two possible selection modes (red and blue). The rejection of the non-wanted mmW LO signal is greater than 30 dB en both cases. The output amplitude is 600mVpp for both cases.

Figure 4.4-4 Time and frequency domain operation of the mmW LO frequency selector for a -10dBm input

Due date: 30 June 2014

In order to evaluate the impact of output buffers on the phase noise floor, another analysis has been performed. The data from the buffers to be used on the Rx and Tx have been used to add a last stage on the circuit schematic of the mmW LO frequency selection ILOs chain, as shown in Figure 4.4-5:

Figure 4.4-5 Test bench used for the simulation of the impact of the ILOs and the mmW LO buffer on the phase noise

The conclusion of this study is that the contribution of the buffers to the output phase noise depends on the input signal amplitude. For larger signal amplitude at the input of the ILOs chain, the impact on the phase noise floor is smaller. However, there is a trade-off with the rejection of the non-wanted mm LO signal at the output (note that the input signal contains the two LO frequencies, 55 GHz and 65 GHz but that the output signal must contain only one of the two tones). This trade-off is illustrated by Figure 4.4-6 and Figure 4.4-7.

Figure 4.4-6 Results of phase noise and rejection of the adjacent LO freq. for the lower amplitude case

Figure 4.4-7 Results of phase noise and rejection of the adjacent LO freq. for the higher amplitude case

# 4.5 mmW LO two tones generator based on a mixer

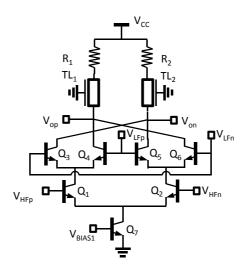

The two-tone signal required as input for the mmW LO frequency selector is implemented using a Gilbert cell mixer as the one shown in Figure 4.5-1.

Figure 4.5-1 mmW LO two-tones generator based on a mixer

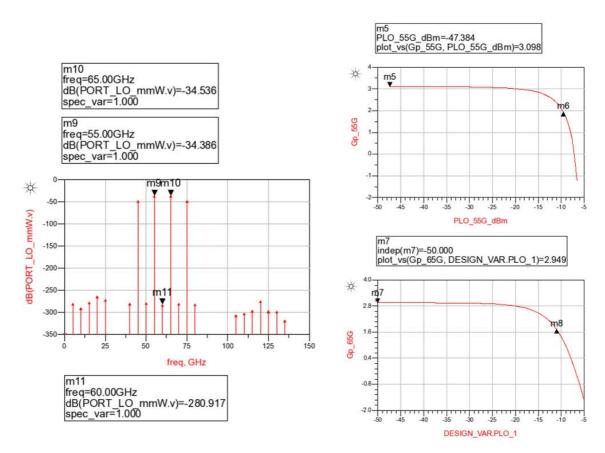

The circuit generates the two tones by mixing the 60 GHz frequency signal output by the doubler 30 GHz VCO of the PLL and the 5 GHz intermediate frequency generated also by the PLL after a division by 6 of the 30 GHz VCO frequency. Simulation results are shown in the next figures.

Figure 4.5-2 Frequency domain and conversion gain of the two-tones mmW LO generator

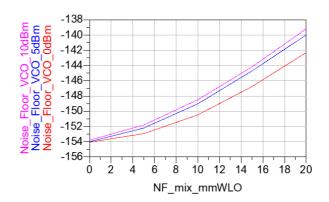

The noise floor of the mmW LO signals generated by the mmW LO two-tones for high offsets is limited by either the noise floor of the VCO inside the PLL or by the NF of the mmW LO generator mixer, depending on which is higher. The NF of the mixer has a different impact for different VCO power levels. Figure 4.5-3 and Figure 4.5-4 present the results of the behavioural simulations of the FS for different NF values and VCO power levels. A higher VCO amplitude results in a larger impact of the same NF value for the mixer.

Figure 4.5-3 Impact of the NF of the mmW LO generator mixer and the VCO amplitude on the phase noise floor at large offsets of the 65 GHz mmW LO output

Figure 4.5-4 Impact of the NF of the mmW LO generator mixer and the VCO amplitude on the phase noise floor at large offsets of the 65 GHz mmW LO output; left NF = 20 dB, right NF = 10 dB

# 4.6 Overall Signal Generator Results

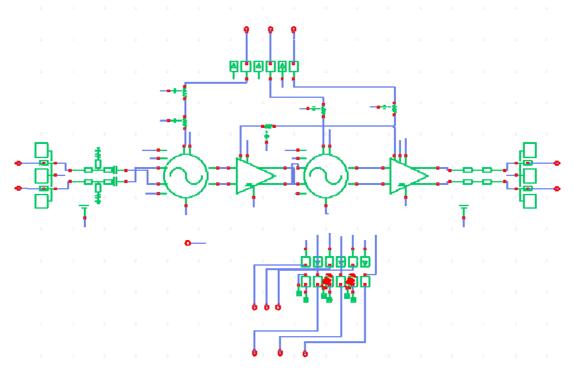

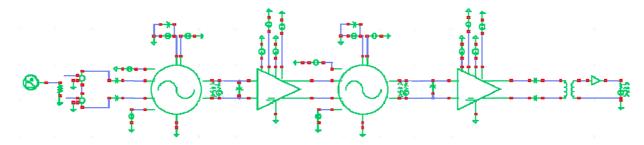

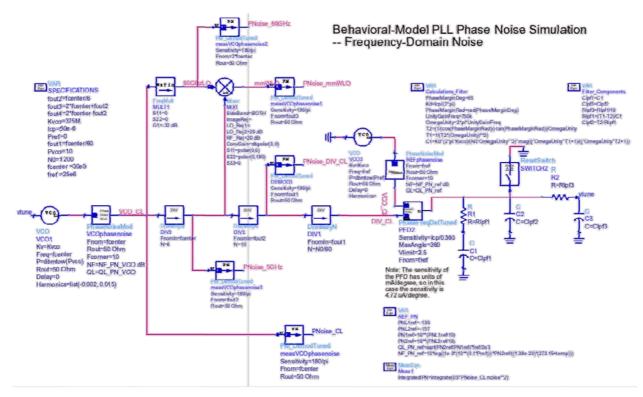

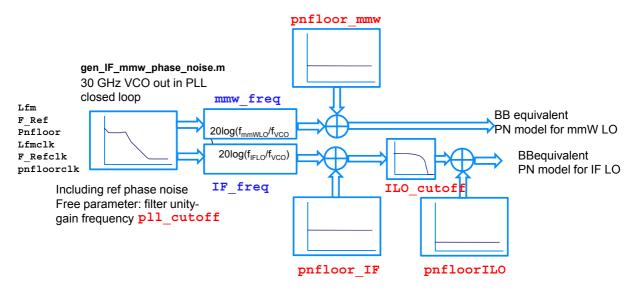

A behavioural model of the complete signal generator comprising the PLL and the IF and mmW LO generators has been implemented. The core of the model consists on the PLL loop plus some mixers, multipliers and dividers that generate the input signals to the IF and mmW LO generators. The phase noise at those intermediate signals is characterized and used as input for the post-layout, circuit level simulation of the ILO chains of the mmW and IF LO signal generators.

The goal of this model is to provide a simulation environment for the optimization and validation of the signal generator block in the context of the overall E-band Tx and Rx. The simulation results in terms of phase noise and signal levels are used as parameters for a Matlab model that allows to add phase noise to the system level simulation of the complete Rx and Tx, therefore allowing an investigation on the impact of the phase noise on the link operation as well as a validation of the compensation algorithms implemented in the digital baseband.

Figure 4.6-1 shows the block diagram of the PLL behavioural model including some additional blocks for the generation of the IF and mmW LO signal generators input signals.

Figure 4.6-1 Block diagram of the behavioural model of the PLL and additional sub-blocks

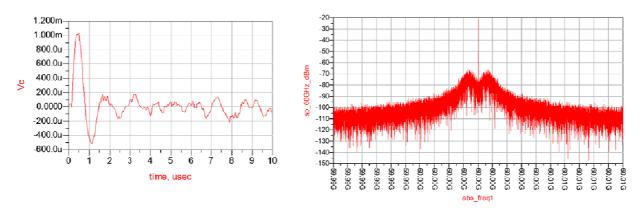

Figure 4.6-2 shows an example of time domain loop locking transient and the spectrum of the 60GHz output signal including phase noise. The lock time is around 3ns. The variations after the locking are due to the phase noise introduced in the VCO and input reference oscillators.

Figure 4.6-2 Locking transient simulation of the PLL and spectrum of the 60 GHz signal output, including phase noise

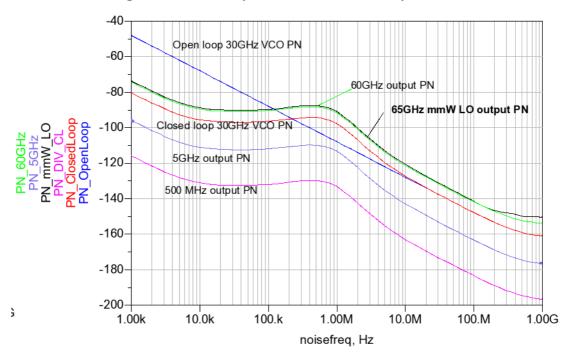

Figure 4.6-3 shows phase noise simulation results at various outputs of the behavioural model: the 65 GHz mmW LO output tone (before the mmW LO frequency selector), the 5GHz and 500 MHz output frequency signals and the open loop 30 GHz VCO phase noise model.

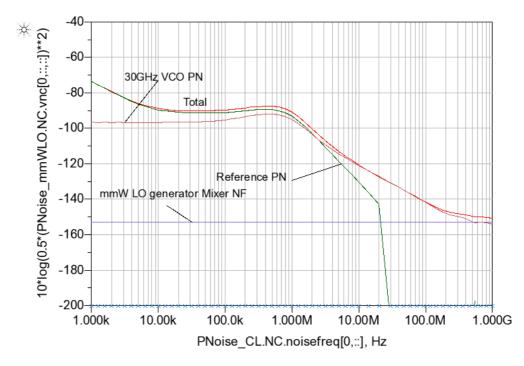

Figure 4.6-4 allows investigating the main contributors to the 65 GHz mmW LO frequency term phase noise. Note that the ILOs of the mmW frequency selector will not add phase noise to this signal.

### Single Sideband Open- and Closed-Loop VCO Phase Noise

Figure 4.6-3 Single sideband phase noise at different outputs of the frequency generator for the 750 kHz loop filter case

# Contributors to mmWLO phase noise

Figure 4.6-4 Analysis of the different contributors to phase noise at the 65 GHz mmW LO output of the frequency generator for the 750 kHz loop filter case

The phase noise profiles shown in the previous figures are modelled in Matlab in order to allow for system level studies of the impact of the phase noise on the overall Rx/Tx and even in a complete link including modulation, transmission, reception, demodulation and detection, with specific algorithms implemented in digital baseband to compensate for various RF and analog impairments such as frequency and phase drift, I/Q mismatching and phase noise. The implementation of such phase noise generation process is illustrated in Figure 4.6-5. The final results of the frequency generator block can be summarized with Figure 4.6-6.

Figure 4.6-5 Illustration of the Matlab process for generating phase noise profiles for system level simulations from the signal generation phase noise results

Figure 4.6-6 Matlab phase noise model including all phase noise sources for mmW and IF LO outputs of the signal generator

Table 4.6-1 and Table 4.6-2 show a comparison between the resulting performance of the various blocks of the signal generator and the updated specifications of D.1.2.2. Note that all phase noise values are obtained based on the phase noise of the 60 GHz output of the PLL, as obtained by system level simulations including the phase noise of the 30 GHz VCO and frequency doubler output presented in D.2.1. Note that the results concerning phase noise have been transformed in single-sideband noise from the double-sideband results shown in some of the figures above in order to compare them with the specifications, which were defined as single-sideband phase noise.

| Parameter                                                                 | Spec | Result | Units  | Fulfilled |

|---------------------------------------------------------------------------|------|--------|--------|-----------|

| SSB Phase noise @ 1Mhz, IF LO for 64QAM (16-21 GHz)                       | -105 | -108   | dBc/Hz | Yes       |

| 1st SSB Phase noise floor, below ILO cut-off, IF LO for 64QAM (16-21 GHz) | -126 | -129   | dBc/Hz | Yes       |

| ILO filter cut-off freq., IF LO for 64QAM (16-21 GHz)                     | 250  | 250    | MHz    | Yes       |

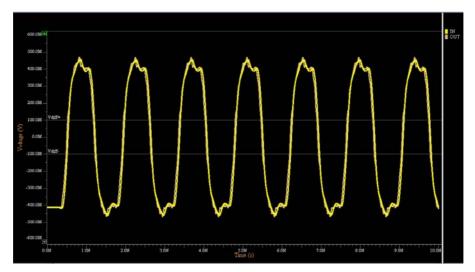

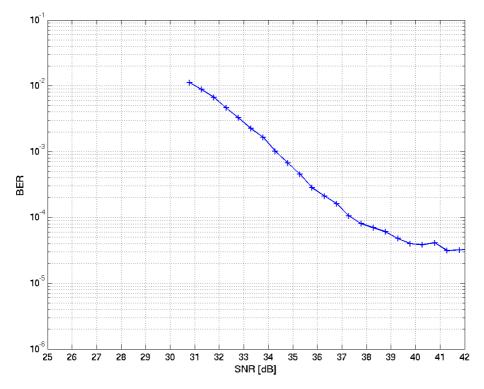

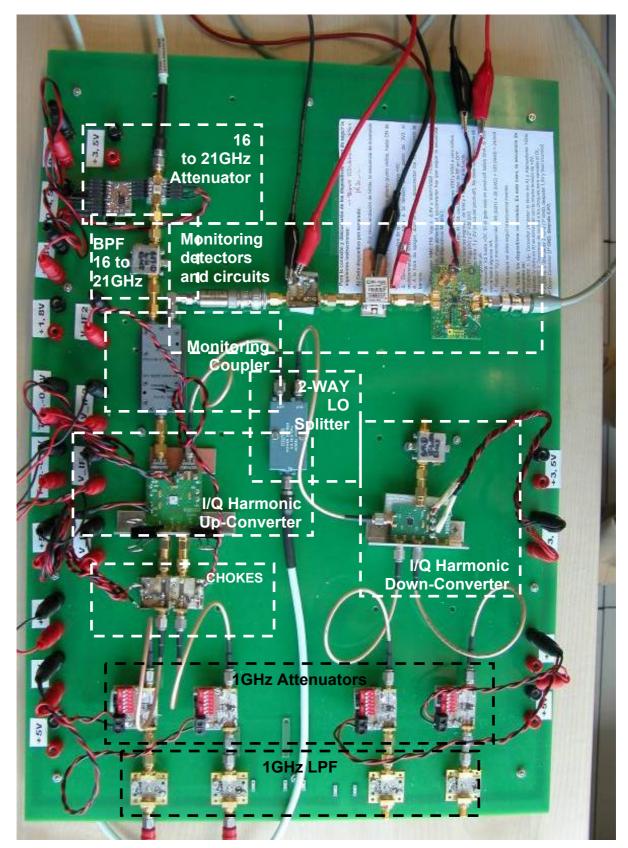

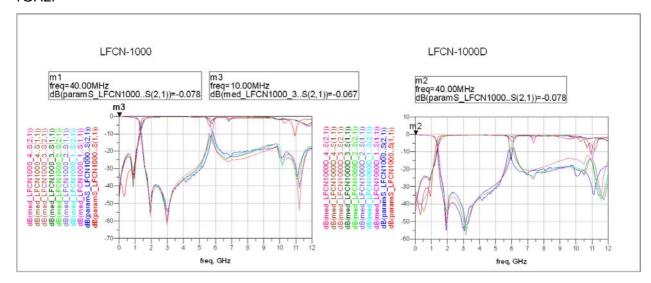

| 2nd SSB Phase noise floor, IF LO for 64QAM (16-21 GHz)                    | -155 | -159   | dBc/Hz | Yes       |