## HIGH PERFORMANCE AND EMBEDDED ARCHITECTURE AND COMPILATION

Project Acronym: HiPEAC

Project full title: High Performance and Embedded Architecture and Compilation

Grant agreement no: ICT-217068

DELIVERABLE 3.1

# **SPREADING EXCELLENCE REPORT**

| 1. | . Sı | ummary on Spreading Excellence                     | . 3 |

|----|------|----------------------------------------------------|-----|

| 2. | . T  | ask 3.1: Conference                                | . 4 |

|    | 2.1. | HiPEAC 2008 Conference, Goteborg                   | . 4 |

|    | 2.2. | HiPEAC 2009 Conference, Paphos                     | 10  |

|    | 2.3. | Conference Ranking                                 | 16  |

| 3. | . T  | ask 3.2: Summer School                             | 16  |

|    | 3.1. | 4 <sup>th</sup> International Summer School – 2008 | 16  |

|    | 3.2. | 5 <sup>th</sup> International Summer School – 2009 | 21  |

| 4. | . T  | ask 3.3: HiPEAC Journal                            | 22  |

| 5. | . T  | ask 3.4: HiPEAC Roadmap                            | 23  |

| 6  | . T  | ask 3.5: HiPEAC Newsletter                         | 24  |

|    | 6.1. | Period 1 issues                                    | 24  |

| 7. | . T  | ask 3.6: HiPEAC Technical Reports                  | 26  |

|    | 7.1. | Publication database                               | 26  |

|    | 7.2. | Tech Reports                                       | 26  |

| 8  | . T  | ask 3.7: Web Site                                  | 27  |

|    | 8.1. | Developments                                       | 27  |

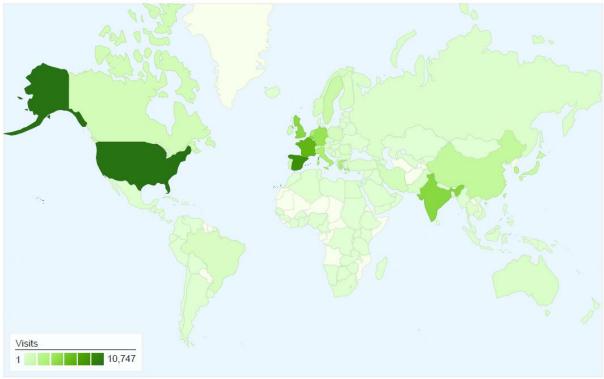

|    | 8.2. | Website numbers                                    | 29  |

|    | 8.3. | Conclusions and future work                        | 31  |

| 9. | . T  | ask 3.8: Web Seminars                              | 31  |

| 1  | 0. T | ask 3.9: Industrial Workshops                      | 32  |

|    | 10.1 | . Spring Industrial Workshop                       | 32  |

|    | 10.2 | . Autumn Industrial Workshop                       | 34  |

| 1  | 1. T | ask 3.10: Promoting HiPEAC Start-Ups               | 38  |

| 1  | 2. T | ask 3.11: HiPEAC Award                             | 38  |

|    | 12.1 | . Selected conferences                             | 39  |

|    | 12.2 | . 2008 results                                     | 39  |

# 1. Summary on Spreading Excellence

An important aspect of a network of excellence is to create visibility for its members and for the research carried out in the network, while at the same time integrating the network members.

#### Improving the visibility of our community

The role of the *Conference* and *Journal* are to improve the scientific visibility in the area of high-performance and embedded processors. They will help in the *promotion of talented* young researchers by inviting them in the visible role of program committee member or reviewer for the journal.

On top of this, publications at other major conferences will be stimulated through an original *Award* program.

The *Newsletter* aims at publicising the activities of our community beyond the strict scientific community: within industry, among public officials, and towards Asia, whose researchers only infrequently participate in scientific forums at this moment. At the same time, it is a means for promoting HiPEAC groups and achievements beyond the standard scientific articles.

The HiPEAC Technical Reports allow the rapid presentation and dissemination of academic work, time stamping hot research ideas, and help show the breadth and scope of the HiPEAC community.

The *Roadmap* helps the HiPEAC community to regularly revisit the key scientific challenges, and it helps disseminating the HiPEAC vision beyond the HiPEAC community.

#### **Integrating our community**

The *Summer School* aims at raising the standards of our PhD students and members by confronting them with renowned teachers in our domains, whatever their geographic origin. It is also a networking event resulting in long-lasting individual links among students, between students and faculty or engineers, and among faculty and engineers.

The *Web Seminars* offers a continuous training cycle for the community, and they also offer an opportunity for researchers, junior and senior alike, to publicise their activity within the HiPEAC community and beyond, possibly triggering new collaborations. The *industrial workshops* are networking events between academia and companies where the academics learn more about the industrial challenges, and the industrial researchers are confronted with the lastest academic research results.

Beyond the cooperation with large companies, we also aim at *stimulating the development of Start-ups* by HiPEAC researchers. Currently, 7 HiPEAC researchers have set up innovative SMEs, and we intend to further support these companies as well as stimulate new initiatives.

Finally, the Web Site serves as a meeting place for all HiPEAC activities.

The Spreading Excellence Program consists of 11 specific tasks:

#### 2. Task 3.1: Conference

The conference is one of the main public events organised by the HiPEAC network. It is quite successful, attracting a wide audience and offering high quality workshops and tutorials.

The topics called for in the conference and the workshops are the topics of the HiPEAC research agenda as described in the research program. The conference and workshops are completely open to both HiPEAC members and non-members from all over the world.

The conference is supervised by a steering committee, which decides on the chairs and the location of the conference and reports to the HiPEAC steering committee. The logistics of the conference are handled by the chairs, supported by the HiPEAC technical and administrative staff.

# 2.1. HiPEAC 2008 Conference, Goteborg

The HiPEAC 2008 Conference, which was organised by Chalmers in Goteborg, was funded by HiPEAC1. However, we will provide a short overview of this conference here as well.

#### The Conference

The conference was organised by Chalmers, and was held at the Chalmers Conference Center, in Goteborg, Sweden.

The Conference was a two-day event, from January 28 to January 29, 2008.

#### **Paper Acceptance Rate**

77 papers from Europe, USA and Asia were submitted to the conference. 25 were presented at the conference (32% acceptance rate).

#### **Conference Committee**

The following people were involved in organising the conference:

| GENERAL CO-CHAIRS |                                   |             |  |  |

|-------------------|-----------------------------------|-------------|--|--|

| Per Stenström     | Chalmers University of Technology | Sweden      |  |  |

| Michel Dubois     | University of Southern California | USA         |  |  |

| PROGRAM CO-CHAIRS | PROGRAM CO-CHAIRS                 |             |  |  |

| Manolis Katevenis | University of Crete/FORTH         | Greece      |  |  |

| Rajiv Gupta       | University of California          | Riverside   |  |  |

| PROGRAM COMMITTEE |                                   |             |  |  |

| Angelos Bilas     | FORTH & Univ. of Crete            | Greece      |  |  |

| Mats Brorsson     | KTH                               | Sweden      |  |  |

| Koen De Bosschere | University of Ghent               | Belgium     |  |  |

| Jack Davidson     | University of Virginia            | USA         |  |  |

| Marc Duranton     | NXP Semiconductors                | Netherlands |  |  |

| Babak Falsafi     | Carnegie Mellon University        | USA         |  |  |

| Paolo Faraboschi  | HP Labs                           | Spain       |  |  |

| Kristian Flautner | ARM                               | UK          |  |  |

| Chris Gniady          | University of Arizona             | USA         |

|-----------------------|-----------------------------------|-------------|

| Wen-mei Hwu           | University of Illinois            | USA         |

| Paolo Ienne           | EPFL                              | Switzerland |

| Norm Jouppi           | HP Labs                           | USA         |

| Mahmut Kandemir       | Penn. State Univ.                 | USA         |

| Stefanos Kaxiras      | University of Patras              | Greece      |

| Christos Kozyrakis    | Stanford University               | USA         |

| Scott Mahlke          | Univ. of Michigan                 | USA         |

| Peter Marwedel        | Univ. Dortmund                    | Germany     |

| Avi Mendelson         | Intel                             | Israel      |

| Andreas Moshovos      | University of Toronto             | Canada      |

| Mike O'Boyle          | Edinburgh University              | UK          |

| Kunle Olukotun        | Stanford University               | USA         |

| Yunheung Paek         | Seoul National University         | Korea       |

| Santosh Pande         | Georgia Inst. of Technology       | USA         |

| Yale Patt             | University of Texas at Austin     | USA         |

| Alex Ramirez          | Univ. Pol. de Cataluna & BSC      | Spain       |

| Lawrence Rauchwerger  | Texas A&M University              | USA         |

| John Regehr           | University of Utah                | USA         |

| Andre Seznec          | INRIA                             | France      |

| Guri Sohi             | University of Wisconsin           | USA         |

| Olivier Temam         | INRIA                             | France      |

| Josep Torrellas       | University of Illinois            | USA         |

| Mateo Valero          | Univ. Pol. de Cataluna & BSC      | Spain       |

| David Whalley         | Florida State University          | USA         |

| Sudhakar Yalamanchili | Georgia Institute of Technology   | USA         |

| WORKSHOPS/TUTORIALS   | CHAIR                             | ·           |

| Mats Brorsson         | KTH                               | Sweden      |

| LOCAL ARRANGEMENTS (  | CHAIR                             |             |

| Ewa Wäingelin         | Chalmers University of Technology | Sweden      |

| FINANCE CHAIR         | , , , , , ,                       |             |

| Per Waborg            | Chalmers University of Technology | Sweden      |

| Wouter De Raeve       | Ghent University                  | Belgium     |

| PUBLICITY CHAIR       |                                   | <u> </u>    |

| Mike O'Boyle          | University of Edinburgh           | U.K.        |

| PUBLICATIONS CHAIR    |                                   | -           |

| Theo Ungerer          | University of Augsburg            | Germany     |

| SUBMISSIONS CHAIR     |                                   |             |

| Michiel Ronsse        | Ghent University                  | Belgium     |

| WEB CHAIR             |                                   |             |

| Sylvie Detournay      | Ghent University                  | Belgium     |

| STEERING COMMITTEE    |                                   |             |

| Mateo Valero          | UPC                               | Spain       |

|                       |                                   | •           |

| Anant Agarwal      | MIT                      | USA       |

|--------------------|--------------------------|-----------|

| Koen De Bosschere  | Ghent University         | Belgium   |

| Mike O'Boyle       | University of Edinburgh  | UK        |

| Brad Calder        | University of California | USA       |

| Rajiv Gupta        | University of California | Riverside |

| Wen-mei W. Hwu     | UIUC                     | USA       |

| Josep Llosa        | UPC                      | Spain     |

| Margaret Martonosi | Princeton University     | USA       |

| Per Stenström      | Chalmers University      | Sweden    |

| Olivier Temam      | INRIA Futurs             | France    |

# **Conference Program**

# Day 1: Monday January 28

| 9:00 -  | KEYNOTE. Supercomputing for the Future, Supercomputing from the Past                                                  |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| 10:00   | Mateo Valero, Barcelona Supercomputing Center                                                                         |

| 10:30 - | SESSION I. Multithreaded and Multicore Processors                                                                     |

| 12:00   | CHAIR: Georgi Gaydadjiev, T. U. Delft, Netherlands                                                                    |

|         | MIPS MT: A Multithreaded RISC Architecture for Embedded and Real-Time Processing                                      |

|         | Kevin D. Kissell                                                                                                      |

|         | MIPS Technolgies Inc.                                                                                                 |

|         | rMPI: Message Passing on Multicore Processors with On-Chip Interconnect                                               |

|         | James Psota and Anant Agarwal                                                                                         |

|         | MIT                                                                                                                   |

|         | Modeling Multigrain Parallelism on Heterogeneous Multi-core Processors: A Case Study of the Cell BE                   |

|         | Filip Blagojevic, Xizhou Feng, Kirk W. Cameron and Dimitrios S. Nikolopoulos                                          |

|         | Virginia Tech                                                                                                         |

| 13:30 - | SESSION IIa. Reconfigurable - ASIP                                                                                    |

| 15:00   | CHAIR: Chris Gniady, University of Arizona, USA                                                                       |

|         | BRAM-LUT tradeoff on a Polymorphic DES Design                                                                         |

|         | Ricardo Chaves, Blagomir Donchev, Georgi Kuzmanov, Leonel Sousa and Stamatis Vassiliadis                              |

|         | Instituto Superior Tecnoci/INESC-ID and TUDelft                                                                       |

|         | Architecture Enhancements For The ADRES Coarse-Grained Reconfigurable Array                                           |

|         | Frank Bouwens, Mladen Berekovic, Bjorn De Sutter and Georgi Gaydadjiev                                                |

|         | IMEC and TUDelft                                                                                                      |

|         | Implementation of an UWB Impulse-Radio Acquisition and Despreading Algorithm on a Low Power ASIP                      |

|         | Jochem Govers, Jos Huisken, Mladen Berekovic, Olivier Rousseaux, Frank Bouwens, Michael de Nil and Jef van Meerbergen |

|         | Eindhoven University of Technology, IMEC, Philips Research Eindhoven and Silicon Hive                                 |

| 13:30 - | SESSION IIb. Compiler Optimizations                                                                                   |

| 15:00   | CHAIR: Koen De Bosschere, University of Ghent, Belgium                                                                |

|         | Fast Bounds Checking Using Debug Register                                                                             |

|         | Tzi-cker Chiueh                                                                                                       |

|         | Stony Brook University                                                                                                |

|         | Studying Compiler Optimizations on Superscalar Processors through Interval Analysis                                   |

|         |                                                                                                                       |

|         | Stijn Eyerman, Lieven Eeckhout and James E. Smith                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------|

|         | Ghent University and University of Wisconsin-Madison                                                                 |

|         | An Experimental Environment Validating the Suitability of CLI as an Effective Deployment Format for Embedded Systems |

|         | Marco Cornero, Roberto Costa, Ricardo Fernandez Pascual, Andrea Ornstein and Erven<br>Rohou                          |

|         | STMicroelectronics                                                                                                   |

| 15:30 - | SESSION III. Industrial Processors & Application Parallelization                                                     |

| 17:00   | CHAIR: Mike O'Boyle, Edinburgh University, UK                                                                        |

|         | Compilation Strategies for Reducing Code Size on a VLIW Processor with Variable Length Instructions                  |

|         | Todd Hahn, Dineel Sule, Eric Stotzer and Mike Asal                                                                   |

|         | Texas Instruments                                                                                                    |

|         | Experiences with Parallelizing a Bio-Informatics Program on the Cell BE                                              |

|         | Hans Vandierendonck, Sean Rul, Michiel Questier and Koen De Bosschere                                                |

|         | Ghent University                                                                                                     |

|         | Drug Design Issues on the Cell BE                                                                                    |

|         | Harald Servat, Cecilia Gonzalez-Alvarez, Xavier Aguilar, Daniel Cabrera-Benitez and Daniel Jimenez-Gonzalez          |

|         | Barcelona Supercomputing Center and Universitat Politecnica de Catalunya                                             |

# Day 2: Tuesday January 29

| 8:30 -  | SESSION IV. Power-Aware Techniques                                                                                                         |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 10:00   | CHAIR: Mats Brorsson, KTH, Sweden                                                                                                          |

|         | COFFEE: COmpiler Framework For Energy-aware Exploration                                                                                    |

|         | Praveen Raghavan, Andy Lambrechts, Javed Absar, Murali Jayapala, Francky Catthoor and Diederik Verkest                                     |

|         | KULeuven, IMEC, STMicroelectronics and VUB                                                                                                 |

|         | Integrated CPU and Cache Power Management in Multiple Clock Domain Processors                                                              |

|         | Nevine AbouGhazaleh, Bruce Childers, Daniel Mosse and Rami Melhem                                                                          |

|         | University of Pittsburgh                                                                                                                   |

|         | Variation-Aware Software Techniques for Cache Leakage Reduction using Value-Dependence of SRAM Leakage due to Within-Die Process Variation |

|         | Maziar Goudarzi, Tohru Ishihara and Hamid Noori                                                                                            |

|         | Kyushu University                                                                                                                          |

| 10:30 - | SESSION V. High-Performance Processors                                                                                                     |

| 12:00   | CHAIR: Kevin Kissell, MIPS Technolgies Inc., France                                                                                        |

|         | The Significance of Affectors and Affectees Correlations for Branch Prediction                                                             |

|         | Yiannakis Sazeides, Andreas Moustakas, Kypros Constantinides and Marios Kleanthous                                                         |

|         | University of Cyprus and University of Michigan                                                                                            |

|         | Turbo-ROB: A Low-Cost, Simple Checkpoint/Restore Accelerator                                                                               |

|         | Patrick Akl and Andreas Moshovos                                                                                                           |

|         | University of Toronto                                                                                                                      |

|         | LPA: A First Approach to the Loop Processor Architecture                                                                                   |

|         | Alejandro Garcia, Oliverio J. Santana, Enrique Fernandez, Pedro Medina and Mateo Valero                                                    |

|         | Barcelona Supercomputing Center, University Politecnica de Catalunya and Universidad de<br>Las Palmas de Gran Canaria                      |

| 13:30 - | SESSION VI. Profiles: Collection and Analysis                                                                                              |

| 15:00   | CHAIR: Dimitrios Nikolopoulos, FORTH, Crete, Greece                                                     |

|---------|---------------------------------------------------------------------------------------------------------|

|         | Complementing Missing and Inaccurate Profiling using a Minimum Cost Circulation Algorithm               |

|         | Roy Levin, Gad Haber and Ilan Newman                                                                    |

|         | Haifa University and IBM Haifa Labs                                                                     |

|         | Using Dynamic Binary Instrumentation to Generate Multi-Platform SimPoints: Methodology and Accuracy     |

|         | Vincent M. Weaver and Sally A. McKee                                                                    |

|         | Cornell University                                                                                      |

|         | Phase Complexity Surfaces: Characterizing Time-Varying Program Behavior                                 |

|         | Frederik Vandeputte and Lieven Eeckhout                                                                 |

|         | Ghent University                                                                                        |

| 15:30 - | SESSION VII. Optimizing Memory Performance                                                              |

| 17:30   | CHAIR: Andreas Moshovos, University of Toronto, Canada                                                  |

|         | MLP-Aware Dynamic Cache Partitioning                                                                    |

|         | Miquel Moreto, Francisco J. Cazorla, Alex Ramirez and Mateo Valero                                      |

|         | Barcelona Supercomputing Center and Universitat Politecnica de Catalunya                                |

|         | Compiler Techniques for Reducing Data Cache Miss Rate on a Multithreaded Architecture                   |

|         | Subhradyuti Sarkar and Dean M. Tullsen                                                                  |

|         | UCSD                                                                                                    |

|         | Code Arrangement of Embedded Java Virtual Machine for NAND Flash Memory                                 |

|         | Chun-Chieh Lin and Chuen-Liang Chen                                                                     |

|         | National Taiwan University                                                                              |

|         | Aggressive Function Inlining: Preventing Loop Blockings in the Instruction Cache                        |

|         | Yosi Ben Asher, Omer Boehm, Daniel Citron, Gadi Haber, Moshe Klausner, Roy Levin and<br>Yousef Shajrawi |

|         | Haifa University and IBM Research Lab, Haifa                                                            |

# **Conference Attendance**

The conference was attended by 256 participants.

53 attendants came from industry. The attending companies were:

| ABB Network Management                     | IAR Systems            | Saab Microwave Systems       |

|--------------------------------------------|------------------------|------------------------------|

| ARM                                        | IBM                    | STMicroelectronics           |

| CAPS Enterprise                            | Infineon Technologies  | Technion                     |

| Central Research Laboratory, Hitachi, Ltd. | Intel Corporation      | Texas Instruments            |

| Codeplay Software Ltd.                     | MIPS Technologies Inc. | Thales Research & Technology |

| Ericsson                                   | Nema Labs              | Volvo Technology             |

| НР                                         | NXP Semiconductors     |                              |

The attendants came from 26 different countries:

| Sweden          | 47  |

|-----------------|-----|

| Spain           | 41  |

| France          | 24  |

| UK              | 23  |

| USA             | 19  |

| Belgium         | 16  |

| The Netherlands | 15  |

| Germany         | 15  |

| Norway          | 11  |

| Italy           | 10  |

| Israel          | 5   |

| Greece          | 4   |

| Cyprus          | 4   |

| Russia          | 3   |

| Portugal        | 3   |

| Turkey          | 2   |

| Switzerland     | 2 2 |

| Japan           |     |

| Iran            | 2   |

| Finland         | 2   |

| Taiwan          | 1   |

| Serbia          | 1   |

| Scotland        | 1   |

| Poland          | 1   |

| Denmark         | 1   |

| Canada          | 1   |

The majority of the attendants came from Sweden, where the conference was held.

133 conference-goers were member of or affiliated with HiPEAC. This means that almost half of the attendants did not have a formal connection to HiPEAC.

#### **Student Grants**

We were able to give a grant to 42 PhD students. The grant waives the registration fee. All students who applied for a grant were given one.

#### **Workshops and Tutorials**

On January 27, 4 workshops were organised, as well as 1 tutorial:

- MULTIPROG workshop (Programmability Issues for Multi-Core Computers)

- SMART'08 workshop (Statistical and Machine learning approaches to ARchitectures and compilaTion)

- 2nd HiPEAC Workshop on Reconfigurable Computing

- INA-OCMC workshop (Interconnection Network Architectures: On-Chip, Multi-Chip)

- The Sunflower Toolsuite Tutorial

The workshops and tutorials were attended in total by 201 people.

# 2.2. HiPEAC 2009 Conference, Paphos

The 4<sup>th</sup> International Conference on High Performance and Embedded Architectures and Compilers was organised by the University of Cyprus, in Paphos, Cyprus

#### The Conference

The Conference took place from January 25-28, 2009, at the Amathus Hotel in Paphos, Cyprus. For the first time the conference was extended to a three-day programme, again preceded by a full day of workshops and tutorials.

#### **Paper Acceptance Rate**

This year we received 97 paper submissions, of which 14 submissions were co-authored by a program committee member. Papers were submitted from 20 different nations (approximately 46% from Europe, 15% from Asia, 32% from North America, 4% from Africa and the Middle East, and 3% from South America).

27 papers were accepted, i.e., an acceptance rate of 28%.

#### **Conference Committee**

The following people were involved in the organisation of the conference:

| GENERAL CO-CHAIRS  |                         |        |

|--------------------|-------------------------|--------|

| Andre Seznec       | IRISA/INRIA             | France |

| Joel Emer          | INTEL/MIT               | USA    |

| PROGRAM CO-CHAIRS  |                         |        |

| Michael O'Boyle    | University of Edinburgh | UK     |

| Margaret Martonosi | Princeton University    | USA    |

| PROGRAM COMMITTEE  |                         |        |

| David Albonesi     | Cornell University      | USA    |

| Eduard Ayguade     | UPC                     | Spain  |

| Francois Bodin     | CAPS Enterprise         | France |

| John Cavazos       | University of Delaware  | USA    |

| Albert Cohen            | INRIA                         | France      |

|-------------------------|-------------------------------|-------------|

| Marco Cornero           | ST                            | Italy       |

| Lieven Eeckhout         | Ghent University              | Belgium     |

| Guang Gao               | University of Delaware        | USA         |

| Thomas Gross            | ETH Zurich                    | Switzerland |

| Michael Hind            | IBM                           | USA         |

| Mary J. Irwin           | Pennsylvania State University | USA         |

| Russell Joseph          | Northwestern University       | USA         |

| Ben Juurlink            | TU Delft                      | Netherlands |

| Stefanos Kaxiras        | University of Patras          | Greece      |

| Rainer Leupers          | University of Aachen          | Germany     |

| Gabriel Loh             | Georgia Tech University       | USA         |

| José Martínez           | Cornell University            | USA         |

| Bilha Mendelson         | IBM Research                  | Israel      |

| Andreas Moshovos        | University of Toronto         | Canada      |

| David Padua             | UIUC                          | USA         |

| Markus Pueschel         | CMU                           | USA         |

| Li-Shiuan Peh           | Princeton University          | USA         |

| Lawrence Rauchwerger    | Texas A&M Univ.               | USA         |

| Ronny Ronen             | Intel Corp.                   | Israel      |

| Yiannakis Sazeides      | University of Cyprus          | Cyprus      |

| Vassos Soteriou         | Cyprus Univ. of Technol.      | Cyprus      |

| Per Stenström           | Chalmers University           | Sweden      |

| Olivier Temam           | INRIA                         | France      |

| M. J. Thazhuthaveetil   | Indian Inst. of Science       | India       |

| Richard Vuduc           | Georgia Tech University       | USA         |

| WORKSHOPS/TUTORIALS CH  | IAIR                          | •           |

| Stefanos Kaxiras        | Univesirty of Patras          | Greece      |

| LOCAL ARRANGEMENTS CH   | AIR                           |             |

| Yiannakis Sazeides      | University of Cyprus          | Cyprus      |

| FINANCE CHAIR           | •                             |             |

| Wouter De Raeve         | Ghent University              | Belgium     |

| PUBLICITY CHAIR         |                               | -           |

| Hans Vandierendonck     | Ghent University              | Belgium     |

| PUBLICATIONS CHAIR      | •                             |             |

| Theo Ungerer            | University of Augsburg        | Germany     |

| SUBMISSIONS CHAIR       |                               | -           |

| Michiel Ronsse          | Ghent University              | Belgium     |

| WEB AND REGISTRATION CH | <u> </u>                      |             |

| Klaas Millet            | Ghent University              | Belgium     |

| STEERING COMMITTEE      | -                             |             |

| Anant Agarwal           | MIT                           | USA         |

| Koen De Bosschere       | Ghent University              | Belgium     |

11

| Michel Dubois     | Univ. of Southern California | USA       |

|-------------------|------------------------------|-----------|

| Rajiv Gupta       | Univ. of California          | Riverside |

| Wen-mei W. Hwu    | UIUC                         | USA       |

| Manolis Katevenis | Univ. of Crete/Forth         | Greece    |

| Per Stenström     | Chalmers University          | Sweden    |

| Theo Ungerer      | University of Augsburg       | Germany   |

| Mateo Valero      | UPC                          | Spain     |

# **Conference Program**

# Day 1: January 26, 2009

| 9:00-  | KEYNOTE I: Challenges on the Road to Exascale Computing,                                                                         |

|--------|----------------------------------------------------------------------------------------------------------------------------------|

| 10:00  | Kathryn O'Brien, IBM Research                                                                                                    |

| 10:30- | SESSION I.Dynamic Translation and Optimisation                                                                                   |

| 12:30  | CHAIR: David Padua, UIUC                                                                                                         |

|        | Steal-on-abort: Improving Transactional Memory Performance through Dynamic Transaction Reordering                                |

|        | Mohammad Ansarin, Mikel Luján, Christos Kotselidis, Kim Jarvis, Chris Kirkham, Ian Watson                                        |

|        | (University of Manchester)                                                                                                       |

|        | Predictive Runtime Code Scheduling for Heterogeneous Architectures                                                               |

|        | Víctor Jiménez (BSC), Lluís Vilanova (UPC), Isaac Gelado (UPC), Marisa Gil (UPC), Grigori<br>Fursin (INRIA), Nacho Navarro (UPC) |

|        | Collective Optimization                                                                                                          |

|        | Grigori Fursin, Olivier Temam                                                                                                    |

|        | (INRIA)                                                                                                                          |

|        | High Speed CPU Simulation using LTU Dynamic Binary Translation                                                                   |

|        | Daniel Jones, Nigel Topham                                                                                                       |

|        | (University of Edinburgh)                                                                                                        |

| 14:00- | SESSION II. Low level Scheduling                                                                                                 |

| 15:30  | CHAIR: John Cavazos, U Deleware                                                                                                  |

|        | Integrated Modulo Scheduling for Clustered VLIW Architectures                                                                    |

|        | Mattias V. Eriksson and Christoph W. Kessler                                                                                     |

|        | (Linköping university)                                                                                                           |

|        | Software Pipelining in Nested Loops With Prolog-Epilog Merging                                                                   |

|        | Mohammed Fellahi and Albert Cohen                                                                                                |

|        | (INRIA)                                                                                                                          |

|        | A Flexible Code Compression Scheme using Partitioned Look-Up Tables                                                              |

|        | Martin Thuresson, Magnus Själander, Per Stenström                                                                                |

|        | (Chalmers University of Technology)                                                                                              |

| 16:00- | SESSION III. Parallelism and Resource Control                                                                                    |

| 18:00  | CHAIR: Yiannakis Sazeides, U Cyprus                                                                                              |

|        | MLP-Aware Runahead Threads in a Simultaneous Multithreading Processor                                                            |

|        | Kenzo Van Craeynest, Stijn Eyerman, Lieven Eeckhout                                                                              |

|        | (Ghent University)                                                                                                               |

|        | IPC Control for Multiple Real-Time Threads on an In-order SMT Processor                                                          |

|        | Jörg Mische, Sascha Uhrig, Florian Kluge, Theo Ungerer                                                                           |

|        | _                                                                                                                                |

| (University of Augsburg)                                |

|---------------------------------------------------------|

| A Hardware Task Scheduler for Embedded Video Processing |

| Ghiath Al-Kadi, Andrei Sergeevich Terechko              |

| (NXP Semiconductors)                                    |

| Finding Stress Patterns in Microprocessor Workloads     |

| Frederik Vandeputte and Lieven Eeckhout                 |

| (Ghent University)                                      |

# Day 2: January 27, 2009

| 8:30-  | SESSION IV. Communication                                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10:00  | CHAIR: Andre Seznec, IRISIA/INRIA                                                                                                                                          |

|        | Deriving Efficient Data Movement from Decoupled Access/Execute Specifications                                                                                              |

|        | Lee W. Howes (Imperial College London), Anton Lokhmotov (Imperial College London),<br>Alastair F. Donaldson (Codeplay Software), Paul H.J. Kelly (Imperial College London) |

|        | MPSoC Design using Application-Specific Architecturally Visible Communication                                                                                              |

|        | Theo Kluter, Philip Brisk, Edoardo Charbon, Paolo Ienne                                                                                                                    |

|        | (EPFL)                                                                                                                                                                     |

|        | Communication Based Proactive Link Power Management                                                                                                                        |

|        | Sai Prashanth Muralidhara and Mahmut Kandemir                                                                                                                              |

|        | (Pennsylvania State University)                                                                                                                                            |

| 10:30- | SESSION V. Mapping for CMPs                                                                                                                                                |

| 12:30  | CHAIR: Per Stenstrom, Chalmers                                                                                                                                             |

|        | Mapping and synchronizing streaming applications on Cell processors                                                                                                        |

|        | Maik Nijhuis (University of Amsterdam), Herbert Bos (University of Amsterdam), Henri E. Bal (INRIA), and Cédric Augonnet (INRIA)                                           |

|        | Adapting Application Mapping to Systematic Within-die Process Variations on Chip                                                                                           |

|        | Multiprocessors  Vana Dina Mahmut Kandamin Mam Jana Impin Badma Baahayan (Bannaylyania Stata                                                                               |

|        | Yang Ding, Mahmut Kandemir, Mary Jane Irwin, Padma Raghavan (Pennsylvania State University)                                                                                |

|        | Accommodating Diversity in CMPs with Heterogeneous Frequencies                                                                                                             |

|        | Major Bhadauria (Cornell University), Vince Weaver (Cornell University), Sally A. McKee (Chalmers University of Technology)                                                |

|        | A Framework for Task Scheduling and Memory Partitioning for Multi-Processor System-on-Chip                                                                                 |

|        | Hassan Salamy and Jagannathan Ramanujam                                                                                                                                    |

|        | (Louisiana State University)                                                                                                                                               |

# Day 3: January 28, 2009

| 9:00-  | KEYNOTE II Compilers in the manycore era                                                  |

|--------|-------------------------------------------------------------------------------------------|

| 10:00  | KETNOTE II Compilers in the manycore era                                                  |

| 10.00  | Francois Bodin, CAPS enterprises                                                          |

| 10:30- | SESSION VI. Power                                                                         |

| 12:30  | CHAIR: Mary Jane Irwin, PSU                                                               |

|        | Hybrid Super/Subthreshold design of a Low Power Scalable-Throughput FFT Architecture      |

|        | Michael B. Henry, Leyla Nazhandali                                                        |

|        | (Virginia Polytechnic Institute and State University)                                     |

|        | Predictive Thermal Management for Chip Multiprocessors using Co-designed Virtual Machines |

|        | Omer Khan and Sandip Kundu                                                                |

|        | (University of Massachusetts)                                                             |

|        | HeDGE: Hybrid Dataflow Graph Execution in the Issue logic                                                                                                    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Suriya Subramanian and Kathryn S. McKinley                                                                                                                   |

|        | (University of Texas at Austin)                                                                                                                              |

|        | Compiler Controlled Speculation for Power Aware ILP Extraction in Dataflow Architectures                                                                     |

|        | Muhammad Umar Farooq, Lizy John, Margarida F. Jacome                                                                                                         |

|        | (University of Texas at Austin)                                                                                                                              |

| 14:00- | SESSION VII. Cache Issues                                                                                                                                    |

| 15:30  | CHAIR: Ben Juurlink, Delft                                                                                                                                   |

|        |                                                                                                                                                              |

|        | Revisiting Cache Block Superloading                                                                                                                          |

|        | Matthew A. Watkins (Cornell University), Sally A. McKee (Chalmers University of Technology), and Lambert Schaelicke (Intel Corporation)                      |

|        | ACM: An Efficient Approach for Managing Shared Caches in Chip Multiprocessors                                                                                |

|        | Mohammad Hammoud, Sangyeun Cho, and Rami Melhem                                                                                                              |

|        | (University of Pittsburgh)                                                                                                                                   |

|        | In Network Caching For Chip Multi Processors                                                                                                                 |

|        | Aditya Yanamandra, Mary Jane Irwin, Vijaykrishnan Narayanan, Mahumut Kandemir, Sri                                                                           |

|        | Hari Krishna Narayanan                                                                                                                                       |

|        | (Pennsylvania State University)                                                                                                                              |

| 16:00- | SESSION VIII. Parallel embedded applications                                                                                                                 |

| 17:00  | CHAIR: Joel Emer, INTEL/MIT                                                                                                                                  |

|        | Parallel LDPC Decoding on the Cell/B.E. Processor                                                                                                            |

|        | Gabriel Falcão (University of Coimbra), Leonel Sousa (Technical University of Lisbon), Vitor                                                                 |

|        | Silva (University of Coimbra), José Marinho (University of Coimbra)                                                                                          |

|        | Parallel H.264 Decoding on an Embedded Multicore Processor                                                                                                   |

|        | Arnaldo Azevedo (Delft University of Technology), Cor Meenderinck (Delft University of                                                                       |

|        | Technology), Ben Juurlink (Delft University of Technology), Andrei Terechko (NXP), Jan<br>Hoogerbrugge (NXP), Mauricio Alvarez (UPC), Alex Ramirez (UPC,BSC) |

|        | 1100geroragge (IVAI), Mauricio Alvarez (OTC), Alex Ramirez (OTC, DSC)                                                                                        |

# **Conference attendance**

The conference was attended by 198 participants, of which 17 from industry.

The attendants came from 23 different countries:

| USA             | 23 |

|-----------------|----|

| Cyprus          | 22 |

| Spain           | 21 |

| France          | 19 |

| Greece          | 14 |

| UK              | 14 |

| Germany         | 13 |

| The Netherlands | 13 |

| Belgium         | 12 |

| Italy           | 10 |

| United Kingdom  | 10 |

| Sweden          | 5  |

| Norway          | 3  |

| Portugal        | 3  |

| Austria         | 2  |

| Brazil      | 2 |

|-------------|---|

| Finland     | 2 |

| Israel      | 2 |

| Poland      | 2 |

| Russia      | 2 |

| Switzerland | 2 |

| Romania     | 1 |

| Scotland    | 1 |

While logically the number of attendants from the organising country (Cyprus) is high, we notice the high attendance from the USA. We also welcomed participants from Russia and Brazil.

#### **Student Grants**

This year we were able to give a grant to 36 students. This means that all students who applied for a grant received the registration fee grant.

#### **Workshops and Tutorials**

On January 25, the day preceding the conference, the HiPEAC clusters and task forces organised 7 workshops and 1 tutorial:

- GROW: GCC Research Opportunities Workshop

- 3rd Workshop on Interconnection Network Architectures: On-Chip, Multi-Chip

- 2nd Workshop on Programmability Issues for Multi-Core Computers (MULTIPROG-2009)

- 1st Workshop on Rapid Simulation and Performance Evaluation: Methods and Tools (RAPIDO09)

- 3rd HiPEAC Workshop on Reconfigurable Computing WRC 2009

- 1st Workshop on Design for Reliability (DFR)

- 3rd Workshop on Statistical and Machine learning approaches to Architectures and compilation (SMART'09)

- Tutorial on Architecture Design for Soft Errors, Shubu Mukherjee, Intel Corporation

175 people attended the workshops:

| GCC Research Opportunities Workshop                | 38 |

|----------------------------------------------------|----|

| Workshop on Interconnection Network Architectures: | 23 |

| On-Chip, Multi-Chip                                |    |

| Workshop on programmability Issues for Multi-core  | 38 |

| Computers                                          |    |

| Workshop on Rapid Simulation and Performance       | 24 |

| Evaluation: Methods and Tools                      |    |

| Workshop on Reconfigurable Computing               | 22 |

| Workshop on Design for Reliability                 | 25 |

| Workshop on statistical and Machine learning       | 39 |

| approaches to Architectures and compilation        |    |

| Tutorial on Architecture Design for Soft Errors    | 24 |

Relatively spoken, more people have taken the opportunity to attend one of the workshops or tutorials compared to last year.

## 2.3. Conference Ranking

There is no easy way of ranking conferences as there is for journals, which are usually associated with impact factors based on the average number of citations. A systematic investigation of citation counts for the papers published in the HiPEAC conference is underway.

#### 3. Task 3.2: Summer School

The successful international ACACES Summer School continues to be one of the most attractive events organised by HiPEAC.

The International Summer School on Advanced Computer Architecture and Compilation for Embedded Systems is open to a wide audience, while we keep a balance between country, senior-junior, gender and industry-academia.

The Summer School programme consists of a combination of courses on the different topics covered by the HiPEAC research agenda. This is guaranteed by letting the different HiPEAC clusters

suggest the best possible teachers for their own topic. This list of teachers is supplemented by topics considered to be of general interest to the whole network (e.g., dealing with crosscutting concerns like power, reliability, ...). The teaching staff consists of academics and industrial researchers, Europeans and non-Europeans alike. Former Summer School teachers normaly keep their links with the cluster that proposed them (as associate member).

Besides the courses, we organise a poster session where the PhD-students can present their own research to the other participants of the school. This is an excellent networking event for the young PhD students, which can lead to extra research ideas and contacts. During the summer school, the HiPEAC collaboration grant program is also presented to allow the students to further develop the newly made contacts.

During this poster session, we take the opportunity to present our network, and related FP6 and FP7-projects. Every project representative is available to give more information about their project.

#### 3.1. 4th International Summer School - 2008

#### The Summer School

The fourth summer school was organised at the premises of Telecom Italia Learning Services (Tils), in L'Aquila, Italy. The Summer School started on July 13 and ended on July 19.

The 2008 Summer School was supported by HiPEAC1.

#### Location

One of the strengths of the Summer School is the location. Situated in the beautiful L'Aquila, the infrastructure provided by Telecom Italia is ideal for the vision we have for the Summer School.

Next to the spacious and modern classrooms, the location provides the participants ideal opportunities to meet and network.

Separate meeting rooms are available, as well as opportunities to relax and have well appreciated social events.

Another strong point of this location is that it is at a remote location. All attendants, teachers and organisation stay in the same venue during the entire week, tremendously increasing the opportunities for interaction.

Having senior researchers and the Summer School teachers available during the whole week is a major advantage of the summer school.

#### **Summer School Program**

The Summer School program consists of 12 courses, covering the research domains our network is focused on. As mentioned earlier, the clusters suggest the teachers for the Summer School.

Apart from the courses, the Summer School also offers a keynote speech, as wel as an invited talk from industry. We adjust the program's focus based on the feedback we receive from the participants.

The 2008 Summer School courses where:

|        | Lecturer             | Course title                                                                     |

|--------|----------------------|----------------------------------------------------------------------------------|

| Slot 1 | Mary Lou Soffa       | Dynamic, Path and Model-Based Code Optimizations                                 |

|        | Chaitali Chakrabarti | Low Power System Design                                                          |

|        | Josep Torrellas      | Multiprocessor Architectures for Speculative Multithreading                      |

| Slot 2 | Nikil Dutt           | Bus-based On-Chip Communication Architectures                                    |

|        | Paolo Ienne          | Automatic Customization of Embedded Processors                                   |

|        | Dean Tullsen         | Multicore and multithreaded processor architectures                              |

| Slot 3 | Luca Benini          | Communication-dominated architectures: toward Networks on Chip                   |

|        | Babak Falsafi        | Bridging the Processor Memory Performance Gap                                    |

|        | Leendert Van Doorn   | Virtualization Technologies                                                      |

| Slot 4 | Olav Lysne           | Multiprocessor Interconnection Networks; Routing, Fault Tolerance and Scalabilty |

|        | Christos Kozyrakis   | Transactional Memory: Concepts, Implementations, and Opportunities               |

|        | Wayne Luk            | Reconfigurable Technology and Custom Computing                                   |

The keynote was given by Yale Patt (University of Texas at Austin). It was titled "The Multi-core Era: What does it mean? (and even more importantly, what does it NOT mean?)".

The invited talk was given by **Peter Magnusson** (founder of Virtutech), titled "**What your mother should have taught you about entrepreneurship**". The topic and speaker were chosen as part of the initiative to promote start-ups in the HiPEAC network.

#### Poster session

On Wednesday afternoon, the yearly poster session was held. This poster session gives PhD students the opportunity to present and discuss their work with fellow students or with the senior researchers and teachers present at the Summer School.

The increasing number of posters displayed shows the appreciation of the PhD students for this event. 80 posters were presented during the afternoon and stayed on display until the end of the Summer School.

Besides the PhD-students, we also invited related FP6/FP7-projects to present their project to the community during the poster session.

We were happy to welcome posters presented by the following projects:

- MOSART

- MERASA

- EMUCO

- ACOTES

- MILEPOST

- VELOX

#### **Attendance**

For the 2008 edition, we received 376 applicantions.

In order to ensure the opportunity to successfully network and interact we limit the number of participants to 200.

When selecting the participants, our focus is to maximise the goals of the network, and to balance the audience.

Selection criteria are:

- Gender: we stimulate female attendance to increase the gender-balance;

- Affiliation: all industry applicants are accepted in order to increase industry participation;

- Country: we try to get a maximum number of different nationalities in order to make it a truly international event;

- Experience: our goal is to have an optimal mix of senior researchers and young phd-students and postdocs.

The attendance-breakdown was as follows.

#### Industry attendance

We had 28 participants coming from 17 different companies:

| Alcatel-Lucent Bell          |

|------------------------------|

| Altera Corp.                 |

| AMD                          |

| Analog Devices Inc.          |

| ARM                          |

| Caps Entreprise              |

| CodeSourcery Inc.            |

| Gemalto                      |

| IBM Haifa Labs               |

| Indra Sistemas               |

| Intel                        |

| NXP                          |

| Simula Labs                  |

| STMicroelectronics Ltd.      |

| Thales Research & Technology |

| T-Mobile, Crnogorski Telekom |

| A.D.                         |

| Virtutech                    |

During the Summer School, there was a private industry meeting on the industrial challenges, chaired by the HiPEAC roadmap coordinator. Their input was reflected in the roadmap document that is currently being prepared.

Additionally, Intel organised a special and well-attended tutorial on their tools for the applicants.

#### Gender balance

18 out of 200 attendants are female. All female applicants were admitted and female students are certain to receive a grant.

#### Members/non-members

96 of the people who attended the summer school are members or affiliated:

- 24 members

- 61 affiliated PhD students

- 9 affiliated colleagues

- 2 staff members

Except for the teachers, half of the attendants had no direct affiliation with HiPEAC.

#### **Summer School Grants**

106 students applied for a student grant. The student grant waves the registration fee. 60 students were given a grant.

#### **Feedback**

Every year we ask all Summer School participants to give their feedback on the Summer School through an extensive survey. 142 People, or 71% filled in the survey. All scales go from 0 to 5; with 5 indicating the highest score.

#### **Organisation**

| The administration (admission, registration, payment) | 4,6 |

|-------------------------------------------------------|-----|

| The website (organisation, content)                   | 4,5 |

| The course schedule (1 week, 4 slots, 12 courses)     | 4,4 |

| The location (Telecom Italia Campus)                  | 4,5 |

| Shuttle busses (Rome-L'Aquila)                        | 4,3 |

| The course material (booklets)                        | 4,2 |

| Price/quality (990 euro, all-in, full week)           | 4,2 |

| Period (last week of July)                            | 4,2 |

The organisation was rated very highly. We continue to try to improve this aspect of the event.

### The program

| The course offering                | 4,2 |

|------------------------------------|-----|

| The keynote talk on Sunday evening | 4,5 |

| The invited talk on Monday evening | 4,1 |

| The poster session                 | 4,2 |

All aspects of the program were rated very highly. We continue to try to offer an attractive program and interesting speakers.

#### **Overall** appreciation

| Would you recommend ACACES to a colleag | ue? 4,8 |

|-----------------------------------------|---------|

| Will you come back next year?           | 4,3     |

We were happy to see that people who filled out the survey were very eager to recommend the Summer School to their colleagues. The high score for the second question shows that there is great interest to attend the Summer School more than once.

#### Course evaluation

|                      | Course | Teacher | Overall | Recommandation | Average |

|----------------------|--------|---------|---------|----------------|---------|

| Mary Lou Soffa       | 4,2    | 4,4     | 4,3     | 4,2            | 4,3     |

| Babak Falsafi        | 4,3    | 4,3     | 4,2     | 4,3            | 4,3     |

| Wayne Luk            | 3,7    | 3,9     | 3,6     | 3,6            | 3,7     |

| Chaitali Chakrabarti | 4,2    | 4,2     | 4,1     | 4,1            | 4,1     |

| Josep Torrellas      | 4,3    | 4,2     | 4,3     | 4,3            | 4,3     |

| Nikil Dutt           | 4,4    | 4,5     | 4,4     | 4,4            | 4,4     |

| Paolo Ienne          | 4,3    | 4,4     | 4,3     | 4,2            | 4,3     |

| Dean Tullsen         | 4,1    | 4,2     | 4,1     | 4,1            | 4,1     |

| Luca Benini          | 4,0    | 4,0     | 4,0     | 4,0            | 4,0     |

| Leendert Van Doorn   | 4,3    | 4,4     | 4,3     | 4,3            | 4,3     |

| Olav Lysne           | 4,1    | 4,1     | 4,2     | 4,2            | 4,2     |

| Christos Kozyrakis   | 4,6    | 4,6     | 4,5     | 4,5            | 4,5     |

All courses were evaluated high to very high. The result of the evaluation forms was sent to the respective teachers, including the comments.

#### 3.2. 5th International Summer School - 2009

#### **The Summer School**

The 2009 ACACES Summer School will be organised at the site of Telecom Italia, in L'Aquila, Italy. It will start on July 12, 2009 and end on July 18, 2009.

#### Location

The Summer School takes place at the same location as last year.

## **Summer School Program**

One of the feedback points we received from the participants last year was the lesser presence of embedded-oriented courses.

When constructing this year's programme, we took this feedback into consideration:

|        | Lecturer           | Course title                                                                               |

|--------|--------------------|--------------------------------------------------------------------------------------------|

| Slot 1 | David Albonesi     | Power- and Reliability-Aware Microarchitecture                                             |

|        | Wailid Najjar      | Opportunities and Challenges of Reconfigurable Computing                                   |

|        | Peter Puschner     | WCET Analysis: Problems, Methods, and Time-Predictable Architectures                       |

| Slot 2 | Jaejin Lee         | Compilers and Runtimes Support for Explicitly Managed Memory Hierarchies                   |

|        | Radu Marculescu    | Networks-on-Chip: Why What, and How?                                                       |

|        | Paul McKenney      | Performance, Scalability, and Real-Time Response From the Linux Kernel                     |

| Slot 3 | David Wood         | Transactional Memory                                                                       |

|        | Grant Martin       | Practical System-Level Design Methodologies for Processor-Centric SoC and Embedded Systems |

|        | Kim Hazelwood      | Process Virtualization and Symbiotic Program Optimization                                  |

| Slot 4 | Bruce Jacob        | Embedded Systems, Memory Systems, and Embedded Memory Systems                              |

|        | J. (Ram) Ramanujam | Optimizations for multicore and GPGPU architectures                                        |

|        | Lieven Eeckhout    | Performance Evaluation and Benchmarking                                                    |

The keynote will be given by Steven Furber, University of Manchester.

This year we will again organise a poster session.

# 4. Task 3.3: HiPEAC Journal

The HiPEAC Journal was first published in 2006. Its fourth volume is currently being prepared.

The HiPEAC journal differentiates itself from other publications in that it has a three-month reviewing cycle. Every accepted paper is also immediately published on the HiPEAC website.

The third volume of the journal received 22 submission, of which 14 were accepted for publication.

#### **Accepted papers**

Volume 3 accepted the following papers:

| Dynamic Cache Partitioning Based on the MLP      | Miquel Moreto, Francisco J Cazorla, Alex          |

|--------------------------------------------------|---------------------------------------------------|

| of Cache Misses                                  | Ramirez, Mateo Valero (UPC/BSC)                   |

| Cache Sensitive Code Arrangement for Virtual     | Chun-Chieh Lin, Chuen-Liang Chen (                |

| Machine                                          | National Taiwan University)                       |

| Data Layout for Cache Performance on a           | Subhradyuti Sarkar, Dean M. Tullsen (University   |

| Multithreaded Architecture                       | Of California)                                    |

| Improving Branch Prediction by considering       | Yiannakis Sazeides, Andreas Moustakas, Kypros     |

| Affectors and Affectees Correlations             | Constantinidis, Marios Kleanthous (University of  |

|                                                  | Cyprus)                                           |

| Exploring the Architecture of a Stream Register- | Matthias Blumrich, Valentina Salapura and Alan    |

| Based Snoop Filter                               | Gara (IBM Thomas J. Watson Research Center)       |

| GROB: Implementing a Large Instrucion            | F. Latorre, G. Magklis, J. Gonzalez, P. Chaparro, |

| Window though Compression                        | A. Gonzalez (Intel Barcelona)                     |

| Power-Aware Dynamic Cache Partitionning for      | Isao Kotera, Kenta Abe, Ryusuke Egawa,            |

| CMPs                                             | Hiroyuki Takizawa, and Hiroaki Kobayashi          |

|                                                  | (Tohoku University, Japan)                        |

| A Multithreaded Multicore System for             | Jan Hoogerbrugge and Andrei Terechko (NXP         |

| Embedded Media Processing                        | Semiconductors)                                   |

| Parallelization Schemes for Memory               | T. Saidani, L. Lacassagne, J. Falcou, C. Tadonki, |

| Optimization on the Cell Processor : A Case      | Samir Bouaziz (Universite de Paris Sud)           |

| Study on the Harris Corner Detector              |                                                   |

| Constructing Application-specific Memory         | H. Devos, J. Van Campenhout, I. Verbauwhede,      |

| Hierarchies on FPGAs                             | D. Stroobandt (Ghent University)                  |

| autopin – Automated Optimization of Thread-to-   | Tobias Klug, Michael Ott, Josef Weidendorfer,     |

| Core Pinning on Multicore Systems                | and Carsten Trinitis (Technische Universitat      |

|                                                  | Munchen)                                          |

| Robust Adaptation to Available Parallelism in    | Mohammad Ansari, Mikel Luján, Christos            |

| Transactional Memory Applications                | Kotselidis, Kim Jarvis, Chris Kirkham, Ian        |

|                                                  | Watson (University of Manchester)                 |

| Efficient Partial Roll-backing Mechanism for     | M. M. Waliullah (Chalmers)                        |

| Transactional Memory Systems                     |                                                   |

| Software-Level Instruction-Cache Leakage         | Maziar Goudarzi, Tohru Ishihara, Hamid Noori      |

| Reduction using Value-Dependence of SRAM         | (Kyushu University, Fukuoka, Japan)               |

| Leakage in Nanometer Technologies                |                                                   |

# 5. Task 3.4: HiPEAC Roadmap

The first HiPEAC roadmap was published in 2007. The steering committee has taken the opportunity of HiPEAC2's launch to start the discussion and brainstorming on creating a new up-to-date roadmap.

The first steps to create the new roadmap, which is currently approaching its first draft, were taken at the cluster level. Every cluster was asked to present their vision on the future of the their research domain.

Because we consider industry input for the roadmap vital to the relevance of the document, a brainstorming session was organised at the Summer School. This event gathered the input of 28 company people, giving the view of 17 companies.

This large amount of data was then further processed by a roadmap committee, including industry.

The result of this convergence was presented at the pre-review in Paphos, and to the community at the general assembly meeting. The feedback was used to create a second draft which will be presented at the review meeting of the first year of HiPEAC.

### 6. Task 3.5: HiPEAC Newsletter

The newsletter workgroup is currently preparing the 18th issue. The issues are printed quarterly and mailed around the world.

The last newsletter issue had a circulation of 725 copies.

One new feature of the newsletter is the inclusion of guest columns, where respected members or member institutions get the opportunity to present their work and the relevance of HiPEAC for their institution.

The newsletter also serves as a dissemination tool to present the HiPEAC start-ups.

The volume of the newsletter has grown from an average of 12 pages to 16-20 pages.

We automatically include all new members.

#### 6.1. Period 1 issues

During the reporting period, 4 issues of the HiPEAC newsletter were printed:

#### Issue 14: April 2008 (12 pages)

- Message from the HiPEAC coordinators

- In the Spotlight

- Second Edition "Antiguos Alumnos UPV"

- Message from the project officer

- Hipeac Activity

- HiPEAC Computing Systems Week

- 5th HiPEAC Industrial Workshop

- Guest Column

- o Grant Martin, Chief Scientist, Tensilica, Inc.

- ALaRI University of Lugano

- HiPEAC Start-ups

- Promotion of HiPEAC start-ups

- PHD News

- Upcoming Events

## Issue 15: July 2008 (16 pages)

- Message from the HiPEAC coordinators

- Message from the project officer

- Community News

- In the Spotlight

- o EC FP7 STREP Project VELOX

- BSC and Microsoft Create Joint Research Centre in Barcelona for Parallel Computing

- Guest Column

- SHAPES and its DIOPSIS Tile

- o Tsuyoshi Isshiki, Tokyo Institute of Technology

- HiPEAC Activity

- HiPEAC Research Collaborations

- HiPEAC Start-ups

- PHD News

- HiPEAC Students

- Upcoming Events

#### Issue 16: October 2008 (20 pages)

- Message from the HiPEAC coordinator Community News:

- o Multicore days in Stockholm, Sweden

- Awards and new books

- Message from the project officer

- HiPEAC Activity:

- o HiPEAC 2009 Conference

- HiPEAC Fall Computing Systems Week

- o HiPEAC 6th Industrial Workshop

- In the Spotlight:

- Good bye and Thanks Sylvie! Hello and Welcome Klaas!

- o EC STREP FP7 Apple-Core Project

- o EC STREP FP7 eMuCo Project

- Guest columns:

- o Norbert When, University of Kaiserlauten

- o Gerd Ascheid, RWTH Aachen University

- HiPEAC Start-ups

#### **Issue 17: Januari 2009 (16 pages)**

- Message from the HiPEAC coordinator

- Message from the project officer

- HiPEAC Activity:

- HiPEAC Journal papers

- o ACACES 2009

- First Workshop on Network on Chip Architectures (NoCArc2008)

- HiPEAC Recorded Seminars

- Promotion of HiPEAC Start-ups

- In the Spotlight:

- o ArchExplorer.org

- o EC FP6 STREP MILEPOST Project

- EC FP7 STREP MULTICUBE Project

- Community News

- o Daniel Litaize (1945-2008)

- o New member: Javier Castillo

- o NVIDIA CUDA Challenge Award

- o Mateo Valero, among the 25 most influential scientists in Europe

- o New Book

- Success for TM in GCC Project

- HiPEAC Start-ups

- HiPEAC Students and Trip Reports

- Phd News

- Upcoming events

# 7. Task 3.6: HiPEAC Technical Reports

HiPEAC technical reports are web-based time stamped internal reports. The goal of the technical reports is to publish the ideas of European researchers as soon as they mature, and make sure that ideas are credited to the original contributor.

The process of publishing an idea in the HiPEAC technical reports is lightweight. It suffices to submit an internal report to the HiPEAC website where the editor of the HiPEAC technical reports will quickly evaluate whether the idea is good enough to be put on the HiPEAC website. If so, the report is immediately published on the website, with the time stamp of the moment the document was submitted to the website.

#### 7.1. Publication database

The first step related to the technical reports was to create a publication database.

This database is a list of all publications by a HiPEAC member or affiliate. While the database is mostly automatically generated, users have the possibility to contribute to the database, by insterting publications manually or by requesting changes to existing publications.

These publications are unfortunately not all related to direct HiPEAC work. It is therefore the task of the cluster coordinators to select those publications that present an accurate overview of cluster and task force activities. An easy-to-use interface was created to facilitate this process.

Our database currently holds 4870 publications:

| 2005 | 1128 |

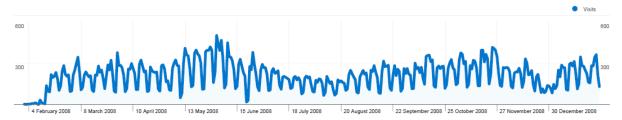

|------|------|