FP7-ICT-2013-11-619871

## **BASTION**

Board and SoC Test Instrumentation for Ageing and No Failure Found

Instrument: Collaborative Project

Thematic Priority: Information and Communication Technologies

# Report on the NFF and ageing fault study (Deliverable D1.1)

Due date of intermediate deliverable: September 30, 2014 (M9)

Due date of final deliverable: June 30, 2015 (M18)

Actual submission date: June 30, 2015

Start date of project: January 1, 2014 Duration: Three years

Organization name of lead contractor for this deliverable: University of Twente

Revision v2.4 30<sup>th</sup> June 2015

| Project co-funded by the European Commission within the Seventh Framework Programme (2014-2016) |                                                                                       |   |  |  |  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|--|--|--|

|                                                                                                 | Dissemination Level                                                                   |   |  |  |  |

| PU                                                                                              | Public                                                                                | × |  |  |  |

| PP                                                                                              | Restricted to other program participants (including the Commission Services)          |   |  |  |  |

| RE                                                                                              | Restricted to a group specified by the consortium (including the Commission Services) |   |  |  |  |

| CO                                                                                              | Confidential, only for members of the consortium (including the Commission Services)  |   |  |  |  |

#### **Notices**

For more information, please contact Dr.ir. H.G. Kerkhoff, e-mail: <a href="mailto:h.g.kerkhoff@utwente.nl">h.g.kerkhoff@utwente.nl</a>

This document is intended to fulfill the contractual obligations of the BASTION project concerning deliverable D1.1 described in contract 619871.

© Copyright BASTION 2015. All rights reserved.

# **Table of Revisions**

| Version | Date                              | Description and reason                                                                                                                | Author                                    | Affected sections                             |

|---------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------|

| 0.1     | June 3, 2014                      | Initial document created                                                                                                              | H.G. Kerkhoff<br>UT                       | Contents                                      |

| 0.2     | June 16 <sup>th</sup> , 2014      | NFF part created                                                                                                                      | H. Ebrahimi<br>UT                         | First part                                    |

| 0.3     | June 19 <sup>th</sup> , 2014      | Aging part created                                                                                                                    | H. Ebrahimi &<br>H.G. Kerkhoff<br>UT      | Second part                                   |

| 0.4     | June 20 <sup>th</sup> , 2014      | Board level NFF and BASTION survey                                                                                                    | Christophe Lotz<br>ASTER                  | Third and fourth parts                        |

| 0.5     | July 12 <sup>th</sup> , 2014      | State-of-the-art on<br>Fault Models                                                                                                   | Erik Larsson,<br>Dimitar Nikolov<br>ULUND | Third part                                    |

| 0.5     | September 9 <sup>th</sup> , 2014  | Fusion of all contributions                                                                                                           | Christophe Lotz<br>ASTER                  | All sections                                  |

| 0.6     | September 11 <sup>th</sup> , 2014 | Integration                                                                                                                           | H. Ebrahimi &<br>H.G. Kerkhoff<br>UT      | All                                           |

| 0.7     | September 24 <sup>th</sup> , 2014 | Major updates on the topics of board-level NFF and the timing fault hypothesis                                                        | Artur Jutman, TL                          | Introduction;<br>Section 3;<br>Section 4.     |

| 0.8     | September 25 <sup>th</sup> , 2014 | Hierarchical NBTI analysis                                                                                                            | Jaan Raik<br>TUT                          | Sections 1, 2                                 |

| 0.9     | September 30 <sup>th</sup> , 2014 | Added ASTER results & Integration                                                                                                     | H. Ebrahimi &<br>H.G. Kerkhoff,<br>UT     | All                                           |

| 1.0     | October 3 <sup>rd</sup> , 2014    | Final check                                                                                                                           | H.G. Kerkhoff,<br>UT                      | All                                           |

| 1.1     | October 7 <sup>th</sup> , 2014    | Minor corrections                                                                                                                     | Artur Jutman, TL                          | Introduction;<br>Section 4;<br>Conclusions    |

| 2.1     | June 9 <sup>th</sup> , 2015       | Updated aging simulation, minor corrections                                                                                           | Jaan Raik, TUT                            | Section 2, all sections                       |

| 2.2     | June 19 <sup>th</sup> , 2015      | Updates on Aging & NFF parts                                                                                                          | H. Ebrahimi,<br>UT                        | Section 2, 3                                  |

| 2.3     | June 26 <sup>th</sup> , 2015      | Update on board NFF                                                                                                                   | Christophe Lotz<br>ASTER                  | Section 4                                     |

| 2.4     | June 30 <sup>th</sup> , 2015      | Update of the Executive Summary, Introduction, Conclusions. List of Abbreviations, review of the final document and minor corrections | Artur Jutman, TL                          | Mainly the introductory parts and Conclusions |

# **Authors, Beneficiaries**

Christophe Lotz, ASTER

Erik Larsson, Lund University

Dimitar Nikolov, Lund University

Jaan Raik, Tallina Tehnikaulikool

Hans G. Kerkhoff, University of Twente

Hassan Ebrahimi, University of Twente

Artur Jutman, Testonica Lab

## **Executive Summary**

The document presents BASTION research results in the area of aging mechanisms at the IC level (task T1.2), and No Fault Found (NFF) at both IC and board level (task T1.1) and concludes activities in related tasks. First, we describe achieved results in aging fault study including the link between low-level measurements and data usage at higher abstraction levels. The second part of the document concentrates on the NFF phenomenon both at IC and board level. Partners' contributions with regard to the experimental analysis and industrial study of NFF faults as well as on overview of prior work are presented.

Intermittent faults have been identified to be an important contributor to IC-level NFFs. Hence a novel simulation model has been developed for this type of NFF with the target of mitigating the issue. In Section 4, a study that demonstrates a gap in board-level state-of-the-art fault coverage metrics, especially in the domain of timing faults, is presented. This hypothesis has been confirmed among other results by an extensive industrial study based on both a questionnaire and actual traceability data extraction and analysis (by QuadDPMO).

The mentioned questionnaire developed by ASTER and BASTION partners is included in the Appendix. Finally, conclusions regarding our research on aging faults and NFFs are also provided.

# **List of Abbreviations**

| ADC              | - Analog-to-Digital Converter                        |  |  |  |

|------------------|------------------------------------------------------|--|--|--|

| AOI              | - Automated Optical Inspection                       |  |  |  |

| AXI              | - Automated X-ray Inspection                         |  |  |  |

| BERT             | - Bit Error Rate Testing                             |  |  |  |

| BST              | - Boundary-Scan Test                                 |  |  |  |

| BTI              | - Bias Temperature Instability                       |  |  |  |

| CHE              | - Channel Hot Electron                               |  |  |  |

| CISC             | - Complex Instruction Set Computing                  |  |  |  |

| CM               | - Contract manufacturer                              |  |  |  |

| CMOS             | - Complementary Metal-Oxide Semiconductor            |  |  |  |

| CRC              | - Cyclic Redundancy Check                            |  |  |  |

| DAC              | - Digital-to-Analog Converter                        |  |  |  |

| DAHC             | - Drain Avalanche Hot Carrier                        |  |  |  |

| dB               | - Decibel                                            |  |  |  |

| DPM              | - Defects Per Million                                |  |  |  |

| DPMO             | - Defects Per Million Opportunities                  |  |  |  |

| EI               | - Embedded Instrument                                |  |  |  |

| EM               | - Electro Migration                                  |  |  |  |

| EMS              | - Enhanced Manufacturing Services                    |  |  |  |

| ESD              | - Electro Static Discharge                           |  |  |  |

| FET              | - Field Effect Transistor                            |  |  |  |

| FinFET           | - Fin-based, multigate FET                           |  |  |  |

| FMEA             | - Failure Mode and Effect Analysis                   |  |  |  |

| FPGA             | - Field Programmable Gate Array                      |  |  |  |

| FP7              | - European Union's 7 <sup>th</sup> Framework Program |  |  |  |

| FPT              | - Flying Probe Test                                  |  |  |  |

| FPY              | - First Pass Yield                                   |  |  |  |

| FT               | - Functional Test                                    |  |  |  |

| HALT/HASS        | - Highly Accelerated Life Test / Stress Screen       |  |  |  |

| HCI              | - Hot Carrier Injection                              |  |  |  |

| IC               | - Integrated Circuit                                 |  |  |  |

| ICT              | - In-Circuit Test                                    |  |  |  |

| I <sub>ddt</sub> | - Transient power-current                            |  |  |  |

| $I_{ddq}$        | - Quiescent power current                            |  |  |  |

| INEMI            | - International Electronic Manufacturing Initiative  |  |  |  |

| IPC                                                                                                | - Institute for Printed Circuits                                 |  |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| IRF                                                                                                | - Intermittent fault                                             |  |

| IST                                                                                                | - Information Society Technologies                               |  |

| IVF                                                                                                | - Intermittent Vulnerability Factor                              |  |

| JEDEC                                                                                              | - Joint Electron Device Engineering Council                      |  |

| JTAG                                                                                               | - Joint Test Action Group                                        |  |

| MOSFET                                                                                             | - Metal Oxide Semiconductor Field-Effect Transistor              |  |

| MPS                                                                                                | - (Coverage metrics based on) Material, Placement & Solder       |  |

| MTTF                                                                                               | - Mean Time To Failure                                           |  |

| NBTI                                                                                               | - Negative Bias Temperature Instability                          |  |

| NDF                                                                                                | - No Defect Found                                                |  |

| NFF                                                                                                | - No Fault Found, No Failure Found                               |  |

| NMOS                                                                                               | - n-type Metal Oxide Semiconductor                               |  |

| NMOSFET                                                                                            | - n-type MOSFET                                                  |  |

| NTF                                                                                                | - No Trouble Found                                               |  |

| OBD                                                                                                | - Oxide Breakdown                                                |  |

| PBTI                                                                                               | - Positive Bias Temperature Instability                          |  |

| PCOLA/SOQ - (Coverage metrics based on) Presence, Correct, Orienta Alignment/Short, Open & Quality |                                                                  |  |

| PCBA                                                                                               | - Printed Circuit Board Assembly                                 |  |

| PMOS                                                                                               | - p-type Metal Oxide Semiconductor                               |  |

| PMOSFET                                                                                            | - n-type MOSFET                                                  |  |

| PPM                                                                                                | - Part Per Million                                               |  |

| PPVS                                                                                               | - (Coverage metrics based on) Presence, Polarity, Value & Solder |  |

| PVT                                                                                                | - Process, Voltage, Temperature                                  |  |

| RISC                                                                                               | - Reduced Instruction Set Computing                              |  |

| RO                                                                                                 | - Ring Oscillator                                                |  |

| SBD                                                                                                | - Soft Breakdown                                                 |  |

| SoC                                                                                                | - System on Chip                                                 |  |

| SGHE                                                                                               | - Secondary Generated Hot Electron                               |  |

| TDDB                                                                                               | - Time Dependent Dielectric Breakdown                            |  |

| TSSOP                                                                                              | - Thin Shrink Small Outline Package                              |  |

| TSV                                                                                                | - Through Silicon Via                                            |  |

| URL                                                                                                | - Uniform Resource Locator                                       |  |

| UUT                                                                                                | - Unit Under Test                                                |  |

| VFIT                                                                                               | - VHDL-Based Fault Injection Tool                                |  |

| VHDL                                                                                               | - VHSIC Hardware Description Language                            |  |

| VHSIC                                                                                              | - Very High Speed Integrated Circuit                             |  |

# **Table of Contents**

| T | able o                                       | f Rev                          | visions                                            | iii |

|---|----------------------------------------------|--------------------------------|----------------------------------------------------|-----|

| A | uthors                                       | , Be                           | neficiaries                                        | iv  |

| L | ist of A                                     | Abbr                           | eviations                                          | vi  |

| T | able o                                       | f Co                           | ntents                                             | iv  |

| 1 | Int                                          | rodu                           | ction                                              | 1   |

|   | 1.1                                          | The                            | e structure of the report                          | 2   |

| 2 | Ag                                           | ing 1                          | faults                                             | 3   |

|   | 2.1                                          | 2.1 Introduction               |                                                    |     |

|   | 2.2                                          | Cla                            | sses of aging faults                               | 3   |

|   | 2.2                                          | .1                             | Electro-migration                                  | 3   |

|   | 2.2                                          | 2.2                            | NBTI-based aging faults                            | 4   |

|   | 2.2                                          | 2.3                            | HCI-based aging faults                             | 4   |

|   | 2.2                                          | .4                             | Time-Dependent Dielectric Breakdown (TDDB) aging   | 5   |

|   | 2.3                                          | Sta                            | te-of-the-art in aging faults                      | 5   |

|   | 2.4                                          | BA                             | STION contributions to aging fault study           | 6   |

|   | 2.4.1 Aging Measurement Embedded Instruments |                                | 6                                                  |     |

|   | 2.4.2                                        |                                | Using On-chip health monitors in SoCs              | 8   |

|   | 2.4                                          | 3                              | Hierarchical identification of NBTI-critical paths | 10  |

|   | 2.4                                          | .4                             | NBTI-critical path delay calculation               | 13  |

|   | 2.5                                          | Co                             | nclusions on aging faults                          | 14  |

| 3 | NF                                           | F fa                           | ults at the IC level                               | 15  |

|   | 3.1                                          | IC-                            | level vs. board-level NFFs                         | 15  |

|   | 3.2                                          | Int                            | Introduction to IC-level NFF                       |     |

|   | 3.3                                          | Classes of IC-level NFF faults |                                                    | 16  |

|   | 3.3                                          | .1                             | Intermittent resistive faults                      | 16  |

|   | 3.3                                          | .2                             | Intermittent stuck-at faults                       | 17  |

|   | 3.3                                          | .3                             | Intermittent short faults                          | 17  |

|   | 3.3                                          | .4                             | Intermittent open faults                           | 17  |

|   | 3.3                                          |                                | Intermittent timing faults                         |     |

|   | 3.4 State-of-the-art in IC-level N           |                                | te-of-the-art in IC-level NFF faults               | 18  |

|   | 3.5                                          | BA                             | STION contributions to NFF fault study             | 18  |

|   | 3.5                                          | 5.1                            | Intermittent fault effects on analogue CMOS        | 20  |

|   | 3.5                                          | 5.2                            | Intermittent fault effects on digital CMOS         | 21  |

|   | 3.6                                          |                                | nclusions on NFF (intermittent resistive) faults   |     |

| 4 | NF                                           | F fa                           | ults at the <i>board</i> level                     | 25  |

|   | <i>1</i> 1                                   | Int                            | roduction                                          | 25  |

| 4.2 St   | ate of the art                                         | 26 |

|----------|--------------------------------------------------------|----|

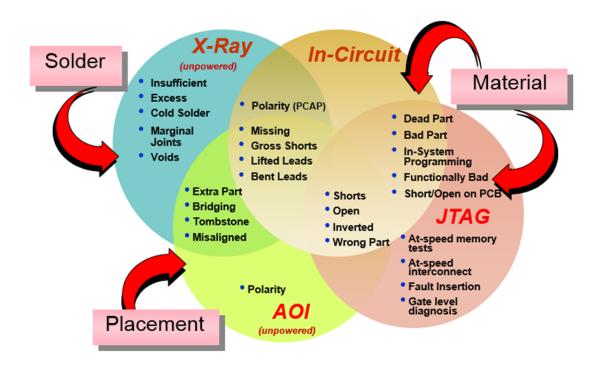

| 4.2.1    | Defects, fault model and test coverage                 | 26 |

| 4.2.2    | Yield estimation: combined defect and test coverage    | 27 |

| 4.3 A    | nalysis of gaps in test coverage                       | 28 |

| 4.3.1    | Escape rate                                            | 29 |

| 4.3.2    | New classes of board-level faults                      | 29 |

| 4.3.3    | NFF faults due to Board-level test coverage weaknesses | 32 |

| 4.4 B.   | ASTION survey                                          | 37 |

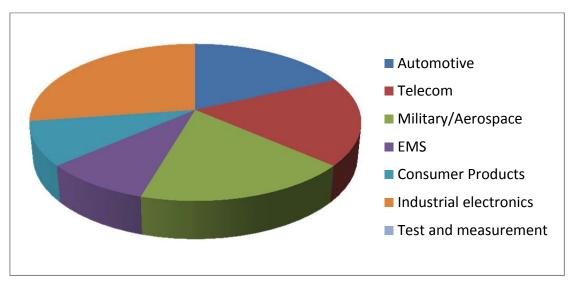

| 4.4.1    | Industrial partners                                    | 37 |

| 4.4.2    | What is NFF?                                           | 38 |

| 4.4.3    | Is NFF important?                                      | 39 |

| 4.4.4    | What is the reason of NFF?                             | 39 |

| 4.4.5    | Test Line                                              | 41 |

| 4.4.6    | The faults you know                                    | 42 |

| 4.5 To   | ools for DPMO analysis and root-cause analysis         | 42 |

| 4.5.1    | Data collection                                        | 42 |

| 4.5.2    | Traceability & repair data                             | 43 |

| 4.5.3    | QuadDPMO: True Defect Opportunities                    | 44 |

| 4.5.4    | DPMO extraction                                        | 45 |

| 4.5.5    | Data preparation                                       | 45 |

| 4.5.6    | Intermittent faults                                    | 46 |

| 4.5.7    | Insufficient coverage                                  | 46 |

| 4.5.8    | Missing test method: Ageing                            | 49 |

| 4.5.9    | Lack of communication between design and test          | 50 |

| 4.6 Co   | onclusions on board-level NFF faults                   | 52 |

| 5 Concl  | usions                                                 | 53 |

| 6 Refere | ences                                                  | 55 |

| ADDENIDI | V I                                                    | 1  |

#### 1 Introduction

The document starts with an overview of the literature at large; also briefly explaining different classes and mechanisms of aging and NFF faults, and then the state-of-the-art in the respective fields is treated. Subsequently, the BASTION investigation results by cooperation of partners about aging faults and NFF are provided.

In terms of the aging study, we are working in two directions. First, designing health monitors to observe the degradation of digital circuits. The second direction is modelling aging faults accurately, in order to enable analysis of aging effects in large digital circuits.

Health monitoring can provide advance warning of malfunction, and help to prevent catastrophic failures. Using on-chip health monitors, one can enhance long-term dependability and extend useful lifetime of MP-SoCs. The proposed approach addresses the design of aging monitors, and enables a new generation of very high dependability many-processors SoCs in safety-critical applications. A process monitor, like an NBTI monitor has been shown to have correlation with propagation delay in an aged processor. Moreover, in order to detect the performance degradation of digital CMOS circuits due to aging effects, an embedded instrument has been designed. This instrument can extract the changes in threshold-voltages which are induced by aging effects. It is planned to also look at other monitors, like HCI, and  $I_{\rm ddt}$  and  $I_{\rm ddq}$  and also ring-oscillator (RO) monitors for being able to observe the degradation of digital CMOS circuits. The research on monitors is an important contribution to be used as a basis in WP3 when developing in-field on-line error detection and monitoring solutions.

To enable analysis of aging effects in large circuits, we have introduced a method of hierarchical modeling of dynamic NBTI aging. Preliminary experimental results show high scalability as well as good match with SPICE simulation results. Work on the evaluation of the method continues along with different kind of aging monitors.

With respect to the *NFF study*, we've been working on the hypothesis that NFF faults can be categorized in the following three categories:

- 1. NFF due to intermittent faults, both at the board level and inside ICs;

- 2. NFF due to insufficient traceability data analysis for process tuning;

- 3. NFF at the board level due to insufficient/unknown test coverage, especially in the domain of speed-related or timing faults (AC domain).

The three categories correspond to different research directions.

The first direction (intermittent faults) led by UT has been also supported by several academic and industrial studies over the last decade. Intermittent faults are extremely difficult to test due to lack of determinism in creating fault activation/manifestation conditions. This fact creates a fruitful soil for test escapes and subsequent NTF problem. In BASTION, a novel simulation model has been developed for this type of NFF with the target of mitigating the issue.

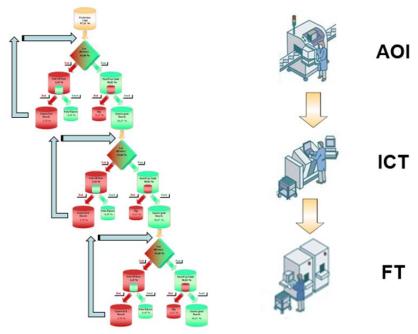

The second direction (data traceability) was identified by ASTER based on their long-term experience working with large multinational corporations having complex electronics manufacturing processes. DPMO is the key parameter that needs to be carefully calculated in addition to knowing test coverage under different coverage categories. Good control over combined test coverage and DPMO promises reduction

of the amount of NFF cases. The second research direction yielded rich results as an outcome of the industrial study organized by ASTER. The study was twofold, 1) based on a survey; 2) by automatic extraction and analysis of actual industrial traceability data using a new QuadDPMO tool. The experimental software tool QuadDPMO has been specifically developed by ASTER. The tool facilitates data stratification, classification and unification in a single database in order to simplify analysis of NFF cases and root-cause analysis. The data collection methods are implemented according to existing IPC standards.

The third direction (insufficient/unknown test coverage) initiated by TL and ASTER is based on the analysis of the cumulative fault coverage achieved by the combination of state-of-the-art board-level test techniques. The weakest point is the coverage of timing faults or performance-related issues, e.g. delay faults, crosstalk, signal integrity, interconnect quality, communication link integrity, etc. State-of-the-art test methods for these fault classes (like BERT or at-speed test) do not provide proof of good or sufficient fault coverage. We expect to improve test coverage metrics based on this research, as well as provide techniques to achieve higher fault coverage (to be reported in D1.3 by M30).

The survey questionnaire used for industrial study is attached as Appendix. It has been developed by ASTER and partners based on initial industrial experience with the goal to receive broader industrial opinion on our focus points.

## 1.1 The structure of the report

The report starts with the analysis of aging and NFF faults at the *IC-level*. After a study on the state-of-the-art, the BASTION investigation results by cooperation of partners about aging faults are presented.

Then, the NFF phenomenon is studied at the IC-level as well as board-level and BASTION partners' contributions with regard to NFF faults are presented.

In its second part, a study of NFF faults at *board-level* is presented including the analysis of weaknesses of state-of-the-art test coverage metrics and best industrial practices. A board-level test coverage gap with respect of timing faults is demonstrated. Afterwards, we describe the results of performed industrial study based on a survey and automated traceability data analysis by QuadDPMO software,

A reference list is provided with papers on aging and NFF. Subsequently, the report is summarized with main initial conclusions.

The Appendix shows the set-up of a BASTION questionnaire which has been distributed to main industrial contacts to enable a better understanding on the industrial view on aging and NFF.

## 2 Aging faults

In this section, the most important classes of aging faults, that include electromigration (EM), hot carrier injection (HCI), time dependent dielectric breakdown (TDDB), and bias temperature instability (BTI), as well as state-of-the-art publications about aging faults are introduced. Then, the first investigations in aging faults from partners are presented. It is concluded with some initial conclusions.

#### 2.1 Introduction

As a result of non-constant aggressive scaling of technology in terms of device dimensions, increasing electric fields and the use of new materials to meet the demands set by these technologies, the reliance on electronic systems fabricated in these technology nodes has become a very important aspect. There are various degradation mechanisms that can worsen the performance of devices, circuits and their associated electronic systems as a result of this aggressive technology scaling. Although the research is mostly focused on CMOS, also FinFETS suffer from aging effects, like NBTI.

## 2.2 Classes of aging faults

The aging faults can be classified according to the main cause into the following categories: electro-migration, hot carrier injection, time dependent dielectric breakdown, and bias temperature instability. There are more aging phenomena, but the ones listed are the most prominent ones in CMOS related technologies.

## 2.2.1 Electro-migration

Electro-migration (EM) is the dominant failure mode of interconnects that results from aggressive interconnect scaling. As the technology is scaling, the device density is increasing and as a result interconnects that carry signals are consequently reduced in size, specifically, in height and cross section.

This leads to extremely high current densities, in the order of at least 10<sup>6</sup> A/cm<sup>2</sup> and associated thermal effects, which can cause reliability problems [1]. At these current densities, momentum transfer between electrons and metal atoms becomes important. The transfer, which is called the *electron-wind force*, results in a mass transport along the direction of electron movement.

Once the metal atoms are activated by the electron wind, they are subject to the electric fields that drive the current. Since the metal atoms are positively ionized, the electric field moves them against the electron wind once they have been activated. The interplay of these two phenomena determines the direction of net mass transfer. This mass transfer manifests itself in the movement of vacancies and interstitials. The vacancies coalesce into voids or micro-cracks, and interstitials become hillocks. The voids, in turn, decrease the cross-sectional area of the circuit metallization and increase the local resistance and current density at that point in the metallization. Both the increase in local current density and temperature, increase EM effects. This

positive feedback cycle can eventually lead to thermal runaway and catastrophic failure which will eventually degrade the system dependability.

#### 2.2.2 NBTI-based aging faults

The bias temperature instability (BTI) is a degradation mechanism that occurs in MOS devices as a result of interface traps between the gate oxide and silicon substrate at elevated temperatures (30 to  $200^{\circ}$ C) [2] and hence degrade the dependability of associated electronic devices. This degradation mechanism results in device threshold voltage (V<sub>th</sub>) shift and loss of drive current (I<sub>on</sub>). The BTI effect is more severe for PMOSFETs than NMOSFETs due to the presence of holes in the PMOS inversion layer that are known to interact with the oxide states.

The highest impact of BTI in PMOSFETs is observed when stressed with high negative gate voltage at elevated temperatures [3]. It is referred to as *negative* BTI (NBTI) due to the negative gate-to-source voltage. In PMOSFETs, the channel holes interact with the passivated hydrogen bonds in the dielectric resulting into generation of traps and interface states. This results into an increase in absolute threshold voltage (V<sub>th</sub>) value and the effect increases at high temperatures. The introduction of new dielectric materials like high-k has enabled the BTI effect in NMOSFETs and is referred to as *positive bias temperature instability* (PBTI) due to the positive gate-to-source voltage.

It has been noticed that BTI degradation starts relaxing very quickly after the removal of the stress. This recovery process is caused by de-trapping of charges during subsequent removal of stress signal after a stress phase [4]. The stress signal causing BTI degradation can be of two types; the static stress (DC Stress) and the dynamic stress (AC Stress). The AC stress is known to be beneficial for lifetime enhancement because it can introduce the recovery process mentioned above [5]. Recovery after NBTI or PBTI stress in MOSFETs and its dependence on gate voltage, temperature and frequency of stress signal has been a hot topic of research in the past decade [6].

Currently, BTI is one of the most serious and important reliability concerns for both digital and analog circuits. At advanced technology nodes this effect is enhanced due to reduced voltage headroom, high oxide electric fields resulting from non-constant field scaling, high temperatures due to higher power dissipation and introduction of new dielectric material.

## 2.2.3 HCI-based aging faults

The hot carrier injection (HCI) degradation mechanism has been an important failure mechanism for the last three decades and still remains important in new technologies. According to Takeda [7], there are three main types of hot carrier injection modes:

- o Channel Hot Electron (CHE) injection.

- o Drain Avalanche Hot Carrier (DAHC) injection.

- o Secondary Generated Hot Electron (SGHE) injection.

CHE injection is due to the escape of "lucky" electrons from the channel, causing a significant degradation of the oxide and the Si-SiO<sub>2</sub> interface, especially at low temperatures [8].

On the other hand, DAHC injection results in both electron and hole gate currents due to impact ionization, giving rise to the most severe degradation at room temperature.

SGHE injection is a result of minority carriers from secondary impact ionization or, more likely, bremsstrahlung radiation, and becomes a problem in ultra-small metal oxide semiconductor (MOS) devices. Therefore, HCI will degrade the electrical characteristics of MOSFETs and hence the dependability of the associated electronic systems.

#### 2.2.4 Time-Dependent Dielectric Breakdown (TDDB) aging

The TDDB is a degradation phenomenon of SiO<sub>2</sub>, the thin insulating layer between the control "gate" and the conducting "channel" of the transistor. SiO<sub>2</sub> has a very high band gap (approximately 9 eV) and has excellent scaling and process integration capabilities, which makes it the key factor in the success of MOS technology.

Although SiO<sub>2</sub> has many extraordinary properties, it is not perfect and suffers degradation caused by stress factors, such as a high oxide field. The exact physical mechanism of TDDB is still an open question. The general belief is that TDDB of gate insulating material results from the cumulative effect of insulator trapped charge buildup during short-term and long-term high-field stress. High trapped-charge-induced local fields build up within the insulator creates defects in the volume of the oxide film. These defects accumulate with time and eventually reach a critical density, triggering a sudden loss of dielectric properties [9]. These defects also cause gate leakage and excess noise in MOSFETs. A surge of current produces a large localized rise in temperature, leading to permanent structural damage in the Sio2. One usually refers to *soft-breakdown* (SBD), which is reversible, and *hard-breakdown*, which results in permanent damage. Both will create failures in MOSFETs and hence the dependability of associated electronic systems will degrade.

## 2.3 State-of-the-art in aging faults

In [10], authors build a unified gate sizing algorithm which considers NBTI and OBD (Oxide Break Down) along with the traditional metrics (power and performance) of gate sizing. They have developed a static timing analysis engine and a discrete gate sizer which use an accurate delay model. Their model is embedded in their sizer to perform NBTI aware gate sizing which degrades circuit lifetime due to OBD. They have used a metric for OBD at the circuit level and performed reliability-aware gate sizing by modifying the cost/metric in the sizer algorithm.

In [80], authors proposed a gate replacement technique to mitigate NBTI-induced circuit aging. Their technique identifies the critical gates by considering the impact of the types of input gates on their protectability, guaranteeing all the critical gates can be protected from static NBTI fatigue. The experimental results show a gain of four times improvement on NBTI-induced delay degradation, compared to the techniques that neglect the impact of input gates' type.

Microprocessors at nano scale have been exposed to various reliability issues, which include a more rapid aging of all components. This leads to increasing pipeline stage delays during the operational lifetime, resulting in imbalanced designs in terms of delay and Mean Time To Failure (MTTF), if the delays are balanced at design time. In [11], authors proposed an aging-aware MTTF-balanced pipeline design scheme to replace the traditional delay-balanced paradigm. Using their approach, the imbalance during runtime is minimized, allowing better designs. Their experimental results show that for the so-called FabScalar microprocessor, the MTTF-balanced design yields in a more than 2.3 times longer MTTF, while showing the same performance as for the delay-balanced design can be maintained.

In order to predict a failure due to transistor aging [77], authors proposed a scan-based on-line aging monitoring scheme which observes aging by capturing functional data at different timing within the functional clock period and comparing the captured data. They added an early capture scan chain which captures the functional data earlier than the original scan chain. To decide the early capture timing, they used the so-called guard-band interval. An early capture scan chain was designed to capture functional data at the falling edges of the functional clock. An adjustable duty cycle clock generator was employed to shift the falling edges within a guard-band interval. Since all the aging monitoring operations are performed during system operation, there is no performance impact.

In [81], authors designed a digital sensor IP for in-situ timing slack monitoring on actual circuit paths. Their sensor extracts timing slack information from circuit paths in the post-silicon phase. The timing slack data reveals how much critical or near-critical paths changed because of reliability effects like process variation and aging.

## 2.4 BASTION contributions to aging fault study

Some of BASTION partners' activities on aging are focusing on the design of embedded instruments and monitors. These methods are able to detect the early effects of aging in processors. Some measurement results are already available on aging, and this data can be used in the next phase, where hierarchy is introduced and more complex digital systems are tackled.

### 2.4.1 Aging Measurement Embedded Instruments

In nanometer CMOS technologies, aging effects tend to increase the threshold-voltage of single MOS transistor in time and hence reduce its drain current. The consequence is certain performance reduction for analogue/mixed-signal IPs.

An existing solution for measuring the degraded performance is using an embedded-instrument (EI). These on-chip EIs are supposed to test basic physical parameters like voltages, currents, temperatures, as well as performance parameters of analogue/mixed-signal IPs.

In Bastion, we designed a threshold-voltage measurement EI for MOSFETs. It can measure the threshold-voltage of a MOS transistor periodically and extract the change in threshold-voltage which is caused by aging effects.

The threshold-voltage is one of the most sensitive parameters in MOS transistors in terms of reliability. Many reliability effects, like NBTI/PBTI, HCI, TDDB and CHC, tend to increase the absolute value of the threshold-voltage with stress time. Therefore, measuring the threshold-voltage repeatedly during MOSFET's lifetime is

highly demanded. Traditionally, the threshold-voltage is measured by complicated equipment like probe stations and a semiconductor parameter analyzer. It increases the cost and limits the time period to observe the threshold-voltage shift. The proposed EI provides a way to measure the MOSFET's threshold-voltage using on-chip ADCs and DACs.

The threshold-voltage  $(V_{th0})$  cannot be measured directly. Normally, It is extracted from the drain current measurement at various gate and drain voltages with compact models.  $V_{th0}$  shift by ageing can be measured by the difference in  $V_{th0}$  between the reference transistor and the DUT aged transistor.

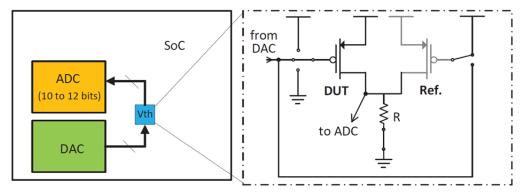

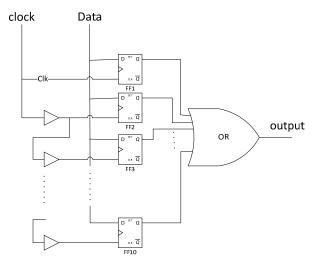

Figure 1 shows the proposed EI for measuring the  $V_{th0}$  ageing behavior inside a SoC.

**Figure 1:** The proposed EI for measuring the V<sub>th0</sub> ageing behaviour inside a SoC.

A long-time stress test on 90nm has been carried out. The test chip is put into an oven and is heated up to 127°C. The test chip contains 32 PMOS DUT transistors and supplied by a 1.15V power supply during the stress test.

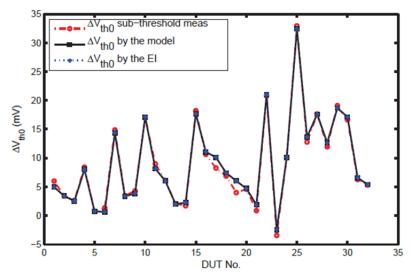

The change of threshold-voltage,  $V_{th0}$  due to reliability effects is plotted in Figure 2. The figure shows the  $V_{th0}$  by the three methods of the same group DUTs after 1 week (167 hours) stress at 127°C. It can be seen that the proposed EI can characterize  $V_{th0}$  shift with 3mV accuracy.

**Figure 2:** After stress for 167 hours, comparing the measured  $V_{th0}$  change with the EI and another two methods in 90nm PMOS DUT transistors

#### 2.4.2 Using On-chip health monitors in SoCs

The trend of downscaling and increased complexity of digital ICs has enabled the implementation of many-processors in complex SoCs. Especially in the case of homogeneous many-processors SoCs (MP-SoCs), this turns out to be an extremely nice feature in terms of reliability. However, the downside of downscaling and complexity is the increase in variability and decrease in reliability of the components. To counteract this loss, use can be made of multi-processors. Our generic approach for implementing high-dependability SoCs uses on-chip health monitor (HM) tests or measurements on processor cores during their operational life to evaluate their health and subsequent repair of (to be) faulty processors by remapping and rerouting (spare) correct cores using run-time mapping software.

We have enhanced long-term dependability of MP-SoCs being used in high-level security and automotive applications. Our prognostic approach for life-time prediction of cores uses on-chip health monitors (e.g., supply-voltage monitoring) per core in combination with advanced prediction algorithms in software to ensure a high dependability. However, this approach assumes that there is a *close correlation* between the on-chip health monitor measurements and key core specification parameters, like for example the maximum operating clock speed or the dynamic power current, as function of time (aging).

In other words, the final goal is that only the on-chip set of HMs will accurately predict, together with embedded life-time prediction software, when cores are expected to fail in time. In this advanced way, a timely replacement can be made. It is much more efficient than an automatic scheduled repair action determined at design time.

For the following example, the target Xentium processor core for the BASTION aging fault study has been used for the measurement results. This target processor core is an (embedded) Xentium<sup>TM</sup> reconfigurable DSP core, implemented in 90nm CMOS technology which has been designed and implemented by Recore Systems.

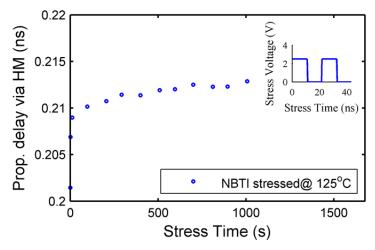

An example of measurement results in terms of cell propagation delay is shown in Figure 3, resulting from NBTI ( $V_{th}$  shift) aging for an Inverter cell. Figure 3 shows the propagation delay increases around 5.7% after a stress time of only 16 minutes under 125°C. The applied stress voltage is also shown.

**Figure 3:** Example of the increased propagation delay of an inverter versus stress based on NBTI Vth shift *measurements*. A pulse-wave stress signal has been used.

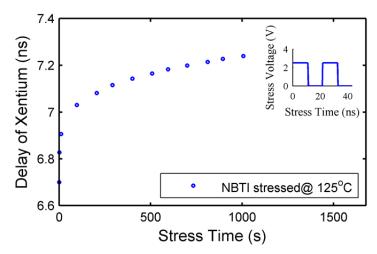

The expected increased propagation delay times of a Xentium versus stress time is shown in Figure 4. Stress temperature, stress time, and voltage stress profile are indicated.

**Figure 4:** The increased delay (decrease in operating frequency) of the most critical path in the Xentium processor core obtained from *simulation*. This result will cause speed failure after some time (reduced dependability).

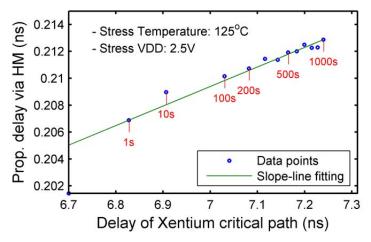

A basic requirement is that in our case the health monitoring data should sufficiently correlate with the key specifications of importance with respect to dependability/reliability. The previous NBTI delay-related data (Figure 3) is linked to the Xentium delay data (Figure 4), both under the same stress regime of voltage, temperature and stress time. This is depicted in Figure 5.

**Figure 5:** Delay obtained via NBTI health monitor (measurements) and delay (simulated) of the Xentium processor core under the same aging regime. Data points are in relation with the stress times (0-1000s).

Horizontal or vertical data lines in the graph would show that there is no correlation at all between the two; anything in between will indicate some degree of correlation. How much correlation is required is often an object of discussion; often it ranges between 85% up to 99%.

As it can be seen from Figure 5, this correlation exists, and hence the concepts used in alternate testing, like deriving mapping functions, can be applied in principle. It can

be further improved if multiple health sensors are incorporated which are showing correlations with the Xentium delay. The same principle also holds for other key parameters.

The advantage of our reliability measurement program approach is that beside the information from the health monitors and Xentium parameters, also actual reliability measurements/calculations can be used to calibrate the life-time via really occurred failures. This is rather unique, and should significantly improve the life-time prediction accuracy.

#### 2.4.3 Hierarchical identification of NBTI-critical paths

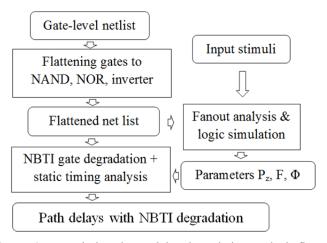

The previous developments in (low-level) NBTI measurements from the University of Twente can be subsequently used by the work on hierarchy of aging faults of the Tallinn University of Technology. In order to enable analysis of aging effects in large circuits, we have introduced a concept of hierarchical modeling of dynamic NBTI aging. To allow calculation of NBTI-induced gate delay degradation, for each signal  $x_i$  in a net list, signal probabilities  $Pz(x_i)$  (i.e. the probability of signal being 0 over a functional test set) are calculated by gate-level logic simulation and the numbers of gate fanouts  $F(x_i)$  are derived by structural analysis at the gate netlist, respectively. These parameters together with the expected operation time  $\Phi$  in years are applied as an input to the NBTI-aware gate delay degradation analysis.

Figure 6 presents the proposed hierarchical NBTI-critical path analysis flow, which takes place as follows. As a preprocessing step, complex gates are flattened into NAND, NOR and inverter gates: e.g., an AND gate will be represented by a NAND gate followed by an inverter gate. Then, gate-level simulation calculating the signal probabilities  $Pz(x_i)$  for all inputs  $x_i$  of the stages is performed which is followed by structural analysis providing the number of fan outs  $F(x_i)$  for the stages that are driven by signals  $x_i$ .

Figure 6: NBTI-induced gate delay degradation analysis flow.

These parameters together with the circuit lifetime  $\Phi$  (in years) are included to the NBTI-induced gate delay degradation analysis. After calculating the individual NBTI-degraded gate delays, static timing analysis in order to identify path delays taking into account the effects of NBTI are obtained.

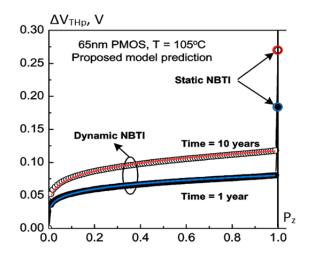

The nominal delays  $d(G_k)$  in the logic gates  $G_k$  are taken from the technology library. Calculation of the NBTI-induced delay degradation  $\tau(G_k)$  is technology dependent. In BASTION, we applied the data for 65 nm technology from [76] as follows. Delay  $t_i$  was calculated for each input signal  $x_i$  separately. The voltage threshold shift  $\Delta V_{th}(x_i)$  was calculated as follows:

$$\Delta V_{th}(x_i) = (\alpha \cdot P_z(x_i))^{\beta}, \tag{1}$$

Where  $P_z(x_i)$  is the signal probability for input signal  $x_i$  and  $\alpha$  and  $\beta$  are technology dependent constants that were set to generate a graph that matches the curves obtained by NBTI-aging analysis in [76] (See Figure 7). (In our experiments  $\beta$  is set to 0.18868 and  $\alpha$  is set to  $15 \cdot 10^{-7}$  for 1 year of aging and to  $115 \cdot 10^{-7}$  for 10 years of aging, respectively). In order to calculate the  $\Delta V_{THp}(x_i)$  values for the static case where  $P_z(x_i) = 1$ , we assigned  $\Delta V_{THp} = 0.18V$  for 1 year and  $\Delta V_{THp} = 0.27V$  for 10 years of aging, respectively. Figure 7 shows the fitting of the mathematically convenient function (1) (the red and blue curves) to the comprehensive analysis of **Error! Reference source not found.** (the white and black dots).

**Figure 7:** Threshold voltage shift  $\Delta V_{THp}$  as a function of signal probability  $P_z$

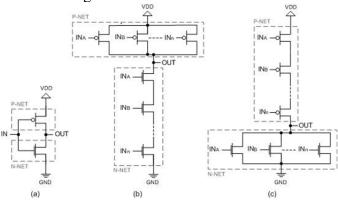

The *SPICE* simulation process consisted of simulating the basic cells of the technology library for different  $\Delta V_{THp}$  (*pMOS* transistor threshold voltage shift) values in order to capture the dependence of gate output delay on  $V_{THp}$ . Figure 8 displays the typical n- and p-networks displaying device interconnections for *INVERTER*, *NAND* and *NOR* gates considered for simulation.

**Figure 8:** Typical n- and p-networks displaying device interconnections for (a) Inverter, (b) NAND and (c) NOR gates considered in this work

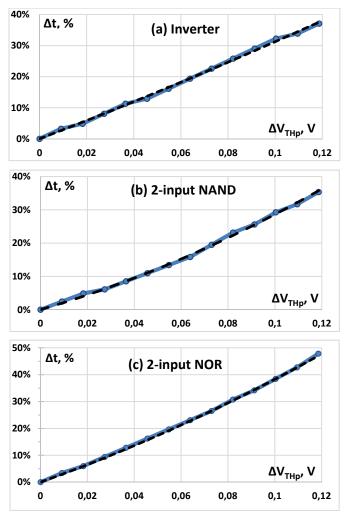

Figure 9: Dependence of gate output delay on  $V_{THp}$  shift for the rising transition  $0 \rightarrow 1$  in SPICE (blue curve) and the curve function (dashed black) that matches the SPICE results for (a) Inverter, (b) NAND2 and (c) NOR2

Figure 9 shows the gate-aging characterization step in SPICE for Inverter, NAND2 and NOR2 gates. It captures the dependence of Gate Output Delay on  $V_{THp}$  for the rising input transition  $0\rightarrow 1$ . The following mathematically convenient function (dashed black curve) was matched to the curves characterized with SPICE (blue curve) in order to calculate the percentile change in gate delay values:

$$\Delta t_{gate} = \lambda \cdot \Delta V_{THp}(x_i) + (\mu \cdot \Delta V_{THp}(x_i))^2 \qquad (2)$$

where  $\Delta t_{gate}$  is the nominal gate delay increase in percent for the gate,  $\Delta V_{THp}(x_i)$  is the change of threshold voltage  $V_{THp}$  for *pMOS* transistors at the gate input  $x_i$  and  $\lambda$  and  $\mu$  are technology dependent constants. In our experiments  $\lambda$  and  $\mu$  are set to 3.1 and 2.7 for the NOR gate, to 2.05 and 2.85 for the NAND gate and to 2.9 and 1.5 for the Inverter, respectively.

Note that only the increased gate delay for the  $0\rightarrow 1$  transition at gate inputs were characterized as the *SPICE* experiments revealed no deviation, or at least there was a negligible deviation in the input  $1\rightarrow 0$  transition delay after aging. This can be explained due to the fact that as the *pMOS* device in the *p*-network is getting older, it facilitates the task of discharging the gate output capacitance by the *nMOS* device,

placed in the *n*-network. The exception is a *NOR* gate, especially *NOR* with multiple inputs, e.g. *NOR4*, where gate delay degradation for input  $1\rightarrow 0$  transition became slightly negative, i.e. transition delay decreased compared to the nominal one.

Note that when compared with the *NOR* gate, the *NAND* gate does not display reduction of the output delay because of the *n*- and *p*-network topologies: in the *NOR* gate case, *pMOS* devices are connected in series (resp. in parallel for *NAND* gate), whereas *nMOS* devices are connected in parallel in *NOR* (series in *NAND* gate, see Figure 8). This device interconnection facilitates the discharge of the gate output capacitance by the *nMOS* devices, while rendering more difficult the task of *pMOS* devices to charge-up the output capacitance in the case of *NOR* gates, that is the reason we observed reduction of the output delay for the fall-edge delay. The proposed functions (1) and (2) closely match the *SPICE* electrical characterization and the *NBTI* data from Error! Reference source not found, respectively. These functions were implemented in *gate-level aging simulation to provide extremely fast calculation for NBTI-induced delay degradation.*

#### 2.4.4 NBTI-critical path delay calculation

In the following, a method for fast calculation of the *NBTI*-induced delay degradation at paths of a gate-level circuit is proposed. In the calculation process we use the following notations:

- $d(G_k)$  is the nominal delay of the fresh gate  $G_k$  without considering aging, i.e. its delay at time zero;

- $\tau(G_{k,i})$  is the increase in the delay of the gate  $G_k$  from the *i*-th input  $x_{k,i}$  to the output of the gate caused by NBTI-induced aging;

- $t(G_{k,i})$  is the total delay of the gate  $G_k$  from the i-th input  $x_{k,i}$  to the output of the gate caused by NBTI-induced aging,

$$t(G_{k,i}) = d(G_k) + \tau(G_{k,i});$$

$t(G_k)$  – is the total maximum delay of the gate  $G_k$  over all its  $m_k$  inputs, when taking into account *NBTI*-induced aging,

$$t(G_k) = \max \{t(G_{k,1}), t(G_{k,2}), ..., t(G_{k,m_k})\};$$

$D(G_k)$  – is the delay calculated for the slowest signal path in the cone  $C_{IN}(G_k)$  based on the values of  $t(G_{k,i})$  for all gates on this path,

$$D(G_k) = \max \{ (D(G_i) + t(G_{k,i})) \mid G_i \in IN(G_k) \},$$

where  $IN(G_k)$  is the set of input gates of  $G_k$ , and  $t(G_{k,i})$  is the total delay of the gate  $G_k$  from the output of the gate  $G_i$  caused by aging;

Consider a combinational circuit as a network of gates where all the gates have numbers which show the ranking of gates in a partial order such that:

- (1) all the input gates are numbered in an arbitrary order,

- (2) all other gates may get their numbers only if all their predecessor gates have already got their numbers.

We present Algorithm 1 for calculating  $D(G_k)$ , which is based on processing the gate-level netlist, gate by gate, from inputs to outputs. The method calculates the maximal degraded path delay values  $D(G_k)$  for all the gates of the circuit based on the estimates of  $t(G_k)$ , where NG is the number of gates in the circuit.

**Algorithm 1**. NBTI-aware static timing analysis

```

FOR all gates G_k, k = 1, 2, ..., NG:

t'(G_{k,i}) = \begin{cases} t(G_{k,i}), & x_{k,i} = 0 \\ d(G_k), & x_{k,i} \neq 0 \end{cases}

D(G_k) = \max \{D(G_i) + t'(G_{k,i}) \mid G_i \in IN(G_k)\}

```

As a result, fast an accurate calculation of NBTI-degraded paths will be performed at the gate-level.

Experimental results show a high scalability as well as good match with SPICE simulation results for the proposed method.

## 2.5 Conclusions on aging faults

After an introduction about aging faults and state-of-the-arts publications, we described our original contributions stemming from the BASTION project.

The proposed approach addresses the design of aging monitors, and enables a new generation of very high dependability many-processors SoCs in safety-critical applications. It consists of aging monitors, which can be related to the performance of processors. More specifically, an NBTI monitor has shown to have correlation with propagation delay in the aged processor.

Moreover, an embedded instrument has been designed. This instrument is able to measure the change in threshold-voltages caused by aging effects. This instrument can provide detailed information with respect to the performances of digital systems.

In addition, the Tallinn University of Technology has introduced a method of hierarchical modeling of dynamic NBTI aging to enable analysis of aging effects in large circuits. This can use the results from the previous research of the University of Twente. Preliminary experimental results show high scalability as well as good match with SPICE simulation results. Work on the evaluation of the method continues, to validate these new results in practice.

#### 3 NFF faults at the IC level

#### 3.1 IC-level vs. board-level NFFs

No Fault (or Failure) Found (NFF) is a term used in various fields, especially in the electronics industry referring to a system or component that has been returned to the manufacturer or distributor for warranty replacement or service repair, but operates properly while being re-tested. This situation is also referred to as No Defect Found (NDF) and No Trouble Found (NTF) and it is closely related to test escapes.

The typical NFF symptoms at the product level are:

- o System passes all tests at the production

- o System fails at the end customer

- o Troubleshooting cannot repeat the failing condition

NFF returns can seriously erode profit margins for manufacturers and service providers. The time, materials and shipping costs in exchanging hardware is enormous in relation to the cost of the item being replaced. Further, NFF returns can also indicate those customers' problems have not been resolved, thus implying reduced customer satisfaction and eroded brand value.

NFF can be considered at different system levels and different stages of the supplierclient value chain. In the context of BASTION, we consider two corner cases:

- a) NFF in the IC (component-level) and

- b) NFF at the **board** (product-level).

The latter case was described a few paragraphs above, while the former case is similar, but it does not involve the end customer. Putting it simple, if board-level or product-level tests are failing in the way that indicates a particular IC being faulty, but that IC re-testing is OK, it is considered to be an *IC-level* NFF problem.

According to our current hypothesis, the two cases should be considered separately and they may have different major NFF causes. The initial findings indicate that a realistic NFF contributor at the IC level is the intermittent fault, which is detailed in the following section. At the board-level test, the root-cause of NFF (in addition to intermittent faults) could be the incompleteness of test coverage metrics due to missing fault models for certain types of defects (primarily timing faults) and, as a consequence, missing of certain types of deterministic test sets.

In this section, NFF faults and different types of NFFs, mainly at IC level are introduced. The relation of NFF and intermittent faults and how intermittent faults can be distinguished from other kind of faults are explained. After a classification of NFFs, a study of state-of-the-art works in NFF faults is presented. In the last part, our contribution with regard to IC-level NFF faults is presented. The *board-level* NFF problem study is given in Chapter 4.

#### 3.2 Introduction to IC-level NFF

With the continuous decrease of CMOS feature size, there are more electrical products that show anomalous behavior in the field but function properly during testing. These products are known as NFF (No Fault Found). These products are also referred to as "could not duplicate", "trouble not identified", "retest OK", "no trouble found" and so on [12-14]. In order to improve product reliability and reduce return costs, manufacturers spend a significant amount of time and money to investigate causes of NFFs.

A potential important cause of NFFs corresponds to intermittent faults. Faults in semiconductor devices can be classified as permanent, transient and intermittent faults. Transient faults are induced by temporary environmental conditions such as neutrons from the atmosphere and energetic particles from packaging material. Hard (or permanent) faults reflect irreversible physical changes, mainly corresponding to manufacturing defects, such as contaminations in silicon devices or wear-out of materials. Intermittent faults occur due to unstable or marginal hardware, and they can sometimes be activated by an environmental change such as temperature or voltage alterations [15], [16].

Transient and intermittent faults manifest very similarly. However, an intermittent fault is distinguishable from a transient one by the following criteria:

First, replacement of the offending circuit removes the intermittent fault, by contrast with transients, which cannot be eliminated by repair.

Second, transient faults affect random locations while an intermittent fault occurs repeatedly at the same location.

Third, errors induced by intermittent faults tend to occur in bursts [17].

#### 3.3 Classes of IC-level NFF faults

A specific category of NFFs are intermittent faults, characterized by random low-level occurrences in time, randomly fixed in locations, but repairable (at least in PCBs and cabinets) if found. Especially in the space and avionic application fields, this category of faults ranks among the highest in terms of occurrence (>50%) as well as cost [18]. Different categories of intermittent faults can be identified. The next subsections address them.

#### 3.3.1 Intermittent resistive faults

Intermittent resistive faults usually are a prelude to permanent faults (in particular, open faults) in time (aging) [19]. It is important to note that intermittent faults are quite dependent on environmental conditions, like temperature or mechanical effects (e.g., vibration) [18].

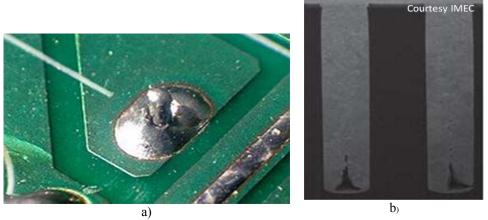

There are several physical root causes of intermittent resistive faults. At PCB and cabinet level, cold solder contacts (see Figure 10a), damaged traces/wires, and loose connectors are the major reasons. In integrated circuits, the continued scaling of interconnection is likely to increase intermittent faults. Origins can be electro

migration (EM), soft breakdown (SBD), material residuals and induced voids (see Figure 10b) and cracks in 3D Through-Via Contacts (TSVs) within chips [20].

Figure 10: Several possible causes of intermittent faults: a) Cold (cracked) soldering joint on a PCB, b) voids and cracks in TSVs.

#### 3.3.2 Intermittent stuck-at faults

An intermittent stuck-at fault causes the value on the faulty signal line to intermittently be stuck at a logic value "1" or "0". The most vulnerable structures to intermittent stuck-at faults are storage structures, such as memory and register file. Intermittent stuck-at faults are caused by residues in storage cells or solder joints during manufacturing.

#### 3.3.3 Intermittent short faults

Intermittent short faults are shorts in wires or shorts in transistors. If an element is intermittently shorted to power or ground, it is equivalent to an intermittent stuck-at fault. If two signal wires are shorted together, an intermittent bridging fault occurs.

#### 3.3.4 Intermittent open faults

Intermittent open faults are breaks or imperfections in circuit interconnections such as wires, contacts, transistors and so forth. These faults are usually caused by electromigration, stress migration, or intermittent contacts.

#### 3.3.5 Intermittent timing faults

Intermittent timing faults will result in timing violations and affect data propagation when they occur. They usually lead to writing wrong data to storage cells. Intermittent timing faults can be broadly classified into intermittent path-delay faults and intermittent transition faults. Intermittent timing faults are mainly caused by inductive noises, aging, crosstalk, or process, voltage, temperature (PVT) variations.

#### 3.4 State-of-the-art in IC-level NFF faults

The effects of transient and permanent faults have been extensively analyzed [21, 22]. However, less attention has been given to the intermittent faults. Field collected data and failure analysis results from avionic instruments [23-25], and commercial electrical systems [14, 17, 26, 27] clearly show that intermittent faults are a major cause for field returns in modern integrated circuits.

Recently, there are few publications which study the impacts of intermittent faults on microcontrollers [28] and microprocessors [29-31]. In [28], the authors have generated fault models for intermittent faults at logic and RTL abstraction levels, and injected these faults in the VHDL model of a microcontroller to study their impact on the system behavior. Their experiments were carried out using the so-called fault injection technique. Their study has been focused on the buses. They used a tool called VFIT to inject intermittent faults in a VHDL model of an 8051 microcontroller. Their fault model included intermittent pulse, intermittent short, intermittent open, and intermittent delay. Their experimental results show that the percentage of failures when injecting *multiple* intermittent faults is between 60% and 80% depending on the *workload*. In addition, the impact of pulse, open and short intermittent faults are very similar, provoking high values of the percentage of failures, but the intermittent delay fault model has a lower impact than the intermittent pulse, intermittent open and intermittent short, due to timing masking in synchronous components.

Gil-Tomás et al. in [31] studied the impact of intermittent faults on the behavior of a reduced instruction set computing (RISC) microprocessor. The authors of this work used VHDL-based Fault Injection to investigate the impact of intermittent faults. Authors emphasize that their work complements their previous works published on a commercial complex instruction set computing (CISC) microcontroller.

Another work which studies intermittent faults in microprocessor is [29]. In this paper, authors propose a metric called *intermittent vulnerability factor* (IVF) to characterize the vulnerability of microprocessor structures to intermittent faults. A structure's IVF is the probability an intermittent fault in that structure causes an external visible failure. They compute IVFs for register files and buffers considering three intermittent fault models: the intermittent stuck-at-1 and stuck-at-0 fault model, the intermittent open and short fault model, and the intermittent timing fault model.

Their experimental results show that among the three major types of intermittent faults, intermittent stuck-at faults have the most serious impact on program execution.

## 3.5 BASTION contributions to NFF fault study

In [32][78], we have made a first step to investigate the effects of a special category of No Faults Found, being intermittent resistive faults resulting from interconnection flaws which are random in time, but not in location(s). They are known to be extremely difficult to detect, diagnose and in chips to correct. They occur in PCBs as well as integrated circuits; with the arrival of 3D-TSV in future integrated systems they are likely to occur more frequently than nowadays, and ball-grid SoCs have been shown to be vulnerable for this type of faults.

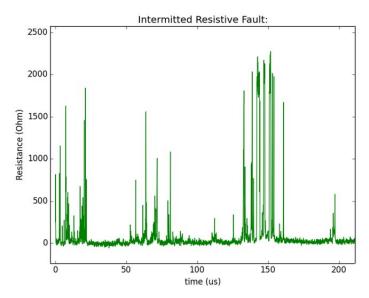

To have an insight into intermittent resistive fault behavior, we emulated several loose connections and cold soldering / ball grids. We precisely measured the amount of

resistance that loose connections or cold solder can induce on a given circuit. Figure 11 shows the *measured* intermittent resistive behavior of a loose connection. Thermal and vibration effects were generated using external stimulators.

Figure 11: Measured resistance of a damaged/cold soldering interconnection.

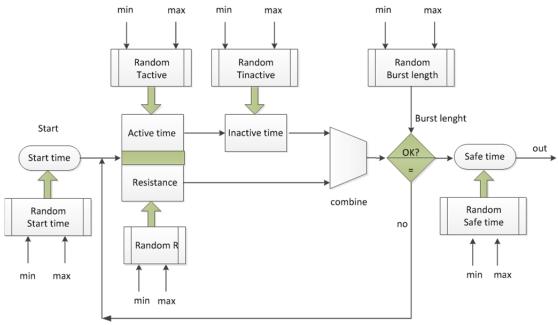

Based on our (and others, like Ridgetop) measurement experiences, a simulation injection model for intermittent resistive faults has been developed (see Figure 12). The parameters in this simulation-based fault injection model can be extended and changed at will, as they are probability functions.

Figure 12: Basic scheme of a programmable intermittent resistive fault injector for our simulator environment. Resistance, burst number, activation time, inactive time and delay are the input parameters.

As intermittent resistive faults have different influence on analogue and digital circuits, we have investigated the influence of them on analogue and digital CMOS circuits separately in [32] and [78].

#### 3.5.1 Intermittent fault effects on analogue CMOS

In order to get an idea of the influence of the fault parameters on analogue CMOS circuits, a number of experiments have been carried out.

Two examples of intermittent resistive faults have been generated by our fault injectors which are shown in Figure 13. The fault model has been written in Verilog-A and can be directly used in combination with Cadence Virtuoso tools.

The first fault model has resistance value  $1\Omega - 850\Omega$ , a start time of  $10\mu s$ , a minimum activation and inactivation time, the safe time equals to  $10\mu s$ , and 10 events occur in the burst.

The second fault has the following specifications R:  $1\Omega$ – $1K\Omega$ , start time of  $5\mu$ s, minimum activation and inactivation time, safe time equal to  $15\mu$ s, and 8 events in burst.

Figure 13: Two examples of an intermittent resistive fault generated by our injector. a): R:  $1\Omega - 850\Omega$ , b) R:  $1\Omega - 1K\Omega$ .

As an initial target circuit for our experiments, an analogue 65nm TSMC OpAmp has been chosen. This can easily degenerate in a digital inverter or buffer; but it has the advantage to provide us more information on what really changes in the circuits, without inmediately being (or not) restored in the pure digital case.

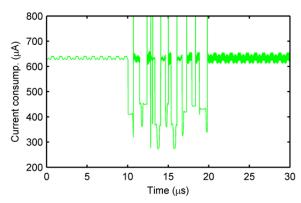

Our experimental (Cadence simulation) results show that intermittent resistive faults on the power signal line can have the largest influence. Figure 14 shows the simulated power-supply current signal of a component with an emulated intermittent resistive fault on the power-supply signal of the component.

Via a current monitor, this kind of behavior could be observed continuously.

Figure 14: Simulated power-current output signal.

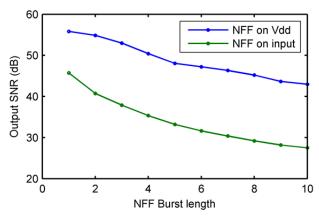

Finally, as it can be observed from Figure 15, the SNR decreases if the number of events increases. This Figure shows the SNR of the output as a function of the number of events in a burst of an intermittent resistive fault in the input and power-supply line.

Figure 15: Influence of sweeping the burst length from 1 to 10 on the output SNR of the example component (OpAmp).

## 3.5.2 Intermittent fault effects on digital CMOS

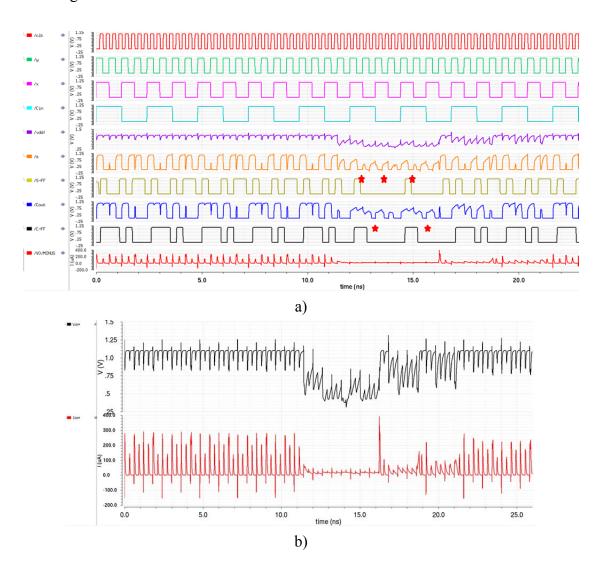

In [78], we have investigated the impact of intermittent resistive faults on the behavior of a digital CMOS circuit via simulation. The occurrence rate of this kind of defects can take a very long time, such as one month, whereas the duration of the defect can be as short as 50 nanoseconds. Therefore, evoking and detection of these faults are a huge scientific challenge. An on-chip data logging system with time stamp and stored environmental conditions, along with the detection, will drastically improve the task of maintenance of avionics and reduce the current high debugging costs.

To evaluate the influence of intermittent resistive faults on the electrical behavior of digital circuit, a fault injector has been used, as showed in Figure 12. There are six parameters that can be set according to the specific application, with a minimum and maximum value and a certain (random) distribution.

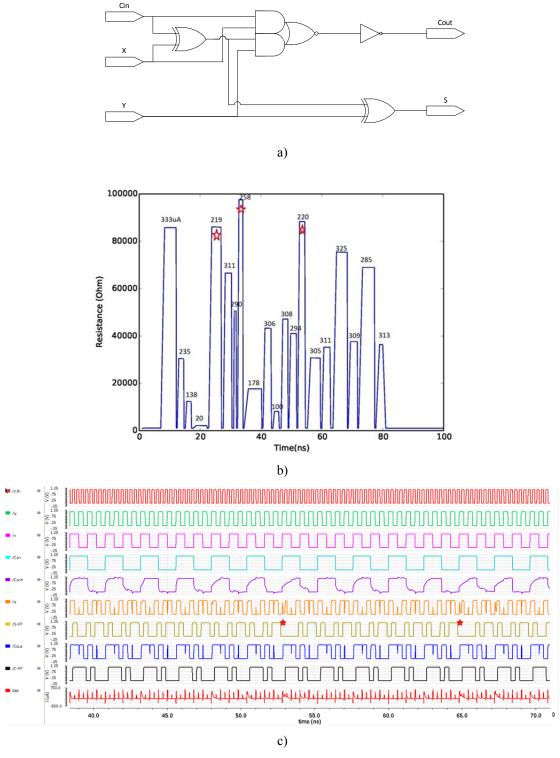

As a simple example we have used a static CMOS full-adder circuit, its sum and carry outputs latched in D-type flip-flops, in 45nm Nangate CMOS technology. The circuit

operates at a clock frequency of  $3.3 \mathrm{GHz}$  (0.3ns). The logic scheme of the combinational part is depicted in Figure 16a; its transistor implementation is provided at a lower hierarchical level. The single (statistically) generated IRF in the carry  $C_{in}$  input is shown in Figure 16b.

**Figure 16:** Simulation of a full adder under influence of an IRF in input Cin. a) logic scheme of a full adder in 45nm NAN CMOS library, b) used IRF input pattern at input Cin (red star shows under which condition a logic error occurred, value on top is the Iddt value), c) the simulated functional output voltages of the full adder, including the dynamic power current. Red stars indicate functional logic failures.

The flip-flop clock clk, inputs (X, Y, Cin) and output (S, S-FF, CO, C-FF) voltages, and dynamic supply current Iddt are shown in Figure 16c.

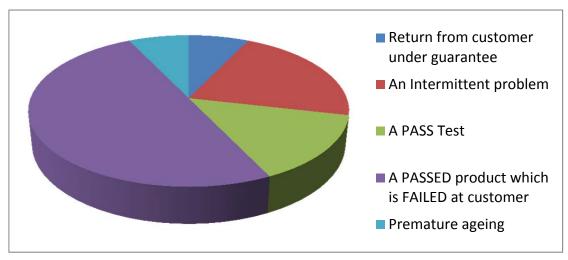

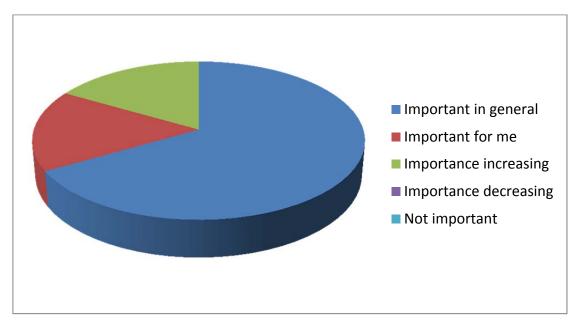

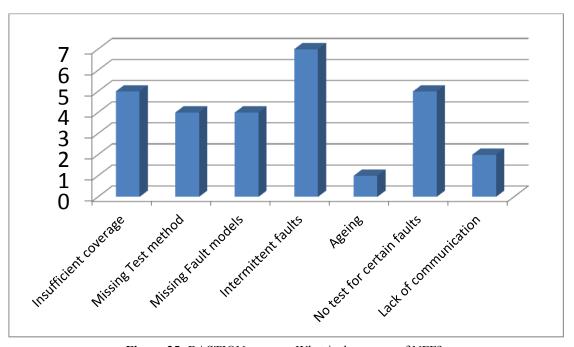

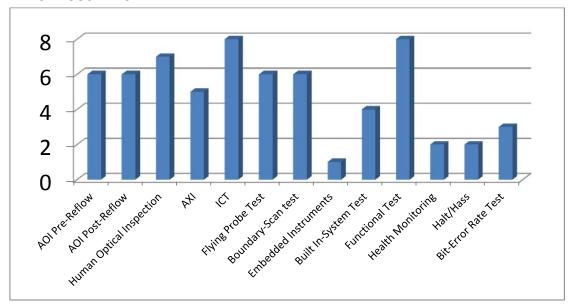

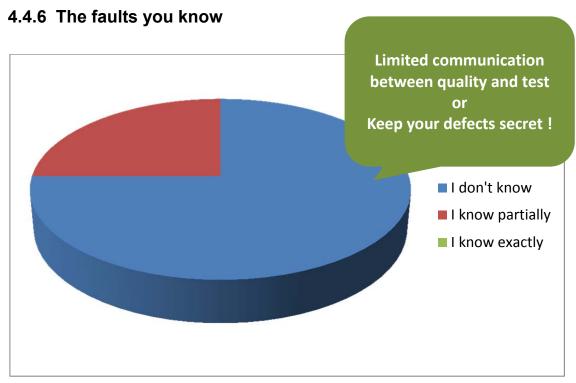

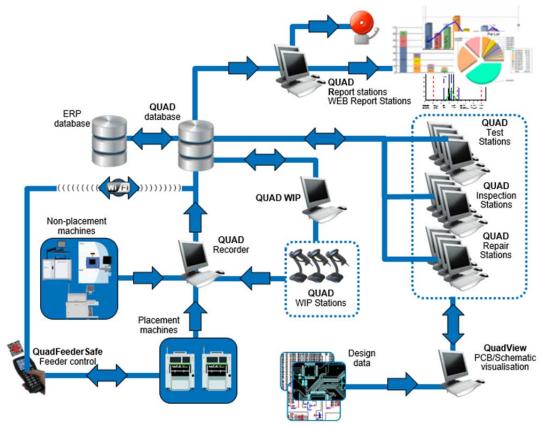

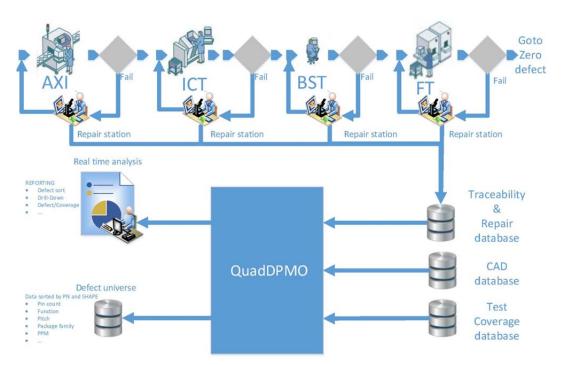

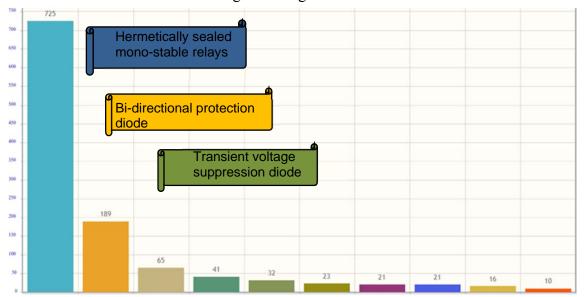

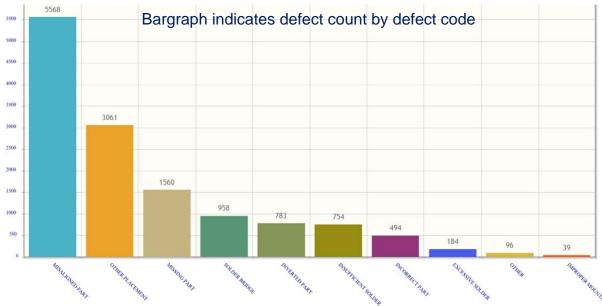

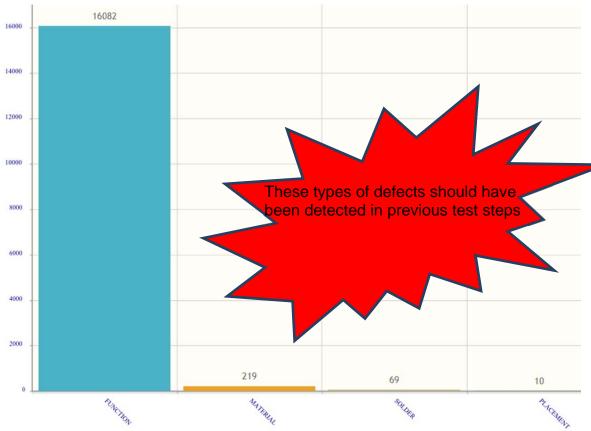

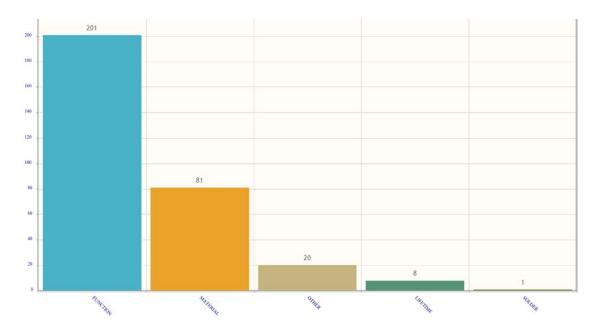

As can be seen in Figure 16b, the carry input Cin has been disturbed by the IRF (a burst of 20 pulses), but only in three cases (red star) this translated into an incorrect logic output after the flip-flops. This is because digital CMOS circuits are very robust with regard to disturbances; or in terms of testing, most of the faults (IRF) are being masked. However in the analogue dynamic power current (Iddt), disturbances can be noticed (bottom Figure 16c).