#### FP7-ICT-2013-11-619871

### **BASTION**

Board and SoC Test Instrumentation for Ageing and No Failure Found

Instrument: Collaborative Project

Thematic Priority: Information and Communication Technologies

# Report on Design & Validation of Embedded Instruments for Detection of Several Aging Faults, based on IEEE1687 (Deliverable D2.1)

Due date of deliverable: December 31, 2015 Ready for submission date: February 2, 2016

Start date of project: January 1, 2014 Duration: Three years

Organisation name of lead contractor for this deliverable: University of Twente (UT)

Revision 1.10 (02/2/2016)

| Proje               | ect co-funded by the European Commission within the Seventh Fr       | amework     |  |  |

|---------------------|----------------------------------------------------------------------|-------------|--|--|

| Prog                | Programme (2014-2016)                                                |             |  |  |

| Dissemination Level |                                                                      |             |  |  |

| PU                  | Public                                                               | $\boxtimes$ |  |  |

| PP                  | Restricted to other programme participants (including the Commission |             |  |  |

|                     | Services)                                                            |             |  |  |

| RE                  | Restricted to a group specified by the consortium (including the     |             |  |  |

|                     | Commission Services)                                                 |             |  |  |

| CO                  | Confidential, only for members of the consortium (including the      |             |  |  |

|                     | Commission Services)                                                 |             |  |  |

#### **Notices**

For information, please contact Hans G. Kerkhoff, e-mail: h.g.kerkhoff@utwente.nl This document is intended to fulfil the contractual obligations of the BASTION project concerning deliverable D2.1 described in contract 619871.

© Copyright BASTION 2016. All rights reserved.

### 1 Table of Revisions

| Version   | Date          | Description and reason                    | Author                       | Affected sections          |

|-----------|---------------|-------------------------------------------|------------------------------|----------------------------|

| 0.1       | Nov 6, 2015   | Structure created                         | H.G. Kerkhoff                | All                        |

| 0.2       | Nov 20, 2015  | Removed verification & optimization IJTAG | H.G. Kerkhoff                | Chap. 5                    |

| 0.3       | Nov 20, 2015  | Background                                | H. Ebrahimi                  | Chap. 2                    |

| 0.4       | Nov 25, 2015  | State-of-the-art                          | H. Ebrahimi                  | Chap. 3                    |

| 0.4       | Nov 26, 2015  | Aging sensor                              | H. Ebrahimi                  | Chap. 4                    |

| 0.5       | Nov 30, 2015  | Reviewed and adapted                      | H.G. Kerkhoff                | All                        |

| 0.6       | Dec. 3, 2015  | Operational phase                         | M. Sonza –<br>Reorda         | 10.3                       |

| 0.7       | Dec 10, 2015  | Update material<br>ULUND                  | E. Larsson, H.G.<br>Kerkhoff | 8.2.1,<br>9.2.2,<br>10.6.1 |

| 0.8       | Dec 11, 2015  | Update, Uni. Of Tallinn                   | J. Raik                      | 10.4                       |

| 0.8.1     | Dec 16, 2015  | Update, IFAG                              | P. Engelke                   | 9.2.1,<br>10.4             |

| 0.9       | Dec 16, 2015  | Update, ULUND                             | E. Larsson                   | All                        |

|           | December 2015 | Review of draft                           | R. Krenz-Baath               | All                        |

| 0.9.1     | Jan 11, 2016  | Update, Testonica                         | A. Jutman                    | 9.7                        |

| 1.0       | Jan 13, 2016  | Update draft                              | H.G. Kerkhoff                | All                        |

| 1.1 – 1.9 | Jan 31, 2016  | Many update drafts & polish               | H.G. Kerkhoff                | All                        |

| 1.10      | Feb 2, 2016   | Preparing for submission                  | A. Jutman                    | 9.7; title pages           |

### 2 Authors, Beneficiary

Hans G. Kerkhoff, University of Twente (UT)

Hassan Ebrahimi, University of Twente (UT)

Alireza Rohani, University of Twente (UT)

Erik Larsson, University of Lund (ULUND)

Matteo Sonza Reorda, Politecnico di Torino (Polito)

Jaan Raik, TU Tallinn (TUT)

Piet Engelke, Infineon (IFAG)

Artur Jutman, Testonica Lab (TL)

Sergei Devadze, Testonica Lab (TL)

### 3 Executive Summary

This document reports on the design and validation of embedded instruments for detection of several aging faults employing IEEE 1687 as performed in BASTION. The work is part of the Task 2.1, where the University of Twente, University of Lund, Politecnico Torino, Technical University of Tallinn, Infineon and Testonica Labs have collaborated. It links to deliverable D1.1, dealing with an NFF and aging fault study

First, the background and the state-of-the art are discussed in terms of aging, related embedded instruments and the issues resulting from the usage of the IEEE 1687 (IJTAG) standard.

Next, new contributions are described from the consortium in terms of new embedded instruments, their validation and several solutions to the issues with regard to the usage of IEEE 1687, such as synchronization and interrupts.

The deliverable concludes with a summary of the obtained results, and a list of references.

### 4 List of Abbreviations

ADC - Analog-to-Digital Converter AOI - Automated Optical Inspection

ASIC - Application-Specific Integrated Circuit

ATE - Automated Test Equipment

BIST - Built-In Self-Test

BSDL - Boundary-Scan Description Language

BST - Boundary-Scan Test

BTI - Bias temperature instability

CAD - Computer Aided Design (also EDA)

CMOS - Complementary Metal-Oxide Semiconductor CPU - Central Processing Unit, also Processor

CUT - Circuit Under Test

DPM - Defects Per Million

DPMO - Defects Per Million Opportunities

DRAM - Dynamic RAM

DRC - Design Rule Check

EDA - Electronic Design Automation (also CAD)

EMS - Enhanced Manufacturing Services FIFO - First In, First Out (data buffer)

FP7 - European Union's 7<sup>th</sup> Framework Program

FPGA - Field Programmable Gate Array

HCI - Hot Carrier Injection

HW - Hardware

IC - Integrated Circuit

ICL - Instrument Connectivity Language

ICT - In-Circuit Test

IJTAG - Internal JTAG, a short name for IEEE 1687 standard and

infrastructure collectively

IP - Intellectual Property (hardware module in FPGA or SoC)

JTAG - Joint Test Action Group; also Boundary Scan; often used as a short

name of the IEEE 1149.1 standard and respective infrastructure

including test access port and header on the board;

LBIST - Logic BIST

MBIST - Memory BIST

MISR - Multiple Input Signature Register

MPS - (Coverage metrics based on) Material, Placement & Solder

NBTI - Negative Bias Temperature Instability

NFF - No Fault Found or No Failure Found (also NTF)

NoC - Network-on-Chip

NTF - No Trouble Found (also NFF)

PBTI - Positive Bias Temperature Instability

PCOLA/SOQ - (Coverage metrics based on) Presence, Correct, Orientation, Live,

Alignment/Short, Open & Quality

PDL - Procedural Description Language PMOS - p-type Metal Oxide Semiconductor

POST - Power-On Self-Test

PPVS - (Coverage metrics based on) Presence, Polarity, Value & Solder

PPRG - Pseudo-Random Pattern Generator

PUT - Path-Under-Test

PVT - Process, Voltage, Temperature RAM - Random-Access Memory

RTD - Research and Technological Development

SBST - Software-Based Self-Test

SIB - Segment Insertion Bit

SoC - System on Chip

SVF - Serial Vector Format

SW - Software

TDC - Time to Digital Converter

TDDB - Time Dependent Dielectric Breakdown

TDR - Test Data Register

TRC - Tunable Replica Circuit

UUT - Unit Under Test

VHDL - VHSIC Hardware Description Language

Vth - Threshold voltage

### 5 Table of Contents

| 1  | Table of Revisions                                                       | i  |

|----|--------------------------------------------------------------------------|----|

| 2  | Authors, Beneficiary                                                     | i  |

| 3  | Executive Summary                                                        | ii |

| 4  | List of Abbreviations                                                    | i  |

| 5  | Table of Contents                                                        | 0  |

| 6  | Structure of the document                                                | 1  |

| 7  | Background                                                               |    |

|    | 7.1 Aging Faults                                                         |    |

|    | 7.1.1 NBTI-based aging faults                                            |    |

|    | 7.1.2 HCI-based aging faults                                             |    |

|    | 7.1.3 Electro-migration                                                  |    |

|    | 7.1.4 Time-Dependent Dielectric Breakdown (TDDB) aging                   |    |

|    | 7.2 Design and Validation of Embedded Instruments for Aging Measuremen   | _  |

|    | the IEEE 1687 Standard                                                   |    |

|    | 7.2.1 The IEEE 1687 standard for fault monitoring                        | 4  |

| 8  | State-of-the-art                                                         | 7  |

| _  | 8.1 Aging Faults resulting in delays and embedded instruments            |    |

|    | 8.2 Design & Validation of Embedded Instruments using IEEE 1687 standard |    |

|    | 8.2.1 Embedded Instruments Based on Existing Built-in Self-test          |    |

|    | 8.2.2 The standard IEEE 1687 for fault monitoring                        |    |

|    |                                                                          |    |

| 9  | Design and Validation of Embedded Instruments for Aging Measur           |    |

| U  | sing IEEE 1687                                                           |    |

|    | 9.1 Aging Measurements                                                   |    |

|    | 9.2 Test Generation and Detection Embedded Instruments                   |    |

|    | 9.3 Design and Simulation Results of Embedded Instruments                |    |

|    | 9.4 Re-Use of Chip-level Embedded Instruments to detect Aging Defects    |    |

|    | 9.4.1 Experimental Results for IJTAG Controlled ADC-BIST                 | 17 |

|    | 9.5 Access of Embedded Instruments via Software in Operational Phase     | 21 |

|    | 9.5.1 Access of Embedded Instruments                                     | 21 |

|    | 9.5.2 Error Checkers Validation & Minimization                           | 23 |

|    | 9.6 Handling Synchronization and Interrupts                              | 25 |

|    | 9.6.1 Self-Reconfiguring Network                                         | 25 |

|    | 9.7 Instrument synchronization and interruption challenges               | 35 |

|    | 9.7.1 Interrupts from instruments to OS                                  | 35 |

|    | 9.7.2 Internal interrupts within the module                              | 36 |

|    | 9.7.3 Calibrated synchronization of instruments                          | 37 |

|    | 9.7.4 Triggered execution of tests & measurements                        | 38 |

| 1( | Summary & Conclusions                                                    | 40 |

|    | I. Defenses                                                              |    |

### 6 Structure of the document

In this deliverable, results are reported about the research performed by BASTION partners on design and validation of embedded instruments for detection of several ageing faults, in combination with the IEEE 1687 standard (Task 2.2).

These instruments are located at the chip level, and reuse of them will be desirable. The correct communication between embedded instruments has also been investigated in detail

This report is structured as follows:

First, a background is given on the different subjects, being aging and its embedded instruments for measuring and error detection and the issues related in using IEEE 1687. Subsequently, the state-of-the-art at the start of the project is provided in both these two areas.

Then, the main body of the work performed in this deliverable is presented, being the design and validation of Embedded Instruments (EI) for aging measurements using the standard IEEE 1687. First, aging measurements and test generation and detection of embedded instruments are treated. Then, the design and simulation results of embedded instruments are presented.

Another issue, the re-use of chip-level embedded instruments to detect ageing defects is discussed next. Subsequently, the access of embedded instruments via software in the operational phase is elaborated. As last subject, handling synchronization and interrupts are explained as well as interruption challenges.

Finally, the overall conclusions are provided. The deliverable is completed with a list of references.

### 7 Background

In this section the background information on aging faults is given, as well as error detection embedded instruments, and error handling via the IEEE 1687 standard. First, aging faults will be introduced, and next the issues with regard to the standard IEEE 1687.

### 7.1 Aging Faults

Due to aggressive scaling of technology in terms of device dimensions in advanced CMOS technologies, the design of resource-efficient reliable systems is becoming more challenging. There are various degradation mechanisms that can worsen the performance of devices, circuits and their associated electronic systems as a result of this aggressive technology scaling.

The major aging faults can be classified into electro-migration (EM), hot carrier injection (HCI), and time-dependent dielectric break-down (TDDB) and bias temperature instability (BTI). Depending on the structure and the operating conditions, transistor aging may result in more than 20% speed degradation [1].

### 7.1.1 NBTI-based aging faults

The bias temperature instability (BTI) is a degradation mechanism that occurs in MOS devices as a result of interface traps between the gate oxide and silicon substrate at elevated temperatures [2] and therefore degrade the dependability of associated electronic devices. This degradation mechanism results in device threshold voltage (V<sub>th</sub>) shift and loss of drive current (I<sub>on</sub>). The BTI effect is more severe for PMOSFETs than NMOSFETs due to the presence of holes in the PMOS inversion layer that are known to interact with the oxide states.

The BTI in PMOSFETs is referred to as negative BTI (NBTI) due to the negative gate-to-source voltage. NBTI has been shown to be the dominant effect in current process technologies. The NBTI is accelerated by elevated temperature and voltage levels and manifests itself as an increase in threshold voltage and a decrease of the drain current and transconductance [3].

In PMOSFETs, the channel holes interact with the passivated hydrogen bonds in the dielectric resulting into generation of traps and interface states [4]. This results into an increase in absolute threshold voltage (Vth) value and the effect increases at high temperatures. The introduction of new dielectric materials like high-k has enabled the BTI effect in NMOSFETs and is referred to as positive bias temperature instability (PBTI) due to the positive gate-to-source voltage.

NBTI degradation occurs all the time the transistor is turned on. However, it has been noticed that BTI degradation starts relaxing very quickly after the removal of the stress. This recovery process is caused by de-trapping of charges during subsequent removal of stress signal after a stress phase [5]. Recovery after NBTI or PBTI stress

in MOSFETs and its dependence on gate voltage, temperature and frequency of stress signal has been a hot topic of research in the past decade [6].

Currently, BTI is one of the most serious and important reliability concerns for both digital and analog circuits. At advanced technology nodes this effect is becoming an increasing challenge due to the reduced voltage headroom, high oxide electric fields resulting from non-constant field scaling, high temperatures due to higher power dissipation and the introduction of new dielectric material.

### 7.1.2 HCI-based aging faults

Hot Carrier Injection (HCI) is the result of defects being accumulated in the interface between the channel and gate and causes a gradual increase in threshold voltage and reduction in mobility. In HCI, electrons accelerated in the electric field of the channel collide with the gate oxide interface. The collision creates electron-hole pairs. Energetic electrons referred to as *hot* get trapped in the gate oxide layer, causing an increase in Vth. HCI degradation mainly affects NMOS transistors. Moreover, it is dependent on the drain current and predominantly occurs during switching [7].

### 7.1.3 Electro-migration

Electro-Migration (EM) is one of the causes of permanent failures of interconnect due to aggressive interconnect scaling and heavy current densities over a period of time.

It is caused by the movement in metal ions in conductors, and can eventually lead to the creation of open and short circuits [8].

At high current densities ( $\sim 10^6$  A/cm<sup>2</sup>), momentum transfer between electrons and metal atoms becomes important. The transfer, which is called the *electron-wind force*, results in a mass transport along the direction of electron movement.

Once the metal atoms are activated by the electron wind, they are subject to the electric fields that drive the current. Since the metal atoms are positively ionized, the electric field moves them against the electron wind once they have been activated. The interplay of these two phenomena determines the direction of net mass transfer. This mass transfer manifests itself in the movement of vacancies and interstitials. The vacancies coalesce into voids or micro-cracks, and interstitials become hillocks. The voids, in turn, decrease the cross-sectional area of the circuit metallization and increase the local resistance and current density at that point in the metallization. Both the increase in local current density and temperature, increase EM effects.

This positive feedback cycle can eventually lead to thermal runaway and catastrophic failure which will eventually degrade the system dependability.

### 7.1.4 Time-Dependent Dielectric Breakdown (TDDB) aging

Time Dependent Dielectric Breakdown (TDDB) is one of the major reasons of permanent failures in recent VLSI technologies. It results from a breakdown in the gate oxide [9]. It can lead to an increase in leakage current, or even in worst case causes failure in the transistors' ability to switch. Similar to NBTI, TDDB is driven by gate potential and occurs whenever the transistor is on.

The TDDB is a degradation phenomenon of SiO<sub>2</sub>, the thin insulating layer between the control "gate" and the conducting "channel" of the transistor. SiO<sub>2</sub> has a very high band gap (approximately 9eV) and has excellent scaling and process integration capabilities, which makes it the key factor in the success of MOS technology.

Although SiO<sub>2</sub> has many extraordinary properties, it is not perfect and suffers degradation caused by stress factors, such as a high oxide field. The exact physical mechanism of TDDB is still an open question.

The general belief is that TDDB of gate insulating material results from the cumulative effect of insulator trapped charge buildup during short-term and long-term high-field stress. High trapped-charge-induced local fields build up within the insulator creates defects in the volume of the oxide film. These defects accumulate with time and eventually reach a critical density, triggering a sudden loss of dielectric properties [9].

These defects also cause gate leakage and excess noise in MOSFETs. A surge of current produces a large localized rise in temperature, leading to permanent structural damage in the SiO2. One usually refers to *soft-breakdown* (SBD), which is reversible, and *hard-breakdown*, which results in permanent damage. Both will create failures in MOSFETs and hence the dependability of associated electronic systems will degrade.

# 7.2 Design and Validation of Embedded Instruments for Aging Measurements using the IEEE 1687 Standard

#### 7.2.1 The IEEE 1687 standard for fault monitoring

While the semiconductor technology development enables integrated circuits (ICs) with increasing transistor count and decreasing features sizes, it has become crucial to address reliability to handle errors that occur when the IC is in operation [10]. A straightforward scheme to detect and handle such errors is to make use of N-modular redundancy, where the system is replicated N times and the correct response is produced through majority voting. The drawbacks are that (1) already at design time the maximal number of errors, given by N must be known, (2) the voter has to be designed to handle errors, and (3) the system has to be replicated N times, which increases the hardware cost to unacceptable levels in many cases.

An alternative is to embed on-chip instruments capable of detecting errors, and connect the instruments to a fault management that makes decisions based on the collected error statuses. The fault management can be implemented in an on-chip or off-chip processor. To avoid that the network connecting the instruments and the fault management become the bottle-neck, the network must be designed such that the time

(latency) from when instruments detect errors and the fault management solution gets aware of the errors is small and deterministic. A small time is needed such that the network does not become the bottle-neck and a deterministic time is important to make the system predictable; the time should not vary significantly, for example due to a high number of concurrent errors.

A network for fault monitoring can make use of the functional network or make use of a stand-alone network. The advantage of reusing the functional network is that the existing network is reused. Hence, there is no additional hardware cost. The drawback is that adding traffic to transport error information may impact the performance of the system. It is also difficult at design time to know the amount of traffic information that is to be generated from errors as the traffic depends on how the errors occur. This might reduce predictability. To be on the safe-side, the network might be over-designed to ensure that performance is kept high. This is however costly. The advantage of a standalone network is that it does not impact the performance of the system. A stand- alone network adds hardware cost, if it is added only for fault management. However, most ICs have stand-alone networks, such as IEEE 1149.1 or IEEE 1687, to enable test, diagnosis, configuration, etc., which makes it attractive to *reusing* such network for error handling during operation.

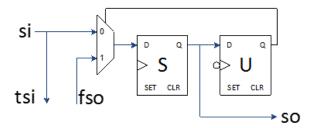

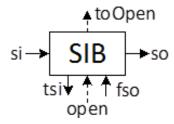

The key feature of IEEE 1687 networks is the reconfigurability, i.e. the possibility to switch segments of the network on and off the JTAG scan-path. One way to add such reconfigurability is by using SIBs. Figure 1 shows a simplified schematic of a (possible implementation of a) SIB, in which select and control signals (namely, capture, shift, and update) are not shown.

The SIB has a shift (S) flip-flop, an update (U) flip-flop, and a two-input scan multiplexer. A key feature in IEEE 1687 is the programming of the SIBs which is done at the same time as data is shifted through the network. SIBs in the network are programmed by shifting a bit into their S flip-flop and latching that bit into the parallel U flip-flop.

Figure 1. A simplified schematic of a SIB

If the latched bit is a "0", the SIB is closed and the scan-path is from the si (scan-in) terminal, to the so (scan-out) terminal via the S flip- flop, bypassing the segment between the tsi (to scan-in) and fso (from scan-out) terminals.

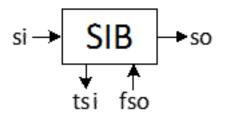

If, on the other hand, the latched bit is a "1", the SIB is open and the scan-path includes the segment connected between tsi and fso terminals of the SIB, referred to as the hierarchical port of SIB in this paper. The symbol shown in Figure 2 will be used in the rest of this paper to represent the SIB.

Figure 2. The symbol used for a SIB

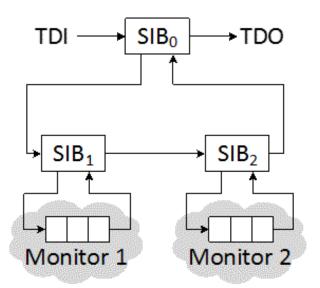

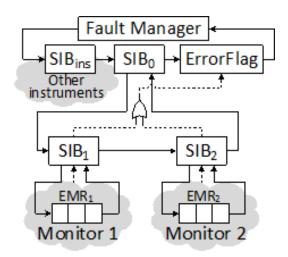

Using SIBs makes it possible to design hierarchical IEEE 1687 networks. Figure 3 shows a hierarchical IEEE 1687 network consisting of three SIBs and two 3-bit instrument shift-registers, named Monitor 1 and Monitor 2. To access the network via

Figure 3. Example of hierarchical IEEE 1687 network with two instruments and three SIBs

the JTAG TAP [11], the first hierarchical level of the network (SIB<sub>0</sub> in this example) is connected as a custom test data register (TDR) between the test-data-in (TDI) and test- data-out (TDO) terminals of the JTAG TAP. In the network shown in Figure 3, initially, only SIB<sub>0</sub> is in the active scan-path. To access e.g. Monitor 1, SIB<sub>0</sub> should be programmed to be open, which requires going through Shift and Update states of the JTAG TAP finite state machine (FSM), referred to as capture-shift-update (CSU) cycles. Next, SIB<sub>1</sub> should be opened while keeping SIB<sub>0</sub> open and SIB<sub>2</sub> closed, which requires performing another CSU. At this point, the register for Monitor 1 is placed in the scan-path and can be read from or written to.

It can be seen from this example that accessing instruments in an IEEE 1687 network produces two types of overhead: (1) the clock cycles needed to operate the JTAG FSM and (2) the clock cycles needed to shift SIB programming data.

It has been shown that the JTAG TAP FSM overhead is negligible compared to the SIB programming overhead [12], and that using a hierarchical design can reduce the SIB programming overhead significantly [13]. Other issues with regard to IEEE 1687

are related to timing problems in terms of synchronization and interrupts; they will be discussed later.

### 8 State-of-the-art

The major mechanisms of aging have not changed recently. As plots from NASA show, new technology nodes sometimes make some aging mechanisms more dominant than the previous node. Some models, like e.g. for NBTI, get more sophisticated, and match better with recent advanced measurements.

With technology scaling, the deviation between predicted path delay after synthesis and actual path delay on silicon increases due to aging and process variation. In digital chips, an increased delay is the major result of aging mechanisms, more specifically resulting from NBTI, currently.

As a second trend, the usage of on-chip measurement (EI) architectures have become more prevalent due to their higher accuracy and lower cost compared to using external expensive measurement devices. Hence, the focus will be on these.

Within BASTION, a strong emphasis has been placed to access the embedded instruments via the emerging IEEE 1687 standard (IJTAG). This includes start, stop, reconfiguration etc., and measurement data transfer. However, the usage of this standard brings also a number of important issues, like triggering, calibration etc. which will also be treated.

### 8.1 Aging Faults resulting in delays and embedded instruments

One effective approach to measure aging of a digital circuit, resulting from the mechanisms discussed in the previous part (more specifically NBTI), is by measuring its *delay*. There are several approaches toward measuring path delay by using dedicated measurement circuits such as ring oscillator (RO), time-to-digital converter (TDC), and tunable replica circuits (TRC). They will be briefly discussed subsequently.

The ring-oscillator-based architecture can be used more efficiently for path delay measurement by making the path-under-test (PUT) a part of oscillator. The ring oscillator consists of an odd number of inverters, connected into a ring. The ring oscillator frequency can be monitored continuously and any degradation in frequency with time can be attributed to device aging affects.

In [14], the author proposed an on-die aging monitor with the combination of symmetric and asymmetric ring oscillator which can measure both BTI and HCI. Their measurement results of a test chip fabricated in 16nm Fin-FET shows that HCI is almost half the percentage of all aging factors in an asymmetric ring oscillator and PBTI degradation is around 1/10 of the NBTI contribution.

Ring-oscillator based test structures that can separately measure the NBTI and PBTI degradation effects in digital circuits have been presented in [15] for high-k

metal gate devices. To decouple the impact of BTI and HCI effects in RO degradation, a novel RO test structure has been proposed in [16].

Although, ROs can simply be used as aging and frequency degradation measurement, however, it has some disadvantage. It is susceptible to self-heating, because of dynamic power dissipation. In addition, it can only distinguish the average delay, not the difference in propagation delay between falling and rising transitions.

A Time-to-Digital Converter (TDC) is a popular on-chip delay measurement circuit. It measures the time interval between two transitional signals. It is typically constructed from registers and delay elements and, like ring oscillators, can be used to measure the effect of process, temperature and voltage variation and aging degradation.

However, as the TDC is an on-chip circuit, it suffers from both process variation and aging effects. Hence, periodical calibration is required to guarantee the accuracy of the delay measurement. A low-area calibration technique for TDCs has been presented in [17]. A TDC circuit allows to accurately measuring its own delay, or the delay of a CUT. The primary limitation is the difficulty in the generating the start and stop measurement signals which must have identical skew.

A Tunable Replica Circuit (TRC) is another method for detecting (aging) errors due to voltage and delay degradation. Process variations and aging affects replicas in a similar way to the critical path. However, the random component of process variation will result in differences between the TRC and the actual critical path [18].

The major drawbacks of TRCs are the complex tuning process and the capability of detecting only the worst-case delay path.

Another approach towards measuring the aging effect is slack monitors accompanied by a guard-band. Most of the aging faults increase delay of transistors and connections. In a synchronous system, a delay increment can result in timing failure. Timing failure occurs when the delayed data does not meet a flip-flop's setup requirement and has a late transition near to the clock edge. Therefore, online delay (or slack) monitoring in an integrated circuit is a suitable metric for measuring the aging of synchronous circuits [18, 19]. The timing slack or guard-band is defined as the delay, between the data arrival time and active edge of the clock, minus the flip-flop setup time. The guard-band assignment is done at the pre-silicon design phase based on the target clock frequency.

In [20]20], the authors have proposed a timing-slack monitoring methodology of inserting monitors at both path ending nets and path intermediate nets. Their experimental results on commercial processors show that with 5% additional timing margin, their methodology can reduce the number of monitors down to 6-8% compared to the number of monitors inserted at the path ending pins.

Recently, a timing slack monitor as well as a sensor insertion flow has been presented in [21]. The output of their slack monitor can be recovered using the IJTAG standard.

### 8.2 Design & Validation of Embedded Instruments using IEEE 1687 standard

Within the BASTION project, a strong emphasis has been placed to access the embedded instruments via the emerging IEEE 1687 standard (IJTAG). This includes start, stop, reconfiguration etc., and measurement data transfer. However, the usage of this standard brings also a number of important issues, like triggering, calibration, fault handling etc. which will also be treated.

### 8.2.1 Embedded Instruments Based on Existing Built-in Self-test

Modern SoCs contain various types of components like digital logic, different types of memories as well as various sorts of mixed-signal components. Traditionally these components are only tested during the production test using dedicated test equipment. Driven by customer demands and functional safety requirements, e.g. ISO26262 for the automotive domain, there is more and more the request to perform the device-level testing not only during production, but also in the application. This in-system test cannot use the typical ATE of the production test, but has to rely on the very limited test resources available in the functional system. Therefore, BIST solutions are integrated into the IC allowing the test of chip-level components without the need of additional tester resources.

For embedded memories dedicated BIST hardware [22] is often already implemented for the production test and can be easily reused in the system. For digital logic built-in self-test approaches are known since years.

A typical Logic BIST (LBIST) solution is often based on the STUMPS [23] approach. It uses a pseudo-random pattern generator (PRPG) providing on-chip test data to operate the scan chains of the production test while the test responses are evaluated using a multiple-input signature register (MISR). The LBIST is a feature mainly dedicated to the in-system test, as the reachable test coverage is usually not sufficient to achieve the high quality goals of the production test.

For the emerging amount of *mixed-signal* components the traditional test is performed using functional test sequences and there is usually no structural test solution available. Built-in self-test solutions are also requested and desired for the mixed signal components. Contrary to digital logic however no standard solution exists that covers a range of different mixed-signal components.

### 8.2.2 The standard IEEE 1687 for fault monitoring

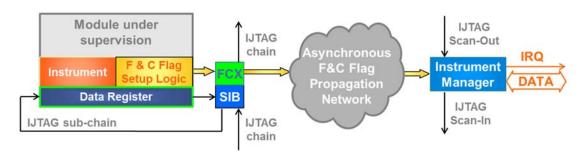

There have been a number of works addressing the network for transporting monitoring data (for transient faults, timing errors, power and temperature estimation, etc.) using a dedicated infrastructure [24]–[26]. The work in [24] stands out as it relies on reusing the existing IEEE 1687 Standard (IJTAG) network [27] for the monitoring purposes. An advantage of a making use of an existing standard is the availability of automation tools (e.g., for insertion and test of the network [13]).

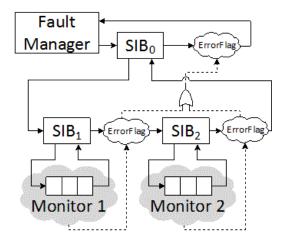

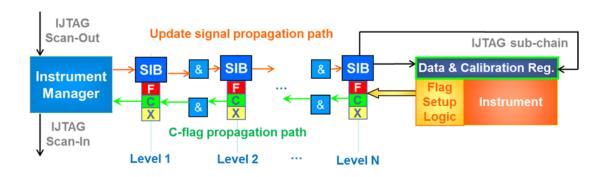

Such hierarchical networks have been used for fault monitoring purposes in fault management schemes proposed by Jutman et al. [25] and by Petersen et al. [26]. The fault management schemes in [25] and [26] make use of an IEEE 1687 network connecting fault monitoring instruments to the fault manager, along with an error propagation network. For example, a simplified representation of the hierarchical network used in [25] is shown in Figure 4.

The key to speed up the error detection in the previous works [25, 26] is the added error-propagation network (marked by the dashed line in Figure 4 in the case of [25]), in which error detection information is immediately reported to the 'ErrorFlag' at the highest hierarchical level. The advantage is that by reading the 'ErrorFlag' the fault management gets informed if there is any error in the system without having to traverse the complete network. To guide error localization, both papers [25] and [26] added ErrorFlags at every hierarchical level. The drawback is that the time for error localization increases dramatically.

In the work by Jutman et al. timing analysis is provided, which is lacking in the work by Petersen et al. A common drawback in the works of both is that error localization, finding where the error is, involves a number of CSUs, which increases the fault localization time.

Figure 4. Illustration of the basic ideas in [25] and [26]

Other issues with regard to IEEE 1687 are related to specific timing problems in terms of synchronization and interrupts; they will be discussed later in chapter 9.

# 9 Design and Validation of Embedded Instruments for Aging Measurements Using IEEE 1687

In this chapter, the research activities of the BASTION consortium are presented regarding the design and validation of several embedded instruments related to aging using the IEEE standard 1687.

### 9.1 Aging Measurements

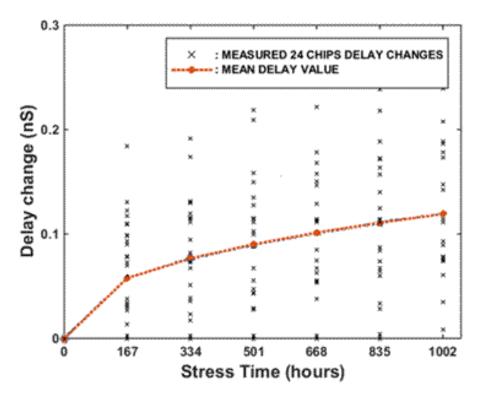

To model an aging fault, like e.g. NBTI, the effect of aging on the performance of twenty four Xentium processors [28] under harsh environmental conditions was measured. Figure 5 shows the delay degradation with the operation time. The total time of the (voltage, temperature) stress experiments was more than 2000 hours, but only the first 1000 hours have been plotted.

The mean path-delay values of the processors are drawn by the dashed line. Our measurements confirmed that there is a direct correlation between (NBTI) aging and (delay) performance degradation. Also our NBTI and HCI monitors were simultaneously stressed, evaluated and compared with delay measurements.

Figure 5. Result of actual delay measurements for 24 Xentium processors

#### 9.2 Test Generation and Detection Embedded Instruments

A positive timing slack indicates that a circuit (e.g. a Xentium processor) is operating safely, with a margin by which the delay can increase before causing failure. Timing slack is an excellent measure for the health of a circuit. Measuring timing slack can allow an early warning of deterioration and trigging pre-emptive actions to avoid failure because of aging. A small or negative quantity of slack is a concern, indicating the circuit is close to, or beyond the point of failure.

It has been shown by experimental results that NBTI is the primary factor leads to timing degradation in current technologies [29]. NBTI has been shown to cause shifts in threshold voltage of up to 50mV over an operating lifespan of 10 years in 65 nm technologies. This translates to more than 20% deterioration in circuit operating speed [30]. To model the delay induced by aging fault (NBTI), the Vth of all PMOSs in the target circuit have been increased by 50mV in our Cadence simulator.

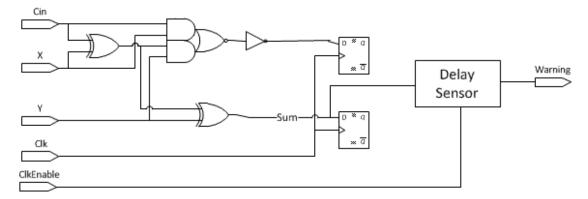

Figure 6. An example of combinational target circuit and delay sensor

To evaluate the proposed delay sensor, a static CMOS circuit in 45nm CMOS technology has been used. The delay sensor monitors output of the circuit before it becomes captured by a flip-flop. The circuit operates at a clock frequency of 2.5GHz. The logic scheme is depicted in Figure 6; its transistor implementation is provided at a lower hierarchical level, but is not shown here for simplicity.

## 9.3 Design and Simulation Results of Embedded Instruments

An online slack measurement sensor to measure the timing slack (delay-related) at critical nodes in the circuit has been designed to directly measure the effects of delay variation resulting from NBTI aging.

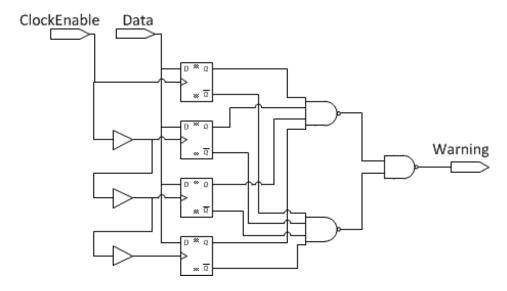

The proposed sensor provides a warning if a specified guard-band (safety margin) has been violated, indicating an impending timing failure. It consists of four D-flipflops (see Figure 7). Each flip-flop receives its clock from the previous output of an inverter, except the first flipflop in which case its clock is connected to the ClockEnable line. Hence, each D-flipflop clock is delayed by the delay of an inverter. All D-inputs are connected to the Data line.

If there is not any late transition in the data line, then all flip-flops capture the same value. In the case the target circuit (see Figure 6) delay is sufficiently increased, the first flipflop will latch the previous value of data before the transition; comparison of the outputs of *all* the flipflops by the NAND gates will then indicate a guard-band violation. The ClockEnable signal determines the guard-band window.

Figure 7. The proposed slack monitor

Figure 8 shows the Cadence Virtuoso simulation environment. At the top, a part of the critical path can be seen of the target circuit (see also Figure 6), and at the bottom the proposed slack/delay monitor can be seen.

Figure 8. Schematic of the proposed delay monitor

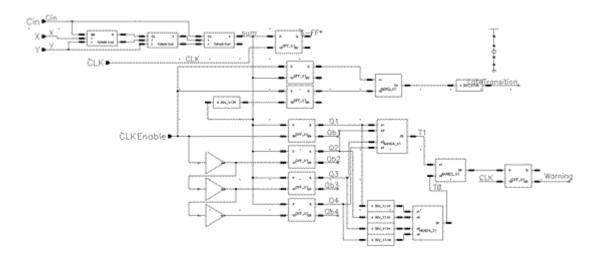

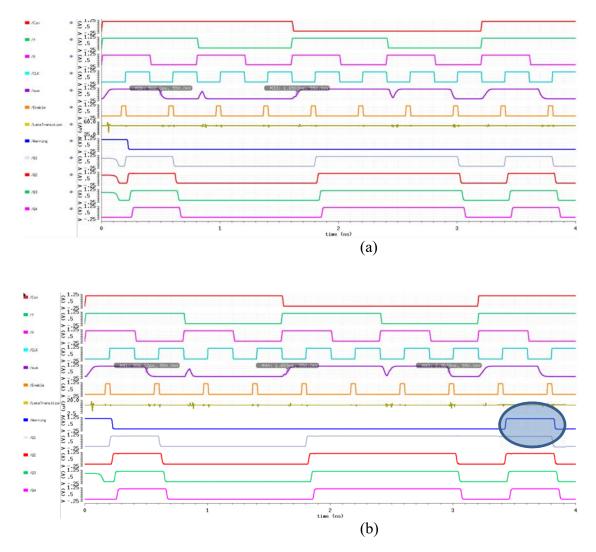

Figure 9 shows the Cadence Virtuoso simulation results of a combinational circuit where its transistors are subjected to *aging* faults. The output (logic) behavior of the circuit as well as the proposed delay aging sensor has been evaluated.

In Figure 9a, the input signals (Cin, X, Y), clock of system (CLK), output signal (Sum), guard-band signal (ClockEnable), output signal of the proposed sensor (warning) and the outputs of the D-flipflops (Q1, Q2, Q3, Q4) are shown from top to down.

Figure 9a shows the simulation results of the target circuit before aging. In this case, there is not any timing (guard-band) violation detected by the monitor, as to be expected.

Figure 9b shows the simulation results of the circuit *after* aging. As it can be seen, the proposed sensor has detected a timing violation. The warning signal indicates that there is a timing violation. After timing violation detection, a warning flag is raised to enable the measurement of the path's slack which is captured in the D-flipflops using the iJTAG standard IEEE 1687 [31].

Figure 9. Simulated waveform results of the proposed slack monitor (a) before NBTI aging and (b) after NBTI aging

# 9.4 Re-Use of Chip-level Embedded Instruments to detect Aging Defects

As ageing effects are considered to become more important, the available self-test components can be reused to check if the device is affected by aging. The goal is to check the overall chip area including all major functional components. The identified aging effects are often affecting the device timing. Therefore, it is essential to target not only static defects, but also to enable the in-system test for dynamic fails.

The (Memory–BIST) MBIST for the memories is usually performed using the functional frequency allowing the detection of both static and dynamic defects. The initial (Logic-BIST) LBIST solutions have been mainly focused on stuck-at defects and have now to be enhanced to perform also an at-speed test. The main problem of the at-speed LBIST is not only the provision of the required clocks with the target frequencies, but also the handling of timing exceptions.

Due to the MISR being used for the on-chip test data compression, flip-flops capturing unreliable data from non-functional paths etc. would prevent the LBIST operation as the signature would be corrupted. Therefore, it is essential to prevent timing exceptions wherever possible.

One approach is the introduction of a hierarchical LBIST architecture. When testing smaller parts of the overall design with separate LBISTs, typically LBIST needs to address fewer clock domains and fewer frequencies. In the best case the design can be partitioned in a way that each LBIST needs to be run only with a single functional clock frequency in the capture phase. As most timing exceptions are usually related to the inter-domain logic between different clock domains, the hierarchical test approach significantly eases the problem.

A hierarchical LBIST solution does not only simplify the handling of timing exceptions, but can also be very beneficial for the localization of defects and the related error handling. In addition, the hierarchical test helps also to deal with test-power issues. When timing exceptions can neither be prevented by suitable test partitioning nor can be fixed by over-constraining the design, the paths not fulfilling the timing need to be broken by design measures during the LBIST execution to prevent unreliable capture.

There is no general BIST solution for the large variety of mixed-signal circuits. However, different approaches exist for some typical components used in many designs. Analog-to-Digital Converters (ADCs) are an essential part of many SoCs. They digitize analog values e.g. coming from various sensors and allow a digital post-processing of the analog measurements.

One approach to monitor aging defects would be to measure a parameter affected by ageing. As an example in [32] the authors suggest measuring NBTI degradation of one of the ADC sub-circuits.

Unfortunately, for production designs the overall functionality has to be guaranteed to the customer. The ADC-BIST circuitry, being on-chip, is not only used for production test purposes, but is also triggered and executed by the system software. This is required in order to ensure functional safety. To allow the reuse of the BIST

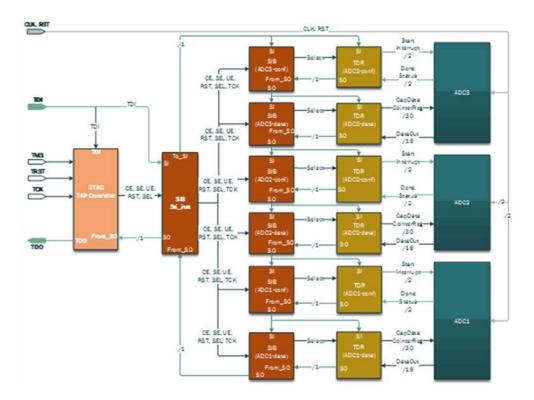

for monitoring ageing defects, the ADC-BIST has been enhanced with a dedicated digital interface allowing the integration into an IJTAG network.

Despite its analog behavior the main purpose of the ADC-BIST is not to measure the ageing of *one* analog parameter. Instead the BIST is executed to check whether the overall ADC functionality is still within the specified limits. To identify ageing effects before the circuit fails it is possible to run the ADC-BIST with stricter limits than functionally required. Another approach driven from safety requirements is to use one or more spare ADCs in the design. The spare ADC is tested while the others are functionally used. After a certain time the design is reconfigured and the ADCs switch roles. The spare ADC becomes functional and one of the other ADCs is tested. Eventually every ADC is tested in a round robin manner.

In case one of the ADCs fails during BIST execution, the system would still be fully functional. Nevertheless, this would be a clear indication that also the remaining ADCs are likely to fail soon and error handling measures need to be performed.

### 9.4.1 Experimental Results for IJTAG Controlled ADC-BIST

The IJTAG controlled ADC-BIST solution has been tried for a small test case design. Each ADC-BIST uses the functional interface as shown in Table 1 and Table 2

Table 1. Inputs of the ADC-BIST instance

| Inputs     |                                                          |

|------------|----------------------------------------------------------|

| Clk        | Clock                                                    |

| Rst        | Asynchronous reset                                       |

| Interrupt  | Synchronous reset                                        |

| Start      | Start signal for BIST execution                          |

| capData    | Configuration value for capacitor to be charged, 14 bits |

| counterRef | Expected reference value for BIST counter value, 16 bits |

Table 2. Outputs of the ADC-BIST instance

| Outputs |                                                             |

|---------|-------------------------------------------------------------|

| Done    | Done signal indicating end of the BIST operation            |

| Status  | BIST result status: 1 test completed successfully, 0 failed |

| DataOut | BIST counter value for read-out, 16 bit                     |

For the evaluation three ADC-BIST instances have been used. In the assumed scenario always two ADCs are operated in functional mode while the third ADC is tested by the BIST. After one ADC has been completely tested, the circuit is reconfigured and the tested ADC becomes functional allowing the test of the next ADC instance.

For each ADC, the BIST verifies the correct operation of the ADC's capacitor network. This network realizes several capacitance configurations that are tested individually by the BIST engine. The result of each test is quantified by a counter value.

This value is to be compared to a reference (e.g. determined when characterizing the ADC during production test) to check if the respective capacitance configuration is operational. When starting a single test run, both the capacitance configuration to be tested and the expected reference value have to be provided to the BIST controller. Then the test will run for a certain time which is – for an operational capacitance configuration – proportional to the reference counter value. After the test is finished, the BIST's done bit is set to high, and the status bit indicates if the counter value indeed matches the expected reference.

The algorithm in Figure 10 describes the overall flow for testing the three ADCs in a round robin manner. The configurations of the capacitance network along with the respective reference counter values are expected to be available as input to the algorithm.

Additionally a dedicated debug mode can be enabled. In this mode the debug information stored in 'DataOut' is retrieved from the BIST. This information is only relevant for general diagnostics and may be ignored for regular production or in-field test.

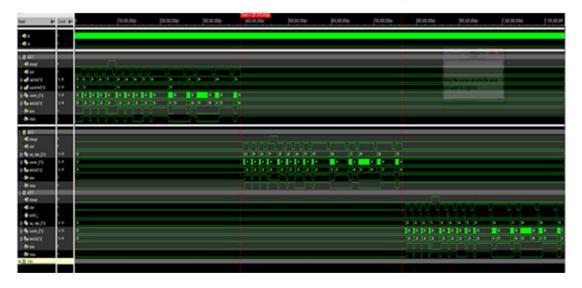

The simulation waveform of the relevant BIST signals is depicted in Figure 11. In particular this figure illustrates, that the three ADCs are indeed tested one after the other.

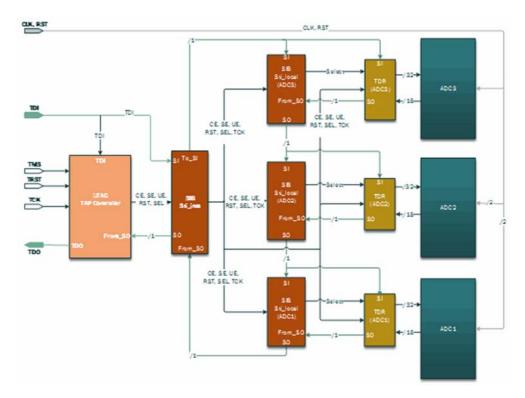

The default IJTAG network for controlling the ADC-BIST is shown in Figure 12. For each ADC a test register of 32 bits is used. From this test register the BIST is configured and started. The 32 bits controlling the ADC-BIST are: 14 bits BIST configuration, 16 bits expected counter value, 1 bit interrupt, 1 bit BIST start. The same test register is also used to capture the test responses. The test results consist of 18 bits: 1 bit BIST done, 1 bit BIST status, 16 bits actual BIST counter result.

```

// start of test

// initialize data for each ADC: 14 pairs of capacitance configuration, and reference value

\mathsf{data} = (\ \mathsf{adc_1} \ \boldsymbol{\rightarrow} \ \{\ (\mathsf{capCfg_{1,1}},\ \mathsf{refDat_{1,1}}),\ ...\ (\mathsf{capCfg_{1,14}},\ \mathsf{refDat_{1,14}})\ \},

adc_3 \rightarrow \{ (capCfg_{3,1}, refDat_{3,1}), ... (capCfg_{3,14}, refDat_{3,14}) \} );

// reset design

reset();

// wait for 10 clock cycles (functional clock frequency)

wait(10);

start:=1, // initiates BIST run

capData:=capCfa, // capacitance configuration

counterRef:=refDat; // expected reference value

// calculate strobe time based on reference value

strobe:=getWaitCycles(refDat);

// wait for strobe clock cycles (functional clock frequency)

| | wait(strobe);

in debug mode actual counter value is read from BIST

if ( debug ) then | | // read status of BIST, and counter value from current ADC <u>adc.</u>

// process testDone, testStatus, and testData

else

// read status of BIST from current ADC adc.

iJTAG read from adc.: testDone:=done, // signals end of test

testStatus:=status; // test result

if ( not ( testDone and testStatus ) ) then

| ___// test failed

| | ...

end

end

// wait for 10 clock cycles (functional clock frequency)

wait(10);

end

end

// end of test

```

Figure 10. The flow for testing three ADCs

Figure 11. Simulation waveform testing one ADC after the other

To set up the BIST of a single ADC, 36 clock cycles are required in total. This includes 4 cycles to configure the SIBs and 32 cycles to shift the data into the respective TDR. The additional cycles needed for setting up the JTAG TAP are not considered. Similarly 36 cycles are needed if the result of a BIST-run is to be read from a single ADC.

Figure 12. Default IJTAG network controlling 3 ADC-BIST instances

With this network configuration, the ADC-BIST can be fully controlled from off-chip resources. However for production or in-field test the IJTAG configuration can be further optimized. Both applications may only rely on the status of the BIST run, and typically do not require the debug information stored in 'DataOut'. Yet with the default network configuration, 'DataOut' is always retrieved as well, contributing to the 36 shift cycles. As the ADC-BIST runs at the functional clock frequency, the overall test time is dominated by the slow shift cycles of the IJTAG network. Consequently reducing the number of shift cycles may immediately reduce the test execution time.

The IJTAG network in Figure 13 is optimized with respect to production or in-field test. In the optimized network, the single-bit control and status signals are separated from the multi-bit configuration and information signals. For each ADC 'start', 'interrupt', 'done', and 'status' are catered by the same TDR. The signals for 'capData', 'counterRef', and 'DataOut' are joined in a separate TDR.

As a result the number of shift cycles needed to set up a single test run increases slightly to 39. The same number of cycles is needed to retrieve the status of a BIST operation, and the debug information. However, when only reading the status of the BIST run, just 9 shift cycles are required. With this IJTAG network configuration the

ADC-BIST can be controlled efficiently from off-chip resources to enable monitoring of ageing defects.

Figure 13. Optimized IJTAG network controlling 3 ADC-BIST instances

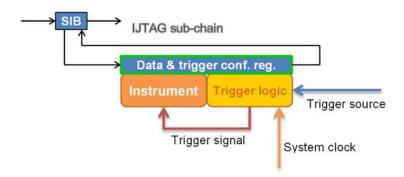

# 9.5 Access of Embedded Instruments via Software in Operational Phase

This section will first deal with issues related to the access options of EIs in the operational phase of a system. In the second part, an example of a digital EI, the error checker, will be introduced as well as a complete flow for implementation and validation.

### 9.5.1 Access of Embedded Instruments

During the operational phase, test is often managed by the operating system (if any exists in the considered system) or by any high-level supervisor (e.g., acting as a process scheduler)<sup>1</sup>.

When considering test, this entity is in charge of different tasks, depending on the specific test solutions which are adopted. Often, they include first of all the access to some instruments existing on board each device, triggering them to provide values (if required), reading, and processing them. Depending on when the test is scheduled, different constraints exist for these activities. BASTION researchers have investigated this and as a result an overview in the following the most common scenarios will be given:

- The test is performed at power-on. This case is common when the system under test is used for short-term missions and the required level of safety is medium-low. For example, this is the solution adopted for several sub-systems on board cars and aircrafts. In this case, the software in charge of performing the test can access and interact with each device in a relatively flexible way, since the application code is still not running. The duration of the test is also less critical in this case with respect to the following ones, although some constraints clearly exist anyway. In some cases, in the test at power-on the test procedure is directly triggered by the reset circuitry.

- The test is performed in the situation that some specific condition is matched (e.g. some error is detected). In this case, the application is temporarily suspended. Hence, the test task has some freedom in this case using the system resources which are not functionally used. However, the status of the system should be kept unchanged as much as possible, thus allowing the normal operation conditions to resume as quickly as possible, if the test does not detect any fault. Similarly, the test duration is an important parameter, although not as crucial as in the following scenario.

- The test is periodically performed, using the *idle* periods of the application. This case is common when the system under test is used for long-term missions or the required level of safety is high. Obviously, the key condition for applying this solution is that the application running on the system has some periodic idle times whose duration is sufficiently long to allow the test task to take the control of the system, run the test, gather some results, and restore the previous status of the system itself. This condition is often verified in safety-critical systems, where often the application code simply corresponds to a single task performing sensor acquisition, basic processing, and actuator driving. Typically, this task is iteratively triggered by a scheduler. In this scenario, the test task can be triggered by the scheduler as soon as the application task ends. By the end of the idle slot, the test task must guarantee that all test related activities are concluded, their (final or intermediate) results

<sup>&</sup>lt;sup>1</sup> We will not consider here the special case, in which a system has been already labeled as faulty, and a test is performed to more exactly identify the failing component. This scenario is rather different than then ones considered here, since in this case the system is not operational during the test, and the test is often performed in a workshop, possibly resorting to some kind of tester.

gathered, and the status of the system is back to the initial one. Moreover, the test task is often limited by a set of constraints related for example to the amount and location of the memory it can use (which must be compatible with the application constraints).

Access to the instruments can be done in different ways, which are summarized in the following:

- The instruments are accessible as special processor registers. This is for example the solution which is used in some processors to access the performance counters introduced to support silicon debug, software debug and performance evaluation. This mechanism is very flexible and powerful, but requires a strong integration in the processor architecture, and can only be adopted in the case of processors.

- The instruments are accessible as peripheral modules (e.g., using the memory-mapped approach). In this case the software accesses to them following the same scheme used for any other I/O peripheral. In this case, peripherals may also be associated to an interrupt, which is triggered in special conditions (e.g., when unexpected values are read), thus allowing the software to access them only when required. This special case can be effectively used in the frame of the second scenario listed before.

- The instruments are accessible using the IEEE 1149.1 TAP. The standard IEEE 1687 may be used on top of that to make the access more flexible. This solution has the advantage that the access mechanism is completely independent on the functional specifications of the device, but requires the software to be able to access the TAP during the test. If an external test manager exists, this could be a suitable solution to follow.

#### 9.5.2 Error Checkers Validation & Minimization

In BASTION, an automated framework for design, validation and minimisation of embedded error checkers has been developed. The error checkers under consideration are targeting "digital" faults within the system, which may be caused because of wear out due to ageing or by soft errors or electromagnetic compatibility issues. Figure 14. Evaluation and minimization flow for checkerspresents the evaluation and minimization flow for the checkers.

The flow starts with synthesising the checkers from a set of combinational assertions. Thereafter, a pseudo-combinational circuit will be extracted from the circuit of the design under checking. The pseudo-combinational circuit is derived out of the original circuit by breaking the flip-flops and converting them to pseudo primary inputs and pseudo primary outputs. Note, that at this point additional checkers that also describe relations on the pseudo primary inputs/outputs may be added to the checker suite in order to increase the fault coverage.

Subsequently, the checker evaluation environment is created by generating exhaustive test stimuli for the extracted pseudo-combinational circuit. These stimuli are fed through a filtering tool that selects only the stimuli that correspond to functionally valid inputs of the circuit. As a result, the complete valid set of input stimuli that will serve as the environment for checker evaluation is obtained.

Figure 14. Evaluation and minimization flow for checkers

The obtained environment, pseudo-combinational circuit and synthesised checkers are applied to fault-free simulation. The simulation calculates fault-free values for all the lines within the circuit. Additionally, if any of the checkers fires during fault-free simulation it means a bug in the checker or an incorrect environment.

If none of the checkers is firing in the fault-free mode then checker evaluation will take place. The tool injects faults to all the lines within the circuit one-by-one and this step is repeated for each input vector. As a result, the overall fault detection capabilities for the set of checkers will be calculated. In addition, each individual checker will be weighted by summing up the total number of true detections by the checker.

Finally, the weighting information will be exploited in minimizing the number of checkers, eventually allowing outlining a trade-off between fault coverage and the area overhead due to the introduction of checker logic. The work presented in this subsection has been partly supported by the Horizon 2020 project IMMORTAL. Further details about the framework have been published in [33].

### 9.6 Handling Synchronization and Interrupts

In the parts of background and state-of-the-art in this deliverable, the status of the emerging standard IEEE 1687 has been presented and explained. In this section several issues will be discussed of *new* research that has been carried out in the area of self-reconfiguring networks related to IEEE 1687 for fault monitors.

### 9.6.1 Self-Reconfiguring Network

Below, the hardware structure is described of self-reconfiguring networks, as well as how to detect and localize errors in the proposed structure.

The basic idea in self-reconfiguration is that when a fault is detected by an (embedded) fault monitor, the corresponding error indication flag/register is automatically included in the active scan-path so that in the next shift-out phase, its contents can be immediately shifted out and analyzed. Such scheme improves the speed of fault localization via:

- (1) avoiding to open layers of hierarchy one layer at a time, and

- (2) using only one ErrorFlag register instead of placing multiple of such registers at every hierarchical level.

### 9.6.1.1 Hardware Structure

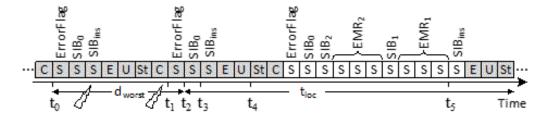

It is assumed that there is a hierarchical IEEE 1687 network interfacing all embedded instruments (test, debug, fault monitors, etc.) in a system to a Fault Manager, which has the purpose of detecting and localizing errors that may occur in different components of the system over time, such that it can initiate necessary fault-handling actions. The novelty of this work relies on the fact that the hierarchical IEEE 1687 has the feature of *self-reconfiguration*.

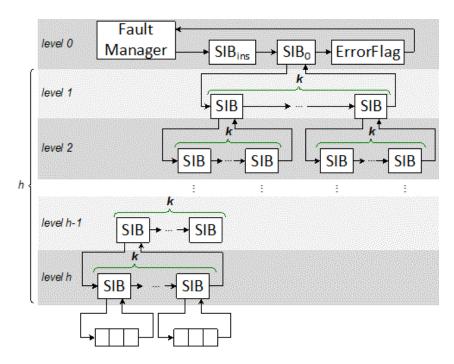

Among all the instruments, it is assumed that there is a set of fault monitoring instruments. At the top level of the hierarchical network, the fault monitoring instruments are connected through a dedicated SIB (see previous section of this deliverable), denoted with SIB<sub>0</sub>, while all the other instruments (test, debug, etc.) are connected through another SIB, denoted by SIB<sub>ins</sub>. The top level also includes a one-bit shift-register (ErrorFlag) to indicate if any errors are detected by any of the fault monitoring instruments.

It is further assumed that a fault monitoring instrument has a fault flag output terminal that is set to logic "1" in case a fault is detected. The fault flag stays active until it is acknowledged via a clear-flag input terminal. The fault flag signal will be used as an input to reconfigure the network, such that an access to the fault

monitoring instrument is enabled. Furthermore, the fault flag signal is propagated across the hierarchical levels and it is captured by the ErrorFlag register at the top level of the hierarchical network.

Additionally, it is assumed that a fault-monitoring instrument produces an error-code which is parallel-loaded during the capture phase into an Error-code \ Mask shift-Register (EMR) interfacing the instrument to the IEEE 1687 network. An EMR is assumed to have capture and update features (similar to standard JTAG TDRs) and it contains an error-code field (written by the *instrument*) and a mask field (written by the *Fault Manager*). Error masking is used to stop a permanent fault from constantly raising the fault flag. To be compliant with the IJTAG standard, error masking should be enabled by default at reset to disable self-reconfiguration of the network. In the case the EMR of a fault monitoring instrument is selected and data is shifted through it, the clear flag is asserted to indicate that the fault from the fault monitor has been acknowledged.

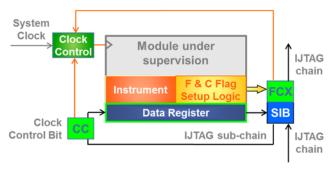

To enable the feature of self-reconfiguration, we propose a modified SIB, which is the core component in a self-reconfiguring network. The proposed modified SIB can be opened asynchronously by means of an additional terminal. The symbol shown in Figure 15. Symbol of the modified SIB will be used to represent the *modified* SIB. In a following section, we will detail the circuitry of the proposed modified SIB.

Figure 15. Symbol of the modified SIB

All fault monitoring instruments in the network are connected to the top-level SIB<sub>0</sub> through a network of modified SIBs. The main difference between a regular SIB and a modified SIB is the pair of terminals "open" and "toOpen". The "open" terminal of a modified SIB is connected either to (1) the fault flag of the monitoring instrument or (2) the OR-ed output of the "toOpen" terminals of all modified SIBs attached to it (placed one hierarchical level below). If the "open" terminal is asserted (pulled high), it changes the state of the SIB to open only if the SIB is not already part of an activescan path. This signal is gated using (an inverted copy of) the select signal to make sure that the state of the SIB does not change (from close to open) when it is part of an active scan-path (e.g., when the Fault Manager is accessing the network). This implies that the fault flag signal should be kept active by the monitor circuitry until acknowledged by the Fault Manager (as discussed above). The "toOpen" terminal propagates the gated open signal to the SIBs in the higher levels of hierarchy. The ErrorFlag register in the top level receives a signal which is obtained by OR-ing the "toOpen" signals from all the modified SIBs directly attached to SIB<sub>0</sub>. It should be noted that the suggested modification does not change the behavior of the SIB from the IEEE 1687 standard point of view.

A requirement for the modified SIB (as well as for SIB<sub>0</sub> and SIB<sub>ins</sub>) is to have its shift (S) flipflop placed after the hierarchical mux port (similar to what is shown in Figure 2). Such placement, while being fully standard compliant, ensures that during shifting, the state of the SIB is always shifted-out first. This is required by the fault-localization algorithm to recognize the current configuration of the network.

Figure 16 shows an example of a self-reconfiguring network with two monitoring instruments. The 3-bit registers which interface the two modified SIBs to the instruments follow our assumptions mentioned in the beginning of this section.

Figure 16. An example of a self-reconfiguring network (dashed line represents the fault propagation network)

The Fault Manager constantly checks the content of the Error-Flag register. The ErrorFlag captures, during Capture phase, the faults through the propagated fault flag (i.e. the ORed "toOpen" signals from SIB<sub>1</sub> and SIB<sub>2</sub>). During the Shift phase, the Fault Manager can observe the latest value captured by the ErrorFlag register. A captured value "1" indicates that at least one monitoring instrument has raised an error flag and therefore, the localization phase should be launched. Note that if the fault flag has managed to propagate to the ErrorFlag register, all the modified SIBs on the path from the fault monitor raising the flag to the top level SIB<sub>0</sub> will be properly configured.

### 9.6.1.2 Fault Detection and Localization Method

Now, the fault detection and localization method will be explained using the example network shown in Figure 16 and the timelines shown in Figure 17 up to Figure 20.

The following scenarios are being considered:

- (1) no error has occurred,

- (2) an error occurs when the Fault Manager is not localizing another fault,

- (3) a fault occurs while the Fault Manager is localizing another fault, and

- (4) two faults occur in a short span of time when the Fault Manager is not localizing another fault.

For these scenarios, it is assumed that whenever a value is shifted out from the network, a zero is shifted in. The effect of this is that all open SIBs are always closed and all error-code registers are set to zero.

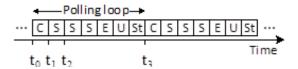

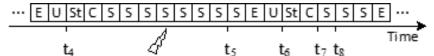

For the first (1) scenario, when no error is reported, the Fault Manager constantly checks the status of the system by polling the value captured by the ErrorFlag register. The Fault Manager does the polling by constantly looping through the Capture, Shift, Exit1, Update, and Select states in the DR branch of the TAP FSM. Since SIB<sub>0</sub> is closed when no errors are detected, the polling takes six test clock cycles (TCK), the interval between t<sub>0</sub> and t<sub>3</sub>, as two shifts are required: one for SIB<sub>0</sub> and one for ErrorFlag. This looping is illustrated in **Error! Reference source not found.**7.

Figure 17. Constant polling to check for faults (C: Capture, S: Shift, E: Exit, U: Update, St: Select)

The value of the fault flag is captured at  $t_1$  into ErrorFlag register and can be observed at  $t_2$ . The looping continues as long as the shifted out bit corresponding to the ErrorFlag register is a logic zero.

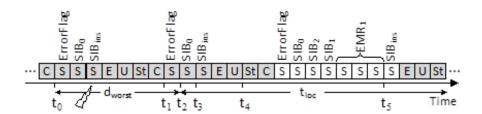

Figure 18. An error (lightning symbol) is detected and localized

For the second (2) scenario (see Figure 18), consider that a fault happens at the interval between t<sub>0</sub> and t<sub>1</sub> and is detected by Monitor 1. The reason this interval is chosen is that no matter when in this interval a fault occurs, it will not be captured until t<sub>1</sub> and will therefore not be detected until shifted out at t<sub>2</sub>. We refer to the interval between t<sub>0</sub> and t<sub>2</sub> as the *worst-case fault detection time* (if no other error is being localized) and refer to it as d<sub>worst</sub>. However, it can be seen that it will not take more than seven TCKs to detect a fault. At the moment this value shifts out at t<sub>2</sub> (which belongs to the ErrorFlag) it is a logic "1", and the localization procedure is launched by shifting a "1" into SIB<sub>0</sub> at t<sub>3</sub> which takes effect at the following Update phase (t<sub>4</sub>).

Once SIB<sub>0</sub> is open, as the rest of the network is already self-reconfigured, the Fault Manager starts shifting out data from the network (while shifting in zeros to reset the SIBs and error registers for the next round) to localize the fault, as follows:

The first two bits shifted out are the contents of ErrorFlag and SIB<sub>0</sub>. The third bit is the contents of SIB<sub>2</sub> for which a value of zero indicates that SIB<sub>2</sub> is closed and the fault is not reported from the network segment connected to the hierarchical port of SIB<sub>2</sub>. The next bit is the contents of SIB<sub>1</sub> which is "1" meaning that SIB<sub>1</sub> is open and the fault is reported from the segment connected to it i.e. Monitor 1 in this example. The last three bits following are the contents of the 3-bit error code register which interfaces Monitor 1 to the IJTAG network. At this point ( $t_5$ ), the error is localized and the error information is retrieved. In this work, we also include in the localization time ( $t_{loc}$ ) the next three TCKs needed to go back to the capture phase such that new faults can be detected. The total worst-case error localization time of a localization round, can then be written as:  $t_{worst} = d_{worst} + t_{loc}$ .

To also take the time from the fault-propagation network into account,  $d_{worst}$  is extended to also include the additional time from a fault-monitoring instrument signal until it reaches the ErrorFlag. This propagation delay is denoted by  $\delta$  and notice that if the fault monitor signals the error later than  $t_0$  -  $\delta$ , it is not captured at  $t_0$ . Therefore,  $d_{worst}$  is given as:  $t_2$  -  $t_0$  +  $\delta$  which is equal to  $(7/f_{TCK})$  +  $\delta$  where  $f_{TCK}$  is the maximum frequency that the JTAG TAP can be operated at.

For the third scenario, when an error happens while the Fault Manager is localizing a previous error, consider Figure 19 which is the continuation of the timeline shown in Figure 18 (at t4 in Figure 18). An error is detected and localized start at t4 in Figure 19.

A second error happens when the previous one is being localized.

Figure 19. A second error (lightning symbol) happens when the previous one is being localized.

As discussed for the second scenario above, at t4 SIB<sub>0</sub> is opened which puts SIB<sub>1</sub> and SIB<sub>2</sub> on the active scan-path. Between t4 and t<sub>6</sub> (when SIB<sub>0</sub> is closed again) SIB<sub>2</sub> is selected (though closed) and, therefore, cannot be opened by a fault flag signal from Monitor 2. That is, any fault happening after t4, is captured at t7 and detected at t8. It should be noted that since SIB<sub>2</sub> is closed, the fault flag from Monitor 2 is not acknowledged and therefore remains active until SIB<sub>2</sub> is opened and the error code from Monitor 2 is captured into the 3-bit shift-register connected to SIB<sub>2</sub>. The detection and localization of the last error, is performed in the next localization round.

For the last scenario, consider the timeline in Figure 20Figure 1, where both monitors detect faults in the interval between  $t_0$  and  $t_1$ .

Figure 20. Two faults (lightning symbols) are detected together

In this case, both faults are detected at t<sub>2</sub>. In comparison to the scenario for one fault (see Figure 18), the localization procedure takes a longer time as SIB<sub>2</sub> is also open and its associated register is also included in the scan-path.

As a final note in this section, one observes from Figure 18 and Figure 20 that the shaded states are traversed no matter how many faults are being detected and localized. In the rest of this work this constant overhead will be denoted by Joh.

Based on the observations made above, we present in the following section a time analysis on the worst-case fault localization time, for the case of a single error, and the case of multiple concurrent errors. As part of the worst-case error detection and localization time ( $t_{worst}$ ) is the constant  $J_{OH}$ ; the presented analysis only focuses on the number of shift states in  $t_{loc}$ , which is the variable part of  $t_{worst}$ .

# 9.6.1.3 Time analysis

In this section analyses are presented for the worst-case error localization time in a self-reconfigurable network designed in a balanced hierarchical manner, for two cases: (1) when a single fault occurs, and when (2) multiple faults occur such that they are all addressed in one localization round (see the discussion on Figure 20).

Consider the network shown in Figure 21 in which (except for the last level) each SIB has a number of k SIBs connected to its hierarchical port. Assuming that we have  $N = k^h$  instruments in total, the network resembles a balanced k-ary tree whose root is the SIB directly connected to the Fault Manager.

Figure 21. A balanced tree hierarchical network

# 9.6.1.3.1 Localization time in the case of a single fault

Given the network in Figure 16, and assuming that only one monitor has raised a fault flag causing all SIBs on its hierarchy to change their state to open, there are  $s=1+k\times h$  SIBs on the path to each instrument where 1 represents the SIB at level 0. The total shift time  $t_s$  is therefore the sum of s and the length of shift-register interfacing the instrument to the network (denoted by L) plus one for the ErrorFlag.

### 9.6.1.3.2 Localization time in the case of multiple faults

Assume that F faults  $(F \le N)$  are to be localized at the same time (same localization round). To calculate the worst-case localization time, we consider monitors detecting these faults to be spread in the network such they cause a maximum possible number of SIBs to be opened (maximizing the length of active scan-path, thus leading to the longest localization time).

## 9.6.1.4 Network design

Next, an optimized design method is described for the proposed self-reconfigurable networks such that the error-localization time for a single fault is minimized.