# Deliverable D2.5.U Report on modeling, variability and validation

WP number: WP2

Lead Beneficiary number: 4 Lead Beneficiary name: IFS

Dissemination Level: PU Nature of deliverable: R

**Delivery Month: M31**

List of authors

Henrique Gomes

Yoann Courant, Philippe Heredia, Firas Mohamed

Carme Martínez Domingo, Eloi Ramon, Jordi Carrabina

Francesc Vila, Jofre Pallares, Lluís Teres

Niels Olij, Arjen Bakker

| Creation date: | 19/04/2013                                      | Revision:      | 1.4 |

|----------------|-------------------------------------------------|----------------|-----|

| Document ref.: | Report on, modeling, variability and validation | Num. of pages: | 65  |

Grant #287682 ©TDK4PE, 2011

| WP Leader: IFS (4)                 |                                                                                            |                                                |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------|--|--|--|

| Partner in charge <sup>1,2</sup> : | IFS (4)                                                                                    | 0                                              |  |  |  |

| Responsible persons <sup>2</sup> : | Firas Mohamed, Yoann Courant,<br>Ph. Heredia                                               | infiniscale                                    |  |  |  |

| Contributing partner               | S                                                                                          |                                                |  |  |  |

| Partner <sup>2,3</sup> :           | UAB (1)                                                                                    |                                                |  |  |  |

| Persons <sup>2</sup> :             | Jordi Carrabina, Carme Martínez,<br>Eloi Ramon, Gerard Sisó, Paris<br>Vélez, Carme Matinez | UAB Universitat Autònoma de Barcelona          |  |  |  |

| <partner<sup>2,3:</partner<sup>    | UAlg (9)                                                                                   | O 40                                           |  |  |  |

| Persons <sup>2</sup> :             | Henrique Gomes                                                                             | 01                                             |  |  |  |

| WP Producer(s): WP5                |                                                                                            |                                                |  |  |  |

| Partner in charge <sup>3,4</sup> : | CSIC (5)                                                                                   | <b>com</b> ⊗                                   |  |  |  |

| Responsible persons <sup>2</sup> : | Lluís Terés, Jofre Pallarès,<br>Francesc Vila, Adrià Conde                                 | INSTITUT DE MICROELECTRÓNICA DE BARCELONA CSIC |  |  |  |

Partner/Person(s) responsible(s) of this delivery.

Specify: Partner SHORT-NAME (partner #).

Partner/Person(s) responsible(s) of this delivery.

Specify: Partner SHORT-NAME (partner #).

| Rev. | Date       | Authors / Reviewers           | Remarks                                                              |

|------|------------|-------------------------------|----------------------------------------------------------------------|

| 1.3  | 08/11/2013 | F. Mohammed,<br>Yoann Courant | Sections 8 & 9                                                       |

| 1.2  | 05/11/2013 | H. Gomes                      | Review of capacitor, diode and OTFT models and extraction procedures |

| 1.1  | 30/10/2013 | F. Mohammed                   | Review & add sections                                                |

| 1.0  | 21/10/2013 | J. Carrabina                  | Restructuring D2.3.U & D2.5.U                                        |

### **Contents**

| C  | onte  | nts                                                                | 3   |

|----|-------|--------------------------------------------------------------------|-----|

| Li | st of | f Figures                                                          | 5   |

| Li | st of | f Tables                                                           | 7   |

| Sı | ımm   | nary                                                               | 8   |

| Αı | oplic | cable Documents                                                    | 8   |

| 1  | •     | DDELING                                                            |     |

| _  | 1.1   | Physical modeling                                                  |     |

|    | 1.2   | Behavioral modeling                                                |     |

|    |       | Semi-physical modeling                                             |     |

|    | 1.4   | Complete story                                                     | 11  |

| 2  | Pa    | rameter extraction for electrical characterization                 | 13  |

|    | 2.1   | Test vehicles for parameter extraction                             | 13  |

| 3  | De    | vice models and parameters                                         | 15  |

|    |       | Resistor model                                                     |     |

|    |       | 1.1 General parameter extraction procedure                         |     |

|    |       | Capacitors model                                                   |     |

|    |       | Inductor models                                                    |     |

|    | 3.    | 3.1 Parameter extraction procedure                                 | .22 |

|    |       | RF devices and transmission line models                            |     |

|    |       | 4.1 Parameter extraction procedure                                 |     |

|    |       | 5.1 Review                                                         |     |

|    |       | 5.2 Electrical characterization of rectifying elements             |     |

|    |       | 5.3 Diode model in a rectifying circuit                            |     |

|    |       | Organic Thin Film Transistors (OTFTs) models (new – August Report) |     |

|    |       | 6.1 Parameter extraction procedure                                 |     |

| _  |       | 6.2 Parasitic effects                                              |     |

| 4  |       | signing experiments by Input Sampler                               |     |

|    |       | Introduction Optimal experiment design                             |     |

|    |       | Generating new experiments                                         |     |

|    |       | Modeling trial of the horizontal linear resistor LR01              |     |

| 5  |       | lidation                                                           |     |

|    | 5.1   | Blind validation                                                   |     |

|    | 5.2   | Viewing models behavior                                            |     |

|    | 5.3   | Validation based on new printed samples                            | 50  |

|    | 5.4   | Models Validity & export                                           | 50  |

| 6  | Dy    | namic modeling                                                     | 51  |

|    |       | 51                                                                 |     |

| 7  | Va    | riability                                                          | 52  |

|    |       | Variability Management                                             |     |

|    |       | 1.1 Variability management on mathematical models                  |     |

|    |       | Strategy to cope with variability and yield                        |     |

|    |       | 2.1 One model per transistor dimension                             |     |

| 7.2.2 General model for OTFTs                                                                                                                  | 55 |

|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.2.3 Preliminary example of the application of the UMEM model to simulates I-V characteristics of OTFTs produced within the TDK4PE consortium | 55 |

| 8 Methodology proposed inside TDK4PE                                                                                                           |    |

| 8.1 Integrated models                                                                                                                          | 57 |

| 8.1.1 Infiniscale Semi-physical model                                                                                                          | 57 |

| 8.1.2 UCM Semi-physical model                                                                                                                  | 58 |

| 8.1.3 UCM parameter extractor                                                                                                                  | 58 |

| 8.2 Devices Examples                                                                                                                           | 60 |

| 8.2.1 Load and Drive OTFTs                                                                                                                     | 60 |

| 8.2.2 Integration in the TDK4PE framework                                                                                                      |    |

| 8.3 Circuits Example                                                                                                                           | 61 |

| 8.3.1 Inverters and Ring Oscillator                                                                                                            |    |

| 9 Conclusions                                                                                                                                  | 63 |

| 10 References                                                                                                                                  | 64 |

| 10.1 Documents                                                                                                                                 | 64 |

### **List of Figures**

| Figure 1: Physical modeling 9                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Behavioral modeling10                                                                                                                                                                                                                                                                                                              |

| Figure 3: Semi-physical modeling11                                                                                                                                                                                                                                                                                                           |

| Figure 4: Modeling complete flow                                                                                                                                                                                                                                                                                                             |

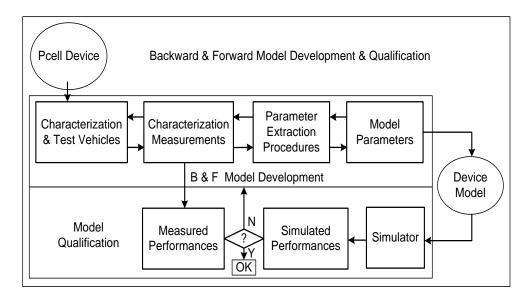

| Figure 5. Schematic diagram of the characterization vehicles and parameter extraction in the development and qualification of the technology                                                                                                                                                                                                 |

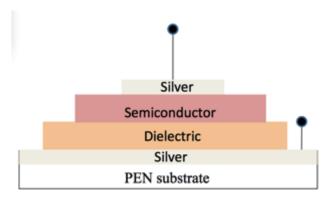

| Figure 6. Schematic structure of the different layers used to make MIS capacitors or TFT devices                                                                                                                                                                                                                                             |

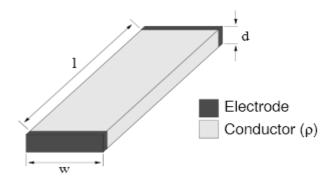

| Figure 7. Physical parameters used to estimate the resistance of a material16                                                                                                                                                                                                                                                                |

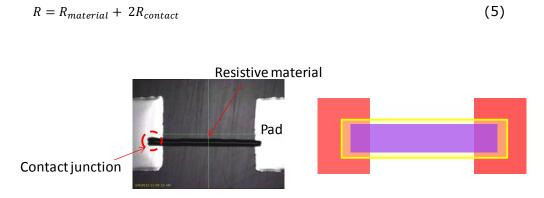

| Figure 8. (a) Photograph of a linear resistor, (b) schematic arrangement of the layer layout                                                                                                                                                                                                                                                 |

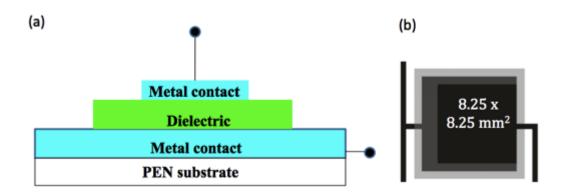

| Figure 9. (a) Schematic cross section view of a printed capacitor, (b) Schematics of a top view showing the active area and printed tracks18                                                                                                                                                                                                 |

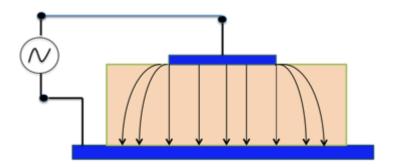

| Figure 10. Schematic representation of an increase in the effective area of the top electrode caused by lateral conduction. This effect can enhance the measured capacitance                                                                                                                                                                 |

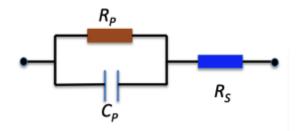

| Figure 11. Equivalent circuit for a printed MIM structure including the series resistance caused by metal tracks                                                                                                                                                                                                                             |

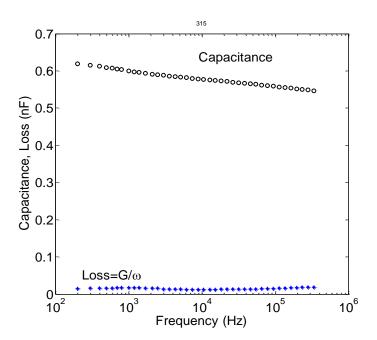

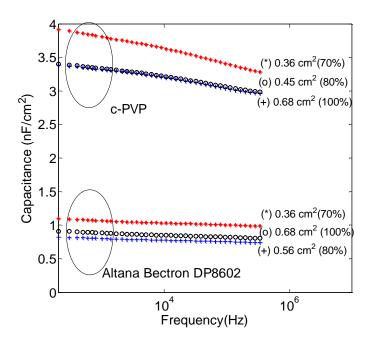

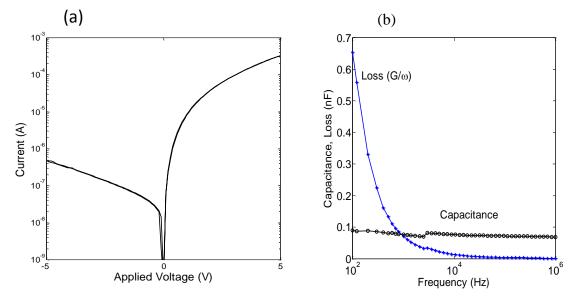

| Figure 12. Capacitance and loss $(G/\omega)$ as function of the frequency for a printed capacitor based on a Altana Bectron dielectric. Apart from a small decrease in capacitance with frequency, the behaviour is typical of a pure capacitor. The flat behavior upon with frequency shows that the resistance of the metal track is small |

| Figure 13. The frequency dependence of the capacitance of several printed MIM structures. The area of the top electrode was varied in respect to the total dielectric area21                                                                                                                                                                 |

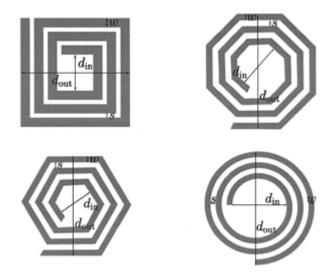

| Figure 14.Typical spiral inductor topologies (square, hexagonal, octagonal and circular).  Extracted from [5]22                                                                                                                                                                                                                              |

| Figure 15. Electrical model of an inductor                                                                                                                                                                                                                                                                                                   |

| Figure 16. Typical inductor frequency response: Impedance absolute value and phase (a) and inductance frequency response (b). Extracted from [6]24                                                                                                                                                                                           |

| Figure 17. Microstrip ring resonator. Bottom ground plane not represented26                                                                                                                                                                                                                                                                  |

| Figure 18. Typical S-parameters response of a band-pass filter. $S_{21}$ represents transmission or gain and $S_{11}$ is the reflection loss (in dB)27                                                                                                                                                                                       |

| Figure 19. TRL differential calibration kit (left) and devices under test PCB (right).  Extracted from [9]28                                                                                                                                                                                                                                 |

| Figure 20. Schottky diode structure                                                                                                                                                                                                                                                                                                          |

| Figure 21. (a) I-V characteristic and (b) capacitance and loss $(G/\omega)$ as function of frequency for a Schottky diode31                                                                                                                                                                                                                  |

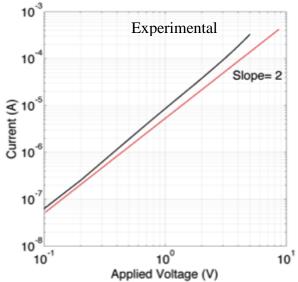

| Figure 22. Log-log plot of the forward bias current-voltage characteristic showing that the slope is slightly higher than 231                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                              |

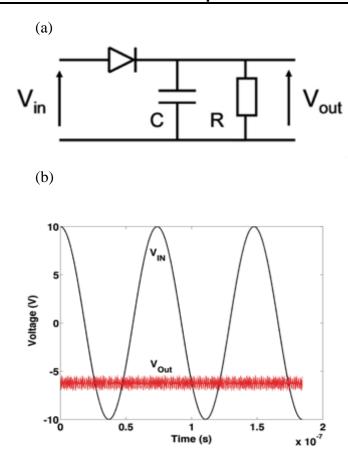

| DC signal. The load circuit uses a capacitor of 100 nF and a resistance of 1 M $\Omega$ . f=13.56 MHz32                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

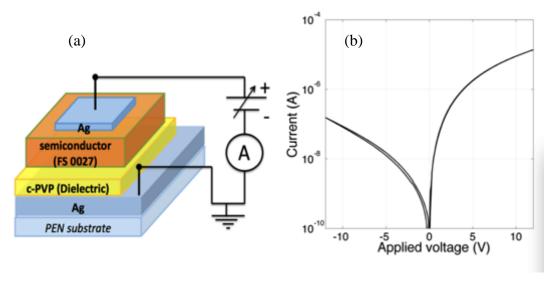

| Figure 24. (a) Schematic representation of a MIS-Diode, (b) typical current voltage characteristic showing an asymmetric behaviour                                          |

| Figure 25. Schematic diagram showing the proposed mechanism to explain non-symmetric $I$ - $V$ curves in MIS structures33                                                   |

| Figure 26. Electrical characteristics of MIS diode. (a) Semilog plot showing the existence of hysteresis in reverse bias. (b) Log-log plot of the forward bias current      |

| Figure 27. (a) Capacitance and loss as function of the frequency (b) Capacitance voltage plot recorded at a test frequency of 1 kHz. The diode area is $1 \text{ mm}^2$ 34  |

| Figure 28. Rectified signal at 2 MHz the load capacitor is 470 nF and the load resistance of 1 M $\Omega$ 34                                                                |

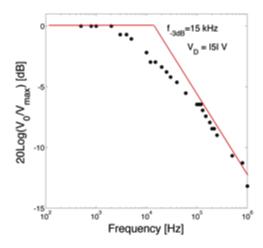

| Figure 29. Frequency dependence of $V_{out}$ /V $_{in}$ for a MIS diode is connected in a rectifying circuit. The load is a RC parallel circuit (R=1 M $\Omega$ , 100 nF)35 |

| Figure 30. $I$ - $V$ characteristic of a diode connected TFT. The Inset shows the circuit configuration. The area of the TFT is 2.5x1.8 mm $^2$ 35                          |

| Figure 31. Basic model for a Schottky barrier diode. The resistance is frequency dependent and related with the charge carrier transport limitations at high frequencies.   |

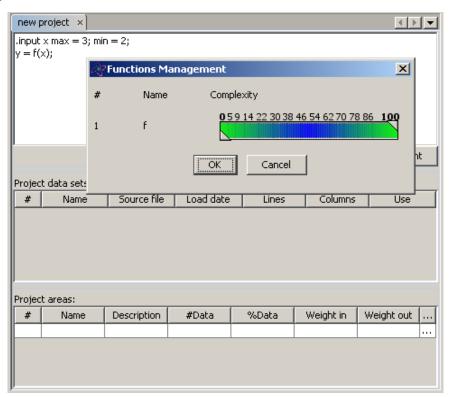

| Figure 32. Incremental input sampler46                                                                                                                                      |

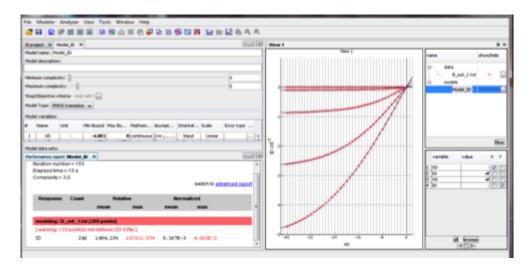

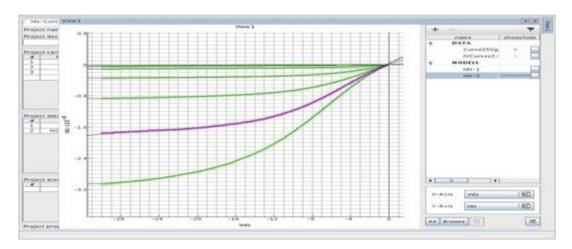

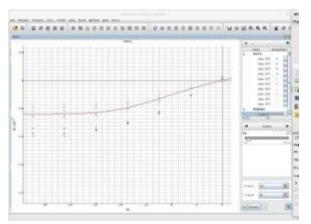

| Figure 33. Modeling ENEA OTFT47                                                                                                                                             |

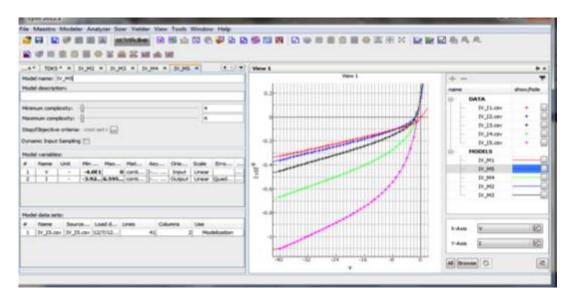

| Figure 34. Semi-Physical modeling of OTFTs data47                                                                                                                           |

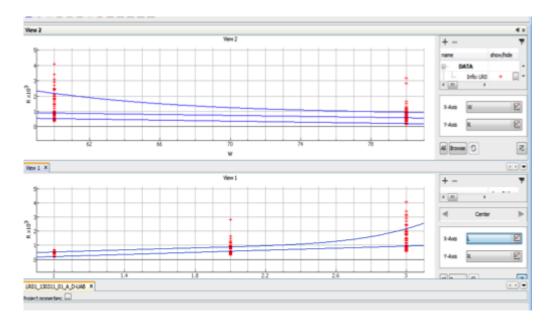

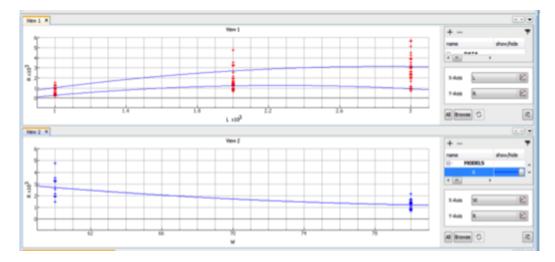

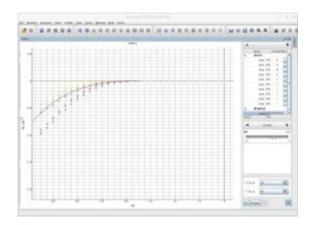

| Figure 35. Variability curves for LR01_A_130405_01_D-UAB_13042348                                                                                                           |

| Figure 36. Variability curves for LR02_130321_01_A_D-UAB48                                                                                                                  |

| Figure 37. Semi-Physical modeling of OTFTs data49                                                                                                                           |

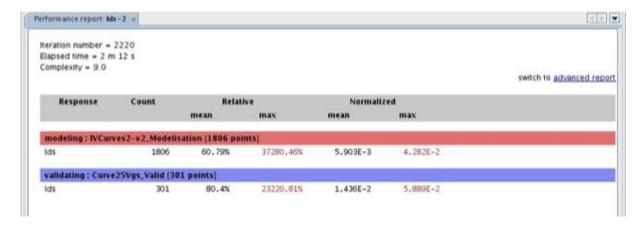

| Figure 38. Error report on modeling and validation data50                                                                                                                   |

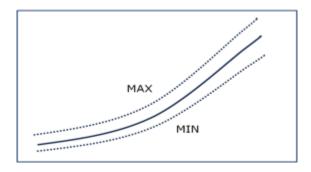

| Figure 39. Managing Variability by MIN/MAX modeling52                                                                                                                       |

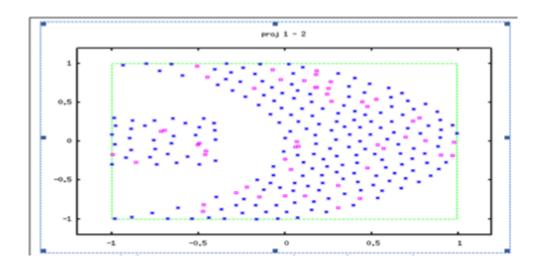

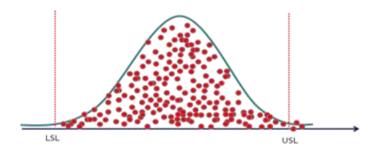

| Figure 40. Monte Carlo sampling54                                                                                                                                           |

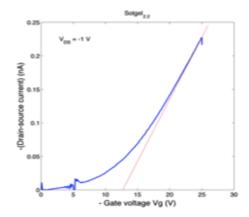

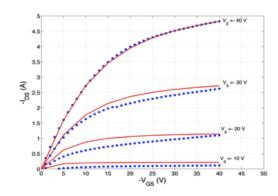

| Figure 41. Transfer curve measured in the liner region ( $V_{DS}$ = -1V)56                                                                                                  |

| Figure 42. Comparison between experimental (dotted line) and simulated (full line) $I-V$ characteristics using the UMEM model56                                             |

| Figure 43. Managing variability within the consortium57                                                                                                                     |

| Figure 44. Semi-physical GUI58                                                                                                                                              |

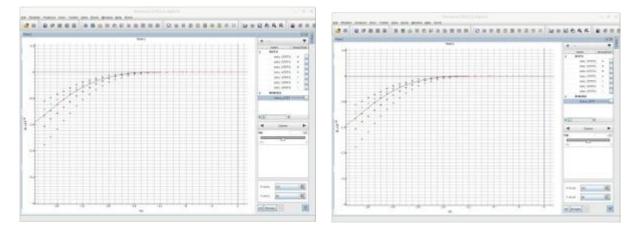

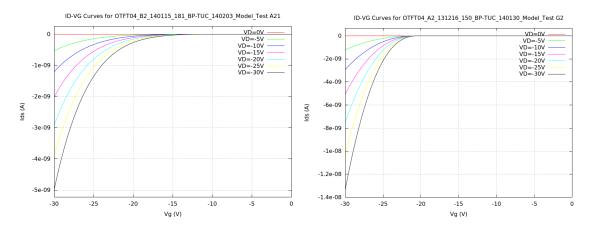

| Figure 45. Load OTFT: ID-vs-VD and Load OTFT ID vs VG60                                                                                                                     |

| Figure 46. Drive OTFT modeling: ID vs VD and ID vs VG61                                                                                                                     |

| Figure 47. Plots of OTFT curves simulated in NGspice using the Verilog-A models61 $$                                                                                        |

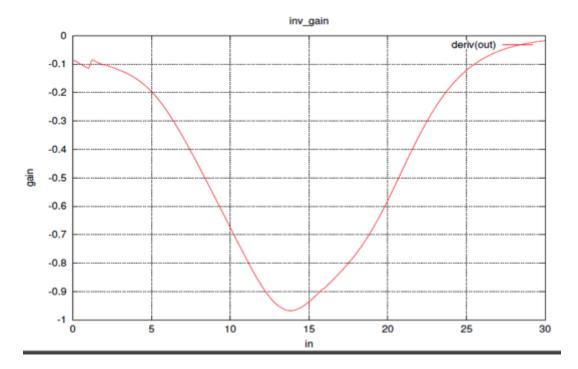

| Figure 47. Simulated inverter transfer curve based on semi-physical models62                                                                                                |

### **List of Tables**

| Table 1. General parameter extraction procedure1                                                      |

|-------------------------------------------------------------------------------------------------------|

| Table 2. Parameter extraction for capacitors2                                                         |

| Table 3. Summary the electrical test vehicle and parameter extraction for inductors. $\dots$ 2        |

| Table 4. Summary the electrical test vehicle and parameter extraction for inductors $2$               |

| Table 5. Basic characteristics of the two approaches to fabricate rectifying diodes3                  |

| Table 6. Rectifying diodes characteristics3                                                           |

| Table 7. Summary of the electrical test vehicle and parameter extraction for Schottky diodes3         |

| Table 8. Parameter extraction using the Unified Compact Model and parameter Extraction Method (UMEM)4 |

| Table 9. Experimental OFET parameters and measurement procedures4                                     |

| Table 10. TET parameters extracted from the simulation of the output $I-V$ curves 5                   |

#### **Summary**

TDK4PE relies in the successful fabrication of organic based circuits using inkjet printed materials. These circuits use thin film transistors (TFTs), diodes and resistors as basic build blocks. The performance of these devices is essential controlled by intrinsic material parameters (such as carrier mobility, free carrier concentration), and by extrinsic parameters, among these the most important one is the density of electrical active impurities present at interfaces. For TFTs the most relevant interface is the dielectric/semiconductor interface, while for diodes metal/semiconductor interface is critical. This report provides an account of the parameters (and appropriate techniques) to be measured/extracted according to the electrical device models. The measurements proposed should provide feedback information for adjustment of the fabrication process and in this case the speed of the measurement is crucial. This task will be undertaken on a phenomenological basis, relying on experience and statistical correlations, this is justified because the understanding of fundamental relationships between cause and effect is still lacking.

Understanding than variability and yield are key issues for building circuits out of a large number of devices lets us to consider the variability issues at circuit simulation level that have to agree with the results of model parameters extraction.

Finally it is presented a technology to design experiments called InputSampler.

As a summary this report:

- a) Specifies the models to be used and the parameters to be extracted.

- b) Defines techniques and measurement protocols suitable for all inkjet organic based electronics (low mobility, poor environmental stability, drifts). The objective is to minimize data dispersion caused by inadequate measurement procedures.

- c) Specifies the devices modelling and validation procedure.

- d) Proposes a two phase strategy to cope with circuit simulation according to the selection and usage of limited number of transistors sizes.

### **Applicable Documents**

List of previous project reports needed or useful to understand this one, in chronological order:

- 1. Deliverable D2.3: TDK Development Guide: Cell Library Development and Characterization.

- 2. Deliverable D6.1: TDK Multi-Printing Process organization and schedule.

#### 1 MODELING

This section describes the modeling techniques going from physical to behavioral modeling.

The goal of is to clarify the concepts and procedures concerning Modeling, Validation and Variability Management for the devices built inside the TDK4PE project, especially for Organic Thin Film Transistors.

This clarification is needed due to the different understanding that we noticed among the different communities involved in the project, basically the organic and the silicon ones.

Once these main goals are clarified, a proposal will be made for managing in the project, the whole process from device fabrication to circuit simulation using those devices.

#### 1.1 Physical modeling

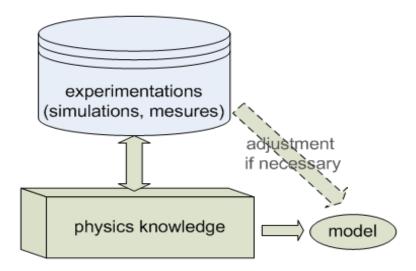

Physical modeling consists in elaborating physical model based on physics knowledge and adjusting them if necessary from experiment measures. Figure 1 describes this framework.

Figure 1: Physical modeling.

One main advantage of this approach is to have a physically certified model. Nevertheless the cost of this advantage is a coarse-grain simplification of the model that could become far away from real complex phenomena.

#### 1.2 Behavioral modeling

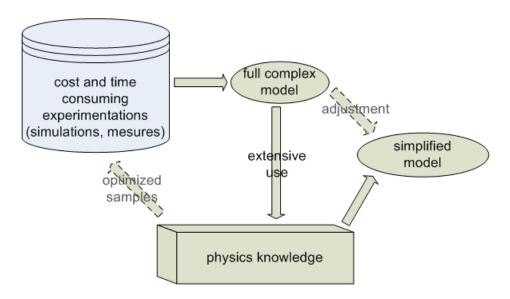

Face to time and cost consuming experimentations, behavioral modeling proposes to model the physical phenomena from a mathematical point of view. These models are often called black-box models because their comportment is complex and also often directly intractable from a human analysis.

Their own benefit is to tackle whole phenomena<sup>5</sup> by replacing time consuming and costly experimentation with fast evaluation of models<sup>6</sup>. Figure 2 shows this kind of modeling. These models are grounded on mathematical formulation. Nevertheless they can help to analyze whole physical phenomena and to build simplified (but physically inspired) models. For example these simplified models could handle phenomena only in specific zone of data, or only some aspect of phenomena.

Figure 2: Behavioral modeling.

#### 1.3 Semi-physical modeling

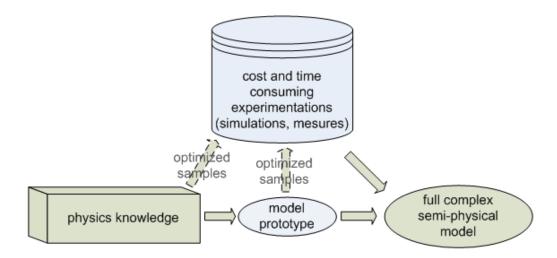

To combine the advantages of physical modeling and behavioral modeling, semi-physical modeling propose to design a physical model prototype from physics knowledge. This prototype is grounded on physical certified formula and has some indeterminate part such as undefined constant (as generally in physical modeling) but also undetermined function of some variable<sup>7</sup>. Then some behavioral modeling technique could be adapted to handle the physical model prototype instead of a mathematical model that could be incompatible with physics knowledge. The model is often compared as a gray-box: some physical aspects of the model are visible and tractable, other are handled by mathematics formula that could be physically erroneous. Very soon, the modeler will be able to treat semi-physical modeling.

\_

<sup>&</sup>lt;sup>5</sup> to be more exact the model is defined with a confidence interval and is only an approximation of phenomena

<sup>&</sup>lt;sup>6</sup> this suppose that the model has lower cost than experimentation which it's generally the case.

<sup>&</sup>lt;sup>7</sup> In a way semi-physical modeling can be viewed as a generalization of physical modeling

Figure 3: Semi-physical modeling.

#### 1.4 Complete story

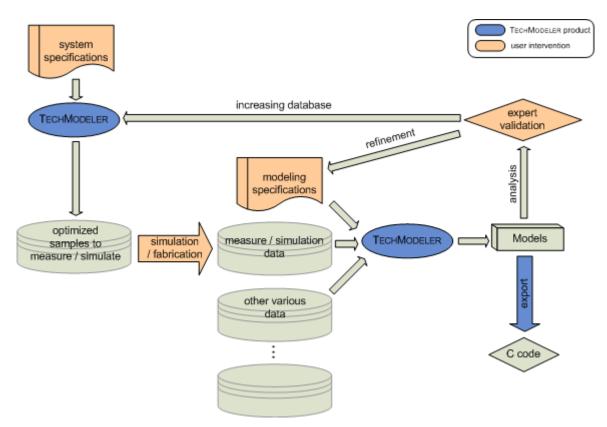

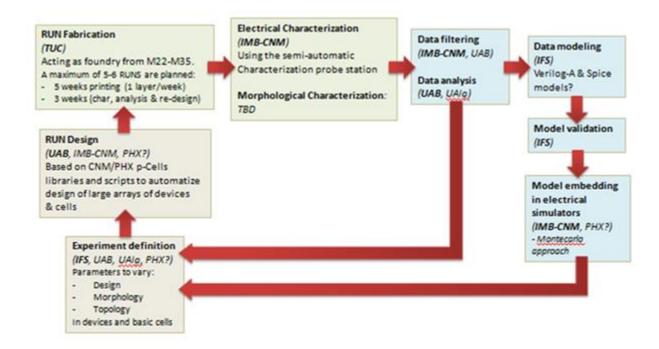

Needed data for sampling can be optimized. An advanced technology called "Optimal experiment design" has been developed to generate samples in multi-dimension space. Samples are chosen in a way to cover the input space of parameters while removing redundancy, i.e. avoiding samples that do not bring more information, for example those that are too close from initial samples. The flow can be detailed as in Figure 4.

Figure 4: Modeling complete flow.

First the user describes the physical system and then creates an optimized database. After simulation or fabrication and measures of the samples, the user defines modeling specifications to create models. The models can be refine by changing modeling specifications

#### **Deliverable Report**

#### 2 Parameter extraction for electrical characterization

In this section, we will discuss the need off electrical parameters for the device models a complete technology characterization.

#### 2.1 Test vehicles for parameter extraction

Electrical characterization can be carried out in three different samples such as (i) witness samples, (ii) test vehicles and (iii) non specialized final circuits.

Witness samples are samples without active function. These samples are used to obtain information of a particular manufacturing step. Examples include the morphology or the roughness of a particular layer. However, the interaction of layers varies from batch to batch. In the case of the non-specialized circuits, the sample contains all the processing steps, but the characterization may not be as straightforward as in witness samples. Because of these constraints, test vehicles were specially designed to allow effortlessly the extraction of the device parameters using electrical techniques. Simulation programs such as SPICE, employ devices models (BSIM3, BSIM4 –more information in D2.3-) for circuit simulation, which uses electrical (and physical) parameters.

In this section we will focus on the test vehicles designed to be probed using electrical measurements. The electrical characterization includes both DC or quasi-static techniques such as current-voltage measurements (I-V) and small signal (AC) impedance based techniques such as capacitance-voltage (C-V) profiling. A detailed description of test equipment used for this characterization in each TDK4PE node is listed in D6.1.

Regarding the physical-based models for circuit simulation, two main classes of parameters are taken into account, electrical and geometrical parameters. For instance, concerning the drain current in linear regime equation of an OTFT, as shown equation 1, the electrical parameters are the mobility ( $\mu$ ), capacitor per unit area ( $C_i$ ) and the threshold voltage ( $V_T$ ); the geometrical parameters are the length (L) and width (W) and the insulator thickness ( $d_i$ ).  $V_{GS}$  and  $V_{DS}$  are the electrical test parameters. The electrical characterization of the test vehicle allows the electrical parameters extraction and to obtain the values of the device model.

$$I_{DS} = \frac{W}{L} \mu C_i (V_{GS} - V_T) V_{DS} \tag{1}$$

The basic role of electrical characterization in the technology is shown in Figure 5. In order to find the parameters value for a device, according to a specific device model, different characterization procedures are required. A good fitting between the model and the parameters occurs when the simulation and the real measurements matches.

### Deliverable Report Parameter extraction for electrical characterization

Figure 5. Schematic diagram of the characterization vehicles and parameter extraction in the development and qualification of the technology.

#### 3 Device models and parameters

In this section we will focus on the models and parameters to be extracted for linear and snake resistors, capacitors, inductors, diodes and OTFTs.

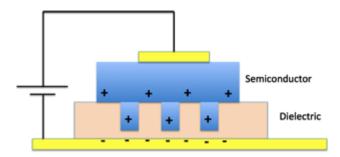

The devices are function of the material stack arrangement because of the interaction among them is important. Regarding TDK4PE technology, which is based on PMOS technology, the material stack is shown in Figure 6. The schematic represents a metal-insulator semiconductor (MIS) structure. It is worth to note that this order of the materials leads to the bottom gate contact OTFT structure.

Figure 6. Schematic structure of the different layers used to make MIS capacitors or TFT devices.

#### 3.1 Resistor model

The most elementary of all devices is the resistor. It consists of a bar of homogeneous materials with two contacts at the extremes. Injection of carriers is assumed to be unhindered and the current only limited by the resistivity of the material. The electrical parameter of a resistor is its resistance R of the material, which is defined by Ohm's Law (equation 2):

$$R = \frac{V}{I} \tag{2}$$

The reciprocal of this resistance is called conductance G and is a more adequate entity in electrical characterization. Both device parameters resistance (equation 3) and conductance (equation 4) can be expressed in their material parameters, resistivity  $\rho$  and conductivity  $\sigma$ , according to

$$R = \rho \, \frac{d}{A} \tag{3}$$

$$G = \sigma \frac{A}{d} \tag{4}$$

where *A* is the cross-section area and d the length of the device (Figure 7).

Figure 7. Physical parameters used to estimate the resistance of a material.

However the Ohm's Law and if we consider the whole resistor device, a parasitic series resistance is created at the junction of the resistive material and the pads due to the difference in their work functions. This parasitic resistance is called contact resistance,  $R_{contact}$ . Then, the resistance of the resistor device is composited by the material and the contacts (equation 5). The following expression is used to model the device, having two areas of interfacial contact as shown in Figure 8. For simplicity, it is assume that both contact resistances are equal which may not be true.

Figure 8. (a) Photograph of a linear resistor, (b) schematic arrangement of the layer layout.

#### 3.1.1 General parameter extraction procedure

| Parameters extracted                | Test vehicle                            | Test vehicle<br>layout                                 | Characterization measurements      | Characterizati<br>on procedure                                                                                                   |

|-------------------------------------|-----------------------------------------|--------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Rsheet<br>Resistivity               | Van Der Pauw                            |                                                        | A B  D C  Contacts in the extremes | Four- probe measurement.  Apply a curve from 0V to 1-2V between A & B contacts, and measure current (I) between C & D contacts.  |

| Rsheet<br>Resisitivity<br>Linewidth | Greek cross                             |                                                        | A B C D Contacts on the pads       | Four- probe measurement. Apply a curve from 0 V to 1-2V between A & B contacts, and measure current (I) between C & D contacts.  |

| Rcontact                            | Greek cross for<br>R <sub>contact</sub> | Material 1 (Blue pattern) and Material 2 (Red pattern) | A B C D Contacts on the pads       | Four- probe measurement. Apply a curve from 0 V to 1-2 V between A & B contacts, and measure current (I) between C & D contacts. |

Table 1. General parameter extraction procedure.

#### 3.2 Capacitors model

Printed capacitors are Metal-Insulator-Metal (MIM) sandwich structure as shown in Figure 9.

Figure 9. (a) Schematic cross section view of a printed capacitor, (b) Schematics of a top view showing the active area and printed tracks.

Capacitor structures were used to extract the insulator parameters such as dielectric constant, leakage currents, and parasitic effects due to inkjet printing. The two major sources of parasitic effects are: (i) fringing effects, (iii) lateral conduction and (ii) series resistance caused by the metal tracks. In addition capacitors may also be used to inspect for layer thickness variations with the area.

As shown in Figure 9b the physical area of the bottom electrode coated with the dielectric is larger than the top metal layer. In a MIM structure the number of free carriers in the polymer is low and fringing effects are not really expected. Fringing may be significant in metal-insulator-semiconductor (MIS) structures. However, the presence of atmospheric moisture may contribute to fringing by making the dielectric surface conductive. When measurements are done under vacuum conditions, the additional parasitic capacitance observed in MIM structures may be due to a lateral conduction along the polymer near the bottom contact surface. This is schematically represented in Figure 10 and can enhance the effective area of the capacitor.

Other sources parasitic capacitance may appear due to the alignment of top and bottom electrode tracks.

Series resistance due to the printed silver tracks may limit the frequency response of the capacitors. Series resistance effects must be minimized by printing wide and short silver tracks.

Figure 10. Schematic representation of an increase in the effective area of the top electrode caused by lateral conduction. This effect can enhance the measured capacitance.

#### 3.2.1 Parameter extraction procedure

Figure 11 shows the equivalent circuit for a printed capacitance.  $C_P$  and  $R_P$  can be evaluated by measuring the impedance at low frequencies (f<1 kHz) using an impedance analyzer. To estimate  $R_S$  one must measure the impedance as function of frequency. The presence of a small series resistance (R< 10  $\Omega$ ) due to the silver electrodes can a cause a relaxation frequency above or within the MHz range.

Figure 11. Equivalent circuit for a printed MIM structure including the series resistance caused by metal tracks.

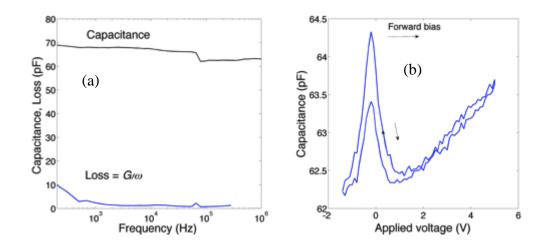

Figure 12 show the capacitance and loss  $(G/\omega)$ , where  $\omega=2.\pi.f$ , as a function of the frequency for a printed capacitor. As commonly observed in organic based electronic devices the capacitance decreases slightly in a linear fashion with frequency. This is a well-know process that is modeled by a constant phase element. The admittance (Y) of the capacitor can be expressed by the empirical relation  $Y=A_0(i\omega)^n$  where  $1\ge n\ge 0$  and Ao a constant. The physical origin of the process is unclear. In semiconductor materials it is reasonable to assume that is caused by to dipolar relaxation with a wide distribution of relaxation times. However, this frequency dependence is relatively small and it can be neglected.

The model of a printed capacitor will only take into account the parameters described in Figure 11. Table 2 summarizes the electrical measurements used to extract capacitor parameters.

| Model Parameter extraction parameter procedures |                                                                                                                                     | Characterization equipment       | Test<br>vehicle |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|

| $R_p$ and $C_p$                                 | Test frequency of 1 kHz, AC signal 100 mV                                                                                           | LCR meter,<br>Impedance Analyzer | MIM             |

| R <sub>S</sub>                                  | Rs causes major disperison in the impedance as function of frequency. The frequency of this dispersion allows the estimation of Rs. | LCR meter,<br>Impedance Analyzer | MIM             |

Table 2. Parameter extraction for capacitors.

Figure 12. Capacitance and loss  $(G/\omega)$  as function of the frequency for a printed capacitor based on a Altana Bectron dielectric. Apart from a small decrease in capacitance with frequency, the behaviour is typical of a pure capacitor. The flat behavior upon with frequency shows that the resistance of the metal track is small.

Figure 13 show the capacitance as function of the frequency recorded in several MIM structures fabricated using two different dielectrics. The cross linked PVP and the Altana Bectron. For each dielectric the printed area as well as the bottom electrode area were kept constant. However the area of top electrode is varied. This allows us to inspect for

fringing effects. From the data in Figure 13 we can see that when the area of top electrode is significant smaller (70%) than the bottom dielectric, there is an excess capacitance. This is possible caused by lateral conduction as discussed above.

Figure 13. The frequency dependence of the capacitance of several printed MIM structures. The area of the top electrode was varied in respect to the total dielectric area.

#### 3.3 Inductor models

An inductor is a passive component that stores energy in form of magnetic field. It consists on a wire or other conductor wounded into a coil (this coil can be air). The inductance is a property by which a variation of the current produces a varying magnetic field that induces voltage in the conductor (inductor) itself and/or other conductors nearby. For RF applications a typical implementation is a printed spiral on the substrate. Several topologies can be used, as is shown in Figure 14.

Figure 14.Typical spiral inductor topologies (square, hexagonal, octagonal and circular).

Extracted from [5]

Inductance must be calculated in function of the used implementation. For planar spiral inductances, expressions introduced in [5] are typically used:

$$Lmw = K_1 \mu_0 \frac{n^2 d_{avg}}{1 + K_2 \rho} \tag{13}$$

$$L_{gmd} = \frac{\mu n^2 d_{avg} c_1}{2} \left( \ln(c_2/\rho) + c_3 \rho + c_4 \rho^2 \right)$$

(14)

The first approximation  $(L_{mw})$  is based on a modification of an expression developed by Wheeler; the second  $(L_{gmd})$  is derived from electromagnetic principles by approximating the sides of the spirals as current-sheets. In these expressions,  $\mu_0$  is the vacuum permeability,  $d_{avg}$  is the average diameter of the spiral (davg = 0.5(dout + din)) and  $\rho$  is the fill ratio  $(\rho = (dout - din)/(dout + din))$ .  $K_i$  and  $C_i$  are topology depending coefficients. Tables are given in [5].

#### 3.3.1 Parameter extraction procedure

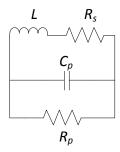

A printed spiral inductor can be modeled as shown in Figure 15.

Figure 15. Electrical model of an inductor.

$R_s$  represents the metal loss (resistance of the conductor),  $R_p$  is the coil loss and  $C_p$  is the distributed capacitance between the turns of the conductor. In the considered structures,  $R_p$  can be neglected because L is small and the capacitance between the turns dominates over these losses.

Using a LCR meter is possible to extract the inductor parameters. Measuring in  $L_s$ - $R_s$  mode,  $L_s$  value can be expressed as:

$$L_{s} = \frac{X}{\omega} = \frac{L\left(1 - \omega^{2}LCp - \frac{CpRs^{2}}{L}\right)}{(1 - \omega^{2}LCp)^{2} + \omega^{2}Cp^{2}Rs^{2}}$$

(15)

If  $\omega^2 C p^2 R s^2 <<1$  and  $\frac{cpRs^2}{L} <<1$ , is possible to simplify  $L_s$ :

$$L_s \cong \frac{L}{1 - \omega^2 L C_n} \tag{16}$$

The stray capacitance  $C_{\rho}$  determines the self-resonant frequency (SRF) of the inductor. At SRF, the inductor presents maximum impedance. At frequencies above SRF,  $C_{\rho}$  is dominant and inductor exhibits a capacitive behavior.

Quality factor can be obtained from  $L_s$ - $R_s$  characterization since:

$$Q = \frac{2\pi f L_s}{R_s} \tag{17}$$

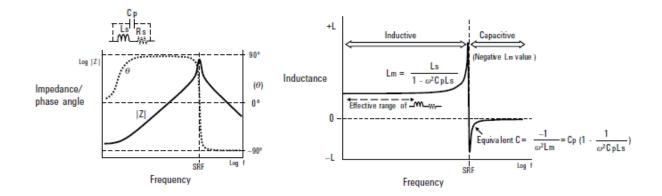

Figure 16. Typical inductor frequency response: Impedance absolute value and phase (a) and inductance frequency response (b). Extracted from [6]

As can be seen in Figure 16(b), the measured inductance ( $L_m$ ) takes its maximum value at SRF.

Using LCR meter is possible the characterization of inductors up to 2 MHz. A vector network analyzer can be used for measurements at higher frequencies. In this case we can obtain S-parameters of the inductor under test and inductor parameters can be extracted from measured impedances using commercial circuit simulation tools, such as Agilent Advanced Design System. Real part of input impedance gives us the series resistance value  $(R_s)$ , and from imaginary part we obtain the reactance. Taking these values at low frequencies, stray capacitance  $(C_p)$  is negligible and inductance (L) can be obtained from reactance.

Measuring at higher frequencies allows also obtaining SRF, typically higher than 2 MHz for the characterized inductors, and, from this frequency,  $C_p$  can be obtained:

$$\omega_{SRF} = \frac{1}{\sqrt{LC_p}} \tag{18}$$

Table 3 shows a summary of the electrical test vehicles and its parameter extraction.

| Model<br>parameter                                    | Parameter extraction procedures                                                                                 | Characterization measurements                        | Characterizati<br>on equipment      | Test<br>vehicle     |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------|---------------------|

| $L_s$ - $R_s$ ;<br>$Q = \omega L_s / R_s$             | Use a sweep test<br>frequency from<br>20Hz up to 2 MHz,<br>AC signal 1V                                         | 2 points-<br>measurement<br>Measure $L_s$ - $R_s$    | LCR meter,<br>Impedance<br>Analyzer | Spiral<br>Inductors |

| $L_s$ - $R_s$ - $C_{pi}$<br>$Q=\omega L_s/R_s$<br>SRF | Use a sweep test frequency from 10 MHz up to GHz.  Extract inductor parameters from S-parameters using software | 1 RF port<br>measurement<br>Measure S-<br>parameters | Network Analyzer                    | Spiral<br>Inductors |

Table 3. Summary the electrical test vehicle and parameter extraction for inductors.

#### 3.4 RF devices and transmission line models

Radiofrequency components, such as filters, couplers, mixers, etc. are an important part in the design of electronic systems. At certain frequencies (from UHF bands) guided wavelengths become shorter and RF devices can be often implemented using planar technology, by means of transmission lines, transmission line sections (stubs) and/or semi-lumped elements. This kind of circuits, usually implemented using conventional PCB techniques, can be also fabricated by means of Printed Electronics.

#### 3.4.1 Parameter extraction procedure

For the electrical characterization of the structures, a vector network analyser is typically used for the measure of scattering (S-) parameters. These parameters give information about the electrical properties, such as transmission and reflection characteristics, of the device under test. However, before designing and characterizing RF devices in a given substrate is necessary to know its electrical properties.

#### **Substrate electrical characterization**

For the design of RF devices using printing electronics techniques, it is necessary the electrical characterization of the substrates. Relative dielectric permittivity ( $\varepsilon_r$ ) (dielectric constant) and loss tangent ( $\tan \delta$ ) (dissipation factor) of the substrate can be extracted using several techniques. A simple method is measuring the resonances of a microstrip ring resonator as show in Figure 17.

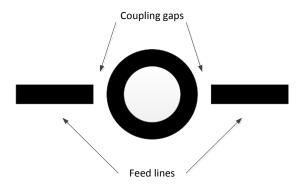

Figure 17. Microstrip ring resonator. Bottom ground plane not represented.

The distance between feed lines and ring resonator (coupling gaps) must be large in order to avoid variation of the intrinsic resonant frequency of the ring and minimize coupling effects (Figure 17). When the mean circumference of the ring (L), is equal to an integral multiple of the guided wavelength, resonance appears:

$$L = 2\pi r = n\lambda_a$$

for  $n = 1, 2, 3...$  (19)

Where r is the mean radius of the ring (difference between inner and outer radius) and  $\lambda_g$  is the guided wavelength, which can be expressed as:

$$\lambda_g = \frac{\lambda_0}{\sqrt{\varepsilon_{eff}}} = \frac{c/f_n}{\sqrt{\varepsilon_{eff}}} \tag{20}$$

being  $f_n$  the ring resonant frequencies and c the speed of light in free space.

From equation (19) and (20):

$$\lambda_g = \frac{L}{n} = \frac{2\pi r}{n} \tag{21}$$

From these expressions, it is possible to obtain the effective permittivity, parameter that takes into account that, in a microstrip line, a fraction of electric fields are not constrained within the substrate:

$$\varepsilon_{eff} = \left(\frac{nc}{2\pi r f_0}\right)^2 \tag{22}$$

And, finally, from the following empirical expression, the relative permittivity ( $\varepsilon_r$ ) can be obtained [7]:

$$\varepsilon_{eff} = \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \left( 1 + 12 \frac{h}{W} \right)^{-1/2} \tag{23}$$

Where h is the height of the substrate and W is the width of the microstrip transmission line. This expression is valid when W/h > 1, condition satisfied in most cases.

Summarizing, for obtaining the dielectric constant of the substrate at several frequencies we can measure S-parameters of a microstrip ring resonator using a network analyser and obtain the resonant frequencies, where peaks of transmitted power appear, and apply the expressions presented.

In order to obtain the dissipation factor is necessary to calculate the attenuation constant using the following expression:

$$\alpha = \frac{8.686\pi}{Q\lambda_g} \qquad (dB/m) \tag{24}$$

Where Q is the unloaded quality factor of the ring resonator:

$$Q = \frac{f_n}{f_2 - f_1} \tag{25}$$

Being  $f_2$  and  $f_1$  the limits of the band (-3dB insertion loss frequencies). The loss tangent (tan  $\delta$ ) can be obtained from the expression [8]:

$$\alpha = 8.686\pi \frac{\varepsilon_{eff} - 1}{\varepsilon_{r} - 1} \frac{\varepsilon_{r}}{\varepsilon_{eff}} \frac{\tan \delta}{\lambda_{g}} \quad (dB/m)$$

(26)

#### **Devices electrical characterization**

For the electrical characterization of the structures, S-parameters will be measured using a network analyser, in combination with a probe station or using 2.4 mm end launch connectors.

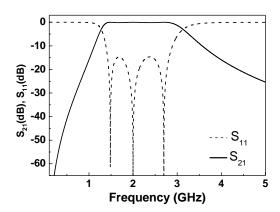

As mentioned before, measuring these parameters we are able to obtain transmission and reflection characteristics of the devices. A typical band pass filter response represented by means of S-parameters is shown in Figure 18.

Figure 18. Typical S-parameters response of a band-pass filter.  $S_{21}$  represents transmission or gain and  $S_{11}$  is the reflection loss (in dB).

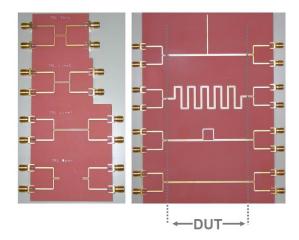

In order to obtain correct measures, a calibration process must be performed before measuring, with the goal of correcting systematic errors in the instrument, characteristics of the cables and adapters. The most typical calibrations are SOLT and TRL. SOLT (Short-Open-Load-Thru) is the simplest one and only requires connecting these standards. In some devices is necessary to remove the contribution of connectors and/or transmission lines included in the device under test. Using the same access lines in all the devices is possible to obtain accurate measurements of the designed components by means of deembedding techniques. De-embedding is a mathematical process that removes the effects of unwanted portions of the structure that are embedded in the measured data by subtracting their contribution. To this end, is necessary to perform TRL (Thru, Reflect, Line) calibration by means of a specifically-designed TRL calibration kit. Figure 19 is an example of a differential TRL kit and devices under test using the same access lines implemented in conventional PCB.

Figure 19. TRL differential calibration kit (left) and devices under test PCB (right). Extracted from [9].

Table 4 shows a summary of the electrical test vehicles and its parameter extraction.

| Test vehicle                                                            | Test vehicle<br>layout | Characterization measurements                 | Characterizatio<br>n procedure                                                                                                           | Parameters<br>extracted                               |

|-------------------------------------------------------------------------|------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Printed Microstrip<br>Ring Resonator<br>(substrate<br>characterization) | -0-                    | 2 RF ports<br>measurement<br>Network Analyzer | Frequency from 10 MHz up to GHz  Measure S- parameters → Extract ring resonant frequencies and bandwidths → Process data using equations | $\varepsilon_r$ – tan $\delta$ at several frequencies |

| TRL calibration kit<br>for de-embedding<br>(device<br>characterization) |                        | TRL calibration<br>Network Analyzer           | TRL calibration in combination with de-embedding techniques                                                                              | Corrected S-<br>parameters                            |

Table 4. Summary the electrical test vehicle and parameter extraction for inductors

#### 3.5 Rectifying diodes

There are several strategies to implement a rectifying element. Therefore, before device parameters and models are presented, it is important to analyze the different approachs and select the most suitable rectifying element.

In this section rectifying diodes fabricated by ink-jet printing were evaluated. We compare the direct current (dc) and high-frequency performance of three different rectifying diode structures, (i) a Schottky diode a (ii) diode connect TFT and (iii) a MIS diode.

Since the most challenging applications are radio-frequency-identification (RFID) tags, the emphasis was put on the ability of the rectifying elements to follow the base-carrier frequency of 13.56 MHz. A suitable diode configuration was identified and an appropriate model proposed.

#### 3.5.1 **Review**

In 2006 Poly IC presented the world first "roll-to-roll" organic RFID tag (a 64-bit tag working at a bit rate higher than 100 b/s, readout by inductive coupling at a base carrier frequency of 13.56 MHz [10,11]. More recently, full organic RFID tags for barcode replacement, generating code sequences up to 128 bits, have been demonstrated operating at the carrier frequency of 13.56 MHz [12,13].

Although impressive high frequency rectifying circuits have been reported [13-18]. All these devices use expensive fabrication technologies (vacuum sublimation and photolithography) as well as high mobility materials mostly relying on small molecules. To the best of our knowledge until now a RFID tag fabricated using all-inkjet printed devices has not been reported.

The most critical component in a RFID tag is the rectifying diode. There are basically two strategies to fabricated rectifying components, Schottky barrier diodes and diode connected TFTs. The diode connected TFT approach has the advantage of easy integration. However, TFTs have relatively long channels. By using photolithography the channel can be reduced but channel lengths below  $10~\mu m$  are not easy to produce by inkjet printing. Cantatore et al. [17] have shown that it is possible to rectify a sinusoidal signal of 13.56 MHz using a diode connected TFT. However, an ac signal with 80 V peak amplitude was required to be obtained a dc level of 10 V. Schottky based diodes perform much better. A pentacene based diode can rectify an incoming ac signal of 18 V amplitude to a dc signal of 11 V at 13.56 MHz [18].

Depending on the channel length used, the diode connected transistor requires a several hundred times lager area as compared to the Schottky diode, which translates in a larger capacitance. The capacitance may not directly limit the frequency response, but the channel length due to slow carrier transport.

Table 5 provides a summary of the main characteristics and limitations of both type of devices.

| Rectifying<br>diode       | Comments                                                                                                                                                                                                                                                   | Refs. |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Schottky<br>diode         | The cut-off frequency is limited by the carrier time-of-flight and not by the diode capacitance.  The low carrier mobility must be compensated by a thinner active layer.  For high frequency response high mobility and thin organic layers must be used. | [19]  |

| Diode<br>connected<br>TFT | Have a low current density. Requires the fabrication of large area TFTs which increases the occurrence of defects The channel length must be kept small.                                                                                                   | [17]  |

Table 5. Basic characteristics of the two approaches to fabricate rectifying diodes.

#### 3.5.2 Electrical characterization of rectifying elements

#### **Schottky diodes**

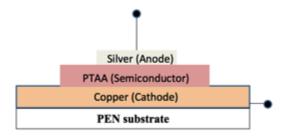

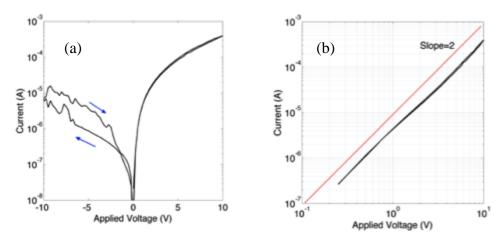

A Schottky diode structure is shown in Figure 20. This diode has a barrier at the interface between cooper and the PTAA semiconductor. This diode was fabricated outside of the TDK4PE consortium and the cooper electrode was evaporated. Although, there is a debate if these diodes can be named Schottky type diodes, for the sake of simplicity we used the conventional terminology. Current-voltage characteristics and the frequency dependence capacitance and loss are show in Figure 21. The analysis of the forward *I-V* characteristics in a log-log plot (see Figure 22) shows that the charge carrier transport is space charged limited (SCL) and follows approximately Child's law (slope 2). As it will be discussed later, this imposes an intrinsic limitation of the diode ability to rectify high frequency signals.

Figure 20. Schottky diode structure.

Figure 21. (a) I-V characteristic and (b) capacitance and loss  $(G/\omega)$  as function of frequency for a Schottky diode.

Figure 22. Log-log plot of the forward bias current-voltage characteristic showing that the slope is slightly higher than 2.

Figure 23. (a) Rectifying circuit. (b) Comparison between the input signal and the output DC signal. The load circuit uses a capacitor of 100 nF and a resistance of 1 M $\Omega$ . f=13.56 MHz.

#### **MIS** diodes

The electrical properties of rectifying diodes based on metal-insulator-semiconductor (MIS) diodes are described. The diode structure and a typical I-V curve is shown in Figure 24. Based on the device structure the MIS diode should behave as capacitor because the insulator is 1  $\mu m$  thick. The fact that there is a substantial leakage current particularly when the semiconductor/insulator interface is driven into accumulation, suggest that the insulator is in reality thin enough to allow current passing trough. We propose that the dielectric has pinholes, which are filled by the top semiconductor layer. The system is in reality nanostructured dielectric/semiconducting matrix as show in Figure 25. When negative bias is applied in the dielectric a high free carrier density is induced in the semiconductor. At local thinner regions as show in Figure 25 these carriers can tunnel across the dielectric. When a negative bias is applied to the dielectric no free carriers are induced in the semiconductor and the leakage is substantially smaller. This view explains the asymmetric I-V characteristics.

These diodes have a rectification ratio of 120 at |10V|. They behave as non-linear resistors. The forward I-V curve follows space charge limited behavior in all the voltage range (see Figure 26). Capacitance-voltage characteristics confirm the absence of depletion layers associated with interfacial barriers (see Figure 27b). The decrease in the

capacitance with increasing bias is due to a high leakage current that bypass the diode capacitance.

Figure 24. (a) Schematic representation of a MIS-Diode, (b) typical current voltage characteristic showing an asymmetric behaviour.

Figure 25. Schematic diagram showing the proposed mechanism to explain non-symmetric I-V curves in MIS structures.

Figure 26. Electrical characteristics of MIS diode. (a) Semilog plot showing the existence of hysteresis in reverse bias. (b) Log-log plot of the forward bias current.

Figure 27. (a) Capacitance and loss as function of the frequency (b) Capacitance voltage plot recorded at a test frequency of 1 kHz. The diode area is  $1 \text{ mm}^2$ .

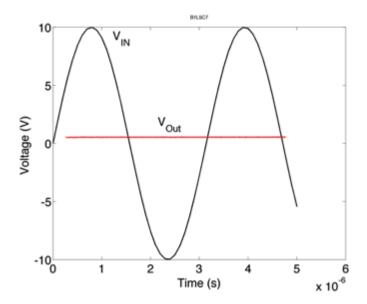

When the MIS diode is mounted in a rectifying circuit with C=470 nF and R=1 M $\Omega$  the signal is strongly attenuated for frequencies above 1 MHz. At the operating frequency of 2 MHz the DC rectified output reaches only 0.5 V for an input amplitude of |10V| as shown in Figure 28. These diodes do not fulfill the requirements for a 13.56 MHz rectifier circuit. Accordingly to Altazin et al. [19] the reason is because the charge carrier mobility is too low. Although, the oxide is thin at local regions, it must have traps, which limit the carrier flow.

Figure 28. Rectified signal at 2 MHz the load capacitor is 470 nF and the load resistance of 1 M $\Omega$ .

Figure 29 shows the frequency dependence of  $V_{\text{out}}/V_{\text{in}}$  .

Figure 29. Frequency dependence of  $V_{out}$  / $V_{in}$  for a MIS diode is connected in a rectifying circuit. The load is a RC parallel circuit (R=1 M $\Omega$ , 100 nF).

#### Diode connected TFT.

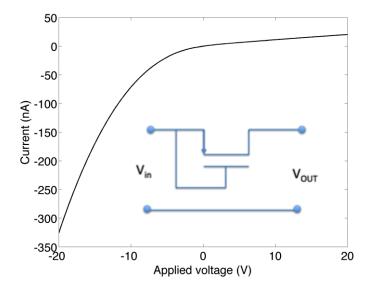

Figure 30 shows the current voltage characteristic of a diode connected TFT. Under a forward bias of -20 V, it can supply 250 nA. Rectifying circuits were tested but the signal is strongly attenuated in the kHz range. This limitation is caused by a long channel length (L=40  $\mu$ m) and low charge carrier mobility ( $10^{-3}$  cm²/V.s). This diode was not considered an option for high frequency rectifying circuits because it requires and optimization not compatible with ink-jet printing (very small channel lengths and high mobility materials).

Figure 30. *I-V* characteristic of a diode connected TFT. The Inset shows the circuit configuration. The area of the TFT is 2.5x1.8 mm<sup>2</sup>.

### **Summary**

All the diode structures were characterized in rectifying circuits. The conclusions are summarized in Table 6. Only the Schottky diode perform reasonable well at frequencies used in RF tags (13.56 MHz). Both diode connected TFTs and MIS diodes cannot produce rectified DC signals for frequencies above 1 MHz.

| Rectifying<br>diode       | Characteritics                                                                                                                                                                                                                                                                                             |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Schottky<br>diode         | Rectification ratio: $200 @ 5V $<br>Forward current: $0.3 \text{ mA} @5 \text{ V}$<br>Reverse leakage current: $0.5 \mu\text{A}$<br>SCL conduction: $I \propto V^{\alpha}$ with $\alpha$ =2 (Child's law)<br>Area: $1 \text{mm}^2$                                                                         |

| MIS diode                 | Rectification ratio: 120 @  10V  Forward current: 0.3 mA @ 10 V Reverse leakage current: 10 $\mu$ A SCL conduction: $I \propto V^{\alpha}$ , $\alpha$ =[2 - 4] Frequency response limited by: the high thickness of the semiconductor layer (carrier transport in the semiconductor) Area: $1 \text{mm}^2$ |

| Diode<br>connected<br>TFT | Rectification ratio: $25 @  20V $<br>Forward current: $250 \text{ nA} @ 20V \text{ (Area: } 2.5 \times 1.8 \text{ mm}^2\text{)}$<br>Reverse leakage current: $10 \text{ nA}$<br>Carrier transport: TFT model I $\propto V^2$<br>Frequency response limited by the TFT channel length                       |

Table 6. Rectifying diodes characteristics.

### 3.5.3 Diode model in a rectifying circuit

The non-linear nature of the rectifying process prevents to apply any standard small signal approach. The diode cannot be simulated alone, but together with the load resistance and capacitance in a time dependent approach. The time dependent drift and diffusion equations have to be numerically solved to model the carrier transport within the diode, coupled with time dependent circuit equations. This approach has been developed by Altazin et al. [19] and it is adopted here.

The time dependent operation of the diode is modeled by solving the continuity equation coupled with the Poisson equation.

Considering that applied voltage  $V_a$  is related to the input voltage  $V_{in}$ ,  $V_0$  and the output voltage  $V_{out}$  by the following set of equations:

$$V_a(t) = V_{out}(t) - V_{in}(t)$$

(27)

$$C\frac{dV_{out}}{dt} + \frac{V_{out}}{R} = i_d(V_{out}(t) - V_{in}(t), t)$$

(28)

Where C and R are the external capacitance and resistance of the rectifying circuit, and  $i_d$  the current flowing through the diode.

In the high frequency regime, simulations are time-consuming and a simplified model has been proposed by Altazin et al. [19]. In their approximation the conductance is modeled by a time dependent function  $G_d(V,t)$ , responding to the applied signal with a characteristic delay time  $\tau$ . The dynamic of this response is empirically modeled by the following first order differential equation

$$\frac{dG_d}{dt} = \frac{G_d(V) - G_{do}(V)}{\tau} \tag{29}$$

A good approximation of the characteristic time constant,  $\tau$  in a unipolar device is proportional to the carrier time-of-flight, given by:

$$\tau = \frac{L^2}{\mu_p(V_a - V_T)} \tag{30}$$

Here  $V_a$  represents the applied bias on the diode and  $V_T$ , an empirical threshold voltage. L is the polymer thickness and  $\mu_p$  the charge carrier mobility. In absence of traps this threshold voltage simply given by the built in potential. In all case, it can be extracted using the semilogarithmic plot of the static I-V curve, and its value is equal to the voltage at which the I-V curve, in the forward regime, is not an exponential anymore.

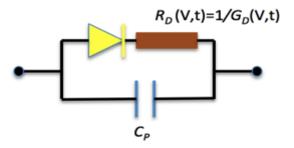

The basic diode model is basically illustrated in Figure 31 as discussed above the  $G_d$  (V,t), is considered to responding to the applied signal with a characteristic delay time  $\tau$  as described by equation 30.

Figure 31. Basic model for a Schottky barrier diode. The resistance is frequency dependent and related with the charge carrier transport limitations at high frequencies.

## 3.5.4 Parameter extraction procedure

| Model parameter                                                                                                                                                                                                                                                    | Parameter extraction procedures                                                                                                                                                                          | Equipment<br>Test vehicle                                             |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| Parameters required to simulate the diode high frequency response                                                                                                                                                                                                  |                                                                                                                                                                                                          |                                                                       |  |  |  |

| Geometric capacitance $C_p$ (F/cm <sup>2</sup> )                                                                                                                                                                                                                   | Measure the capacitance at a resonable high frequency ( $f > 100 \text{ kHz}$ ) to elminate possible relaxation caused by interfacial effects such as electrode polarization or depletion layer effects. | Impedance<br>Analyzer<br>(Schottky diode)                             |  |  |  |

| Threshold volatge $oldsymbol{V_T}$ (v)                                                                                                                                                                                                                             | Extracted from the semilogarithmic plot of the static <i>I-V</i> curve, and its value is equal to the voltage at which the <i>I-V</i> curve, in forward bias, is not an exponential anymore.             | <i>I-V</i> meter<br>(Schottky diode)                                  |  |  |  |

| Trap concentration $N_t$ (cm <sup>-3</sup> ) Doping concentration $N_a$ (cm <sup>-3</sup> ) Hole concentration at injecting contact $N_h$ (cm <sup>-3</sup> ) Mobility $\mu$ (cm <sup>2</sup> /(Vs)) Work function difference between the two contacts $\Phi$ (eV) | By fitting the static <i>I-V</i> characteristic of diodes of several thicknesses, fabricated using the same process.                                                                                     | I-V curves of<br>diodes of several<br>thicknesses<br>(Schottky diode) |  |  |  |

| Cut-off frequency $m{f_c}$ (Hz)                                                                                                                                                                                                                                    | Estimated from the measured $V_T$ and the active diode layer thickness ( $L$ ). $V_A$ is the applied voltage.                                                                                            | $f_c = \mu \frac{V_A - V_T}{L^2}$                                     |  |  |  |

| Parameters required to specify the operation point in a rectifier circuit                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                       |  |  |  |

| Maximum forward current  I <sub>Dfmax</sub> (A/cm²)  Reverse leakage current  I <sub>leakage</sub> (A/cm²)                                                                                                                                                         | Measure the I-V curve in the highest voltage range tolerable by the diode.                                                                                                                               | <i>I-V</i> meter<br>(Schottky diode)                                  |  |  |  |

| Reverse breakdown voltage $V_{Rmax}$ (V)                                                                                                                                                                                                                           | Apply a reverse voltage to cause breakdown or a very high reverse leakage current.                                                                                                                       | I-V meter<br>(Schottky diode)                                         |  |  |  |

Table 7. Summary of the electrical test vehicle and parameter extraction for Schottky diodes.

## 3.6 Organic Thin Film Transistors (OTFTs) models (new - August Report)

The physical model than conveniently describes the OTFT behavior is the Unified Compact Model and parameter Extraction Method (UMEM) developed by A. Cerdeira and M. Estrada [20-26].

### 3.6.1 Parameter extraction procedure

The model is a physical based model and allows the extraction of DOS parameters of the organic semiconductor material used in the device. The mobility in OTFTs is based on analytical expressions obtained under the assumption that in all operating range of OTFTs, the concentration of localized charge predominates over free charge. The mobility expression can be written in the form of a power dependence of the gate voltage, allowing the use of the procedure UMEM (Unified model and extraction methodology) to determine all parameters to model the mobility, as well as the electrical characteristics of these transistors. With this method, DOS parameters, considering the typical exponential distribution assumed for OTFTs, can be easily extracted from the transfer characteristic of the device.

In the UMEM model the drain current in the linear region and for  $V_{GS} > V_T$  can be written as

$$I_{DS(lin)} = \frac{K}{V_{AA}^{\gamma}} (V_{GS} - V_T)^{1+\gamma} V_{DS}$$

(31)

Or alternatively in the saturation region

$$I_{DS(sat)} = \frac{1}{2} \frac{K}{V_{\Delta\Delta}^g} \left( V_{GS} - V_T \right)^{2+g}$$

(32)

The field effect mobility  $\mu_{FET}$  is assumed to be given by

$$\mu_{FET} = \mu_0 \cdot \frac{(V_{GS} - V_T)^{\gamma}}{V_{AA}^{\gamma}}$$

Where  $V_{AA}$ , K and  $\gamma$  are parameters to be extracted.

$$g = 2\frac{T}{T_0} - 2 \tag{33}$$

T is the absolute temperature and  $T_0$  the characteristic temperature of the DOS

The energy distribution of the DOS  $g_d(E)$ , is expressed as

$$g_d(E) = g_{do} \exp \frac{\Re E}{\oint K_h T_o} \frac{\ddot{o}}{g}$$

(34)

where  $K_b$  is the Boltzmann constant.

$\gamma$  can be extracted from the transfer curves (in the linear region) when plotted as:  $I_{DS}^{1/(1+\gamma)}$  versus  $V_{GS}$ . This can be done by trial and error or by an integration procedure [20,23].

$$H(V_{GS}) = \frac{\int_{DSin}^{V_{GS}max} I_{DSin}(V_{GS}) dV_{GS}}{I_{DS}Iin(V_{GS})}$$

(35)

Using the measured linear transfer characteristics  $I_{DSlin}$  in the integral function, the slope P and intercept of  $H(V_{GS})$  are calculated

$$V_T = \frac{Intercept}{P} \tag{36}$$

and

$$\gamma = \frac{1}{p} - 2 \tag{37}$$

since

$$\gamma = 2\frac{To}{T} - 2 \tag{38}$$

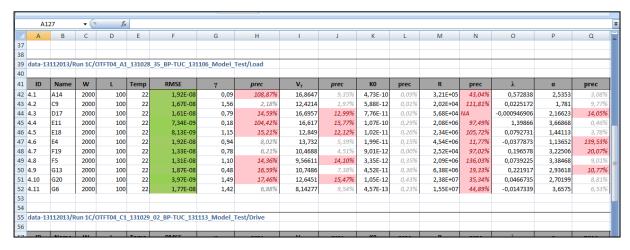

$T_o$  is calculated after extracting  $\gamma$