#### INFORMATION AND COMMUNICATION TECHNOLOGIES

#### COORDINATION AND SUPPORT ACTION

# **EUROSOI+**

# **European Platform for Low-Power Applications on Silicon-On-Insulator Technology**

Grant Agreement nº 216373

# D4.4 EUROSOI+ state-of-the-Art final report

Due date of deliverable: 30-06-2011 Actual submission date: 30-06-2011

Start date of project: 01-01-2008 Duration: 42 months

Project coordinator: Prof. Francisco Gámiz, UGR

Project coordinator organisation: University of Granada, Spain Rev.1

### **Table of contents**

| Project co-funded by the European Commission within the Seventh Framework Programme (FP7) |                                                                                       |   |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|

| Dissemination Level                                                                       |                                                                                       |   |

| PU                                                                                        | Public                                                                                | X |

| PP                                                                                        | Restricted to other programme participants (including the Commission Services)        |   |

| RE                                                                                        | Restricted to a group specified by the consortium (including the Commission Services) |   |

| CO                                                                                        | Confidential, only for members of the consortium (including the Commission Services)  |   |

# **INDEX**

| Section 1. Deliverable Description | 3  |

|------------------------------------|----|

| ·                                  |    |

|                                    |    |

| Section 2. State of the Art Report | .6 |

# Section 1. Deliverable description.

The EUROSOI network embraces a broad range of research areas related to Silicon-On-Insulator technology (from materials to end-user electronic applications in traditionally strong European industrial sectors such as automotive, communications, space).

The aim of the EUROSOI network was to establish Europe as the international scientific leader in Silicon on Insulator (SOI) Technology, Devices, Circuits and Systems. EUROSOI has networked together the SOI related resources and expertise already existing in Europe and has successfully promoted different activities needed to reach the scientific leadership mentioned above. The final goal of EUROSOI was to provide the European Industry with easier access to the large amount of expertise and invaluable experience available in Europe, so that it will become the leading SOI player in the international arena. Therefore, the EUROSOI co-ordination efforts were focused on fostering those activities which contribute to improving the role of the European semiconductor industry with regard to SOI and to the knowledge that will enable Europe to compete internationally. These goals were realized by achieving the following objectives:

# 1) Increase the knowledge and expertise about SOI technology in Europe by enhancing interaction and synergy between academic groups and industry.

EUROSOI is a platform that promotes the exchange of knowledge and experience between its partners. To achieve this, we have created a virtual research centre to give answers to specific problems about SOI, and which can be found at www.eurosoi.org. It contains excellent resources, including different sections such as Landmark SOI publications, and links to abstracts for more than 1000 relevant articles in research journals around the world (EUROSOI Virtual Journal).

2) Foster the exchange of knowledge between research groups working on materials, devices, circuits and electronic end-user applications, through the organization of Working Group meetings, and EUROSOI Workshops (UGR-Granada-2005, GRENOBLE INP-Grenoble-2006, IMEC-Leuven-2007, Tyndall-Cork-2008)

This vertical integration is essential in order to ensure the co-evolution of technology and applications so that technology advances are exploitable in innovative products and services. Particular attention has been paid to users' needs and to usability and accessibility of SOI technologies and applications.

# 3) Collect, filter and provide structured information about SOI in Europe

During this first stage of EUROSOI running, we have elaborated the SOI State-of-the-Art (SoA) Report. This report gives a summary of the European expertise in relation to SOI activities ongoing worldwide.

### 4) Elaborate the European SOI Roadmap

The recommendations and conclusions of the SoA report have been used to identify scientific priority areas, and formulate research and development strategies about SOI technology, that is to say, to elaborate the European SOI Roadmap. This report will be used in this second stage as the starting point for the elaboration of proposals for advanced research projects and to promote their joint submission to the appropriate funding agencies. The SOI Roadmap is a helpful tool for European researchers since it identifies the future needs of SOI technology in EUROPE, foresees its physical limits, and provides, when possible, alternative solutions.

#### 5) Promote industrial participation in the Network activities

We have informed industry about relevant progress in SOI technology and provided a feedback loop for industrial mid- and long-term interests. To achieve this objective, the key industrial partners in the field are members of the management board, and co-leads with another partner, the different working groups in which the area of interest of the network has been divided.

#### 6) Organize and advertise SOI events

Special attention has been paid in the fast distribution of the results of the network through the organization and sponsoring of workshops, working groups, training courses and tutorials, project results, job opportunities, grants. 18 student grants have been given to attend EUROSOI Workshops.

#### 7) Manage funding for short technical visits to other labs

We have also promoted the scientific exchange between partners through a unified management structure that encourages staff mobility, staff exchanges, and joint execution of research projects. Fourteen (14) short scientific visits have been carried out funded by EUROSOI.

#### 8) Interaction between existing SOI projects

Along these years we have promoted:

- i. The interaction between existing SOI projects at national and European levels, and facilitated the coordination of their work.

- ii. The dissemination of available knowledge and pertinent results in new research projects to the industry.

- iii. Through the elaboration of the EUROSOI "Who is Who" guide, organization of working group meetings and EUROSOI Workshop.

### 9) Training activities for young scientists

We have developed initiatives to retain qualified young scientists and engineers within Europe, thereby avoiding the brain escape. Two training courses have been organized, with more than 60 attendants and involving, as lecturers, the best specialists in SOI topics all over the world.

#### 10) Beyond microelectronics: Towards nanotechnology

We have addressed and fostered initiatives beyond CMOS, taking advantage of the SOI knowledge to develop platforms for further technological development in nanotechnology and not only in microelectronics.

To achieve the objectives of this project it is necessary i) to promote interaction between scientists, ii) to take advantage of the existing experiences within the research groups, iii) to join forces to maximize the synergy between

the individual skills, thus obtaining the best achievable global results, and iv) to provide an appropriate communication channel between academic groups and industrial production centres.

One of the key deliverables of EUROSOI is the State of the art (SoA) report. The goal of this report is to provide an extended review of the past and present of Silicon-on-Insulator technology, based on the collective knowledge of researchers in the field (in this case, the partners of EUROSOI). The report wants to sum up the present situation of SOI technology, highlighting not only scientific advances but also weaknesses, i.e., those aspects which require more research effort. The main idea is to compile, filter and present data on SOI topics in a way that is easily accessible by industrial partners, so that they can decide whether or not to incorporate this information into their R&D work or production process. The work has directly involved the six WG leaders, but also the experience and expertise of the other partners has been fundamental.

■ The report would have nine chapters.

| Topic                                    |

|------------------------------------------|

| SOI Materials.                           |

| Devices. Characterization.               |

| Devices. Fabrication Technologies.       |

| Devices. Physics.                        |

| Simulation and modeling.                 |

| Reliability of SOI devices and circuits. |

| Physics. Advanced Device Concepts.       |

| Circuit design.                          |

| End-users and Industrial Applications.   |

#### ■ Each chapter should have

- Introduction

- Extended review of the past and present of Silicon-on-Insulator technology in the chapter area. Research projects related to SOI.

- Identification of not only scientific advances but also weaknesses,

i.e., those aspects which require more research effort. Main publications in the field.

- All this should be done in a way that is easily accessible by industrial partners, so that they can decide whether or not to incorporate this information into their R&D work or production process.

# Section 2. State of the Art Report

### **Table of Contents**

| 1. SOI Materials                                                                                                                         | 10       |

|------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1. Commercially available SOI substrates and key manufacturing steps                                                                   | 11       |

| 1.1.1. SIMOX                                                                                                                             | 12       |

| 1.1.2. Wafer Bonding related techniques                                                                                                  | 14       |

| 1.1.2.1 BSOI/BESOI                                                                                                                       | 14       |

| 1.1.2.2 Layer transfer based on Porous silicon layers (ELTRAN <sup>TM</sup> )                                                            | 15       |

| 1.1.2.3 Layer transfer based on ion implantation (Smart Cut <sup>™</sup> )                                                               | 16       |

| 1.1.2.4 Basic wafer bonding process and evolution trends                                                                                 | 18       |

| 1.1.3. Others                                                                                                                            | 19       |

| 1.1.4. CVD-epitaxy for SOI                                                                                                               | 24       |

| 1.1.5. Liquid-phase epitaxy for SOI                                                                                                      | 25       |

| 1.2. New SOI-Like materials in development                                                                                               | 26       |

| 1.2.1. High mobility SOI                                                                                                                 | 26       |

| 1.2.1.1. High mobility I: Strained Si on Insulator Wafers                                                                                | 26       |

| 1.2.1.2. High mobility II: Ge on Insulator Wafers                                                                                        | 32       |

| 1.2.1.3. Crystalline orientation effect and Hybrid orientation SOI                                                                       | 36       |

| 1.2.2. New buried insulators                                                                                                             | 38       |

| 1.2.3. Complex SOI structures                                                                                                            | 40       |

| 1.3. Material characterization                                                                                                           | 46       |

| 1.3.1. Electrical characterization                                                                                                       | 46       |

| 2. Devices. Characterization                                                                                                             | 48       |

| 2.1. C-V measurements                                                                                                                    | 49       |

| 2.2. Diodes: Lifetime characterization                                                                                                   | 51       |

| <ul><li>2.3. MOSFET characterization and parameter extraction methods</li><li>2.4. Transport measurements in MOS-like devices.</li></ul> | 53<br>55 |

| 2.5. Phonons in SOI                                                                                                                      | 57       |

| 2.6. Interface characterization by Charge Pumping                                                                                        | 59       |

| 2.7. Electro-luminescence techniques                                                                                                     | 61       |

| 2.8. Noise and fluctuations                                                                                                              | 64       |

| 2.9. Transient and history effects                                                                                                       | 66       |

| 2.10. Floating Body effects (including gate-induced FBE                                                                                  | co       |

| and Meta-Stable Dip effect) 2.11. Ultra-thin film effects in MOSFETs                                                                     | 68<br>70 |

| 2.12. Self-heating (+ High T°)                                                                                                           | 70<br>72 |

| 2.13. Special device characterization (multiple gates, high voltage FETs,)                                                               | 74       |

| 2.14. SOI High Voltage Transistor Characterization                                                                                       | 76       |

| 2.15. High Voltage Characterization During Production                                                                                    | 77       |

| 3. Devices. Fabrication Technology                                                                                                       |          |

| 3.1. SOI CMOS Technology                                                                                                                 | 79       |

| 3.1.1. Field isolation: LOCOS, mesa, trench isolation                                                                                    | 79<br>82 |

|                                                                                                                                          |          |

| 3.1.3. Source and drain engineering: silicide source ar       | nd drain, elevated |

|---------------------------------------------------------------|--------------------|

| source and drain                                              | 86                 |

| 3.1.4. Gate stack, gate electrode materials, gate dielectrode | etric 89           |

| 3.2. High Voltage Devices                                     | 92                 |

| 3.2.1. LDMOS processes                                        | 92                 |

| 3.2.2. Vertical SOI High Voltage Processes                    | 95                 |

| 3.2.3. Bipolar SOI processes                                  | 97                 |

| 3.3. RF and Power Devices                                     | 103                |

| 3.3.1. SOI LDMOS RF-Power Transistors                         | 103                |

| 3.4. Optical SOI technology                                   | 106                |

| 3.4.1. SOI waveguides                                         | 106                |

|                                                               |                    |

| 3.4.2. SOI based photonic bandgap structures                  | 110<br>113         |

| 3.4.3. Hybrid SOI-organic optical structures                  | 113                |

| 4. Devices. Physics                                           | 115                |

| 4.1. Classical SOI MOSFET                                     | 116                |

| 4.1.1. Partially-depleted SOI transistors                     | 116                |

| 4.1.2. Fully-depleted SOI transistors                         | 116                |

| 4.1.3. Ultra-thin SOI MOSFET                                  | 117                |

| 4.1.4. Accumulation Mode MOSFETs                              | 117                |

| 4.2. High Voltage and Power Devices                           | 119                |

| 4.2.1. High-Voltage devices                                   | 119                |

| 4.2.2. Power Devices                                          | 121                |

| 4.3. RF Devices                                               | 125                |

| 4.3.1. SOI CMOS RF transistors                                | 125                |

| 4.3.2. SOI bipolar transistors                                | 129                |

| 4.4. SOI MEMS                                                 | 135                |

| 4.4.1. MEMS processes                                         | 135                |

| 4.4.2. Ultrathin SOI nano-acelerometers                       | 137                |

| 4.4.3. Bulk-mode SOI MEM resonators                           | 137                |

| 4.5. Optical SOI waveguides                                   | 141                |

| 4.5.1. GAA MOS capacitors light modulators                    | 141                |

|                                                               | 143                |

| 4.5.2. SOI Photonic Integrated Circuits                       |                    |

| 4.6. 3-Dimensional Integration                                | 145                |

| 4.7. Novel Devices                                            | 147                |

| 4.7.1. Resonant Tunnelling Diodes                             | 147                |

| 4.8. Operation at high temperatures of SOI devices            | 156                |

| 4.8.1. High-Temperature Subthreshold Slope in SOI M           |                    |

| 4.8.2. High-Temperature Off-State Current in SOI MOS          | SFETs 159          |

| 5. Simulation and modelling                                   |                    |

| 5.1. Process and technology simulation                        | 167                |

| 5.2. Device Simulation                                        | 176                |

| 5.2.1. Introduction                                           | 176                |

| 5.2.2. Device models and model approximations                 | 178                |

| 5.2.3. Capabilities of Commercial Simulation Tools            | 182                |

| 5.2.4. Research Level Simulators                              | 188                |

|                                                               |                    |

| 6. Reliability of SOI devices and circuits                    |                    |

| 6.1. Wafer Level Reliability                                  | 201                |

| 6.1.1. Gate-oxide quality – TDDB                              | 202                |

| 6.1.2. Hot-carrier degradation                                | 202                |

| 6.1.3. Negative Bias Temperature Instability (NBTI)           | 203                |

| 6.2. Electro – Static Discharge (ESD)                         | 204                |

| 6.3. Latch-Up                                                 | 204                |

| 6.4. Electro-migration                                           | 205 |

|------------------------------------------------------------------|-----|

| 6.4.1. Junction spiking                                          | 205 |

| 6.4.2. Wiring                                                    | 205 |

| 6.4.3. Thermal fatigue                                           | 205 |

| 6.4.4. New Materials                                             | 205 |

| 6.5. Radiation Effects                                           | 206 |

| 6.6. Mechanical effects: Strain, thermal cycling                 | 206 |

| 6.7. Application-specific tests                                  | 208 |

| 6.7.1. High-voltage and power products                           | 208 |

| 6.7.2. Sensors, Actuators                                        | 208 |

| 6.7.3. Packaging                                                 | 208 |

|                                                                  |     |

| 7. Physics. Advanced Device Concepts                             |     |

| 7.1. Transport enhanced FETs                                     | 212 |

| 7.1.1. Strained Si, Ge, SiGe, SiGeC, SON or other semiconductor  |     |

| on SOI                                                           | 214 |

| 7.2. Metal gates                                                 | 219 |

| 7.3. Ultrathin body SOI FETs                                     | 223 |

| 7.4. Source and drain engineering                                | 227 |

| 7.4.1. Metallic S/D junctions                                    | 228 |

| 7.4.2. Non-overlapping S/D junctions                             | 228 |

| 7.5. Double gate devices                                         | 233 |

| 7.5.1. Ground plane SOI transistor                               | 234 |

| 7.5.2. Volume inversion transistors                              | 234 |

| 7.5.3. Asymmetrical DGSOI transistor                             | 234 |

| 7.5.4. Velocity modulation transistors (VMTs)                    | 234 |

| 7.6. Multigate devices                                           | 239 |

| 7.6.1. FinFETs                                                   | 239 |

| 7.6.2. Vertical transistors                                      | 241 |

| 7.6.3. Gate-all-around (GAA) and G4-FETs                         | 241 |

| 7.7. Ballistic transistors                                       | 247 |

| 7.8. High-K materials                                            | 249 |

|                                                                  |     |

| 8. Circuit Design                                                | 251 |

| 8.1 Transistor modelling for circuit simulators                  | 252 |

| 8.1.1. Partially-depleted                                        | 256 |

| 8.1.2. Fully-depleted                                            | 258 |

| 8.1.3. Double and Multiple Gate SOI MOSFETs                      | 260 |

| 8.2. Digital Logic                                               | 264 |

| 8.2.1. High-Speed (Microprocessor, Data Communications)          | 264 |

| 8.2.2. Low-power / Low-voltage.                                  | 267 |

| 8.2.3. Ultra Low Voltage                                         | 270 |

| 8.3. Memories                                                    | 274 |

| 8.3.1. SRAM                                                      | 274 |

| 8.4. Analog & RF                                                 | 279 |

| 8.4.1. Analog and RF characterization techniques                 | 279 |

| 8.4.1.1 Wide frequency band characterization at room temperature | 279 |

| 8.4.1.2. DC to high-frequency characterization from low to high  |     |

| temperature (77-400K)                                            | 279 |

| 8.4.2. HR substrates and Crosstalk analysis                      | 287 |

| 8.4.3. RF modeling (small signal, noise)                         | 296 |

| 8.4.4. Analogue circuits                                         | 298 |

| 8.4.5. RF Design                                                 | 301 |

|                                                                  |     |

| 9 Endusors & Industrial Applications                             | 303 |

| 9.1. Radiation-hard Products (Aeronautics & Space Applications)            | 304 |

|----------------------------------------------------------------------------|-----|

| 9.2. High-temperature Products (Oil & Gas, Aeronautics & Space, Automotive |     |

| Applications)                                                              | 307 |

| 9.3. High-speed Products (Microprocessors & Data Communications)           | 310 |

| 9.4. High-voltage Products (Audio, Power Management and Automotive         |     |

| Applications)                                                              | 313 |

| 9.5. Ultra-low-power Ultra-low-power applications (Watches,)               | 316 |

| 9.6. RF & Microwave Products (Wireless Applications)                       | 318 |

|                                                                            |     |

# **CHAPTER I**

# **SOI Materials**

**Chapter 1. SOI Materials**

Section 1.1. Commercially available SOI substrates and key manufacturing steps Subsections

1.1.1. SIMOX

1.1.2. Wafer Bonding related techniques

1.1.3. Others

Date of Issue: Dec - 2010 Partner: SOITEC, Chalmers, CEA-LETI.

#### Abstract

This section intends to list and update the main techniques existing today for the fabrication of SOI substrates on a commercial basis, as well as the main actors and Vendors. Key manufacturing steps and limitations will be reviewed for each process, calling for further improvements in some areas.

#### Introduction

This section intends to list the main techniques existing today for the fabrication of standard SOI substrates on a commercial basis, with a focus on the new events, main actors and remaining challenges for the future.

Many good books and review papers [1-6] already exist on the topic. In these documents, the reader will be able to find a thorough description of all the possible techniques to make SOI substrates. Here, we will focus first on those techniques that are used today to (or have the potential to) produce commercially large volume quantities of SOI materials with appropriate quality. In that respect, some very-well known techniques such as Zone Melting Recrystallization (ZMR), Epitaxial Lateral Overgrowth (ELO), Full Isolation with Porous oxidized silicon (FIPOS) etc ... will not be addressed.

Consequently, mainly SIMOX and wafer bonding techniques (BSOI, Smart Cut, ELTRAN) will be reviewed, as well as some other more marginal but existing technologies such as SOS (Silicon On Sapphire) and SON (Silicon On Nothing).

This document will not describe all the details of those selected techniques but will give an overview of the main achievements and possibilities offered by each of them. Market applications targeted by each of them will be addressed mainly through the segmentation "thin/thick SOI products".

Last, we'll focus on the remaining challenges corresponding to each technique to identify the different R&D axes that need to be addressed in the future. All those technical challenges do not necessarily have to be tackled by European partners. Some recommendations will be given on which of those R&D activities should be supported, based on the picture of the strength and weakness of Europe.

#### 1.1.1. SIMOX

Although many more steps are actually needed, two basic steps define this process. (1) Implantation of high dose of oxygen and (2) high temperature annealing (>1320°C) . Oxygen implantation is performed within a bulk substrate to separate (insulate) the active layer from the rest of the bulk substrate by the formation of an oxygen-rich silicon layer. High temperature annealing is afterwards performed to promote oxygen diffusion / precipitation for the buried  $SiO_2$  formation / densification, and to cure the many crystalline defects created in the silicon by the implantation of heavy oxygen ion species.

The buried oxide (BOX) thickness is fixed by the oxygen dose. First generations of SIMOX materials (called "standard SOI") had typical BOX thicknesses of about 4000 Å corresponding to ion dose in the range of  $1.5 \cdot 10^{18}$  O+/cm². Thicker BOX is not available, which makes the use of SIMOX wafers difficult if not impossible for certain applications (Power applications for instance). Thinner BOX substrates are available or are in development, such as the so-called "low dose SIMOX" wafers. In this case 1000-1500 Å thick BOX can be achieved and is available commercially. One advantage for the SIMOX approach going to thinner BOX is the cost and throughput since the high dose implantation step is probably one of the most limiting factors of the process. The main risk with lowering the oxygen dose (hence the BOX thickness) is the existence of shorts through the BOX (discontinuities in the BOX called "pipes"). Last, it should be noticed that due to the narrow process windows for the BOX synthesis by the SIMOX process (limited process flexibility), such wafers are not available at any BOX thickness but only at some discrete values: for instance 3800, 2000, 1450, 1000Å depending also on the supplier.

The Si thickness is primarily fixed by the implantation energy. Standard dose SIMOX processes use energies in the 100-200keV range, which enable to realise SOI layers as thick as 2000Å. Thinner SOI (lower implantation energy) processes do exist. Adjustments to the SOI thickness may be done at the final stage: (i) towards thick films by growing a final epitaxial layer on the SOI or (ii) towards thin films by thinning the SOI (by sacrificial oxidation for instance).

Still those SIMOX wafers are in the "thin" SOI segment and address more particularly CMOS applications.

In order to improve both the BOX integrity (pipes, interface sharpness, breakdown voltage, ..) and the SOI quality (oxygen precipitates, dislocations, stacking faults, ..) many different improvements have accompanied the now long history of SIMOX:

- very high temperature anneals: 1320°C which is beyond temperature allowed by standard furnaces.

- ITOX (Internal Oxidation) process consisting of growing further the already formed buried oxide layer: a very high temperature oxidation (1320°C) allowing oxygen atoms to penetrate and diffuse through the SOI to react with the SOI/BOX interface

- Control of temperature during implantation: especially heating around 600°C prevents too many crystalline defects to form, which in turn leads to lower final dislocation densities

- multiple implantation steps performed at different temperatures, with or without intermediate annealing steps

• etc ...

On the process side, further improvements are still necessary to improve thickness control and uniformity, roughness, pipes and BOX integrity, SOI defectivity (HF defects, dislocations, ...), Light Point Defects, interface sharpness (SOI/BOX and BOX/handle substrate), thin BOX substrates (below 800 Å).

Beyond the needs for quite specific furnaces (1320°C, in large diameters), the high dose oxygen implanter is the critical and non-standard equipment limiting a broader diffusion of this technology. Among others, the specifics are:

- Need for oxygen species implantation,

- High dose (first throughput limiting factor of the process),

- Dose uniformity (as thickness uniformities and pipe densities directly depend on them),

- Heating and temperature control during implantation (500-700°C),

- Importance for such high doses of sputtering of internal implanter walls and parts, generating metallic contamination and particles (which in turn play a critical role on BOX homogeneity).

Basically two main suppliers are addressing this equipment market: IBIS Technology Corp. in the US and Hitachi in Japan.

Concerning the industrial exploitation of the SIMOX process and the associated SOI wafer market:

Europe is absent. Only SOITEC (supported by CEA-LETI) used to exploit this technology with a leading position up to the mid 90's before switching to a wafer bonding technology: Smart  $Cut^{TM}$ ).

In the US, IBIS Technology Corp. [8] has been the main and only US supplier with a strong position worldwide. Their business model until the summer 2004 was to develop the implanters and to commercialize the SOI wafers. During the summer 2004 however, they announced that they exit the wafer business to focus on their equipment business [9]. Their SIMOX deal with MEMC was also announced at the same time to be terminated [9]. Indirectly, one of the main players for SIMOX material in the US (with a worldwide leadership) has been IBM [10] who had a leading position for the development of further generations of SIMOX material (see for instance late "MLD: Modified Low Dose" processes). IBM has been manufacturing internally such wafers for some of their needs, starting in its early device R&D phases. This material technology had also been licensed to IBIS.

In Japan, SUMCO (Sumitomo Metals + Mitsubishi Materials) is probably the leader today for the supply of SIMOX materials [11]. Komatsu and Nippon Steel have also had in the past some SIMOX material related activities.

In China, SIMGUI, a company recently created by the Shangaï Institute of Metallurgy is also proposing SIMOX wafers [12].

#### 1.1.2. Wafer Bonding

Although it has been known and studied for several decades now, wafer bonding technology is quite a new manufacturing module that has been industrially introduced only recently, driven in particular by SOI material technologies as well as by MEMS. It is a tool that is used in very similar ways for several different SOI material manufacturing processes. Several excellent books and review exist on the science and technology of wafer bonding: see for instance [1-7].

Those techniques also basically share the way the buried oxide is formed. In general, a standard oxide layer (thermal or deposited oxide) is formed on the surface of at least one of the two surfaces to be bonded. In this respect, the final BOX thickness value is much more flexible than for the SIMOX process. It can vary continuously from hundreds of Å (and even below in theory) up to many micrometers.

The different SOI manufacturing techniques based on wafer bonding are characterized and differentiated by the technology used to thin down the top substrate (donor substrate) into a (more or less) thin SOI layer. Such thinning techniques can be real material removal techniques such as grinding/polishing/etching (BSOI, BESOI). They can also be based on a splitting/detachment along a certain layer introduced into the donor wafer to delineate the thin Si layer, which will become the SOI layer.

#### 1.1.2.1 **BSOI/BESOI**

After bonding, the thinning is realized by real material removal techniques such as grinding/polishing/etching. The obtained BSOI wafers are well known to suffer from thickness uniformity limitations: one needs to realize that  $\mu$ ms thick SOI layers are obtained as the result of the removal of hundreds of  $\mu$ m from a bulk donor substrate. In most of the cases, those techniques are addressing thick SOI markets: typically 5-50 $\mu$ m, with some possibilities to extend in the1 to 5  $\mu$ m range of thickness. In this respect they address perfectly applications such as power applications. This situation can be improved if an etch stop layer (Boron doping, SiGe layers, porous layer, ..) is previously added within the donor substrate (BESOI approach). Then a final selective etch is used to achieve much better thickness uniformities.

Beyond thickness related limitations, such technologies are quite simple and processing is cost-competitive for thick products. However, a disadvantage compared to the techniques that will be addressed later in this document is the cost of the starting wafers: the donor substrate is sacrificed in the process, leading to a consumption of 2 bulk wafers for the realization of one final SOI wafer.

Several BSOI/BESOI suppliers exist today.

In Japan, historically one of the oldest players in bonded SOI is SEH (N°1 worldwide for bulk Si wafers), which is still proposing such wafers for specific applications [13].

In the following sections, it will be explained that SEH is also pursuing other technological ways to address thin SOI material for mainstream CMOS.

In Europe, BCO Technologies in Ireland, used to produce such wafers. After a period in the Analog Devices group, all activities related to the SOI substrate business have disappeared. UMICORE in Belgium [14] and Okmetic in Finland [15] are also proposing SOI substrates based on such a technology. A new start-up originating from CEA-LETI, TRACIT Technologies, has been created in Grenoble (FR) and it offers different services based on wafer bonding such as BSOI specific wafers [16].

In the US, only small companies, as is also the case for most of the European companies in the field, are proposing such wafers like Virginia Semiconductors and

Isonics.

As a conclusion, Europe has a competitive position in the field of BSOI/BESOI substrates, which however is limited to marginal business segments markets, mainly because it can not address mainstream CMOS applications but only niche applications (where they still have to compete with other techniques). These companies however have a good knowledge and experience in wafer bonding on an industrial level and are also generally addressing other wafer bonding based activities and services (application specific substrates, MEMS, dissimilar materials integration, processed layer transfers, packaging solutions, ...).

Little R&D is done in the field of blanket BSOI/BESOI wafers, except regular engineering developments at industrial substrate suppliers to improve regularly the general quality of the SOI wafers. The field of patterned and / or other specific BSOI/BESOI wafers is addressed in the next section: New SOI-like materials.

### 1.1.2.2 Layer transfer based on Porous silicon layers (ELTRAN™)

This technology is based on the transfer of an epitaxial silicon layer grown initially on a porous silicon layer. It has seen several evolutions. At the origin, one of the main goals of the porous layer was to supply an etch-stop layer in a BESOI-like configuration. The porous silicon layer, the last layer to be removed before reaching the final non-porous SOI layer, is etched very fast compared in comparison [17]. Recent evolutions have consisted of using this intermediate porous layer as a fragile layer for a wafer scale fracture [18]. Along this layer splitting is performed thanks to mechanical efforts. In particular, CANON has demonstrated the use of a water jet technique [19, 20] to apply appropriate mechanical stress. Probably due to the necessity to limit the damage to the active layer, the porous layer became a double porous layer in the last CANON publications in order to better localize the splitting surface [19, 20].

The remaining porous material on the resulting SOI is selectively etched away after splitting, leaving the initial epitaxial layer transferred to the buried oxide. The SOI thickness control relies on the ability to form good epitaxial layers on porous silicon and enables then good results for thin films. Like in the case of Smart Cut<sup>TM</sup> (another splitting technology), the remaining donor wafer can be reclaimed and re-used in a subsequent process. ELTRAN<sup>TM</sup> is a trademark owned by CANON.

There are several key steps in this process. The first of them is the ability to form good quality, low contamination porous silicon layers. Another is the epitaxial deposition of single crystalline silicon layers on such porous layers. The technical challenge related to this task can be measured when referring to the critical importance of surface preparation before epitaxy (and in particular when this surface consists of porous Si). The generation of macroscopic crystalline defects such as hillocks and stacking faults, very sensitive to these surface preparations, can not be tolerated as they would be detrimental to the wafer bonding operations. Yield issues may become critical as small defects before bonding may lead to millimetric voids after layer transfer. Another key step concerns the controlled fracture along the porous layer by mechanical means without damaging the adjacent thin silicon layers. The double porous layer developed by CANON reflects clearly the difficulties related to this step. Last, the finishing step of the wafer consisting in removing the porous layer still needs to be well controlled as it leaves afterwards the final surface of the SOI layer, which needs to be of high quality (roughness, pitting, uniformity, etch pits, particles, ..).

Many R&D efforts are clearly required to accompany the evolution of this technology along with the ITRS roadmaps requirements.

One main actor is involved and has a strong position (patents, ..) with this process: CANON [20]. Other players are limited and have only been involved in limited demonstrations of the process.

### 1.1.2.3 Layer transfer based on ion implantation (Smart Cut™)

This technology is based on the use of an ion implantation step to define within a donor wafer a damaged layer that will serve as a splitting layer. Hydrogen species implantations are preferentially used but other species can also be used. In order to realize SOI wafers, the implanted donor wafers are bonded to handle substrates, which act also as stiffeners in the process. Right after splitting and layer transfer, the SOI shows generally some roughened/damaged surface. Some surface finishing steps are used to recover a surface comparable to that of a bulk substrate. Polishing (CMP) is one of the most extensively used techniques today for that purpose. For more details on this process, see for instance [5, 6, 21, 22].

As in most of the wafer bonding techniques, the buried oxide layer thickness is formed before bonding on either one of (or both) the surfaces to be bonded, and is therefore quite flexible. The SOI layer thickness is primarily given by the implantation energy. With standard industrial implanters (limited at around 200keV), and considering H+ ions as the implanted species, SOI as thick as 1.5µm are possible. Thicker SOI may also be obtained with an additional epitaxial step formed afterwards. Thinner SOI may be obtained by decreasing the implantation energy and/or by using thinning techniques (sacrificial oxidation, etching, polishing, ..).

SOI thickness non-uniformities, one of the main challenges in CMOS SOI, especially for Fully Depleted technologies, are induced by the combination of several steps in this process: the ion implantation energy uniformity, the thickness uniformity of the oxide layer formed on the donor wafer before implantation, the surface finishing technique uniformity (CMP, ..), and to a lesser extent by splitting conditions. Nevertheless, overall SOI thickness uniformities achievable with this technology are much better than what can be achieved by any BSOI/BESOI techniques. In that respect they are more suited to thin SOI wafers, in the submicron thickness regime.

Among the other advantages of this technology are:

- the possibility to reclaim the donor wafer,

- the fact that epi layer does not need to be grown on the donor wafer, and

- the fact that it uses only standard equipment (no development at the equipment level, easy extension to large diameters, such as 300mm).

As opposed to SIMOX (for instance), it should be noticed that this technology has a generic nature in the sense that it can be applied to (1) other materials than silicon for the active layer or handle substrate, (2) other buried insulators than  $SiO_2$  (and even multiple layers of insulators) and (3) also structures containing patterned layers as well as several levels of SOI (double SOI, etc). Those aspects are addressed in the following sections.

Variations and developments related to this technology have focused on the implantation step (co-implantation with other species such as He, temperature during implantation,...), the impact of the donor wafer properties (doping types and levels, crystalline orientation, ...), the splitting zone evolution as a function of different parameters, the fracture parameters and the post splitting surface finishing processes.

Another effort that has been (and that should be kept) high priority is defect reduction. It has been understood for a few years that the quality of the final SOI was more and more limited by the quality of the starting bulk silicon: especially bulk crystalline defects such as COPs (Crystal Originated Particles) coming from the ingot growth. This became a more serious problem when the thickness of the useful layers reached the order of such nano-defects (100nm scale and below). Since then high quality incoming wafers have been used for those most demanding applications such as advanced CMOS. The apparent "cost penalty" associated with those more expensive substrates is balanced by the fact that they are reclaimed and re-used.

Considering the actors worldwide, Europe is clearly leading in this field. This technology has been invented in CEA/LETI and industrially developed by SOITEC (in collaboration with CEA/LETI). With this technology, SOITEC is today the worldwide leader in the thin SOI material market. Smart Cut<sup>TM</sup> and UNIBOND<sup>TM</sup>, two trademarks owned by SOITEC, correspond respectively to the technology and the SOI wafers made by the technology. The power and potential of this technology has been recognized by major actors worldwide: Shin Etsu Handotaï (SEH) in Japan, N°1 in the bulk Si market has adopted this technology with an agreement signed in 1997 with SOITEC. SEH has started to offer such wafers on a commercial basis. In Europe, Wacker-Siltronic, N°3 worldwide in bulk Si, has recently signed with SOITEC an agreement concerning the licensing of this technology for the manufacturing of SOI wafers. On the R&D side, some public labs are also present in Europe. For instance, MPI-Halle (D) is having activities in the field of Smart Cut in addition to their strong activities in wafer bonding in general [23]. VTT in Finland has also used hydrogen implantation splitting with a focus on Low temperature splitting to realize different structures such as SOI and silicon on glass (SOG) [24].

Outside Europe, strong R&D activities are a proof of the recognized and strategic importance of this technology. Mostly in the US, but also in Asia, both large IC companies, smaller private companies (including some start-up), and public labs/universities work in this area, sometimes with some support from national institutions (DARPA, DoE, NSF..). Concerning the large companies, IBM for instance has made several demonstrations of the Smart Cut<sup>TM</sup> technology to realize specific SOI structures (strained SOI, etc ..) [25]. Among the small companies, SiGen (Silicon Genesis Corp.) in the US has been working and publishing actively on such technology for several years [26], with a specific focus on some steps and options (hydrogen plasma implantation, low T splitting, plasma activated bonding, variations of combinations of finishing steps. They recently announced a change in their business model: giving up the SOI wafer sale side to focus on a pure IP company model. Many other labs outside Europe also have been active in the field such as for instance the US Naval Research Laboratory (NRL), Duke University, Lucent Technologies.

Overall, although Europe has been pioneering in the field, the situation today is that many actors have entered into the arena, and have engaged significant resources. As a result, especially on the Intellectual Property side, many patent applications (more or less sensible) have been filed on many topics related to such a technology. Europe's leading position here is being threatened.

Concerning the technical challenges, in the short term they are addressing:

- Continuous improvement of material quality in line with the industry roadmaps (ITRS, etc ...)

- Thickness reductions towards sub-10nm dimensions and a strong focus on thickness uniformities at large diameter wafer scales. In that field major progress have been done in 2008-2009 and today the state of the art in term of

SOI thickness uniformity is 150Å ±5Å.

Technology cost and technology yield improvements through a better control of each of the key steps of the technology (wafer bonding, splitting, surface finishing, ..)

On the longer term, many other key developments do exist to build the next generations of SOI wafers. They will be treated in the following sections; they include high mobility in SOI thanks to strained-Si or Ge-On-Insulator, changing the buried insulator for better thermal management purposes, incorporating patterns into or below the transferred layers. Other developments will consist in adapting the SOI wafers for some specific applications (which do not rule out high volume). For instance, RF applications require high resistivity substrates. Wafer bonding techniques, among them Smart Cut<sup>TM</sup>, enable specific solutions consisting in placing high quality transistor grade silicon film onto high resistivity silicon. Other specific substrates may be optimized for high power devices, MEMS, and for Opto devices.

#### 1.1.2.4 Basic wafer bonding process and evolution trends

The focus of this section is on direct wafer bonding techniques used for SOI-type material fabrication. Gluing and similar approaches are not discussed.

Wafer bonding is a key technology in SOI material formation, at least for those techniques based on layer transfer such as addressed in this section. It is known that this technological step is very sensitive to parameters such as particle density, organic contamination, flatness, roughness, and surface chemical activity. Those aspects are addressed in detail in some books/papers [1-7, 27-29]. Severe defects (sometimes mms wide and even larger) are often associated with a lack of control of some of these parameters. In that respect, not only the geometrical parameters of the initial bulk wafers are of importance but also the final preparation of the wafers before bonding. Today, most of the final preparations are based on wet chemistry, such as (more or less modified) RCA cleanings. As far as industrial scale is concerned, these cleanings are usually performed in separated industrial wet benches of the same type than those used in Si-based IC manufacturing. Wafer bonding, easily done manually in a research setting, is performed in automated machines when manufacturing is considered; Europe counts two leaders in wafer bonding equipment: EVG in Austria [30] and Karl-Suss [31] in Germany. However this industry is quite young and is subject to further developments. In the field of science and technology of wafer bonding based on wet chemistry, Europe has a position of leadership with several labs (CEA-LETI, MPI-Halle, VTT Finland, Queen's Univ. Belfast, Chalmers Univ.,) and several industrial end-users (SOITEC, Okmetic, TRACIT Technologies, Umicore,...).

Usually a wafer bonding preparation based on wet chemistry pre-cleaning is associated with a post-bonding high temperature annealing (>1000°C) to transform low/medium bonding energy into a strong covalent one. The wafer contacting and bonding step is usually performed at room temperature. While lower energies can be tolerated for some applications, SOI wafer processing in general cannot afford it. For future evolutions of SOI materials, there is a need to go to high bonding energies, using processes without the use of high temperature anneals: the so-called Low T° wafer bonding processes (Low T refers to the maximum temperature used in the post bonding annealing).

#### Low Temperature processes

The possibility of increasing surface energy of bonded interfaces at low annealing temperatures or even at room temperature is of importance in the application to dissimilar materials (i.e novel dielectrics in SOI) and for future applications of layer transfer techniques. There are several ways to reach an increased mechanical stability of the bonded interface after exposure to low or moderate thermal budgets. They all include various modifications of the surfaces. Only extending the annealing time at low temperatures after conventional wet cleaning does not improve the situation more than marginally. Modifications reported to increase the surface energy at low temperatures include:

- -Plasma treatment (most of the time oxygen or nitrogen) of the surfaces to form a low density subsurface layer increasing the diffusion of water from the interface. Works at room temperature or with 100-200°C annealing temperatures. The increased water diffusion rate as an effect of the plasma treatment is generally agreed. However, reported results are very scattered, pointing at the fact that the structure of the surface layer is very dependent on the detailed conditions (and chamber geometries, etc) during plasma treatment.

- Non-standard chemical treatments combined with low temperature annealing.

- Ion bombardment or UHV treatments to atomically clean surfaces before bonding. The challenge of most of the methods is to increase the reactivity (normally the density of silanol groups or the diffusion constant of water in the interfacial region) without detrimentally damaging the materials.

It should be noticed that low T° wafer bonding is also of major interest in the field of Microsystems where wafer bonding is an enabling step to form complex structures. Temperatures and thermal budgets have most of the time to be limited there. Some common interest does exist between the 2 fields of applications SOI and MEMS.

Most of the European labs involved in wafer bonding have also high energy bonding programs. In the field of low T° wafer bonding, Europe today is running in a strongly competitive domain, with strong contributions in the US and Japan. Low T° wafer bonding is important for the future and should be addressed carefully, for instance by gathering together the many rich but elementary activities spread across Europe.

#### 1.1.3. Others (SOS, SON)

#### SOS

The advent of reliable 100% silicon based SOI wafer manufacturing process has pushed SOS substrates into narrowly defined applications. One of them, probably the most important is about RF applications. For these applications, insulating (or high

enough resistivity) substrates are required. This improves passive component performance (high Q inductors for instance) making above IC architectures possible, and also reduces detrimental cross-talk effects. High resistivity versions of silicon materials enable certainly to address a large part of RF applications but their limited maximum resistivity (typically below a few k $\Omega$ .cm) leaves some room for truly insulating substrates such as sapphire.

Today, SOS activities on the material realisation side are close to zero in Europe. The main actors are based in the US as far as materials are concerned (Peregrine Semiconductors and some labs often linked to Defense organizations) [32]. The process used for the material manufacturing is based on epitaxy, and one key element is the control of the hetero-epitaxial growth of Si onto sapphire, as well as metallic contamination control from sapphire.

#### SON

Silicon On Nothing (SON) is usually obtained through the selective etch of a buried epitaxial layer (for instance a buried SiGe embedded in a silicon matrix). For enabling the selective etchant to reach the buried layer to be etched away, patterning is necessary. This makes this approach more suitable for local SOI structures than for full blanket wafers. As *Nothing* may not have the best insulating properties, and since *Nothing* does not behave properly during IC manufacturing process, the emptied buried layer may be selectively filled by another material, such as SiO<sub>2</sub>. The thickness control is a combination of epitaxial and etching step control. When filling the cavities is considered, lateral filling of those horizontal buried cavities is the limiting factor for the width and homogeneity of such structures. Europe has a pioneering position in this area with ST's already long experience [33].

It should lastly be noticed that other approaches have been evaluated to create SON. For instance the "Toshiba approach" uses a combination of deep trench formation by etching and subsequent capping by silicon surface reconstruction thanks to smoothing anneals (hydrogen anneal). To the authors' knowledge, this is so far not reported to be industrially exploitable.

#### References

#### **Books and review papers**

- [1] Q.-Y. Tong and U. Gösele, "Semiconductor Wafer Bonding, Science and Technology" (John Wiley&Sons, New York, 1999)

- [2] M. Alexe and U. Gösele (Eds.), "Wafer Bonding: Applications and Technology." (Springer, Berlin, 2004)

- [3] Plöl, G. Kräuter, Mat. Sci. and Eng. R25 (1999) 1-88.

- [4] J. Haisma, G.A.C.M. Spierings, T.M. Michielsen and C.L. Adema: "Philips Journal of Research 49" (1995).

- [5] G.K. Celler, S. Cristoloveanu, Journal of Applied Physics, Vol. 93 (9), May 2003, 4955-4978.

- **[6]** J.-P. Collinge, "Silicon-On-Insulator Technology: Materials to VLSI", 2<sup>nd</sup> Ed. (Kluwer, Boston, 1995).

- [7] "Silicon Wafer bonding Technology for VLSI and MEMS applications". Edited by S.S. Iyer and A.J. Auberton-Hervé (IEE Inspec, EMIS processing series; no.1), 2002

#### SIMOX

- [8] www.ibis.com

- [9] www.siliconstrategies.com. July 21rst, 2004 (article Id=23904675)

- [10] D. K. Sadana, M. I. Current, "IBM Research Report RC23337 (W0409-077)", Sept. 14, 2004

- [11] www.sumcosi.com

- [12] www./simgui.com.cn

#### **BSOI/BESOI**

- [13] (SEH site web)

- [14] (www.umicore.com)

- [15] (www.okmetic.com).

- [16] (www.tracit-tech.com).

#### Layer transfer based on Porous silicon layers and ELTRAN

- [17] N. Sato et al., Proceedings 1995 IEEE Internat. SOI Conference, Oct 1995, p. 176.

- [18] K. Yamagata and T. Yonehara, Mat. Res. Soc. Symp. Proc. Vol. 681E, 2001 Materials Research Society

- [19] T. Yonehara, Chapter 4 in "Silicon Wafer bonding Technology for VLSI and MEMS applications". Edited by S.S. Iyer and A.J. Auberton-Hervé (IEE Inspec, EMIS processing series; no.1), 2002

- [20] http://www.canon.com

#### Layer transfer based on ion implantation and Smart Cut

- [21] M. Bruel, Electron. Lett., 31 (14), 1201, (1995)

- [22] http://www.soitec.com

- [23] http://www.mpi-halle.mpg.de/

- [24] http://www.vtt.fi

- [25] K. Rim et al, Proc. IEDM 2003 Conf, p. 49.

- [26] http://www.sigen.com

#### Basic Wafer bonding process and evolution trends

- [27] P. Amirfeiz, S. Bengtsson, M. Bergh, E. Zanghellini and L. Börjesson, J. Electrochem. Soc. 147, 2693 (2000)

- [28] C. Maleville, O. Rayssac, H. Moriceau, B. Biasse, L. Baroux, B. Aspar and M. Bruel, "Semiconductor wafer bonding, Science Technology and Applications IV", Electrochemical Society Proceedings, PV 97-36, pp 46-55 (1998)

- **[29]** H. Moriceau et al., "6<sup>th</sup> Int. Symp. on Semiconductor Wafer Bonding : Science, Technology and Applications", ECS Proceedings PV 2001-27 (2001) pp 1-16.

- [30] www.evgroup.com

- [31] www.suss.com

#### SOS, SON

- [32] http://www.peregrine-semi.com

- [33] S. Monfray, D. Chanemougame, S. Borel, A. Talobot, F. Leverd, N. Planes, D. Delille, D. Dutartre, R. Palla, Y. Morand, S. Descombes, M.-P. Samson, N. Vulliet, T. Sparks, A. Vandooren and T. Skotnicki, IEDM Techn. Dig., pp 635-638, 2004.

| <b>European Contribution on the Field</b>                                                                                                                                                                                                                                  | Current Situation                                                                    |                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------|

| European Groups:                                                                                                                                                                                                                                                           | Strong Points                                                                        | Weaknesses                                                |

| Leadership on wafer bonding science and technology (MPI-Halle, CEA-LETI, SOITEC, EVG, Karl-Zuss, QUB, VTT, Okmetic, Chalmers ,)                                                                                                                                            | Key for most of the SOI material techniques (except SIMOX) but also μ -microsystems. | Aggressive competition outside Europe                     |

| <b>Leadership</b> on wafer bonding tools (EVG, Karl-Zuss)                                                                                                                                                                                                                  | Key for industrial application of wafer bonding                                      |                                                           |

| Leadership based on the Smart Cut process (SOITEC, CEA-LETI) for industrial exploitation (MPI-Halle, CEA-LETI, VTT) for basic research                                                                                                                                     | Pioneering based on the<br>Smart Cut process                                         | Aggressive competition outside Europe                     |

| Contributors in BSOI (Tracit, UMICORE, Okmetic )                                                                                                                                                                                                                           |                                                                                      |                                                           |

| Follower in combination of wafer bonding and other than Smart Cut splitting/thinning techniques                                                                                                                                                                            |                                                                                      | Very small activity                                       |

| Nothing for other approaches such as SIMOX, SOS                                                                                                                                                                                                                            |                                                                                      | approaches than<br>wafer bonding +<br>Smart Cut           |

| Leadership in SON (ST) Comments:                                                                                                                                                                                                                                           | SON (ST leadersdhip )                                                                | No (or almost no)<br>activity in SIMOX,<br>Porous silicon |

| Leading activities in combination of wafer bonding and porous layer splitting in Asia (Canon). Strong contributions on combination of plasma bonding and Smart Cut alike techniques in the US. Strong contributions on wafer bonding in the US (NRL, EVG) and Asia (Tokyo) |                                                                                      | splitting, SOS                                            |

#### **Conclusions and recommendations**

- Almost no SIMOX material activity in Europe: Closing the gap would be too expensive and SIMOX is not the present European solution.

- European overall leadership in wafer bonding science and technology

- Importance of wafer bonding technologies for most of the techniques available in Europe

- Thin SOI market potential much bigger than thick SOI due to the perfect match with mainstream CMOS needs

- European leadership in thin SOI material market with Smart Cut

- European activities behind international efforts in some combinations of wafer bonding and wafer splitting/thinning techniques (ex. Porous Si)

- A further integration of European activities through joint projects necessary.

- → Focus resources on keeping leadership in wafer bonding, Smart Cut and thin SOI material market to keep pace with US and Asia in terms of innovation, IP, ...

#### **Chapter 1. SOI Materials**

Section 1.1 Commercially available SOI substrates and key manufacturing steps Subsection 1.1.4. CVD-epitaxy for SOI

Date of Issue: Dec - 2010 Partner: IMEP

#### **Abstract**

CVD selective epitaxial lateral overgrowth was successfully demonstrated in thin SOI films.

#### Introduction

Numerous attempts were made to fabricate transistors in varying films made by sputtering, zone-melt recrystallization, and different epitaxy reactor geometries. The work by Philips SC [1] was the first to demonstrate a fully-depleted MOSFET with two individually controllable gates. Recently three-dimensional (3D) thin-film transistors (TFTs) have been intregated forming static random access memory (SRAM). The technique to grow selective epitaxial Si films through the seeding contact hole was successfully developed with a single-wafer-type chemical vapor deposition (CVD) and dichlorosilane gas with HCl in  $H_2$  carrier gas. The electrical characteristics of the cell TFTs made on the selective epitaxial growth (SEG) Si films are very close to those of the bulk transistor. 72 Mbit SRAM was successfully developed with this SEG technique and 3D  $S_3$  SRAM cell technology.

#### References

[1] R. Zingg et al, IEDM 1989, pp.909

[2] S.M. Jung, H. Lim, K. Lim, "CVD selective epitaxial lateral overgrowth technique for 3D stacked SRAM cell on soi-like silicon films"; Electrochemical and Solid-State Letters, vol. 12(10), pp. H392-H394 (2009).

| European Contribution on the Field          | Current Situation |                  |

|---------------------------------------------|-------------------|------------------|

| European Groups:                            | Strong Points     | Weaknesses       |

| Leadership: first successful full-depletion | Full depletion,   | Slow growth rate |

| device                                      | almost symmetric  | and very high    |

|                                             | gates             | costs.           |

| Comments: Issues around gate-oxide          |                   | No industrial    |

| grown on polycrystalline silicon and on     |                   | acceptance.      |

| interface-states on silicon grown on oxide  |                   |                  |

| had to be resolved.                         |                   |                  |

|                                             |                   |                  |

#### **Conclusions and recommendations**

No commercial solutions.

#### **Chapter 1. SOI Materials**

Section 1.1 Commercially available SOI substrates and key manufacturing steps Subsection 1.1.5. Liquid-phase epitaxy for SOI

Date of Issue: Dec - 2010 Partner: IMEP

#### Abstract

Devices made in SOI film fabricated by liquid-phase epitaxy (LPE) are characterized.

#### Introduction

Gas-phase epitaxy for local overgrowth has the disadvantage of slow growth rate and high cost (large consumption of high-purity super-dry hydrogen and heat energy). Liquid phase epitaxy has the advantage that the solvent (Ga or In) can be re-used and the temperatures are lower [1].

Liquid-phase epitaxy allows the islands grown from different orientation seeds. To do so, single-crystalline Si wafers are used as seeds for the location-controlled grain growth with  $\mu$ -Czochralski process during excimer laser crystallization (ELC). With an enough energy density, Si wafers seeds liquid epitaxial growth and grains with arbitrary orientation can be obtained at the predetermined positions [2].

#### References

[1] R. Zingg et al, IEEE EDL-13 (5), May 1992

[2] He, M., Ishihara, R., Hiroshima, Y., Inoue, S., Shimoda, T., Metselaar, J.W., Beenakker, C.I.M., "Effects of crystallographic orientation of single-crystalline seed on µ-Czochralski process in excimer-laser crystallization", IDW/AD'05 - Proceedings of the 12th International Display Workshops in Conjunction with Asia Display, pp. 1213-1214 (2005).

| European Contribution on the Field               | Current Situation |                          |

|--------------------------------------------------|-------------------|--------------------------|

| European Groups:                                 | Strong Points     | Weaknesses               |

| Leadership: only some institutes working on LPE. | Cost advantage    | No industrial acceptance |

| Conclusions and recommendations |

|---------------------------------|

| No commercial solution.         |

|                                 |

**Chapter 1. SOI Materials**

Section 1.2. New SOI-Like materials in development

Subsection 1.2.1. High mobility SOI

1.2.1.1. High mobility I: Strained Si on Insulator Wafers

Date of Issue: Dec - 2010 Partner: SOITEC, CEA-LETI.

#### Abstract

Improved versions of SOI material tend to incorporate high carrier mobility layers on Insulator: Strained Si and/or SiGe layers on Insulator are considered in a first version.

#### Introduction

Improving the carrier mobility, in addition to adopting SOI architectures, is becoming a priority if one wants to meet the next challenges raised by the ITRS roadmap for the sub 65nm nodes (drive current, ION/IOFF trade-off, ...). Strained Si in a "bulk" configuration is already considered by some actors for the 90nm node. Combining strained Si and SOI will more precisely address 65nm and below nodes, depending on the applications. High performance devices (logic applications, ..) will be the first to benefit from / require such evolutions.

### Strained Si

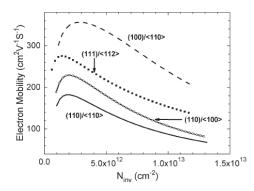

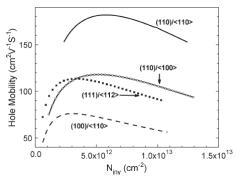

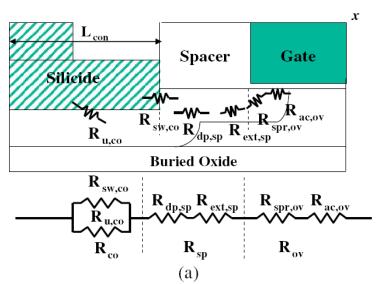

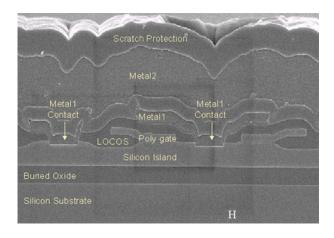

One known way to modulate carrier mobilities in semiconductors is to apply strain to the material. Applying tensile strain to silicon is known to increase electron mobilities for moderate strain values but also hole mobilities if strong enough strain is applied. To extend the capabilities of silicon in terms of mobilities, the use of strained Si is a solution of choice because it remains a silicon based solution and does not require to revisit completely the transistor fabrication processes (unlike the migration towards other semiconductors such as Ge for instance).

Several ways exist to realize controlled strain induced into silicon. These have generally been initially developed for "bulk" solutions. In this section one should consider whether (and at which price) these solutions can be combined with SOI architectures. Today, two main approaches are investigated for introducing strain in CMOS transistor channels.

The first approach, often referred to as "local strain" or "process-induced strain", is based upon the local strain (generally uniaxially oriented) that is introduced during the CMOS manufacturing steps such as epitaxial SiGe source/drain pocket formation, nitride spacer deposition, gate encapsulation, shallow trench isolation (STI). It has proven very successful and leading edge IC makers have implemented it in 90nm technology manufacturing. These approaches have as advantage that they do seem to depend only on the fine but a priori easy tuning of some basic deposition or etch steps. On the other hand however, one could remark that scalability is a tricky point to control as reducing the lateral dimensions of the transistors affects definitely the efficiency of the induced strain. Strain engineering needs to be taken into account at the transistor level and may limit the flexibility and complexity of transistors architectures. Flexibility

can be limited as each new transistor needs a redesign at a technological level in terms of the strain that needs to be initially applied and the way it transfers to the point of use. Defectivity is another unknown parameter today. The presence of strong strain gradients associated with the local strain approach may indeed raise questions as to the formation of crystalline defects such as dislocations to release the strong gradients of strain. The evolution and impact of such defects on transistor performances and overall yield is not very well known at the moment. Although initially developed for "bulk" solutions, this approach can be combined with the use of SOI substrates [1], with a priori no specific development required at the SOI substrate level.

The other approach ("Global strain" at the material level) transfers the strain building and engineering concerns at the starting material level, adding definitely some value in the substrate. Once the strain is incorporated in the substrate, the device engineers are relieved from additional constraints that limit their flexibility, except maybe to avoid global strain relaxation induced by too aggressive manufacturing steps. The general biaxial symmetry of the strain associated with this approach makes the impact of the transistor width and length equivalent. A key element here is then the formation of the substrate, a SOI wafer integrating the strained Si active layer. There is definitely room in this field for key and innovative developments on the material side. Europe today has a leading position on the field (see below) and should stay well positioned in that respect.

Initially the two approaches (local versus global strain) appeared as two competitive solutions that several companies and labs worldwide were evaluating in parallel (IBM, TOSHIBA, MIRAI consortium in Japan, MIT, ...). However, instead of pure competition, global strain shall be considered as a further step in strain engineering to further boost device mobility and current drive. It helps overcome the limitations of uniaxial techniques, and its combination with local strain techniques is proposed to maximize performance for the future technology nodes. Global strain is not only an alternative but can be combined with process induced strain to enable the optimization of both NMOS and PMOS transistors.

#### Competitive solutions at the substrate level for the "Global strain" approach

Still corresponding to the same spirit of introducing the strain at the substrate level in a SOI configuration, alternative ways of creating those high added-value substrates exist.

Probably the oldest (and still competitive) way to form strained Si for "bulk solutions" relies on the hetero-epitaxy of silicon onto relaxed  $Si_{1-x}Ge_x$  layer, the final strain being an increasing function of the Ge content (x) and the relaxation rate (R) of this layer (R= 0 for fully strained and =1 for fully relaxed). Since bulk SiGe substrates and ingots do not exist (or only for low diameters, low Ge content, high defectivity), virtual SiGe substrates are formed by hetero-epitaxy onto bulk Si with the help of different sorts of buffer layers (graded buffers etc ...).

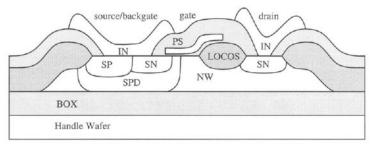

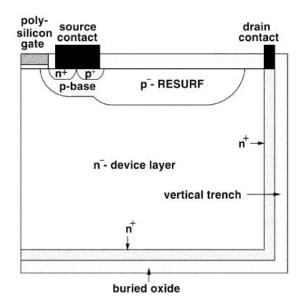

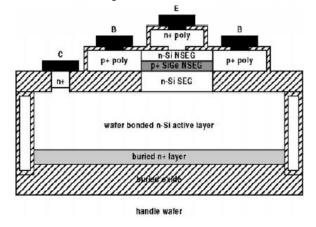

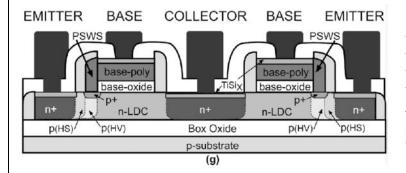

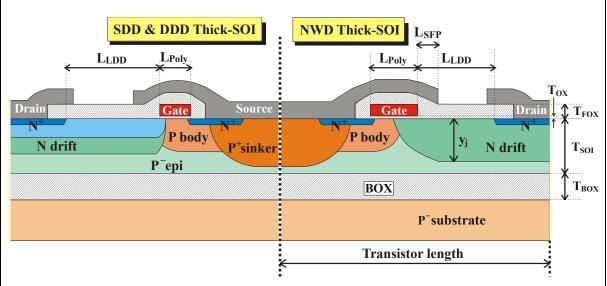

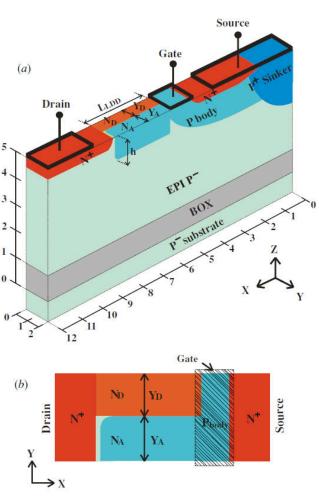

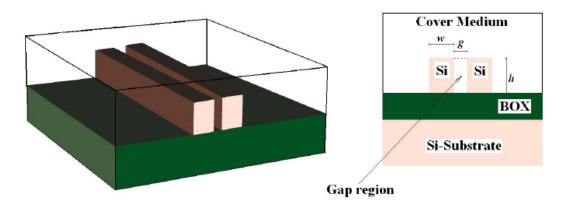

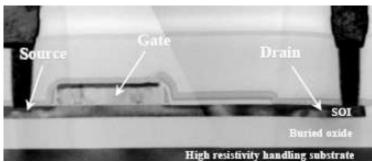

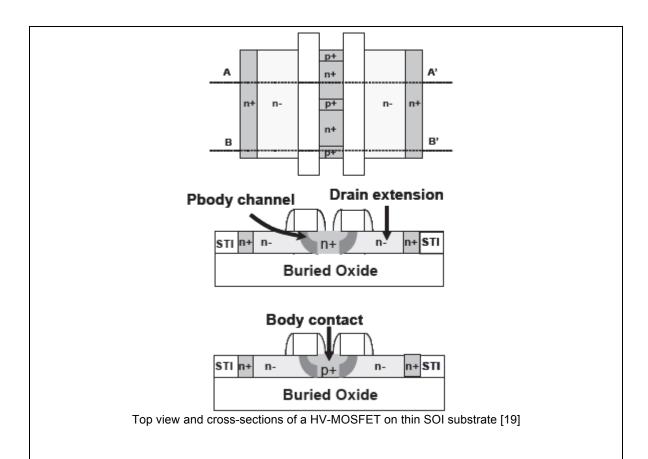

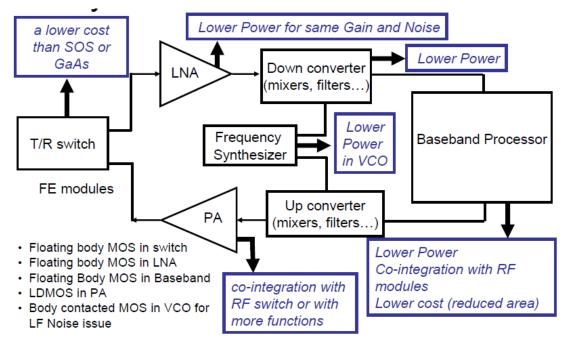

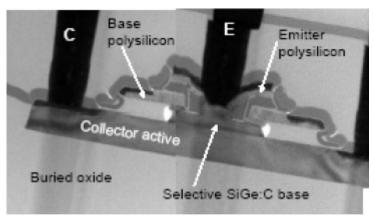

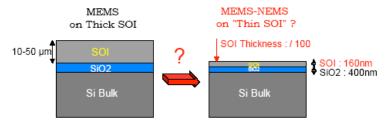

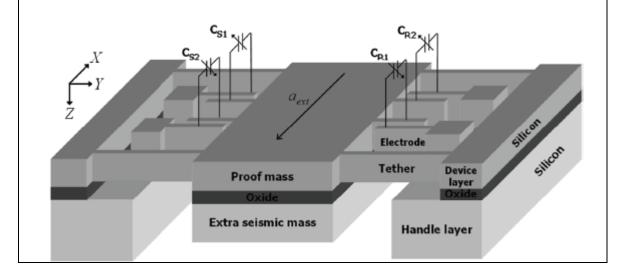

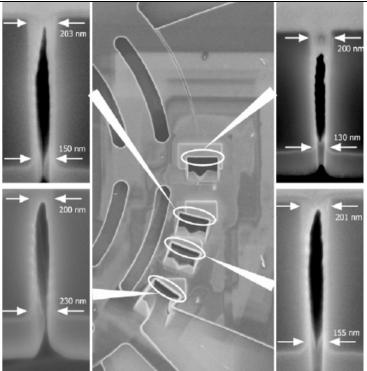

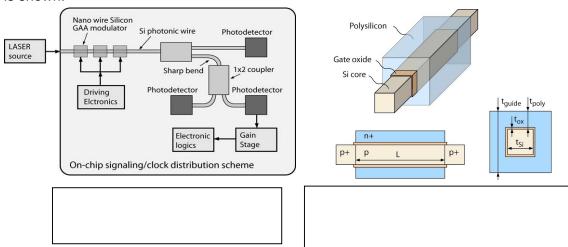

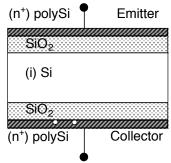

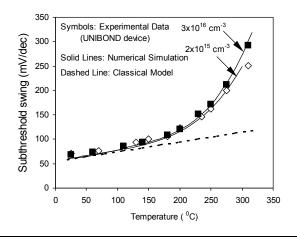

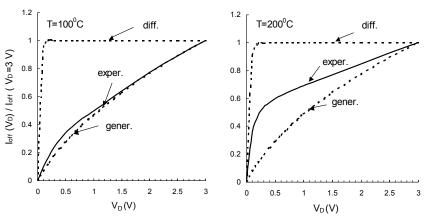

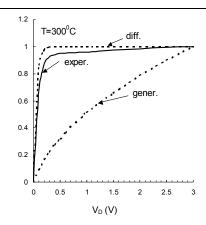

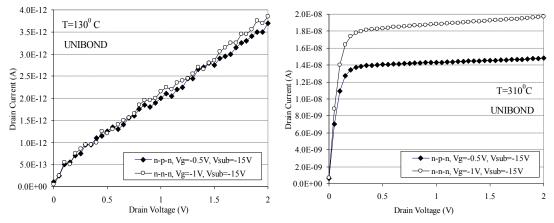

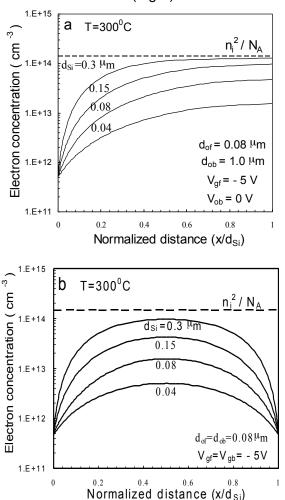

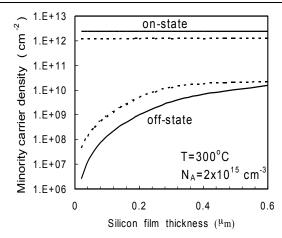

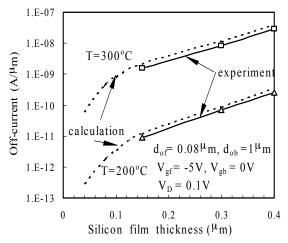

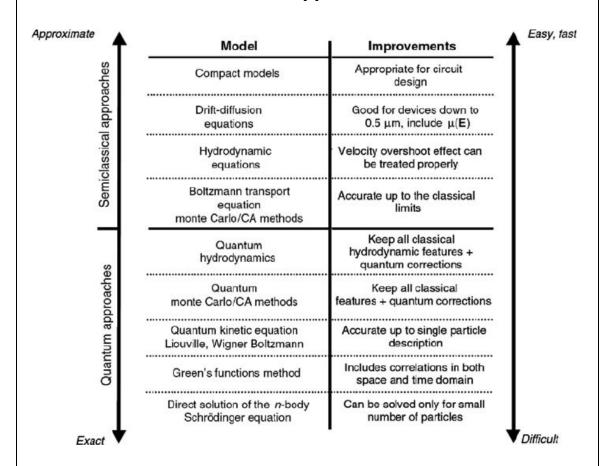

For the case of SOI architectures, it appears that most of the different classes of substrates that can be obtained contain at least one thin relaxed SiGe layer (but without any additional buffer layer that would be detrimental to the transistor behaviour) in addition to the strained Si layer. Correspondingly, an intermediate substrate is obtained: SiGeOI. In a second phase, this intermediate substrate is used as template for a final strained Si epitaxial deposition step. This approach is called "SGOI". Only in