#### INFORMATION AND COMMUNICATION TECHNOLOGIES

#### COORDINATION AND SUPPORT ACTION

#### **EUROSOI+**

## **European Platform for Low-Power Applications on Silicon-On-Insulator Technology**

Grant Agreement nº 216373

# D4.7 Report on EUROSOI+ Workshop held in Cork, 23-25 January, 2008

Due date of deliverable: 29-02-2008 Actual submission date: 29-02-2008

Start date of project: 01-01-2008 Duration: 39 months

Project coordinator: Prof. Francisco Gámiz, UGR

Project coordinator organisation: University of Granada, Spain Rev.1

| Project co-funded by the European Commission within the Seventh Framework Programme (FP7) |                                                                                       |   |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|--|

|                                                                                           | Dissemination Level                                                                   |   |  |

| PU                                                                                        | Public                                                                                | X |  |

| PP                                                                                        | Restricted to other programme participants (including the Commission Services)        |   |  |

| RE                                                                                        | Restricted to a group specified by the consortium (including the Commission Services) |   |  |

| CO                                                                                        | Confidential, only for members of the consortium (including the Commission Services)  |   |  |

#### **Table of contents**

- 1.- Introduction

- 2.- Agenda

- 3.- List of participants.

- 4.- Selection of papers to be published in a special issue of the Solid State Electronics Journal.

- 5.- Minutes of the Management Board Meeting held in Cork, on January  $23^{\rm rd}$ , 2008

- 6.- Conclusions.

**Annex. Conference Proceedings.**

#### 1. Introduction

SOI is no longer a promising technology. It is the necessary technology for the future of the microelectronics and for the smooth transition to the nanoelectronics. The incentive to foster the interactions among SOI material specialists, technologists, device experts, and circuit & system designers was supported by the Information Society of the European Union. As a result, EUROSOI'08 is the Fourth Workshop of the Thematic Network on Silicon on Insulator technology, devices and circuits. EUROSOI'08 takes place in Cork, Ireland from Wednesday January 23 to Friday January 25, 2008.

EUROSOI is designed as an international forum for promoting high-level scientific research and exchanges between research groups and industrial partners involved in SOI activities all over the world. Following the lively experience of the previous meetings (Granada, 2005, Grenoble, 2006 and Leuven, 2007), EUROSOI'08 features oral and poster sessions, key-note presentations, a training course as well as room for informal discussions. EUROSOI covers recent progress in SOI, including: (1) Synthesis of advanced SOI wafers (Ge, SiGe and strained layers, SOI heterostructures); (2) Materials evaluation, properties of ultra-thin films and buried oxides; (3) SOI MOSFETs: characterization, modeling and simulations, parameter extraction, reliability issues; (4) High performance CMOS and bipolar devices: low power/voltage and RF circuits, memories, sensors and MEMS; (5) Innovative devices: multiple-gates, tunneling transistors, etc.

A high number of papers have been submitted this year and 55 contributions have been selected for presentation. Many of them originate from strong national and international co-operations. Our special guests are Dr. Sergei Okhonin and Dr. Laurent Clavelier who kindly accepted to deliver outstanding key-note talks. In addition, 6 lectures by international experts are included in the Training Course. A Special Issue of Solid-State Electronics will contain selected full-length papers.

## 2.- Agenda

|       | Wednesday,<br>January 23 <sup>rd</sup> ,<br>2008 | Thursday,<br>January 24 <sup>th</sup> ,<br>2008 | Friday, January<br>25 <sup>th</sup> , 2008 |

|-------|--------------------------------------------------|-------------------------------------------------|--------------------------------------------|

| 9-10  | <b>Short Course:</b>                             | Session1:                                       | Session5:                                  |

| 10-11 | Multigate SOI                                    | SOI Memory                                      | SOI Material                               |

|       | MOSFETs                                          | devices                                         | characterization                           |

|       |                                                  | Session2:                                       | Session 6:                                 |

| 11-12 |                                                  | Device                                          | Passive RF                                 |

|       |                                                  | Modelling and                                   | Devices                                    |

| 12-13 |                                                  | SOI Circuits                                    | Panel                                      |

|       |                                                  | Lunch                                           | Discussion                                 |

| 13-14 |                                                  |                                                 |                                            |

|       |                                                  |                                                 | Lunch                                      |

| 14-15 |                                                  | Session3:                                       |                                            |

| _     |                                                  | Quantum                                         | Session7: SOI                              |

| 15-16 |                                                  | Device                                          | devices physics                            |

|       |                                                  | Modelling                                       | and character. I                           |

|       |                                                  | Session 4:                                      |                                            |

| 16-17 |                                                  | Active RF                                       | Session8: SOI                              |

| 1= 10 |                                                  | Devices                                         | devices physics                            |

| 17-18 | EUROSOI+                                         | Poster Session                                  | and character. II                          |

|       | Management                                       |                                                 | Cloncluding                                |

| 10.10 | <b>Board Meeting</b>                             |                                                 | remarks                                    |

| 18-19 | <b>147</b> 1                                     | 0 (                                             |                                            |

| 19-20 | Welcome                                          | Conference                                      |                                            |

| 20-21 | Reception                                        | Dinner:                                         |                                            |

|       |                                                  | EUROSOI+<br>Kickoff                             |                                            |

3.- List of participants

| J LI |             | licipanis      | I                                        |                                      |

|------|-------------|----------------|------------------------------------------|--------------------------------------|

|      | First Name  |                | Affiliation, Country                     | Email address                        |

| 1.   | Aryan       | Afzalian       | Tyndall, Ireland                         | aryan.afzalian@tyndall.ie            |

| 2.   | Jouni       | Ahopelto       | VTT, Finland                             | Jouni.Ahopelto@vtt.fi                |

| 3.   | John        | Alderman       | Tyndall, Ireland                         | john.alderman@tyndall.ie             |

| 4.   | Nicolas     | Andre          | UCL, Belgium                             | nicolas.andre@uclouvain.be           |

| 5.   | Michael     | Angermayer     | EV Group, Austria                        | m.angermayer@evgroup.com             |

| 6.   | Mervyn      | Armstrong      | Queen's University<br>Belfast, UK        | b.armstrong@ee.qub.ac.uk             |

| 7.   | Alastair    | Armstrong      | Queen's University<br>Belfast, UK        | a.armstrong@ee.qub.ac.uk             |

| 8.   | Xavier      | Baie           | Belgium                                  | xavier.baie@gmail.com                |

| 9.   | Paul        | Baine          | Queen's University<br>Belfast, UK        | p.baine@ee.qub.ac.uk                 |

| 10.  | Maria       | Balaguer       | U. Granada, Spain                        | mbalaguer@ugr.es                     |

| 11.  | Sophie      | Baudot         | CEA, France                              | sophie.baudot@cea.fr                 |

| 12.  | Marco       | Braccioli      | ARCES-University of Bologna, Italy       | mbraccioli@arces.unibo.it            |

| 13.  | Cor         | Claeys         | IMEC, Belgium                            | claeys@imec.be                       |

| 14.  | Laurent     | Clavelier      | CEA/LETI, France                         | laurent.clavelier@cea.fr             |

| 15.  | Jean-Pierre | Colinge        | Tyndall, Ireland                         | jean-pierre.colinge@tyndall.ie       |

| 16.  | Cindy       | Colinge        | Tyndall, Ireland                         | cindy.colinge@tyndall.ie             |

|      | •           | Contes         | *                                        |                                      |

| 17.  | Ignasi      |                | CNM, Spain                               | ignasi.cortes@cnm.es                 |

| 18.  | Sorin       | Cristoloveanu  | ENSERG, France                           | sorin@enserg.fr                      |

| 19.  | Paul        | Daly           | Analog Devices,<br>Ireland               | paul.daly@analog.com                 |

| 20.  | Michelly    | de Souza       | University of Sao<br>Paulo, Brazil       | michelly@lsi.usp.br                  |

| 21.  | Nima        | Dehdashti      | Tyndall, Ireland                         | nima.dehdashti@tyndall.ie            |

| 22.  | Pierre      | Delatte        | Cissoid, Belgium                         | delatte@cissoid.com                  |

| 23.  | Russel      | Duane          | Tyndall, Ireland                         | russel.duane@tyndall.ie              |

| 24.  | Mostafa     | Emam           | UCL, Belgium                             | mostafa.emam@uclouvain.be            |

| 25.  | Olivier     | Faynot         | CEA-LETI, France                         | olivier.faynot@cea.fr                |

| 26.  | Veronique   | Ferlet-Cavrois | CEA, France                              | veronique.ferlet@cea.fr              |

| 27.  | Denis       | Flandre        | UCL, Belgium                             | denis.flandre@uclouvain.be           |

| 28.  | David       | Flores         | CNM, Spain                               | david.flores@cnm.es                  |

|      | Harold      | Gamble         | Queen's University<br>Belfast, UK        | h.gamble@ee.qub.ac.uk                |

| 30.  | Francisco   | Gamiz          | University of<br>Granada, Spain          | fgamiz@ugr.es                        |

| 31.  | Andres      | Godoy          | U. Granada, Spain                        | agodoy@ugr.es                        |

| 32.  | Wei         | Guo            | U Caen, France                           | agodo y (agugr.co                    |

| 33.  | Dina        | Heidar         |                                          | _<br>dina.kamel@student.uclouvain.be |

|      |             |                | UCL, Belgium                             |                                      |

| 34.  | Samer       | Houri          | UCL, Belgium                             | samer.houri@uclouvain.be             |

| 35.  | Louis       | Hutin          | LETI, France                             | louis.hutin@cea.fr                   |

| 36.  | Masaaki     | lijima         | Kobe University,<br>Japan                | iijima@cas.eedept.kobe-u.ac.jp       |

| 37.  | Benjamin    | Iňiguez        | URV, Spain                               | <u>benjamin.iniguez@urv.cat</u>      |

| 38.  | Takashi     | Ito            | Tohoku University                        | tito@ecei.tohoku.ac.jp               |

| 39.  | David       | Jiménez        | Universitat Autònoma de Barcelona, Spain | david.jimenez@uab.es                 |

| 40.  | Malgorzata  | Jurczak        | IMEC, Belgium                            | jurczakm@imec.be                     |

| 41.  | Gerhard     | Knoblinger     | Infineon, Austria                        | Gerhard.Knoblinger@infineon.com      |

| 42.  | Abhinav     | Kranti         | Queen's University<br>Belfast, UK        | a.kranti@ee.qub.ac.uk                |

| 43.  | James       | Kuo            | NTUEE, Taiwan                            | jbkuo@cc.ee.ntu.edu.tw               |

| +∪.  | variies     | ixuo           | INTOLL, Talwall                          | prao(wco.ee.nta.eua.tw               |

|            | First Name       | Last Name         | Affiliation, Country                       | email address                                     |

|------------|------------------|-------------------|--------------------------------------------|---------------------------------------------------|

| 44.        | Dimitri          | Lederer           | Tyndall, Ireland                           | dimitri.lederer@tyndall.ie                        |

| 45.        | Chi-Woo          | Lee               | Tyndall, Ireland                           | chi-woo.lee@tyndall.ie                            |

| 46.        | Vladimir         | Lysenko           | ISP, Ukraine                               | lysenko@lab15.kiev.ua                             |

| 47.        | Bogdan           | Majkusiak         | Warsaw University of<br>Technology, Poland | majkusiak@imio.pw.edu.pl                          |

| 48.        | David            | Martin            | Uppsala University,<br>Sweden              | david.martin@angstrom.uu.se                       |

| 49.        | Joao             | Martino           | University of Sao<br>Paulo, Brazil         | martino@lsi.usp.br                                |

| 50.        | Jean-Paul        | Mazellier         | LETI, France                               | jean-paul.mazellier@cea.fr                        |

| 51.        | Alexei           | Nazarov           |                                            | nazarov@lab15.kiev.ua                             |

| 52.        | Atsushi          | Ogura             | Meiji University,<br>Japan                 | a_ogura@isc.meiji.ac.jp                           |

| 53.        | Serguei          | Okhonin           | Innovative Silicon<br>Inc., Switzerland    | sokhonin@z-ram.com                                |

| 54.        | Benoit           | Olbrechts         | UCL, Belgium                               | benoit.olbrechts@uclouvain.be                     |

| 55.        | JÖrgen           | Olsson            | Uppsala University,<br>Sweden              | jorgen.olsson@angstrom.uu.se                      |

| 56.        | Jong Tae         | Park              | Korea                                      | jtpark@incheon.ac.kr                              |

| 57.        | Elena            | Pascual           | University of<br>Salamanca, Spain          | elenapc@usal.es                                   |

| 58.        | Carine           | Pastore           | ST, France                                 | carine.pastore@st.com                             |

| 59.        | Johan            | Piscator          | Chalmers U.,<br>Sweden                     | johan.piscator@chalmers.se                        |

| 60.        | Quentin          | Rafhay            | IMEP, France                               | rafhay@enserg.fr                                  |

| 61.        | Jean-Pierre      | Raskin            | UCL, Belgium                               | jean-pierre.raskin@uclouvain.be                   |

| 62.        | Cesar            | Roda Neve         | UCL, Belgium                               | cesar.rodaneve@uclouvain.be                       |

| 63.        | Jean-Marc        | Routoure          | rrance                                     | routoure@greyc.ensicaen.fr                        |

| 64.        | Fred             | Ruddell           | Belfast, UK                                | f.ruddell@qub.ac.uk                               |

| 65.        | Tamara           | Rudenko           | ISP, Ukraine                               | tamara@lab15.kiev.ua                              |

| 66.        | Cora             | Salm              | U. Twente, The<br>Netherlands              | c.salm@utwente.nl                                 |

| 67.        | Carlos           | Sampedro          |                                            | csampe@ugr.es                                     |

| 68.        | Andreas          | Schenk            | ETH Zurich,<br>Switzerland                 | schenk@iis.ee.ethz.ch                             |

| 69.        | Jurriaan         | Schmitz           | U. Twente, The<br>Netherlands              | j.schmitz@utwente.nl                              |

| 70.        | Gil              | Shalev            |                                            | gil.shalev@intel.com                              |

| 71.        | Viktor           | Sverdlov          | TU Wien, Austria                           | sverdlov@iue.tuwien.ac.at                         |

| 72.        | Julio            | Tinoco            | UCL, Belgium                               | julio.tinoco@uclouvain.be                         |

| 73.        | Örjan            | Vallin            | Uppsala University,<br>Sweden              | orjan.vallin@angstrom.uu.se                       |

| 74.        | Andrei           | Vladimirescu      | ISEP, France                               | andreiv@isep.fr                                   |

| 75.        | Ran              | Yan               | Tyndall, Ireland                           | ran.yan@tyndall.ie                                |

| 76.        | Tetsuya          | Yoshida           | Meiji U., Japan                            | ce77087@isc.meiji.ac.jp                           |

| 77.        |                  | PNG Group         | Tyndall, Ireland                           |                                                   |

| 78.<br>79. | Fabrice<br>Singh | Nehouchi<br>Jagar | LETI, France<br>Analog Devices,<br>Ireland | fabrice.nemouchi@cea.fr<br>jagar.singh@analog.com |

| 80.        | Damien           | Bretegnier        |                                            | damien.bretenier@soitec.fr                        |

| 81.        | Worawat          | Khunsin           | JOILO                                      | <u>aarmon.brotomon@30itec.ii</u>                  |

| 01.        | Ivvoiawat        | i a lulioli i     | <u> </u>                                   |                                                   |

## 4.- Selection of papers to be published in Solid State Electronics Journal

|     | Title                                                                                                                                     | Author                           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.  | INVITED PAPER: Z-RAM Memory Technology                                                                                                    | S Okhonin, Innovative<br>Silicon |

| 2.  | INVITED PAPER: Review of Advanced Substrate trends                                                                                        | L. Clavelier, LETI               |

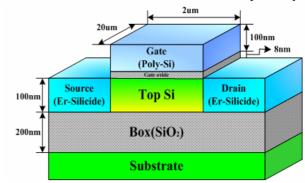

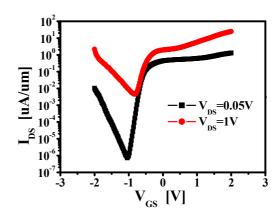

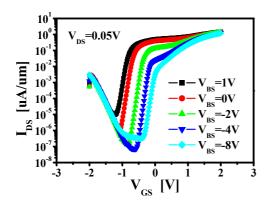

| 3.  | Paper 7.1: Substrate bias effects on the performance of Schottky-<br>barrier SOI nMOSFETs                                                 | Jong Tae Park, U<br>Incheon      |

| 4.  | Paper 2.4: Improved Source-Follower Buffer Implementation by Using Graded-Channel SOI nMOSFETs                                            | M. de Souza, USP                 |

|     | Paper 3.1: Electron Subband Structure and Controlled Valley<br>Splitting in Silicon Thin Body SOI FETs: Two-Band k•p Theory and<br>Beyond | V. Sverdlov, TU Wien             |

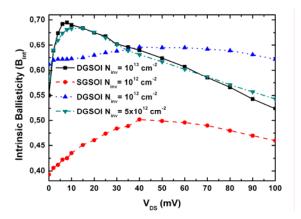

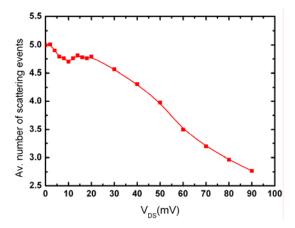

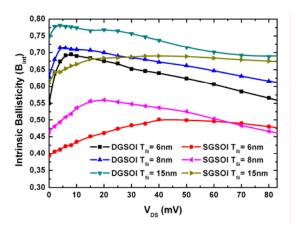

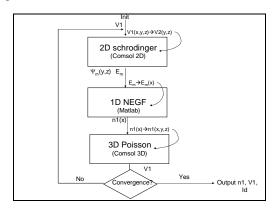

| 6.  | Paper 3.3: Study of Ballisticity in SOI Nano-MOSFETs at Very Low<br>Drain Bias                                                            | C. Sampedro, U Granada           |

|     | Paper 4.1: Silicon-on-SiC hybrid substrate with improved high-<br>frequency and thermal performance                                       | J. Olsson, Uppsala U             |

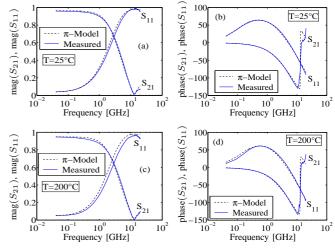

| 8.  | Paper 4.2: High-Temperature RF Behavior of Partially-Depleted SOI MOSFET Transistors                                                      | M. Emam, UCL                     |

| 9.  | Doping Fluctuation Effects in Trigate SOI MOSFETs                                                                                         | R. Yan, Tyndall                  |

| 10. | STI-Induced Mechanical Stress-Related Kink Effect of 40nm PD<br>SOI NMOS Devices                                                          | JB. Kuo, Taipei                  |

| 11. | Germanium on Sapphire By Wafer Bonding                                                                                                    | P. Baine, Queen's U<br>Belfast   |

| 12. | Equivalent Oxide Thickness of SOI-GAA devices                                                                                             | F.J. García Ruiz, U<br>Granada   |

| 13. | On the switching speed of SOI LEDs                                                                                                        | J. Schmitz, MESA, U<br>Twente    |

|     | New Explicit Compact Charge and Capacitance Model for<br>Undoped Ultra-Thin Body Silicon-on-Insulator (UTB-SOI)<br>MOSFETs                           | O. Modovan, U<br>Barcelona                      |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 15. | Paper 5.3: Evaluation of super-critical thickness strained-Si on insulator (sc-SSOI) substrate                                                       | T. Yoshida, Meiji U                             |

| 16. | Paper 7.2: A Radiation Study of High-Resistivity SOI Substrates for High Energy Physics Applications                                                 | S. Ruddell, Queen's U<br>Belfast                |

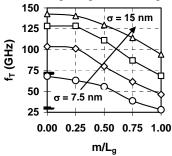

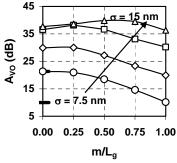

| 17. | Paper 7.4: How Crucial is Gate Misalignment for Low–Voltage<br>Operation in Double Gate SOI MOSFETs?                                                 | A .Kranti, Queen's U<br>Belfast                 |

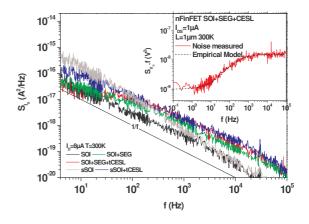

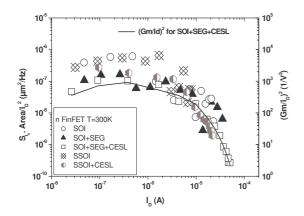

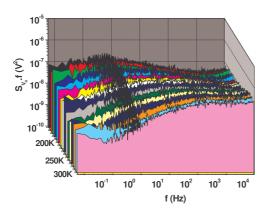

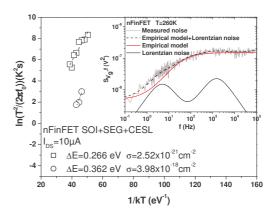

|     | Paper 8.3: Unusual Noise Behavior Versus Temperature in nFinFETs on Silicon on Insulator (SOI) Substrates Processed with Different Strain Techniques | W. Guo, U Caen                                  |

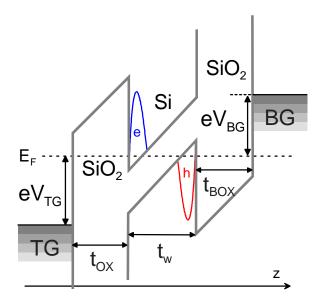

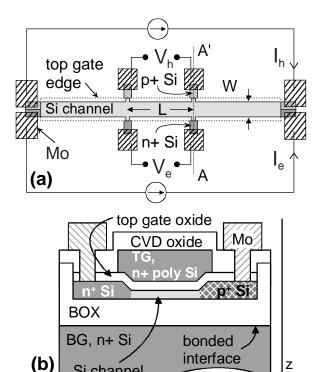

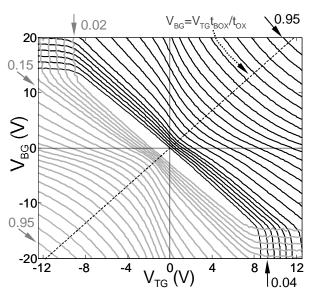

| 19. | Paper 8.4: Co-existence of two-dimensional electron and hole gases in thin double-gate SOI FETs                                                      | M. Prunnila, VTT                                |

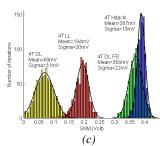

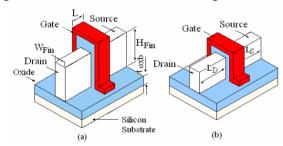

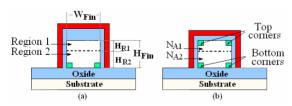

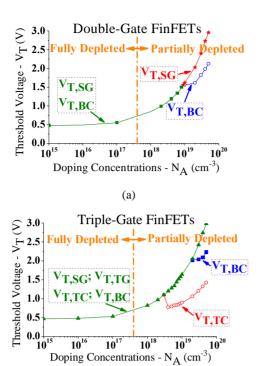

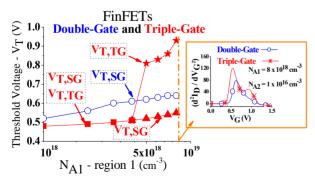

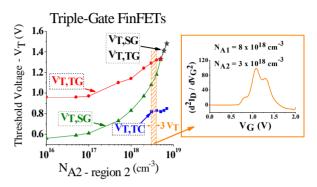

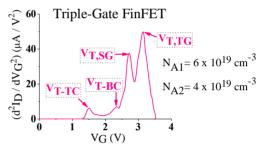

|     | Paper 2.1: Threshold Voltages of Double and Triple Gate SOI<br>FinFETs                                                                               | M. Caño de Andrade,<br>USP                      |

| 21. | Paper 2.3: Ultra-Low-Power Logic Style for Low-Frequency High-<br>Temperature Applications                                                           | D. Bol, UCL                                     |

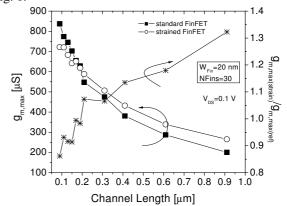

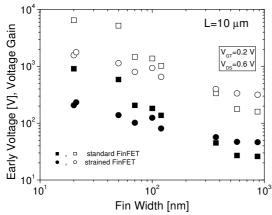

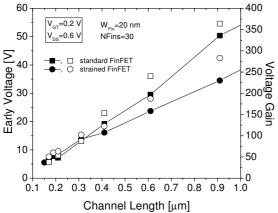

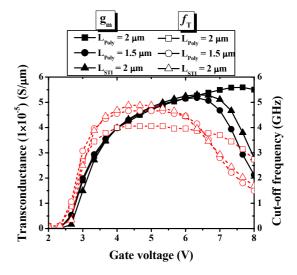

| 22. | Paper 7.3: Comparison Between Analog Performance of Standard and Strained Triple-Gate nFinFETs                                                       | M. A. Pavanello, Centro<br>Universitário da FEI |

| 23. | Paper 6.3: Temperature Behavior of Spiral Inductors on High<br>Resistivity Substrate in SOI CMOS Technology                                          | M. El Kaamouchi, UCL                            |

| 24. | Paper 3.2: Estimations of the Ion-Ioff Performances of Nano nMOSFETs with Alternative Channels Materials                                             | Q. Rafhay, IMEP-LAHC                            |

|     |                                                                                                                                                      |                                                 |

## 5.- Minutes of the Management Board Meeting held in Cork, on January 23<sup>rd</sup>, 2008

# **EUROSOI Management Board Meeting held in Cork, on 23-01-2008**

#### Attendees:

Prof. Sorin Cristoloveanu, IMEP, Grenoble

Prof. Jean Pierre-Colinge, Tyndall Institute, Cork

Prof. Cor Claeys, IMEC, Leuven

Prof. Denis Flandre, UCL, Louvain la Neuve

Prof. Olof Engstrom, Chalmers, Sweden

Dr. Olivier Faynot, LETI, CEA, Grenoble

Prof. Andrés Godoy, UGR, Granada

Prof. Francisco Gámiz, UGR, Granada (Co-ordinator)

The first management board meeting of EUROSOI+ project (FP7-ICT-2007-216373) was held in Cork, Ireland on January 23<sup>rd</sup>, 2008, with the following agenda:

- 1.- Welcome.

- 2.- Running Guidelines.

- 3.- Training activities.

- 4.- Scientific Exchange Program.

- 5.- Student Grants.

- 6.- Reports upgrading (SoA and Roadmap).

- 7.- Technological platform. Working plan.

- 8.- Questions and suggestions.

#### 1.- Welcome.

Prof. Colinge, organizer and General Chairman of the 4<sup>th</sup> EUROSOI Workshop welcomed all the attendees for this first MB meeting.

#### 2.- Running Guidelines.

Prof. Gámiz, EUROSOI Co-ordinator, thanked all the attendees for being present at this meeting and emphasized the importance of this new project. He summarized the objectives of the project, and highlighted the tasks which we will have to face along the following months. All the details and description about the work to carry out (DoW) can be found on the Annex I of the Grant

Agreement. This document (DoW) is available to all the contractors, and will be published on the Website (<a href="http://www.eurosoi.org">http://www.eurosoi.org</a>) as soon as possible for the consultation of all EUROSOI partners. Prof. Gamiz also mentioned that he would introduce the main objectives, tasks and goals of the project to EUROSOI partners during the Banquet Dinner.

The first task to be organized is the 4<sup>th</sup> EUROSOI+ Workshop and a Training Course to be held at Cork. Prof. Colinge, Chairman of the Workshop and Leader of WorkPackage 3 (Training activities on Silicon on Insulator Technology) gave the details of the two events.

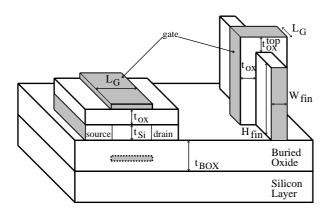

- With regard to the training event, Prof. Colinge mentioned that it was organized based on a book recently published by Springer and entitled "FinFETs and other multi-gate transistors", edited by Prof.Colinge (ISBN-978-0387-71751-7). The lectures were focused on each one of the chapters, and given by the corresponding authors. Thus, in addition to the viewgraphs of the lectures which were given to the participants before each lecture, the participants would have a reference text for further consultation.

- With regard to the Workshop, Prof. Colinge mentioned that there were 81 participants officially registered (46 at the short course) plus several Tyndall members who did not register. There were 21 students from EU and also participants coming from countries outside the EU such as Switzerland, Japan, South Korea, Taiwan, Brazil, Israel, Ukraine. There were 10 industrial participants (Analog Devices, SOITEC, INTEL, CISSOID, Innovative Silicon, EV group, ST, and Infineon). Regarding the communications we had 55 presentations (32 oral + 23 posters) and 2 invited presentations. As in previous Workshops, a selected number of communications will be published in an special issue of Solid-State Electronics Journal whose guest editors are Prof. Colinge and Prof. Lederer. In the DoW, it is mentioned that a person of each EUROSOI partner will have a reduction of 50% in the Workshop fee. As this workshop was organized before the signature of the contract with the Commission, all the attendees paid for the full fee. However, we agreed that this Workshop will be also supported by EUROSOI+ project. Prof. Colinge announced that after the Workshop he would contact the different partners who attended the Workshop for the reimbursement of half of the fee.

#### 3.- Training activities

In addition to the aforementioned Training Event, we also discussed about other related tasks to carry out:

**Task3.1.** Elaboration of the EUROSOI+ Distinguished Lecturers list. Prof. Claeys is the responsible for this deliverable (D3.1) to be finished in month 6 (M0+6).

**Task3.2.** Inventory of the SOI-related training material. Prof. Colinge in close collaboration with Prof. Godoy will design the strategy for the elaboration of this task.

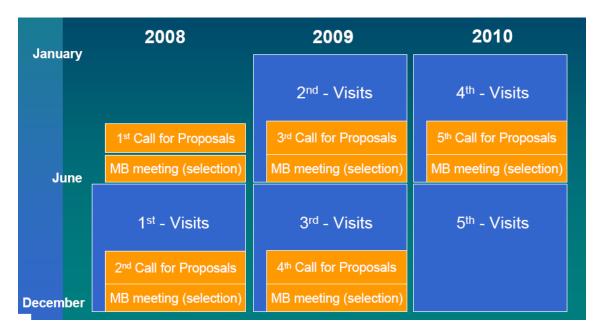

#### 4.- Scientific Exchange Program

We have budgeted 54 weeks (@1400€/week) for scientific visits between partners during the three years. We discussed and agreed the guidelines and application procedure according to the following points developed by Prof. Godoy:

1. Applicants should send a proposal including a short CV + comprehensive description of the visit (purpose, destination, duration, budget, etc) to the Coordinator before the following deadlines:

- Selection of proposals will be made by the MB in the corresponding meeting of June or December/January. The selection will take into account the following points:

- a. The field should fall within research domains defined by EUROSOI+.

- b. At least one EUROSOI member should be involved in the project research.

- c. Priority will be given to industrial partners.

- d. The visit must be shorter than 4 weeks.

- e. Gender aspects will be considered (promote the participation of women).

- f. No salary costs or expenses generated by research activities will be covered.

- 3. After the visit (less than one month), the participant should provide a report describing the work developed during the visit.

#### 5.- Student Grants

We have seven student grants (750€/each) to cover travel and registration fees of students who attend and present a paper in EUROSOI Workshops. One month before each Workshop, a call for applications will be launched. For Cork's Workshop, we will do it after the conference. All the students interested in applying for a Grant will submit to the coordinator a letter of support of his/her advisor before February, 15<sup>th</sup>. The MB will select seven applications among the ones received.

#### 6.- Report Upgrading

Prof. Godoy, Leader of WP2 (Networking activities), reminded that according to our Plan of Activities, Upgraded versions of State-of-the-Art report and EUROSOI Roadmap should be delivered in month 18 (M0+18). In order to be successful it is necessary to start to work on these tasks as soon as possible. He will develop a specific plan of work in the following days. Different partners will be invited to participate in the process. Monothematic meetings are foreseen in the future.

#### 7.- Technological platform

Dr. Olivier Faynot reported about the next steps in this WP5. As leader of WP5 Dr. Faynot will coordinate the characterization of LETI FDSOI devices which will be provided under request to the partners. He also mentioned the organization of specific monothematic working groups meetings to address this issue. The first one will be organized in month 9 (M0+9). FDSOI devices will be available for EUROSOI partners by March 08.

Dr. Olivier Faynot also reported on the organization of visits to different industrial companies to promote the use of FDSOI technology.

#### 8.- Questions and suggestions.

Finally we discussed about the possibility of joint organization of the EUROSOI+ Workshop and IEEE International SOI conference, as it has been suggested by IEEE members. The idea is to reduce the number of international SOI conferences so that their topics will be more focused, more visible and more attended. The joint conference would be organized one year in the USA and, in the following year, in Europe. However the co-ordinator reported that until the end of this project, EUROSOI workshop is a deliverable of the project and therefore it is not possible to organize it outside Europe. However, this is in fact a very interesting proposal, and it means that we are on the right path.

Finally, since there are no more issues to deal with, the co-ordinator thanked the attendants for coming to this meeting, and reminded them that the next MB meeting will be held at UCL, Louvain-la-Neuve, Belgium, in June, 2008.

## **CONCLUSIONS**

The fourth EUROSOI Workshop of the Thematic Network on Silicon on Insulator Technology, Devices and Circuits was held in Cork (Ireland) on 23-25 January, 2008 and was focused on recent theoretical, experimental and industrial progress on SOI materials, devices, and circuits. The meeting was attended by more than 80 researchers from labs, universities and industries all over Europe. Fifty five (55) accepted contributions were presented and widely discussed, successfully covering SOI topics, such as: i) SOI Materials, Devices and Systems; ii) Modelling and characterization; iii) Simulation; and iv) SOI Circuits and Applications.

This workshop became the appropriate forum to promote interaction and the exchange of information between research groups and industrial partners working in SOI. The main idea of the meeting was that each participant group should communicate their findings, opinions, experiences and conclusions about SOI questions. In this sense, the main workshop's goal is becoming a first step towards preparing future European task forces in SOI (RTD projects, collaborations, etc.)

We also wanted to have the point of view of different specialists coming from Industrial Centers. We had had two invited talks given by well-known experts in the field of SOI:

- Dr. Sergei Okhonin, Innovative Silicon, Switzerland, "ZRAM memory technology"

- Dr. Laurent Clavelier, CEA-LETI and SOITEC, France, "Review of advanced substrate trends"

We organized this rather informal and lively meeting, whose main objective was to discuss the situation of SOI technology in Europe. We had people from the EU, Switzerland, Japan, South Korea, Taiwan, Brazil, Israel, Ukraine. There were 21 students. There were 10 industrial participants from Analog Devices, SOITEC, INTEL, CISSOID, Innovative Silicon, EV group, ST, and Infineon.

We also organized a panel discussion chaired by Prof. Sorin Cristoloveanu from IMEP, Grenoble and composed by the following five experts:

- 1. Dr. Damien Bretegnier, SOITEC, France

- 2. Prof. Denis Flandre, UCL, Louvain-la-Neuve, Belgium

- 3. Dr. Sergei Okhonin, Innovative Silicon, Switzerland

- 4. Dr. Olivier Faynot, CEA-LETI, Grenoble France

- 5. Prof. Jean-Pierre Colinge, Tyndall, Cork, Ireland

Each expert presented his point of view and position on the SOI technology, future applications, and the European situation. After the initial positioning, there was a long live debate among the panellists and the rest of the audience and as a final consequence we can highlight the following three points:

- 1. There are plenty of "SOI species" which could be potential solutions for 22nm and below (SOI Zoo and Botanic Garden) but we need to designate an only SOI candidate among all of them. Otherwise it is impossible to advance our position much more from where we are now: we have excellent devices (LETI FDSOI, IMEC FinFETs, but very few circuit applications).

- 2. It is becoming urgent to involve/convince design people in next future to work using this only device

- The announcement of SOITEC about a strong reduction of SOI wafer price and according to SOITEC mainly focused on communication applications: "rather cheap mobile telephone with SOI inside".

Once more, the main conclusion we can draw from this workshop is the importance that the achievement of EUROSOI+ goals will have for the European Semiconductor Industry. In this respect it was highlighted the lack of prototyping capability in SOI in EUROPE, in spite of the fact that European companies have developed the most advanced SOI devices which are not accessible to many fabless companies or research groups whose designs would be much more competitive.

The final outcome of this meeting is a consequence of the quality of the contributions and the spirit of friendly cooperation shown by all the contributors. We wish to thank all of them for their effort. We would also like to thank all the people who enabled this meeting to take place, in particular Prof. J.P. Colinge, and Tyndall for its support.

A selection of the contributions presented at the Workshop will be published in a special issue of Solid State Electronics Journal devoted to the Fourth Workshop of the Thematic Network of Silicon on Insulator Technology, Devices and Circuits.

## **EUROSOI 2008**

Fourth Workshop of the Thematic Network on Silicon-On-Insulator Technology, Devices and Circuits

## **CONFERENCE PROCEEDINGS**

23-25 January 2008 Cork, Ireland

## **EUROSOI** is organized by

## **Tyndall**

Tyndall National Institute

## and sponsored by

#### **EUROSOI**

Thematic Network on Silicon-On-Insulator Technology, Devices and Circuits

### **CISSOID**

Harsh Environment Electronics Solutions

### Welcome - Fáilte

SOI holds now a 35% market share of the logic integrated circuit industry. SOI is mainly used for microprocessor, gaming and mobile applications, but SOI has also deeply penetrated other markets, such as memory, power and high-temperature electronics. Multi-core microprocessors built on a 45nm silicon-on-insulator copper process are now an industrial reality and SOI has earned its place on the ITRS roadmap.

The EUROSOI initiative was set up in order to foster strong interactions among SOI material specialists, device experts, and circuit & system designers. The initial EUROSOI Thematic Network, involving 29 partners from 14 countries and supported by the Information Society of the European Union, came to a completion in 2006. The Network was re-conducted in 2008 under the name EUROSOI+.

After the success of the three first EUROSOI Workshops in Granada (2005), Grenoble (2006) and Leuven (2007), it was decided to organize a fourth edition in Cork in 2008.

This year's workshop features a Short Course on Multi-Gate SOI Technology. The importance of Multi-Gate devices is now fully recognized by the ITRS roadmap. The Short Course lectures are given by world-leading experts and focus on the opportunities offered by Multi-Gate FETs and on the challenges they pose in the field of fabrication, device physics and circuit design.

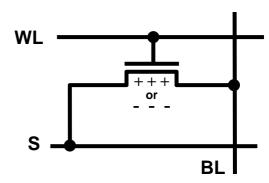

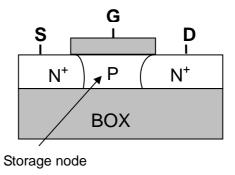

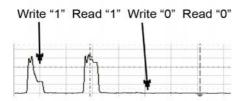

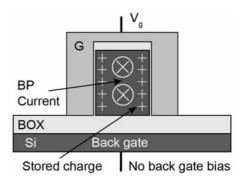

One of the most recent successful offspring of SOI technology is the single-transistor, zero-capacitor memory cell. It was named the number one winning technology by *IEEE Spectrum* Magazine readers in April 2007. EUROSOI has invited Dr. Serguei Okhonin of Innovative Silicon Inc. to present the latest in zero-capacitor SOI memory technology.

Heterogeneous integration techniques require innovations in the field of substrate engineering. Dr. Laurent Clavelier of CEA/LETI has accepted an invitation from EUROSOI to share with us the most recent results in advanced substrate synthesis techniques.

I want to thank all the authors for their contribution and the members of the Steering and Organizing Committees for their help putting together the Workshop. Welcoming the participants coming from all four corners of our little planet, I am looking forward to an exciting conference in the charming city of Cork.

Jean-Pierre Colinge EUROSOI 2008 Chair

## **Organizing Committee**

Prof. Jean-Pierre Colinge (Chair) Tyndall National Institute

Dr. John Alderman Tyndall National Institute

Dr. Russell Duane Tyndall National Institute

Dr. Dimitri Lederer Tyndall National Institute

Dr. Jenny Patterson Intel

Mrs. Ran Yan Tyndall National Institute

## **Steering Committee**

Prof. Stefan Bengtsson Chalmers, Sweden

Prof. Cor Claeys IMEC, Belgium

Prof. Sorin Cristoloveanu IMEP, Grenoble, France

Dr. Pierre Delatte CISSOID, Belgium

Prof. Denis Flandre UCL, Belgium

Prof. Francisco Gámiz Universidad Granada, Spain

Dr. Bruno Ghyselen SOITEC, France

Prof. Ilka Suni VTT, Finland

## **Workshop Program**

#### Wednesday, January 23: Training Course

#### Conference welcome reception

#### Thursday, January 24: Technical Program

Session 1: SOI Memory Devices

Chair: D. Flandre

Session 2: Device Modelling and SOI Circuits

Chair: P. Delatte

Session 3: Quantum Device Modelling

Chair: S. Cristoloveanu

Session 4: Active RF devices

Chair: D. Lederer

**Poster Session**

**Conference Dinner**

#### Friday, January 25: Technical Program

Session 5: SOI Material Characterization

Chair: C. Claeys

Session 6: Passive RF devices

Chair: J.-P. Raskin

Discussion panel

Session 7: SOI Device Physics and Characterization I

Chair: F. Gámiz

Session 8: SOI Device Physics and Characterization II

Chair: J. Alderman

# Short Course on Multi-Gate SOI MOSFETs

#### Wednesday, January 23, 2008

| 08:30       | REGISTRATION                                                     |                   |

|-------------|------------------------------------------------------------------|-------------------|

| 09:15       | Welcome Address                                                  | D. Lederer        |

| 09:30       | The SOI MOSFET: from Single Gate to Multi-Gate                   | JP. Colinge       |

| 10:10       | COFFEE BREAK                                                     |                   |

| 10:30       | Multi-Gate MOSFET Technology                                     | M. Jurczak        |

| 11:20       | Physics of the Multi-Gate MOS System                             | B. Majkusiak      |

| 12:10       | LUNCH                                                            |                   |

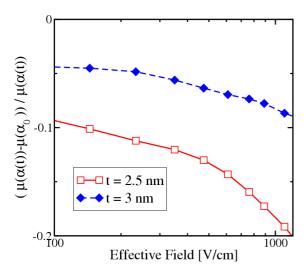

| 14:00       | Mobility in Multi-Gate MOSFETs                                   | F. Gámiz          |

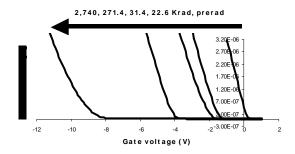

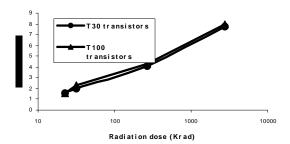

| 14:50       | Radiation Effects in Advanced Single- and Multi-Gate SOI MOSFETs | V. Ferlet-Cavrois |

| 15:40       | COFFEE BREAK                                                     |                   |

| 16:00-16:50 | Multi-Gate MOSFET Circuit Design                                 | G. Knoblinger     |

|             |                                                                  |                   |

## **Technical Program Schedule**

#### Thursday, January 24, 2008

| 08:30 | REGIS | TRATION |

|-------|-------|---------|

#### 09:00 **OPENING ADDRESS**

R. Whatmore and J.-P. Colinge, Tyndall National Institute, Cork, Ireland

|       | Session 1. SOI Memory Devices Chair: D. Flandre, DICE, UCL, Belgium                                                                                                          |    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

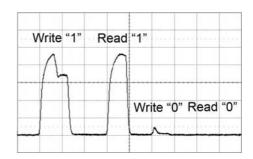

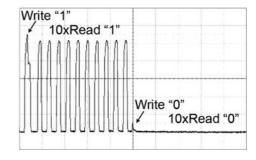

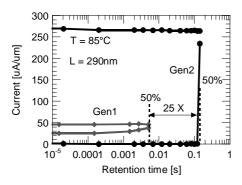

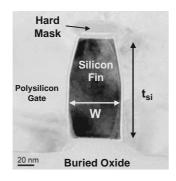

| 09:10 | <b>Z-RAM Memory Technology, Invited</b> S. Okhonin, M. Nagoga Innovative Silicon                                                                                             | 19 |

| 09:40 | Influence of Gate-Underlap Design on the Performance of 6T-SRAM Cell with Double Gate SOI MOSFETs Rashmi, A. Kranti and G.A. Armstrong NISRC, Queen's University Belfast, UK | 23 |

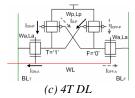

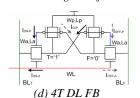

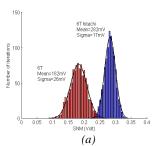

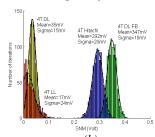

| 10:00 | An In-Depth Study of SRAM Cells in Double-Gate CMOS with Statistical Variation  B. Giraud, A. Vladimirescu and A. Amara ISEP, Paris, France                                  | 25 |

#### 10:20 **COFFEE BREAK**

|       | Session 2. Device Modelling and SOI Circuits Chair: P. Delatte, CISSOID, Louvain-la-Neuve, Belgium                                                                                                                                                                                                                                                                        |    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 10:40 | Threshold Voltages of Double and Triple Gate SOI FinFETs M. G. Caño de Andrade¹ and J. A. Martino²¹Centro Universitário da FEI, São Bernardo do Campo, Brazil²LSI/PSI/USP, University of São Paulo, São Paulo, Brazil                                                                                                                                                     | 29 |

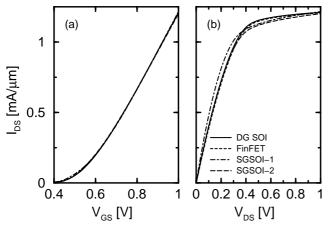

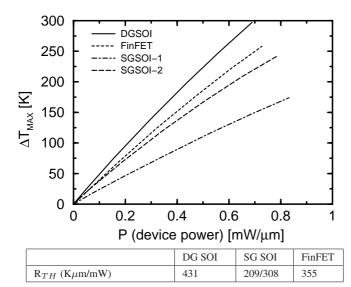

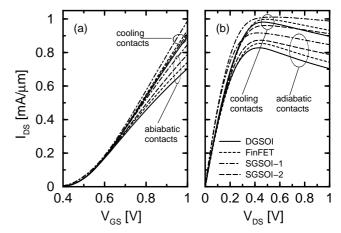

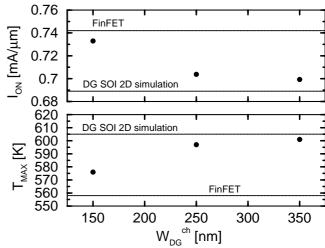

| 11:00 | Comparative Analysis of Self-Heating in Different SOI Architectures M. Braccioli, C. Fiegna and E. Sangiorgi ARCES-DEIS, University of Bologna, Cesena, Italy                                                                                                                                                                                                             | 31 |

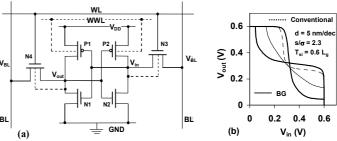

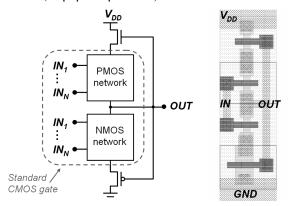

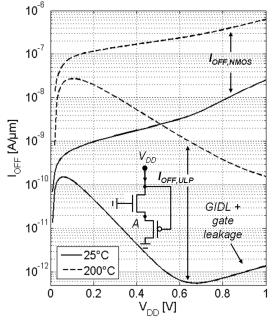

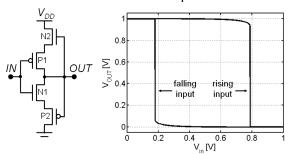

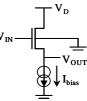

| 11:20 | Ultra-Low-Power Logic Style for Low-Frequency High-Temperature Applications D. Bol, D. Flandre and JD. Legat DICE, UCL, Louvain-la-Neuve, BELGIUM                                                                                                                                                                                                                         | 33 |

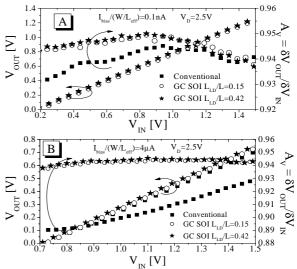

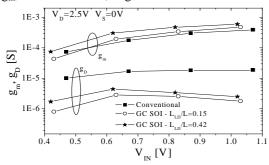

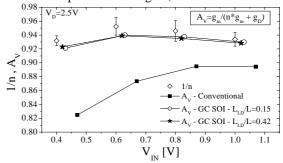

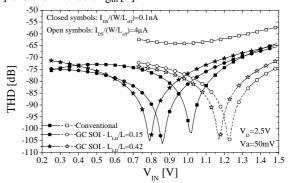

| 11:40 | Improved Source-Follower Buffer Implementation by Using Graded-Channel SOI nMOSFETs  M. de Souza <sup>1</sup> , D. Flandre <sup>2</sup> and M. A. Pavanello <sup>1,3</sup> <sup>1</sup> LSI/PSI/USP, University of São Paulo, São Paulo, Brazil <sup>2</sup> DICE, UCL, Louvain-la-Neuve, Belgium <sup>3</sup> Centro Universitário da FEI, São Bernardo do Campo, Brazil | 35 |

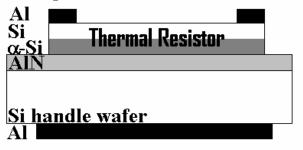

| 12:00 | Introduction of Diamond into Advanced FDSOI CMOS  JP. Mazellier <sup>1,2</sup> , O. Faynot <sup>1</sup> , F. Andrieu <sup>1</sup> , S. Cristoloveanu <sup>2</sup> and S. Deleonibus <sup>1</sup> <sup>1</sup> CEA LETI - MINATEC, Grenoble, France <sup>2</sup> IMEP-INP, MINATEC, Grenoble, France                                                                       | 37 |

#### 12:20 **LUNCH**

|       | Session 3. Quantum Device Modelling Chair: S. Cristoloveanu, IMEP, Grenoble, France                                                                                                                                                                                                                                                |    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

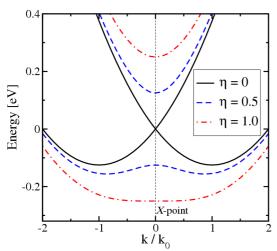

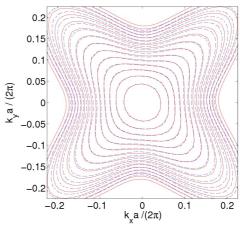

| 14:00 | Electron Subband Structure and Controlled Valley Splitting in Silicon Thin Body SOI FETs: Two-Band k*p Theory and Beyond V. Sverdlov, H. Kosina, and S. Selberherr Institute for Microelectronics, TU Wien, Wien, Austria                                                                                                          | 41 |

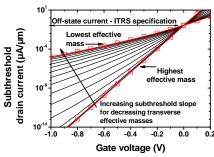

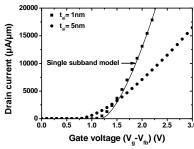

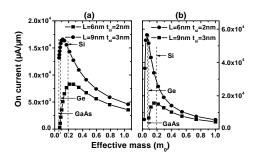

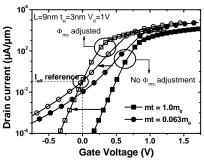

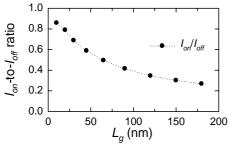

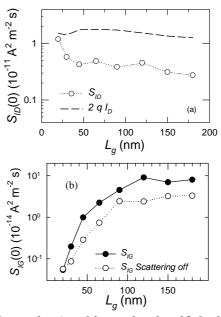

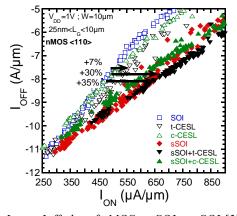

| 14:20 | Estimations of the Ion-loff Performances of Nano nMOSFETs with Alternative Channels Materials Q. Rafhay, R. Clerc, G. Pananakakis and G. Ghibaudo IMEP-LAHC (INPG-UJF-CNRS), Minatec, Grenoble, France                                                                                                                             | 43 |

| 14:40 | Study of Ballisticity in SOI Nano-MOSFETs at Very Low Drain Bias C. Sampedro <sup>1</sup> , F. Gámiz <sup>1</sup> , A. Godoy <sup>1</sup> , S. Cristoloveanu <sup>2</sup> and I. M. Tienda-Luna <sup>1</sup> Dpt de Electrónica y Tecn. de Computadores, University of Granada, Granada, Spain IMEP-INP, MINATEC, Grenoble, France | 45 |

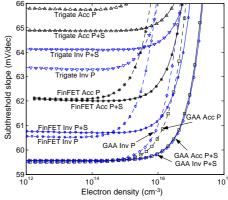

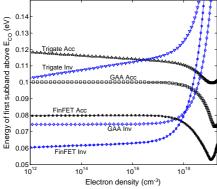

| 15:00 | Ultra Scaled MultiGate SOI MOSFETs: Accumulation-Mode vs. Inversion-Mode  A. Afzalian, D. Lederer, Chi-Woo Lee, Ran Yan and JP. Colinge Tyndall National Institute, Cork, Ireland                                                                                                                                                  | 47 |

#### 15:20 **COFFEE BREAK**

|       | Session 4. Active RF Devices Chair : D. Lederer, Tyndall National Institute, Cork, Ireland                                                                                                                                                                                                                       |    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

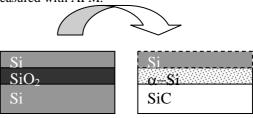

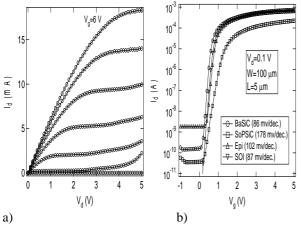

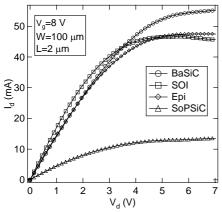

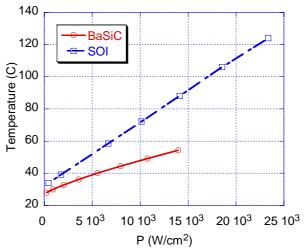

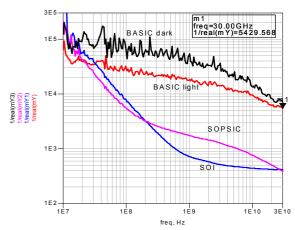

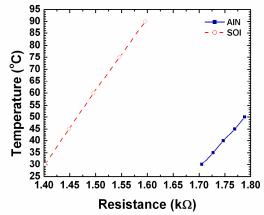

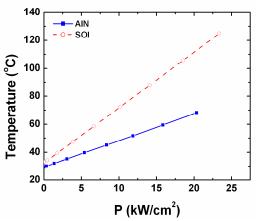

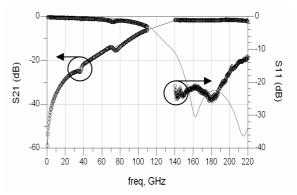

| 15:40 | Silicon-on-SiC Hybrid Substrate with Improved High-Frequency and Thermal Performance  J. Olsson¹, Ö. Vallin¹, D. Martin¹, L. Vestling¹, U. Smith¹ and H. Norström²  ¹ The Ångström Laboratory, Solid State Electronics, Uppsala University, Uppsala, Sweden  ² Infineon Technologies AB, SE-164 81 Kista, Sweden | 51 |

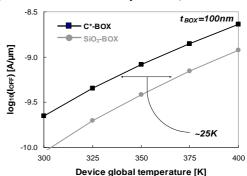

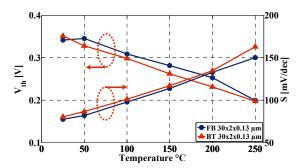

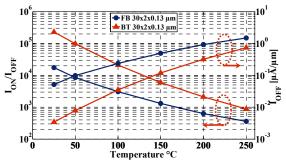

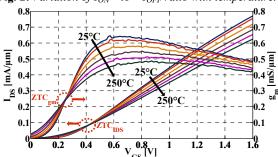

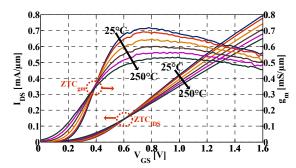

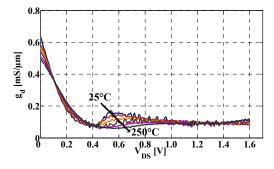

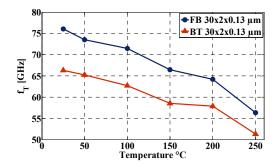

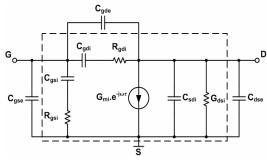

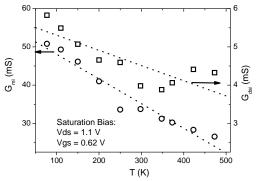

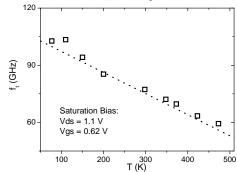

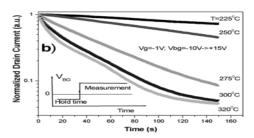

| 16:00 | High-Temperature RF Behavior of Partially-Depleted SOI MOSFET Transistors  M. Emam, J. C. Tinoco, D. Vanhoenacker-Janvier and JP. Raskin EMIC, UCL, Louvain-la-Neuve, Belgium                                                                                                                                    | 53 |

| 16:20 | RF Behavior of Strained Fully Depleted SOI MOSFETs S. Houri, M. Emam and JP. Raskin EMIC, UCL, Louvain-la-Neuve, Belgium                                                                                                                                                                                         | 55 |

| 16:40 | DC and RF Characteristics of FinFET over a Wide Temperature Range J. C. Tinoco <sup>1</sup> , B. Parvais <sup>2</sup> , A. Mercha <sup>2</sup> , S. Decoutere <sup>2</sup> and JP. Raskin <sup>1</sup> <sup>1</sup> EMIC, UCL, Louvain-la-Neuve, Belgium <sup>2</sup> IMEC Leuven, Belgium                       | 57 |

| 17:00- | Poster Session.                                                                                                                                                                                                                                                                                                                                |    |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 19:00  | Chair: R. Duane, Tyndall National Institute, Cork, Ireland                                                                                                                                                                                                                                                                                     |    |

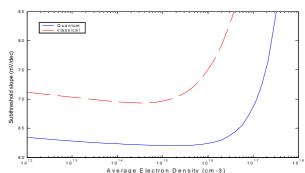

| P1     | Influence of Carrier Confinement on the Subthreshold Swing of Multigate SOI MOSFETs                                                                                                                                                                                                                                                            | 61 |

|        | JP. Colinge, A. Afzalian, D. Lederer, Chi-Woo Lee and Ran Yan<br>Tyndall National Institute, Cork, Ireland                                                                                                                                                                                                                                     |    |

| P2     | Triode-like Non-Saturation Characteristics of SOI-MOSFETs under Reverse Drain Bias                                                                                                                                                                                                                                                             | 63 |

|        | Takashi Ito, Koji Kotani, and Toshihiko Miyashita<br>Graduate School of Engineering, Tohoku University,Sendai, Japan                                                                                                                                                                                                                           |    |

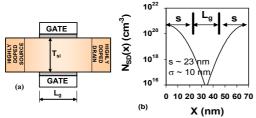

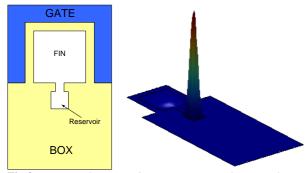

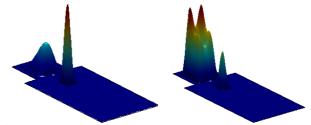

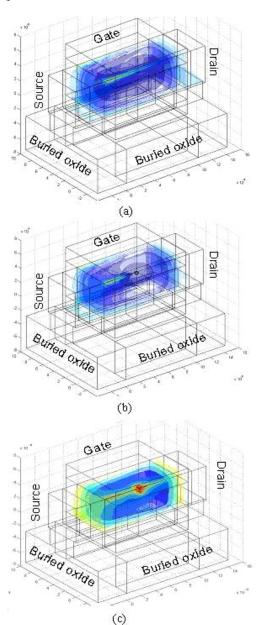

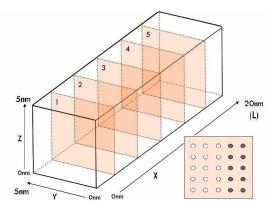

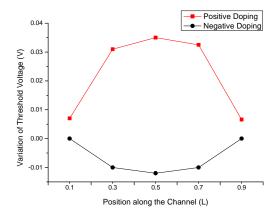

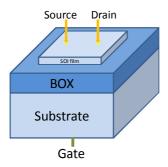

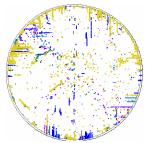

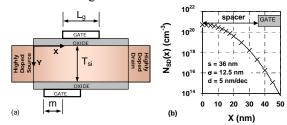

| P3     | Doping Fluctuation Effects in Trigate SOI MOSFETs  Ran Yan¹, D. Lynch², T. Cayron³, D. Lederer¹, A. Afzalian¹, Chi-Woo Lee¹ and J.P. Colinge¹ ¹ Tyndall National Institute, Lee Maltings, Prospect Row, Cork, Ireland ² University College Cork, Ireland ³ Institut National Polytechnique, Grenoble, France                                   | 65 |

| P4     |                                                                                                                                                                                                                                                                                                                                                | 67 |

| F4     | Impact of the Top Surface Density of States on the Characteristics of Ultrathin SOI Pseudo-MOSFETs  N. Rodriguez <sup>1,2</sup> , S. Cristoloveanu <sup>2</sup> , T. Nguyen <sup>2</sup> and F. Gámiz <sup>1</sup> <sup>1</sup> Departamento de Electrónica, University of Granada, Granada, Spain <sup>2</sup> IMEP-MINATEC, Grenoble, France | 67 |

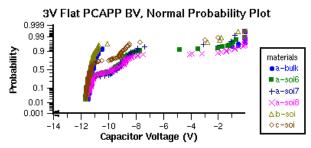

| P5     | Gate Oxide Integrity on SOI                                                                                                                                                                                                                                                                                                                    | 69 |

|        | P. Daly and S. Whiston Analog Devices BV, Limerick, Ireland                                                                                                                                                                                                                                                                                    |    |

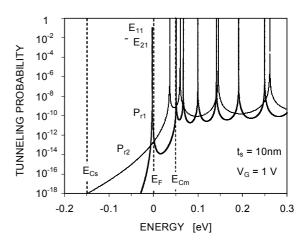

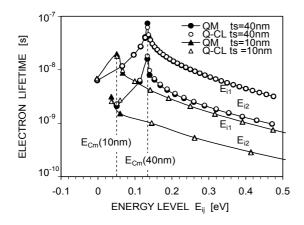

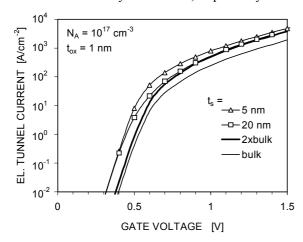

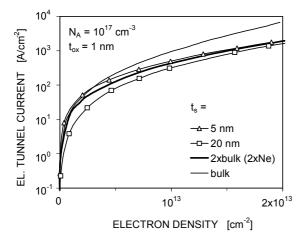

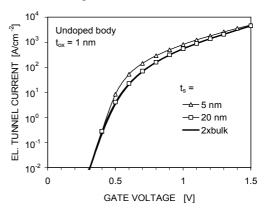

| P6     | Theoretical Considerations on Lifetime of Electrons in Quasi-Bound States and the Tunnel Current from the MOS/SOI Quantum Wells B. Majkusiak¹ and D. Flandre²¹ Inst. of Micro- and Optoelectronics, Warsaw University of Technology, Warsaw, Poland² DICE, UCL, Louvain-la-Neuve, Belgium                                                      | 71 |

| D7     | •                                                                                                                                                                                                                                                                                                                                              | 70 |

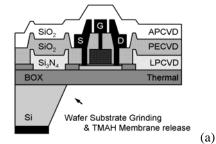

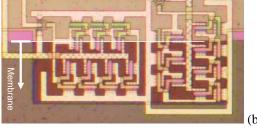

| P7     | Cross-Sensitivities of Ring Oscillators on Thin Dielectric Membrane for Pressure Sensing Applications  B. Olbrechts <sup>1</sup> , B. Rue <sup>2</sup> , D. Flandre <sup>2</sup> and JP. Raskin <sup>1</sup> EMIC and <sup>2</sup> DICE, UCL, Louvain-la-Neuve, Belgium                                                                        | 73 |

| P8     | <b>3-D Capacitive MEMS Sensors co-Integrated with SOI CMOS Circuits</b> <i>N. André</i> <sup>1</sup> , <i>B. Rue</i> <sup>1</sup> , <i>C. Renaux</i> <sup>1</sup> , <i>D. Flandre</i> <sup>1</sup> and <i>JP. Raskin</i> <sup>2</sup> <sup>1</sup> DICE and <sup>2</sup> EMIC, UCL, Louvain-la-Neuve, Belgium                                  | 75 |

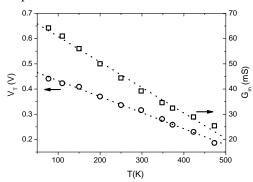

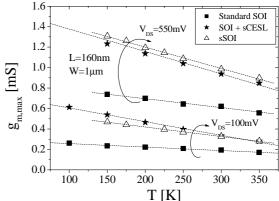

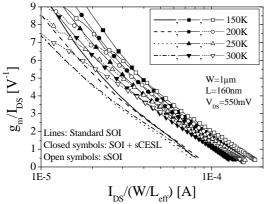

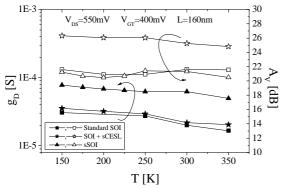

| P9     | Analog Operation of Uniaxially and Biaxially Strained FD SOI nMOSFETs at Cryogenic Temperatures                                                                                                                                                                                                                                                | 77 |

|        | M. de Souza <sup>1</sup> , J. A. Martino <sup>1</sup> , E. Simoen <sup>2</sup> , C. Claeys <sup>2,3</sup> and M. A. Pavanello <sup>1,4</sup> <sup>1</sup> LSI/PSI/USP, University of São Paulo, São Paulo, Brazil <sup>2</sup> IMEC, Leuven, Belgium                                                                                           |    |

|        | <sup>3</sup> E.E. Dept., KU Leuven, Leuven, Belgium<br><sup>4</sup> Centro Universitário da FEI, São Bernardo do Campo, Brazil                                                                                                                                                                                                                 |    |

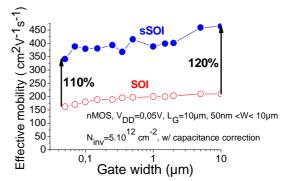

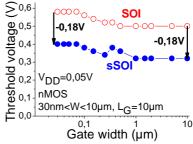

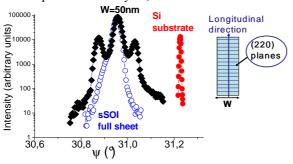

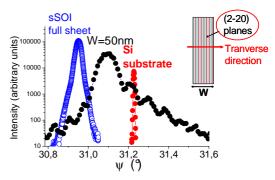

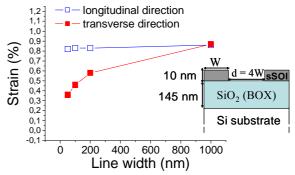

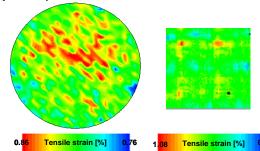

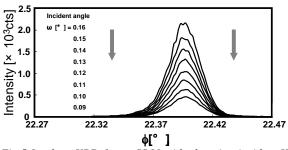

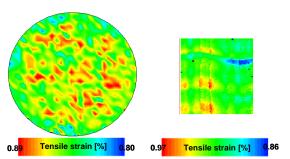

| P10    | Width Effects in 50nm Narrow Strained SOI: Electrical Characterizations of FDSOI nMOSFETs and Grazing Incidence X-Ray Diffraction Measurements                                                                                                                                                                                                 | 79 |

|        | S. Baudot <sup>1,2</sup> , J. Eymery <sup>1</sup> , F. Andrieu <sup>2</sup> , F. Rieutord <sup>1</sup> , O. Faynot <sup>2</sup> and S. Deleonibus <sup>2</sup> <sup>1</sup> CEA-CNRS group "Nanophys. et Semicond." and <sup>2</sup> CEA LETI, Minatec, Grenoble, France                                                                       |    |

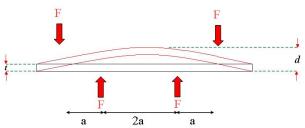

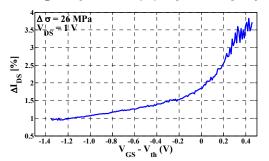

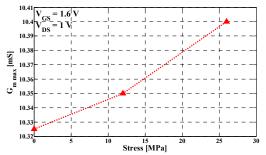

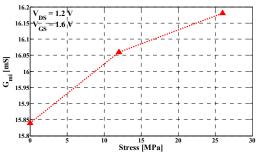

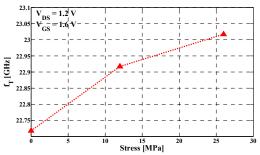

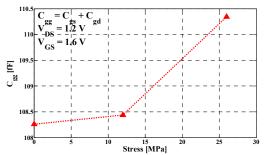

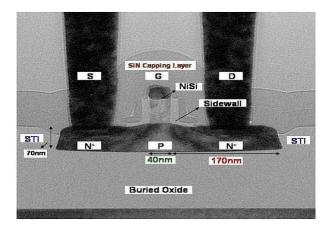

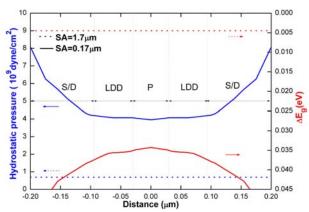

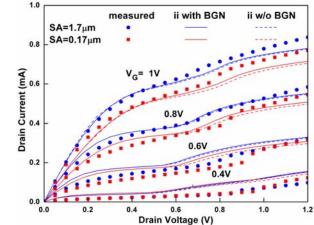

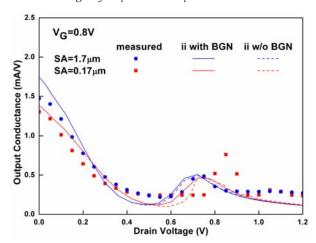

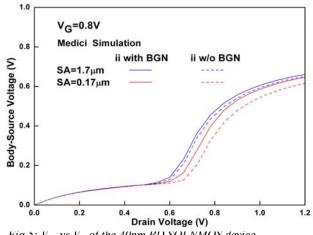

| P11    | STI-Induced Mechanical Stress-Related Kink Effect of 40nm PD SOI NMOS Devices                                                                                                                                                                                                                                                                  | 81 |

|        | I.S. Lin <sup>1</sup> , V.C. Su <sup>1</sup> , J. B. Kuo <sup>1</sup> , D. Chen <sup>2</sup> , C.S. Yeh <sup>2</sup> , C.Z. Tsal <sup>2</sup> , and M. Ma <sup>2</sup> <sup>1</sup> Dept of Electrical Eng., National Taiwan University, Taipei, Taiwan <sup>2</sup> UMC, Hsinchu, Taiwan                                                      |    |

| 17:00- | Poster Session (Ctd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 19:00  | Chair: R. Duane, Tyndall National Institute, Cork, Ireland                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

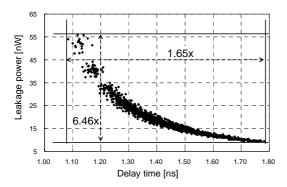

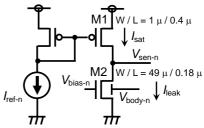

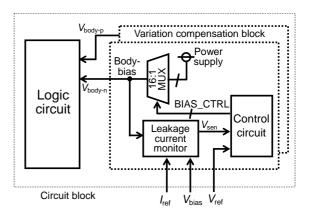

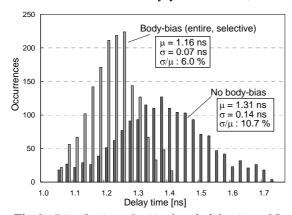

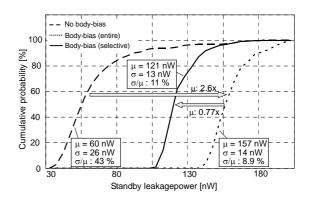

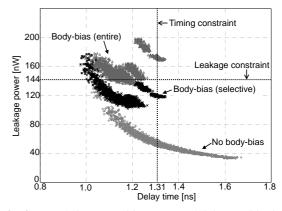

| P12    | Variation-Tolerant Design by Selective Body-Biasing Control on PD-SOI for Yield Improvement  Masaaki lijima <sup>1</sup> , Masayuki Kitamura <sup>1</sup> , Yosuke Torii <sup>1</sup> , Kayoko Seto <sup>1</sup> , Masahiro Numa <sup>1</sup> ,  Akira Tada <sup>2</sup> and Takashi Ipposhi <sup>2</sup> <sup>1</sup> Kobe University 1-1 Rokko-dai, Nada, Kobe 657-8501, Japan <sup>2</sup> Renesas Technology Corp, Itami, Japan                                                                                                                                                                                                                                                                                      | 83  |

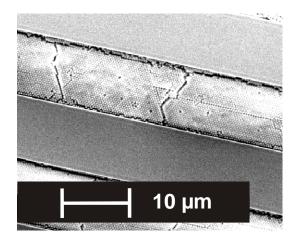

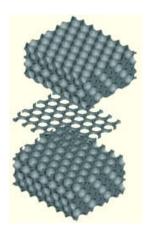

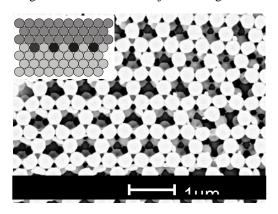

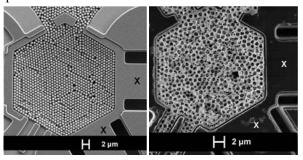

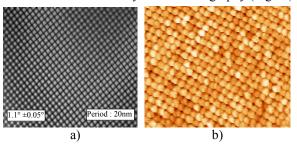

| P13    | SOI-Based 2D- and Si-Based 3D Photonic Crystals G. Kocher¹, W. Khunsin¹, J. Romero Vivas¹, K. Vynck², S. Arpiainen³, S. G. Romanov¹, B. B. Lange⁴, M. Mulot³, T. Charvolin⁵, E. Hajdi⁵, D. Cassagne², R. Zentel⁴, J. Ahopelto³, C. M. Sotomayor Torres¹,  ¹ Tyndall National Institute, Cork, Ireland ² GES UMR-CNRS, Université Montpellier II, Montpellier, France ³ Micro and Nanoelectronics, VTT Technical Research Centre of Finland, Finland ¹ Department of Chemistry, University of Mainz, Mainz, Germany ⁵ DRFMC/SPMM, CEA Grenoble, SiNaPS, Grenoble, France ⁶ Institute for Research and Advanced Studies, ICREA, Barcelona, Spain ⊓ Institut Fresnel, Faculté des Sciences et Techniques, Marseille, France | 85  |

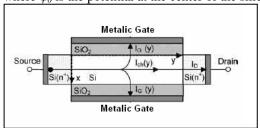

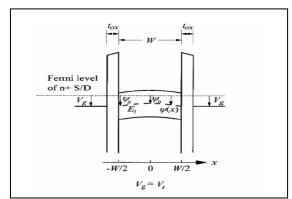

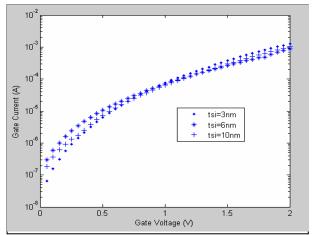

| P14    | Study of the Gate Direct Tunneling Current in Symetric DG MOSFET Based on an Analytic Potential Model F. Chaves, D. Jiménez and J. Suñé Departament d'Enginyeria Electrònica, Escola Tècnica Superior d'Enginyeria, Universitat Autònoma de Barcelona, Barcelona, Spain.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87  |

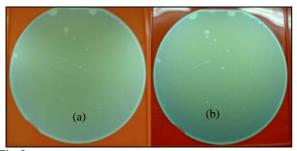

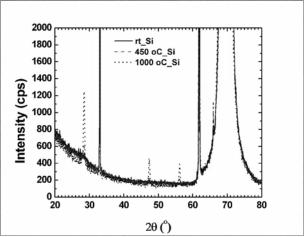

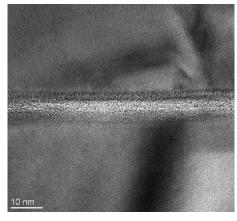

| P15    | Germanium on Sapphire By Wafer Bonding P.T Baine, H. Gamble, B.M. Armstrong, D.McNeill and S.J.N Mitchel Department of Electrical Engineering, Queens University Belfast, Belfast, UK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 89  |

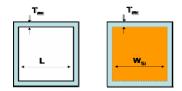

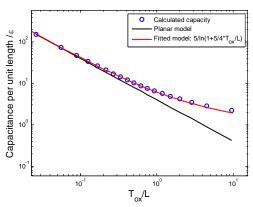

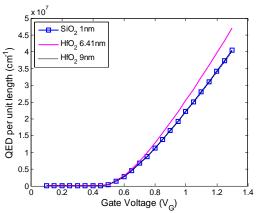

| P16    | Equivalent Oxide Thickness of SOI-GAA devices F. J. García Ruiz, I. M. Tienda-Luna, L. Donetti, A. Godoy and F. Gámiz Dpto. de Electrónica y Tecnología de los Computadores, Universidad de Granada, Spain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91  |

| P17    | Current-Voltage Model for Schottky-Barrier Graphene Based Transistors  D. Jiménez Departament d'Enginyeria Electrònica, Escola Tècnica Superior d'Enginyeria, Universitat Autònoma de Barcelona, Barcelona, Spain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 93  |

| P18    | Oxide Free Wafer Bonding of Silicon-On-Silicon Carbide Substrates<br>Ö. Vallin, D. Martin, U. Smith, and J. Olsson<br>The Ångström Laboratory, Solid State Electronics, Uppsala University, Uppsala, Sweden                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95  |

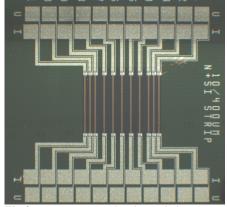

| P19    | Improved Thermal Characteristics in SOI using a Buried Aluminium Nitride Insulator  D. M. Martin*, Ö. Vallin, L. Vestling, I. Katardjiev and J. Olsson The Ångström Laboratory, Solid State Electronics, Uppsala University, Uppsala, Sweden                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 97  |

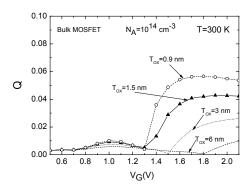

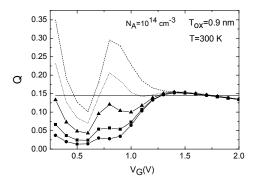

| P20    | In-Depth Characterization of Quantum Effects in SOI MOSFETs for Modeling Purposes  J. B. Roldán, M. Balaguer, A. Godoy, F. G. Ruiz and F. Gámiz Dpt de Electrónica y Tecn. de Computadores, University of Granada, Granada, Spain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 99  |

| P21    | On the Switching Speed of SOI LEDs  J. Schmitz, R. de Vries, C. Salm, Tu Hoang, R. Hueting and J. Holleman  MESA+ Institute for Nanotechnology, University of Twente, Enschede, The Netherlands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101 |

| 17:00-<br>19:00 | Poster Session (Ctd) Chair: R. Duane, Tyndall National Institute, Cork, Ireland                                                                                                                                                                                                                                                                                                                                                                                   |     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

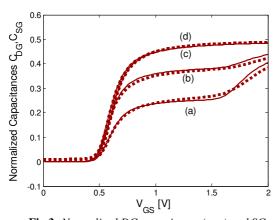

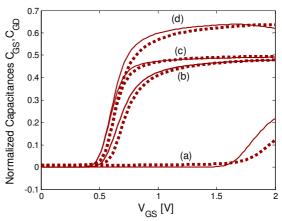

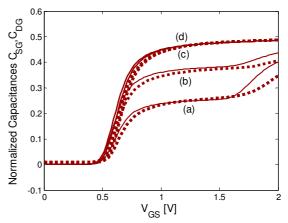

| P22             | New Explicit Compact Charge and Capacitance Model for Undoped Ultra-Thin Body Silicon-on-Insulator (UTB-SOI) MOSFETS  O. Moldovan <sup>1</sup> , F. A. Chaves <sup>2</sup> , D. Jiménez <sup>2</sup> and B. Iñiguez <sup>1</sup> Dpt d' Eng. Electrònica, Elèctrica i Automàtica, Universitat Rovira i Virgili, Tarragona, Spain <sup>2</sup> Dpt d' Eng. Electrònica, Escola Tècnica Superior d' Enginyeria, Universitat Autònoma de Barcelona, Barcelona, Spain | 103 |

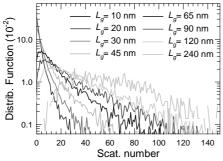

| P23             | Ballistic Transport and RF Noise in Ultra-Scaled SOI MOSFETs: a Monte Carlo Study  M. J. Martín, E. Pascual, T. González and R. Rengel Departamento de Física Aplicada, Universidad de Salamanca, Spain                                                                                                                                                                                                                                                           | 105 |

#### 19:30 **Conference Dinner**

Banquet Speaker: F. Gámiz, Universidad de Granada, Granada, Spain

## **Technical Program Schedule**

#### Friday, January 25, 2008

|       | Session 5. SOI Material characterization Chair: C. Claeys, IMEC, Leuven, Belgium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

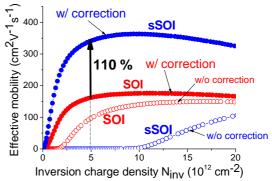

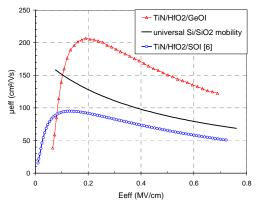

| 09:00 | Review of Advanced Substrates Trends, <i>Invited</i> L. Clavelier <sup>1</sup> , C Deguet <sup>1</sup> , F. Andrieu <sup>1</sup> , C. Le Royer <sup>1</sup> , Y. Letiec <sup>1</sup> , M. Kostrzewa <sup>1</sup> , J.P. Mazellier <sup>1</sup> , A. Tauzin <sup>1</sup> , J.S. Moulet <sup>2</sup> , F. Fournet <sup>1</sup> , O. Faynot <sup>1</sup> , F. Letertre <sup>2</sup> , I. Cayrefourcq <sup>2</sup> , B. Ghyselen <sup>2</sup> , C. Mazure <sup>2</sup> <sup>1</sup> CEA-LETI MINATEC, Grenoble, France <sup>2</sup> SOITEC, Bernin, FRANCE                                                   | 109 |

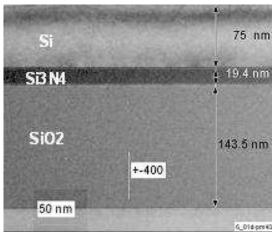

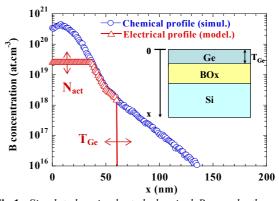

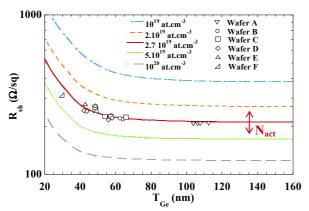

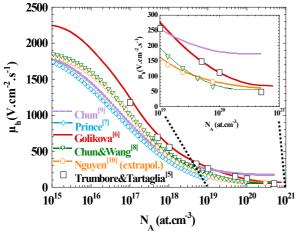

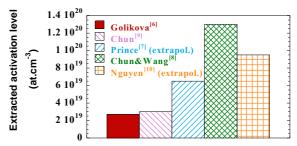

| 09:30 | On the Extraction of Dopant Activation Level for Boron-Doped Thin Germanium-On-Insulator (GeOI)  L. Hutin, S. Koffel, C. Le Royer, L. Clavelier, P. Scheiblin, V. Mazzocchi and S. Deleonibus CEA/LETI MINATEC, Grenoble, France                                                                                                                                                                                                                                                                                                                                                                         | 111 |

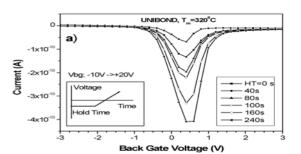

| 09:50 | Hydrogen as Source of High-Temperature Charge Instability in the Buried Oxide of SOI Structures and MOSFETs  A. Nazarov <sup>1</sup> , V. Lysenko <sup>1</sup> , J.P.Colinge <sup>2</sup> and D. Flandre <sup>3</sup> <sup>1</sup> Lashkaryov Institute of Semiconductor Physics, NASU, Kyiv, Ukraine <sup>2</sup> Tyndall National Institute, Cork, Ireland <sup>3</sup> DICE, UCL, Louvain-la-Neuve, Belgium                                                                                                                                                                                           | 113 |

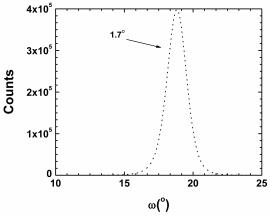

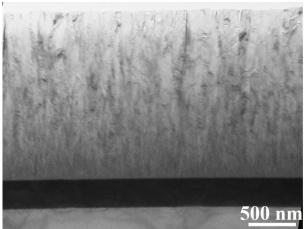

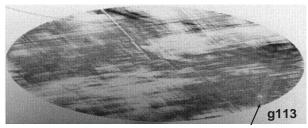

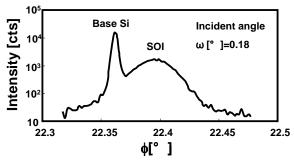

| 10:10 | Evaluation of Super-Critical Thickness Strained-Si On Insulator (sc-SSOI) Substrate T. Yoshida <sup>1</sup> , D. Kosemura <sup>1</sup> , Y. Kakemura <sup>1</sup> , M. Takei <sup>1</sup> , H. Saito <sup>1</sup> , A. Ogura <sup>1</sup> , T. Shimura <sup>2</sup> , T. Koganesawa <sup>3</sup> and I. Hirosawa <sup>3</sup> <sup>1</sup> School of Science and Technology, Meiji University Kawasaki, Kanagawa, Japan <sup>2</sup> Graduate School of Engineering, Osaka University, Suita, Osaka, Japan <sup>3</sup> Japan Synchrotron Radiation Research Institute, Sayo-cho, Sayo-gun, Hyogo, Japan | 115 |

#### 10:30 **COFFEE BREAK**

|       | Session 6. Passive RF Devices Chair: JP. Raskin, EMIC, UCL, Louvain-la-Neuve, Belgium                                                                                                                                                                                                                                                                          |     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

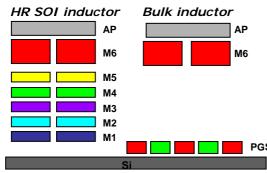

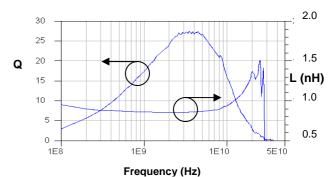

| 10:50 | High-Performance Thick Copper Inductors Integrated in Advanced High Resistivity SOI RF CMOS technology C. Pastore <sup>1,2</sup> , F. Gianesello <sup>1</sup> , D. Gloria <sup>1</sup> , E. Serret <sup>1</sup> , B. Rauber <sup>1</sup> and Ph. Benech <sup>2</sup> <sup>1</sup> STMicroelectronics, FTM, Crolles, France <sup>2</sup> IMEP, Grenoble, France | 119 |

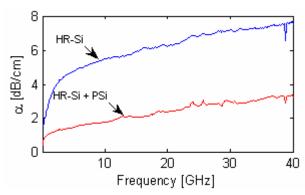

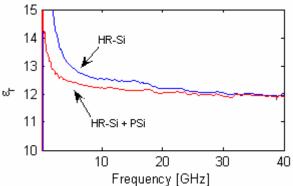

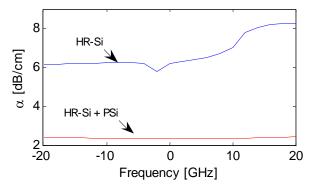

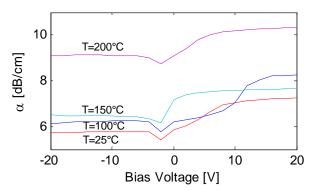

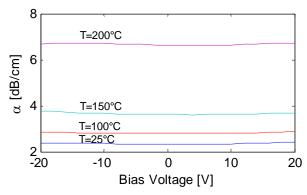

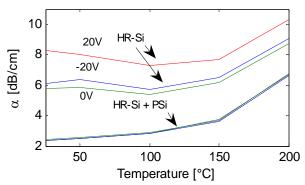

| 11:10 | Temperature and Bias Dependent Performance of Coplanar Waveguide on High Resistivity Silicon Substrate with Passivation Layer  C. Roda Neve <sup>1</sup> , D. Lederer <sup>2</sup> and JP. Raskin <sup>1</sup> <sup>1</sup> EMIC, UCL, Louvain-la-Neuve, Belgium <sup>2</sup> Tyndall National Institute, Lee Maltings, Prospect Row, Cork, Ireland            | 121 |

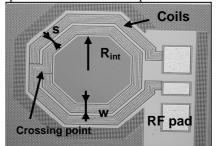

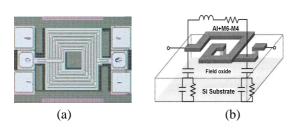

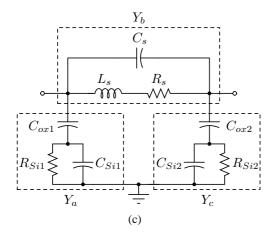

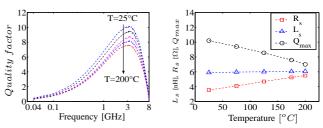

| 11:30 | Temperature Behavior of Spiral Inductors on High Resistivity Substrate in SOI CMOS Technology M. El Kaamouchi, M. Si Moussa, JP. Raskin and D. Vanhoenacker-Janvier EMIC, UCL,Louvain-la-Neuve, Belgium                                                                                                                                                        | 123 |

#### 11:50 **Discussion Panel**

Chair: S. Cristoloveanu, IMEP, Grenoble, France

#### 13:00 **LUNCH**

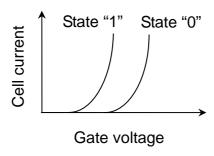

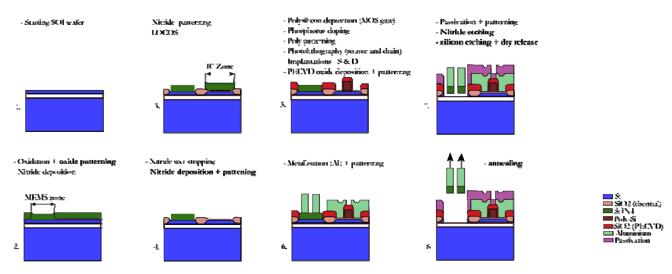

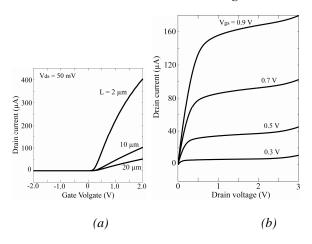

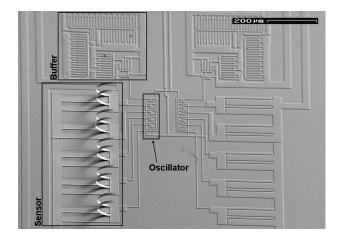

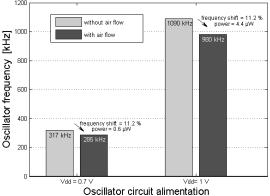

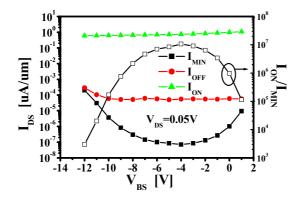

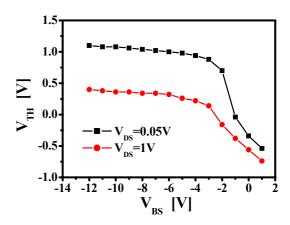

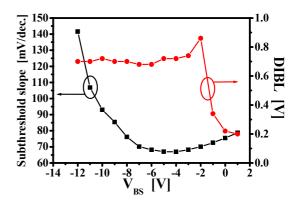

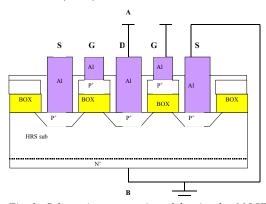

|       | Session 7. SOI Device Physics and Characterization I Chair: F. Gámiz, Universidad de Granada, Spain                                                                                                                                                                                                                                                                                                                                                                         |     |