ICT-2009.3.2-248603-IP

Modelling, Control and Management of Thermal Effects in Circuits of the Future

|             | WP no. | Deliverable no. | Lead participant |  |  |

|-------------|--------|-----------------|------------------|--|--|

| Cherminator | WP8    | D8.4.5          | STP              |  |  |

# **Preliminary THERMINATOR Roadmap**

Prepared by **B. Giacalone**

Issued by **THERMINATOR Project Office**

Document Number THERMINATOR/D8.4.5/v1.0

Dissemination Level Confidential

Date

© Copyright 2010-2013 STMicroelectronics, Intel Mobile Communications, NXP Semiconductors, GRADIENT DESIGN AUTOMATION, MUNEDA, SYNOPSYS, BUDAPESTI MUSZAKI ES GAZDASAGTUDOMANYI EGYETEM, CSEM, FRAUNHOFER, IMEC, CEA-LETI, OFFIS, Politecnico di Torino, ALMA MATER STUDIORUM -Universita' DI Bologna, ST-POLITO S.c.a.r.l.

This document and the information contained herein may not be copied, used or disclosed in whole or in part outside of the consortium except with prior written permission of the partners listed above.

#### 1 **Document**

| Title          | Preliminary THERMINATOR Roadmap                                 |

|----------------|-----------------------------------------------------------------|

| Type           | Deliverable CO                                                  |

| Ref            | D8.4.5                                                          |

| Target version |                                                                 |

| Current issue  |                                                                 |

| Status         |                                                                 |

| File           |                                                                 |

| Author(s)      | Biagio GIACALONE                                                |

|                |                                                                 |

| Reviewer(s)    | Moritz Voelker (IMC), Axel Erlebach (SNPS), Michelangelo Grosso |

|                | (STP)                                                           |

|                |                                                                 |

| Approver(s)    | Giuliana Gangemi (ST)                                           |

| Approval date  | 17-Dec-2012                                                     |

| Release date   |                                                                 |

|                | 17-Dec-2012                                                     |

|                |                                                                 |

#### 2 Distribution of the release

| Dissemination level | CO |

|---------------------|----|

| Distribution list   |    |

## History

| Rev. | DATE              | Comment                                                     |

|------|-------------------|-------------------------------------------------------------|

| 1.0  | 17 July 2012      | First skeleton of the document sent around to gather inputs |

| 1.1  | 28 July 2012      | First integration of partners inputs                        |

| 1.2  | 4 October<br>2012 | Second request of inputs                                    |

| 1.3  | 15 Nov 2012       | Second Integration amd major changes                        |

| 1.4  | 25 Nov 2012       | Sent for internal review                                    |

| 1.5  | 5-15 Dec<br>2012  | Implementation of Reviewers comments                        |

| 1.6  | 17 Dec 2012       | Approval and release                                        |

#### 3 References

**IPCA – THERMINATOR Consortium Agreement**, D8.4.1 "First Release of Market Survey"

| 1 I | Oocument                                                       | ii |

|-----|----------------------------------------------------------------|----|

| 2 E | Distribution of the release                                    | ii |

| 3 R | References                                                     | ii |

| 1 T | HERMINATOR Roadmap: Objective                                  | 1  |

|     | HERMINATOR Roadmapping Committee                               |    |

|     | THERMINATOR Roadmap: Introduction                              |    |

|     | -                                                              |    |

| 3.1 |                                                                |    |

| 3.2 |                                                                |    |

| 3.3 | "More Moore" vs. "Moore than Moore"                            | 4  |

| 4 T | THERMINATOR Roadmap: Topics of Relevance                       | 6  |

| 4.1 | Power Supply and Power Dissipation                             | 7  |

| 4.2 | 2 Cost of manufacturing                                        | 7  |

| 4.3 | High-Performance MPU/ASIC and Chip Size                        | 8  |

| 4.4 | Lithographic-Field and Wafer-Size                              | 8  |

| 4.5 | Performance of Packaged Chips: Number of Pads and Pins         | 9  |

| 4.6 | Performance and Package Chips: Frequency On-chip Wiring Levels | 9  |

| 4.7 | 7 System Drivers                                               | 10 |

| 4.8 | B Design                                                       | 15 |

| 4.9 | Interconnect, SoC integration                                  | 17 |

| 4.1 | 10 Modelling and Simulation                                    | 19 |

| 4.1 | 11 Assembly and Packaging: System Level Integration – SiP      | 24 |

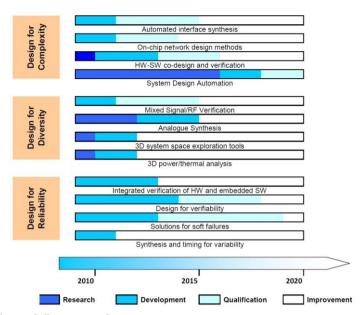

| 5 E | EDA Roadmap – Design Technologies                              | 29 |

| 5.1 | Introduction                                                   | 29 |

| 5.2 | 2 Competitive value                                            | 30 |

| 5.3 | Grand Challenges                                               | 31 |

| 5   | 5.3.1 Competitive Situation                                    | 31 |

| 5   | 5.3.2 Managing Diversity                                       | 32 |

| 5   | 5.3.3 Design for Reliability and Yield                         | 33 |

### THERMINATOR FP7 ICT – 2009.3.2 - 28603D8.4.5

| 5.4    | Timeframes                                     | 34 |

|--------|------------------------------------------------|----|

| 5.5    | Synergies with Other Domains                   | 35 |

| 6 Refe | erence glossary                                | 36 |

| 6.1    | Moore's Law                                    | 36 |

| 6.2    | Functional Diversification ("More than Moore") | 36 |

| 7 Con  | nclusion                                       | 37 |

### Remark

In addition to the THERMINATOR consortium, the content of this document is considerably complemented with projected data and statistics coming from reference organizations, mainly from **ITRS** (International Technology Roadmap for Semiconductors).

As the majority of the partners are members of ITRS to refer to such documents was the most effective way to not duplicate unnecessarily the effort and to be sure to not break any confidentiality, as the matter is quite sensitive.

## 1 THERMINATOR Roadmap: Objective

The objective of this deliverable is to provide a document of the THERMINATOR roadmap covering the aspects of modelling, design and EDA, looking at the future.

This document will serve as guideline for the Consortium to be prepared for the new users requirements.

Roadmap will provide an outlook of needs and trends for future technologies, methodologies and tools and has been done based on the THERMINATOR experience which is wholesome in the different design domains and at all level of abstraction, the reader can easily refer to the different THEMINATOR WPs, if this has not been done by the author it is to not heavy the reading.

<u>THERMINATOR</u> activity has sorted or proposed a solution for many of the current thermal issues but the investigations have also set the path for future developments and research activities.

## 2 THERMINATOR Roadmapping Committee

The road mapping effort spans the entire duration of the project, the THERMINATOR Board Committee has nominated the Road mapping Committee. This Committee includes representative of the partners organisation involved in the task as stated in milestone MS841. The Exploitation Manager drives the activity of the committee. In spite of the vacancy of the role of the Exploitation Manager the activities have been carried on by the partners, the late nomination of the manager has permitted a coordination of the works and the organic collection of the outcomes inside this report.

## 3 THERMINATOR Roadmap: Introduction

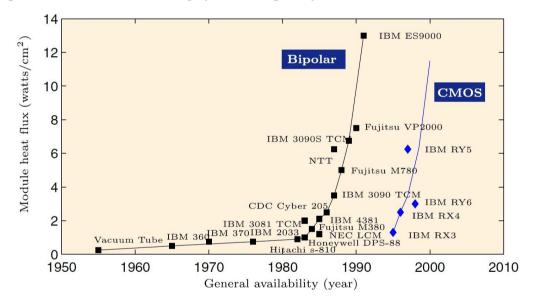

For more than four decades, the semiconductor industry has distinguished itself by the rapid pace of improvement in its products. The principal categories of improvement trends are shown in the following Tables with examples of each. Most of these trends have resulted principally from the industry's ability to exponentially decrease the minimum feature sizes used to fabricate integrated circuits. Of course, the most frequently cited trend is in integration level, which is usually expressed as Moore's Law (that is, the number of components per chip doubles roughly every 24 months).

The goal of the semiconductor industry is to be able to continue to scale the technology in overall performance. The performance of the components and the final chip can be measured in many different ways; higher speed, higher density, lower power, more functionality, etc.

Traditionally, dimensional scaling had been adequate to bring about these aforementioned performance merits but it is no longer so. Processing modules, tools, material properties, etc., are presenting difficult challenges to continue scaling.

Scaling may also lead to an effective increase of the stress factors. First, the current density is increasing and this increase impacts interconnect reliability. Second, voltages are often scaled down more slowly than dimensions, leading to increased electric fields that impact insulator reliability. Third, scaling has led to increasing power dissipation that results in higher chip temperatures, larger temperature cycles, and increased thermal gradients, all of which impact multiple failure mechanisms. The temperature effects are further aggravated by the reduced thermal conductivity that accompanies the reduction in the dielectric constant of the dielectrics between metal lines.

## 3.1 Decreasing cost-per-function

The most significant trend is the decreasing cost-per-function, which has led to major improvements in economic productivity and overall quality of life through proliferation of computers, communication, and other industrial and consumer electronics and the pervasiveness in everyday life.

| TREND             | IMPACT                               |

|-------------------|--------------------------------------|

| Integration Level | Components/chip, Moore's Law         |

| Cost              | Cost per function                    |

| Speed             | Microprocessor throughput            |

| Power             | Laptop and cell phone's battery life |

| Compactness       | Small and light-weight products      |

| Functionality     | Nonvolatile memory, imager           |

Improvement Trends for ICs Enabled by Feature Scaling

All of these improvement trends, sometimes called "scaling trends", have been enabled by large R&D investments. In the last three decades, the growing size of the required investments has motivated industry collaboration and spawned many R&D partnerships, consortia, and other cooperative ventures. To help guide these R&D programs, the Semiconductor Industry Association (SIA) initiated The National Technology Roadmap for

Semiconductors (NTRS), which had 1992, 1994, and 1997 editions. In 1998, the SIA was joined by corresponding industry associations in Europe, Japan, Korea, and Taiwan to participate in a 1998 update of the Roadmap and to begin work toward the first International Technology Roadmap for Semiconductors (ITRS), published in 1999.

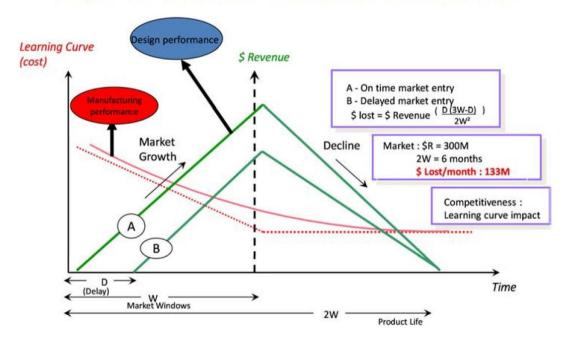

#### 3.2 Markets Drivers

Future semiconductor manufacturing and design technology capability is developed in response to economic drivers within the worldwide semiconductor industry. Today, introduction of new technology solutions is increasingly application-driven – i.e., *applications drive technology*. Computer microprocessors have been joined as drivers by mixed-signal systems, battery-powered mobile devices, wall-plugged consumer devices, and networking devices. In-house chip designs are replaced by system-on-chip (SoC) and system-in-package (SiP) designs that incorporate building blocks from multiple sources.

So far, microprocessors, memories, and logic devices strongly rely on silicon-based CMOS technologies. The downscaling of minimum dimensions enables the integration of an increasing number of transistors on a single chip, as described by Moore's Law. The essential functions on such a system-on-chip (SoC) are data storage and digital signal processing. However, many quantitative requirements, such as power consumption (both dynamic and leakage power), communications bandwidth and many functional requirements, such as analog and RF components, sensors and actuators and even embedded software functions, do not scale with Moore's Law.

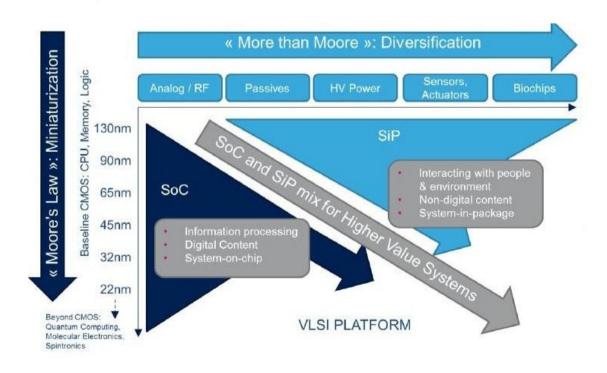

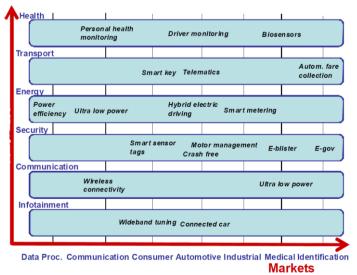

Fig. 1 Moore's Law and More than Moore.

This concept (see Fig. 1) has been established and pushed forward by ENIAC-JTI (European Technology Platform on Nanoelectronics) during 2005-2006 and refined, making a successfully fertilization, through ITRS and SIA.

### 3.3 "More Moore" vs. "Moore than Moore"

As a consequence, general consensus has been reached on the following peculiar definitions:

### Scaling ("More Moore," Fig. 1 vertical axis)

Scaling is a continued shrinking of physical feature sizes of the *digital* functionalities (logic and memory storage) in order to improve *density* (cost per function reduction) and *performance* (speed, power).

#### Functional Diversification ("More than Moore", Fig. 1 horizontal axis)

Functional diversification is the incorporation into devices of functionalities that do not necessarily scale according to "Moore's Law", but provide additional value in different ways. The "More-than-Moore" approach allows for the *non-digital* functionalities to migrate from the system board-level into the package (SiP) or onto the chip (SoC).

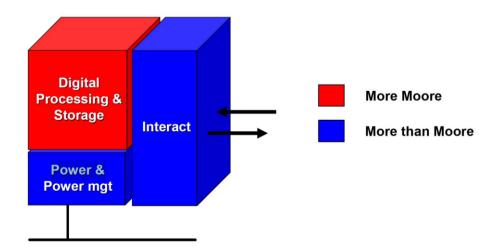

It should be emphasized that "More-than-Moore" technologies do not constitute an alternative or even competitor to the digital trend as described by Moore's Law. In fact, it is the heterogeneous integration of digital and non-digital functionalities into compact systems that will be the key driver for a wide variety of application fields, such as communication, automotive, environmental control, healthcare, security and entertainment. Whereas "More Moore" may be viewed as the brain of an intelligent compact system, "More-than-Moore" refers to its capabilities to interact with the outside world and the users.

Fig. 2"More-than-Moore" devices complement the digital processing and storage elements of an integrated system in allowing the interaction with the outside world and in powering the system.

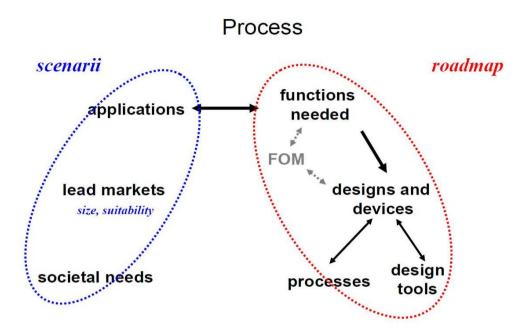

In order to identify relevant MtM devices and technologies to be roadmapped, one may start in looking for suitable markets and applications, derive then underlying functionalities and devices. A set of associated parameters and processes will be derived.

Fig. 3 From societal needs to markets.

Underlying the evolution of markets and applications, and therefore their economic potential, is their potential in addressing societal trends and challenges for the next decades. Societal trends can be grouped as health & wellness, transport & mobility, security & safety, energy & environment, communication and e-society (this latter term including infotainment). Many other names may be used but all cover more or less the same fields. These trends create significant opportunities in the markets of consumer electronics, automotive electronics, medical applications, communication, etc. Examples of applications linking societal trends and markets are given in the figure 4 below:

Fig. 4 Examples of applications liking societal trends and market.

## 4 THERMINATOR Roadmap: Topics of Relevance

As said in the initial remark, in addition to the THERMINATOR consortium the content of this document is valuably complemented with projected data and statistics coming from reference organizations, mainly from **ITRS**.

This Roadmap has been written in the spirit of defining what industry needs to develop in order to stay on Moore's Law and the other trends.

Within industry needs, the objectives of THERMINATOR project play a very important role. In fact, an unfortunate side effect of miniaturization and the continued scaling of CMOS technology is the ever increasing device power density with increasing difficulties in managing temperature. Moreover, neglecting *thermal* information during design may imply excessive over-design, due to the extremely conservative constraints that designers may pose in order to guarantee correct circuit operation under all possible running conditions. For these reasons the primary scientific and technical objective of the THERMINATOR project is to develop innovative design technologies for modeling, controlling, compensating and managing temperature in semiconductor circuits and systems to be manufactured with the most advanced processes and technologies (WP3-WP4). For what concern the power discrete devices (WP5) thermal modeling issues and estimation aspects are particularly important for high-voltage switching applications, where thermal effects have a huge impact.

Another important trend is the further increasing demand for *co-simulation* in various respects, including electro, *thermal* and mechanical effects, length scales from transistors through chips and packages to fabrication equipment, and covering not only performance but also **variability**, **reliability** and **reliability** under variability.

Co-simulation is also the MUST DO in the next future roadmap of SMART Power devices such as IPEM and the THERMINATOR experience is already influencing projects such as SMAC Error! Reference source not found.

In the following sections of this report the need of "thermal awareness" will be highlighted in most of the items.

| Key Lithography-related | Characteristics 1 Characterist | by Product |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| Year of Production                                 | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 |

|----------------------------------------------------|------|------|------|------|------|------|------|------|

| DRAM ½ Pitch (nm) (contacted)                      | 36   | 32   | 28   | 25   | 23   | 20   | 17.9 | 15.9 |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                 | 30   | 32   | 27   | 24   | 21   | 18.9 | 16.9 | 15   |

| MPU Printed Gate Length (nm)                       | 35   | 31   | 28   | 25   | 22   | 19.8 | 17.7 | 15.7 |

| MPU Physical Gate Length (nm)                      | 24   | 22   | 20   | 18   | 17   | 15.3 | 14   | 12.8 |

| ASIC/Low Operating Power Printed Gate Length (nm)  | 41   | 35   | 31   | 25   | 22   | 19.8 | 17.7 | 15.7 |

| ASIC/Low Operating Power Physical Gate Length (nm) | 26   | 24   | 21   | 19.4 | 17.6 | 16   | 14.5 | 13.1 |

| Flash ½ Pitch (nm) (un-contacted Poly)(f)          | 22   | 20   | 18   | 17   | 15   | 14.2 | 13   | 11.9 |

**Notes for Table**: The technology requirements are intended to indicate current best estimates of introduction timing for specific technology requirements

## 4.1 Power Supply and Power Dissipation

Total power dissipation will be limited more by system level cooling and test constraints than packaging.

| Year of Production                                                                         | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 |

|--------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| DRAM ½ Pitch (nm) (contacted)                                                              | 36   | 32   | 28   | 25   | 23   | 20   | 17.9 | 15.9 |

| Flash ½ Pitch (nm) (un-contacted Poly)(f)                                                  | 22   | 20   | 18   | 17   | 15   | 14.2 | 13   | 11.9 |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                     | 38   | 32   | 27   | 24   | 21   | 18.9 | 16.9 | 15   |

| MPU Physical Gate Length (nm)                                                              | 24   | 22   | 20   | 18   | 17   | 15.3 | 14   | 12.8 |

| Power Supply Voltage (V)                                                                   |      |      |      |      |      |      |      |      |

| Vdd (high-performance)                                                                     | 0.9  | 0.87 | 0.85 | 0.82 | 0.80 | 0.77 | 0.75 | 0.73 |

| V <sub>dd</sub> (Low Operating Power, high V <sub>dd</sub> transistors)                    | 0.93 | 0.90 | 0.87 | 0.84 | 0.81 | 0.78 | 0.75 | 0.72 |

| Allowable Maximum Power                                                                    |      |      |      |      |      |      |      |      |

| High-performance with heat sink (W)                                                        | 161  | 158  | 149  | 152  | 143  | 130  | 130  | 136  |

| Maximum Affordable Chip Size Target for High-<br>performance MPU Maximum Power Calculation | 260  | 260  | 260  | 260  | 260  | 260  | 260  | 260  |

| Maximum High-performance MPU Maximum Power Density for Maximum Power Calculation           | 0.52 | 0.51 | 0.48 | 0.49 | 0.46 | 0.42 | 0.42 | 0.44 |

| Cost-performance (W)                                                                       | 161  | 158  | 149  | 152  | 143  | 130  | 130  | 136  |

| Maximum Affordable Chip Size Target for Cost-performance<br>MPU Maximum Power Calculation  | 140  | 140  | 140  | 140  | 140  | 140  | 140  | 140  |

| Maximum Cost-performance MPU Maximum Power Density for Maximum Power Calculation           | 1.13 | 1.11 | 1.10 | 1.17 | 1.19 | 1.07 | 1.12 | 1.19 |

| Battery (W)—(low-cost/hand-held)                                                           | 3    | 3    | 3    | 3    | 3    | 3    | 3    | 3    |

## 4.2 Cost of manufacturing

| Year of Production                                                                       | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017  | 2018  |

|------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------|-------|

| DRAM ½ Pitch (nm) (contacted)                                                            | 36   | 32   | 28   | 25   | 23   | 20   | 17.9  | 15.9  |

| Flash ½ Pitch (nm) (un-contacted Poly)(f)                                                | 22   | 20   | 18   | 17   | 15   | 14.2 | 13.0  | 11.9  |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                   | 38   | 32   | 27   | 24   | 21   | 18.9 | 16.9  | 15.0  |

| MPU Physical Gate Length (nm)                                                            | 22   | 20   | 18   | 17   | 15.3 | 14.0 | 12.8  | 11.7  |

| Affordable Cost per Function ++                                                          |      |      |      |      |      |      |       |       |

| DRAM cost/bit at (packaged microcents) at samples/introduction                           | 0.66 | 0.46 | 0.33 | 0.23 | 0.16 | 0.12 | 0.082 | 0.058 |

| DRAM cost/bit at (packaged microcents) at production §                                   | 0.24 | 0.17 | 0.12 | 0.08 | 0.06 | 0.04 | 0.030 | 0.021 |

| Cost-performance MPU (microcents/transistor) (including on-chip SRAM) at introduction §§ | 5.50 | 3.89 | 2.75 | 1.94 | 1.38 | 0.97 | 0.688 | 0.486 |

| Cost-performance MPU (microcents/transistor) (including on-chip SRAM) at production §§   | 3.33 | 2.35 | 1.66 | 1.18 | 0.83 | 0.59 | 0.416 | 0.294 |

| High-performance MPU(microcents/transistor) (including on-chip SRAM) at production §§    | 3.04 | 2.15 | 1.52 | 1.08 | 0.76 | 0.54 | 0.380 | 0.269 |

## 4.3 High-Performance MPU/ASIC and Chip Size

|                                                                                                            |        |        |        | I      | 1      | 1       | I      |        |

|------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|---------|--------|--------|

| Year of Production                                                                                         | 2011   | 2012   | 2013   | 2014   | 2015   | 2016    | 2017   | 2018   |

| DRAM ½ Pitch (nm) (contacted)                                                                              | 36     | 32     | 28     | 25     | 23     | 20.0    | 17.9   | 15.9   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                                     | 38     | 32     | 27     | 24     | 21     | 18.9    | 16.9   | 15.0   |

| MPU Physical Gate Length (nm)                                                                              | 24     | 22     | 20     | 18     | 17     | 15.3    | 14.0   | 12.8   |

| Logic(Low-volume<br>Microprocessor)High-performance‡                                                       |        |        |        |        |        |         |        |        |

| Generation at Introduction                                                                                 | p13h   | p13h   | p16h   | p16h   | p16h   | p19h    | p19h   | p19h   |

| Functions per chip at introduction (million transistors)                                                   | 8,848  | 8,848  | 17,696 | 17,696 | 17,696 | 35,391  | 35,391 | 8,848  |

| Chip size at introduction (mm <sup>2</sup> )                                                               | 520    | 368    | 520    | 413    | 328    | 520     | 413    | 328    |

| Generation at production **                                                                                | p11h   | p11h   | p13h   | p13h   | p13h   | p16h    | p16h   | p16h   |

| Functions per chip at production (million transistors)                                                     | 4,424  | 4,424  | 8,848  | 8,848  | 8,848  | 17,696  | 17,696 | 17,696 |

| Chip size at production (mm <sup>2</sup> ) §§                                                              | 260    | 184    | 260    | 206    | 164    | 260     | 206    | 164    |

| HighperformanceMPUMtransistors/cm at introduction and production (including on-chip SRAM) ‡                | 1,701  | 2,406  | 3,403  | 4,287  | 5,402  | 6,806'' | 8,575  | 10,804 |

| ASIC                                                                                                       |        |        |        |        |        |         |        |        |

| ASIC usable Mtransistors/cm <sup>2</sup> (auto layout)                                                     | 1,701  | 2,406  | 3,403  | 4,287  | 5,402  | 6,806   | 8,575  | 10,804 |

| ASIC max chip size at production (mm <sup>2</sup> ) (maximum lithographic field size)                      | 858    | 858    | 858    | 858    | 858    | 858     | 858    | 858    |

| ASIC maximum functions per chip at production (Mtransistors/chip) (fit in maximum lithographic field size) | 14,599 | 20,646 | 29,198 | 36,787 | 46,348 | 58,395  | 73,573 | 92,697 |

# 4.4 Lithographic-Field and Wafer-Size

| Year of Production                                                                      | 2011 | 2012 | 2013 | 2014 | 2015 | 2016          | 2017          | 2018          |

|-----------------------------------------------------------------------------------------|------|------|------|------|------|---------------|---------------|---------------|

| Lithography Field Size                                                                  |      |      |      |      |      |               |               |               |

| Maximum Lithography Field Size—area (mm²)                                               | 858  | 858  | 858  | 858  | 858  | 858           | 858           | 858           |

| Maximum Lithography Field Size—length (mm)                                              | 33   | 33   | 33   | 33   | 33   | 33            | 33            | 33            |

| Maximum Lithography Field Size—width (mm)                                               | 26   | 26   | 26   | 26   | 26   | 26            | 26            | 26            |

| Maximum Substrate Diameter (mm)—High-volume<br>Production (>20K wafer starts per month) |      |      |      |      |      |               |               |               |

| Bulk or epitaxial or SOI wafer                                                          | 300  | 300  | 300  | 300  | 300  | 300 or<br>450 | 300 or<br>450 | 300 or<br>450 |

|                                                                                         |      |      |      |      |      |               |               |               |

## 4.5 Performance of Packaged Chips: Number of Pads and Pins

| Year of Production                                                   | 2011     | 2012     | 2013     | 2014     | 2015     | 2016     | 2017     | 2018     |

|----------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| DRAM ½ Pitch (nm) (contacted)                                        | 22       | 20       | 18       | 17       | 15       | 14.2     | 13.0     | 11.9     |

| Flash ½ Pitch (nm) (un-<br>contacted Poly)(f)                        | 36       | 32       | 28       | 25       | 23       | 20.0     | 17.9     | 15.9     |

| MPU/ASIC Metal 1 (M1) ½<br>Pitch (nm) (f)                            | 38       | 32       | 27       | 24       | 21       | 18.9     | 16.9     | 15.0     |

| MPU Physical Gate Length (nm)                                        | 35       | 31       | 28       | 25       | 22       | 19.8     | 17.7     | 15.7     |

| Number of Chip I/Os<br>(Number of Total Chip<br>Pads)—Maximum        |          |          |          |          |          |          |          |          |

| Total pads—MPU unchanged                                             | "3,072"  | "3,072"  | "3,072"  | "3,072"  | "3,072"  | "3,072"  | "3,072"  | "3,072"  |

| Signal I/O—MPU (% of total pads)                                     | 33.3%    | 33.3%    | 33.3%    | 33.3%    | 33.3%    | 33.3%    | 33.3%    | 33.3%    |

| Power and ground pads—<br>MPU (% of total pads)                      | 66.7%    | 66.7%    | 66.7%    | 66.7%    | 66.7%    | 66.7%    | 66.7%    | 66.7%    |

| IS: Total pads—ASIC High<br>Performance unchanged                    | "4,800"  | "5,000"  | "5,400"  | "5,400"  | "5,600"  | "6,000"  | "6,000"  | "6,200"  |

| Signal I/O pads—ASIC high-performance (% of total pads)              | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    |

| Power and ground pads—<br>ASIC high-performance (%<br>of total pads) | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    |

| Number of Total Package<br>Pins—Maximum [1]                          |          |          |          |          |          |          |          |          |

| Microprocessor/controller, cost-performance                          | 720-3061 | 720–3367 | 800-3704 | 800-4075 | 880-4482 | 880-4930 | 960-5423 | 960–5966 |

| Microprocessor/controller,<br>high-performance                       | 5094     | 5348     | 5616     | 5896     | 6191     | 6501     | 6826     | 7167     |

| ASIC (high-performance)                                              | 5094     | 5348     | 5616     | 5896     | 6191     | 6501     | 6826     | 7167     |

## 4.6 Performance and Package Chips: Frequency On-chip Wiring Levels

| Year of Production                        | 2011  | 2012  | 2013  | 2014  | 2015  | 2016  | 2017  | 2018  |

|-------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| DRAM ½ Pitch (nm) (contacted)             | 36    | 32    | 28    | 25    | 23    | 20.0  | 17.9  | 15.9  |

| Flash ½ Pitch (nm) (un-contacted Poly)(f) | 22    | 20    | 18    | 17    | 15    | 14.2  | 13.0  | 11.9  |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)    | 38    | 32    | 27    | 24    | 21    | 18.9  | 16.9  | 15.0  |

| MPU Physical Gate Length (nm)             | 24    | 22    | 20    | 18    | 17    | 15.3  | 14.0  | 12.8  |

| Chip Frequency (GHz)                      |       |       |       |       |       |       |       |       |

| On-chip local clock [1]                   | 3.744 | 3.894 | 4.050 | 4.211 | 4.380 | 4.555 | 4.737 | 4.927 |

| Maximum number wiring levels [3] [**]     | 12    | 12    | 13    | 13    | 13    | 13    | 14    | 14    |

|                                           |       |       |       |       |       |       |       |       |

## **4.7 System Drivers**

As said above, the assumption that technological advances are deployed in all semiconductor products, independent of the specifics of key product classes, is no longer valid. Today, introduction of new technology solutions is increasingly application-driven – i.e., *applications drive technology*. Computer microprocessors have been joined as drivers by mixed-signal systems, battery-powered mobile devices, wall-plugged consumer devices, and networking devices. One more driver must be considered: the consumer stationary driver that represents a high-performance version of the increasingly important consumer electronics and digital TV market.

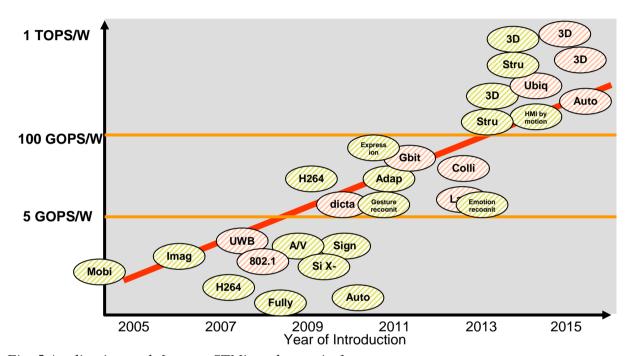

Fig. 5 Application rush [source STMicroelectronics].

## **4.7.1 Key Drivers**

### • Power consumption: a first-class constraint

> Both for portable and non-portable applications

#### • Highly parallel architectures

> Increasing number of "small" processing unit

#### • System-On-Chip design techniques

➤ The System Drivers continues to evolve to include market-driven drivers that reflect the demands of a 21st-century roadmap. These driver segments include *Networking*, *Consumer stationary*, *Consumer mobile*, *Office / MPU*.

The long-term goal is to match system-level and chip-level requirements on a driver basis.

Major Product Market Segments and Impact on System Drivers.

| Market Drivers                                                                                                                                                                                             | SoC                                                                                                                                                                                                     | Analog/MS                                                                                                                                                                                                          | MPU                                                                                                                                                                                         |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                                                                                                            | I. Portable                                                                                                                                                                                             | e/consumer                                                                                                                                                                                                         |                                                                                                                                                                                             |  |  |  |  |  |

| 1. Size/weight ratio: peak in 2004 2. Battery life: peak in 2004 3. Function: 2×/2 years 4. Time-to-market: ASAP                                                                                           | Low power paramount  Need SoC integration (DSP, MPU, I/O cores, etc.)                                                                                                                                   | Migrating on-chip for voice processing, A/D sampling, and even for some RF transceiver function                                                                                                                    | Specialized cores to optimize processing per microwatt                                                                                                                                      |  |  |  |  |  |

| II. Medical                                                                                                                                                                                                |                                                                                                                                                                                                         |                                                                                                                                                                                                                    |                                                                                                                                                                                             |  |  |  |  |  |

| Cost: slight downward pressure (~1/2 every 5 years)     Time-to-market: >12 months     Function: new on-chip functions     Form factor often not important     Durability/safety     Conservation/ ecology | High-end products only. Reprogrammability possible. Mainly ASSP, especially for patient data storage and telemedicine; more SoC for highend digital with cores for imaging, real-time diagnostics, etc. | Absolutely necessary for physical measurement and response but may not be integrated on chip                                                                                                                       | Often used for programmability especially when real-time performance is not important  Recent advances in multicore processors have made programmability and real-time performance possible |  |  |  |  |  |

|                                                                                                                                                                                                            | III. Networking ar                                                                                                                                                                                      | nd communications                                                                                                                                                                                                  |                                                                                                                                                                                             |  |  |  |  |  |

| 1. Bandwidth: 4×/3–4 years 2. Reliability 3. Time-to-market: ASAP 4. Power: W/m <sup>3</sup> of system                                                                                                     | Large gate counts High reliability More reprogrammability to accommodate custom functions                                                                                                               | Migrating on-chip for<br>MUX/DEMUX circuitry<br>MEMS for optical switching.                                                                                                                                        | MPU cores, FPGA cores and some specialized functions                                                                                                                                        |  |  |  |  |  |

|                                                                                                                                                                                                            | IV. D                                                                                                                                                                                                   | efense                                                                                                                                                                                                             |                                                                                                                                                                                             |  |  |  |  |  |

| Cost: not prime concern     Time-to-market: >12 months     Function: mostly on SW to ride technology curve     Form factor may be important     High durability/safety                                     | Most case leverage existing processors but some requirements may drive towards single-chip designs with programmability                                                                                 | Absolutely necessary for physical measurement and response but may not be integrated on chip                                                                                                                       | Often used for programmability especially when real-time performance is not important  Recent advances in multicore processors have made programmability and real-time performance possible |  |  |  |  |  |

|                                                                                                                                                                                                            | V. (                                                                                                                                                                                                    | Office                                                                                                                                                                                                             | F F                                                                                                                                                                                         |  |  |  |  |  |

| 1. Speed: 2×/2 years 2. Memory density: 2×/2 years 3. Power: flat to decreasing, driven by cost and W/m <sup>3</sup> 4. Form factor: shrinking size 5. Reliability                                         | Large gate counts; high speed  Drives demand for digital functionality  Primarily SoC integration of custom off-the-shelf MPU and I/O cores                                                             | Minimal on-chip analog; simple A/D and D/A  Video i/f for automated camera monitoring, video conferencing  Integrated high-speed A/D, D/A for monitoring, instrumentation,                                         | MPU cores and some specialized functions  Increased industry partnerships on common designs to reduce development costs (requires data sharing and reuse across multiple design systems)    |  |  |  |  |  |

|                                                                                                                                                                                                            |                                                                                                                                                                                                         | and range-speed-position resolution                                                                                                                                                                                |                                                                                                                                                                                             |  |  |  |  |  |

| VI. Automotive                                                                                                                                                                                             |                                                                                                                                                                                                         |                                                                                                                                                                                                                    |                                                                                                                                                                                             |  |  |  |  |  |

| Functionality     Ruggedness (external environment, noise)     Reliability and safety     Cost                                                                                                             | Mainly ASSP, but increasing SoC<br>for high end using standard HW<br>platforms with RTOS kernel,<br>embedded software                                                                                   | Cost-driven on-chip A/D and D/A for sensor and actuators  Signal processing shifting to DSP for voice, visual  Physical measurement ("communicating sensors" for proximity, motion, positioning); MEMS for sensors |                                                                                                                                                                                             |  |  |  |  |  |

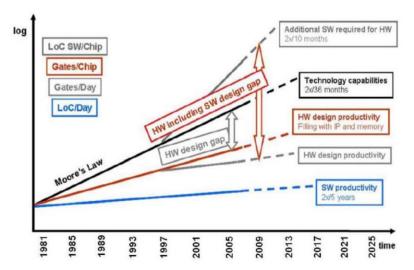

### SoC-CP Design Productivity Trends

The SoC Consumer Portable (SoC-CP) Driver increasingly represents SoC designs; it spans portable and wireless applications such as smart media-enabled telephones, tablets and digital cameras, as well as other processing purposes such as high-performance computing and enterprise applications. The SoC-CP driver is based on a model created by the Japan Semiconductor Technology Roadmap Design Group.

- Its typical application area is electronic equipment categorized as "Portable/Mobile Consumer Platforms", as this application area will make rapid progress in the foreseeable future across semiconductor technology generations.

- Typical requirements for this type of SoC ("Portable/Mobile Consumer Platforms") dictate a rapid increase in processing capability, despite an upper bound constraint on power to maintain battery lifetime. Processing power increases by 1000× in the next ten years, even as dynamic power consumption does not change significantly.

- Lifecycles of "Portable/Mobile Consumer Platform" products are and will continue to be short. Hence, design effort cannot be increased, and must remain at current levels for the foreseeable future.

| Year of Production                                                                             | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 |

|------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Design block reuse [1] % of all logic                                                          | 54%  | 58%  | 62%  | 66%  | 70%  | 74%  | 78%  | 82%  |

| Requirement: Productivity for new designs (normalized to 2007)                                 | 1.00 | 1.22 | 1.60 | 2.02 | 2.50 | 3.08 | 3.72 | 4.48 |

| Requirement: Productivity for reused designs (normalized productivity for new designs at 2007) | 1.00 | 1.22 | 1.60 | 2.02 | 2.50 | 3.08 | 3.72 | 4.48 |

#### SoC-CP Driver Trends

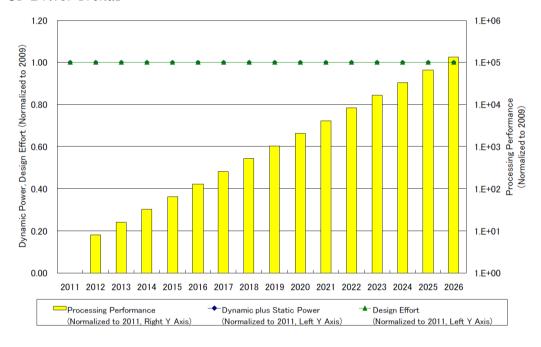

Fig. 6 Several Trends for the SOC Consumer Portable Driver.

#### SoC CONSUMER STATIONARY (SoC-CS) DRIVER

The SoC Consumer Stationary (SoC-CS) Driver represents SoC designs over a wide variety of applications in digital consumer electronic equipment, such as high-end game machines; these are assumed to be typically used in a tethered (non-mobile) environment. Key aspects of the model are as follows.

• Processing performance is the most important differentiator.

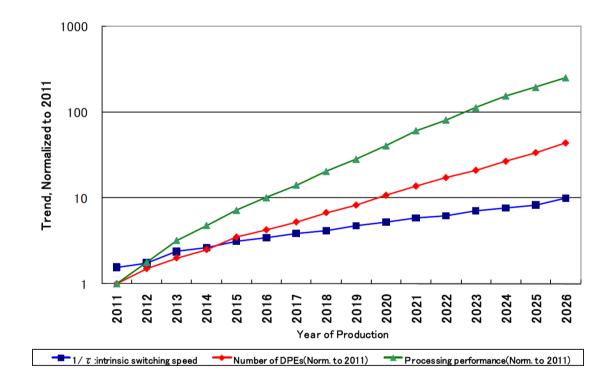

- Functions will be implemented and realized mainly by software. Thus, high processing power is required, and this SoC will have many Data Processing Engines (DPEs).

- In comparison with the SoC Consumer Portable driver, this driver has worse performance to power ratio, but superior functional flexibility to support adding or modifying functions.

- Because it is easy to add or modify functions, the lifecycle of SoC Consumer Stationary designs is relatively long, and as a result the application area is wide.

#### SoC CONSUMER STATIONARY PERFORMANCE TRENDS

The SoC Consumer Stationary driver's processing performance can be assumed proportional to the product of device performance and the number of DPEs on the SoC. Fig. 6 shows SoC Consumer Stationary processing performance trends. Required processing performance grows rapidly, by approximately 250x over the next fifteen years. Key potential solutions to achieve the required performance include various design technologies (particularly in the logical, circuit and physical design stages) to maximize circuit performance. Automated design methodologies such as high-level synthesis are of course important as well.

Fig. 7 SoC Consumer Stationary Performance Trends.

#### SoC CONSUMER STATIONARY POWER CONSUMPTION TRENDS

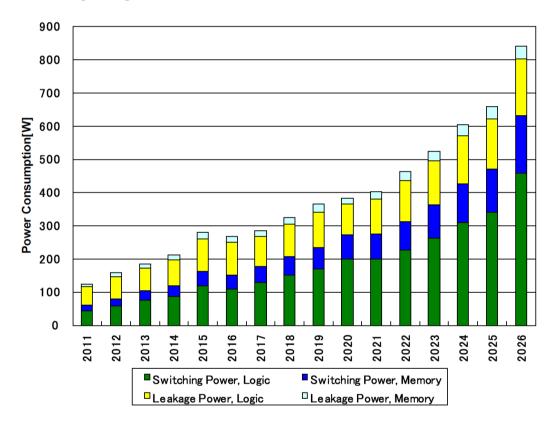

An explosion in power consumption will be a critical consideration for the design of future SoC Consumer Stationary chips. Fig. 7 shows the trend for total chip power, decomposed into switching and leakage power, across logic and memory. The analysis is based on transistor performance, interconnect performance parameters and the design complexity trends. We note the following.

- Unlike the SoC Consumer Portable Driver, the SoC Consumer Stationary Driver is generally free from battery life issues; however, the rapid increase in power consumption will result in critical chip packaging and cooling issues.

- Leakage power will be much greater than the calculated value shown in Fig. 7, due to variability and temperature effects.

- Power consumption per DPE will decrease according to trends for supply voltage and insulator dielectric constant. However, this will be outweighed by the increase in number of DPEs per chip.

Fig. 8 SoC Consumer Stationary Power Consumption Trends.

Clearly, the trend in Fig. 7 highlights a pressing need to develop new solutions, beyond those already embedded in the technology roadmaps, so that actual power consumption remains within acceptable limits.

## 4.8 Design

The main message remains: cost (of design) is the greatest threat to continuation of the semiconductor roadmap. Cost determines whether differentiating value is best achieved in software or in hardware, on a programmable commodity platform, or on a new IC. Manufacturing non-recurring engineering (NRE) costs are on the order of millions of dollars (mask set + probe card); design NRE costs routinely reach tens of millions of dollars, with design shortfalls being responsible for silicon re-spins that multiply manufacturing NRE. Rapid technology change shortens product life cycles and makes time-to-market a critical issue for semiconductor customers. Manufacturing cycle times are measured in weeks, with low uncertainty. Design and verification cycle times are measured in months or years and this implies a high uncertainty.

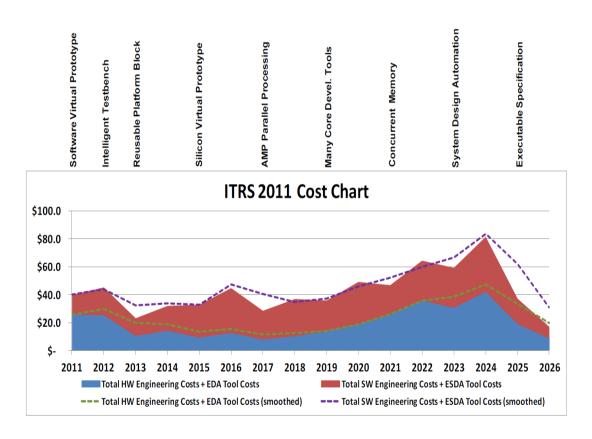

ITRS have noted a **design productivity gap**: the numbers of available transistors growing faster than the ability to meaningfully design them. This gap impacts IC product value, placing at risk foundry amortization, return on investment (ROI) for supplier industries, and indeed the entire semiconductor investment cycle. Yet, investment in process technology continues to dominate investment in design technology. The DT (Design Technology) roadmap enables control of design costs.

Fig. 9 ITRS 2011 Cost chart.

### Table Overall Design Technology Challenges.

| Challenges ≥ 22 nm  | Summary of Issues                                                                                                                                                            |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design productivity | System-level: high level of abstraction (HW/SW) functionality spec, platform based design, multi-processor programmability, system integration, AMS co-design and automation |

|                     | Verification: executable specification, ESL formal verification, intelligent test bench, coverage-based verification                                                         |

|                     | Logic/circuit/physical: analog circuit synthesis, multi-objective optimization"                                                                                              |

|                     | Logic/circuit/physical: SiP and 3D (TSV-based) planning and implementation flows                                                                                             |

|                     | Heterogeneous component integration (optical, mechanical, chemical, bio, etc.)                                                                                               |

| Power consumption   | Logic/circuit/physical: dynamic and static, system- and circuit-level power optimization                                                                                     |

| Manufacturability   | Performance/power variability, device parameter variability, lithography limitations impact on design, mask cost, quality of (process) models                                |

|                     | ATE interface test (multi-Gb/s), mixed-signal test, delay BIST, test-volume-reducing DFT                                                                                     |

| Reliability         | Logic/circuit/physical: MTTF-aware design, BISR, soft-error correction                                                                                                       |

| Interference        | Logic/circuit/physical: signal integrity analysis, EMI analysis, thermal analysis                                                                                            |

| Challenges <22 nm   | Summary of Issues                                                                                                                                                            |

| Design productivity | Verification: complete formal verification of designs, complete verification code reuse, complete deployment of functional coverage                                          |

|                     | Tools specific for SOI and non-static logic, and emerging devices                                                                                                            |

|                     | Cost-driven design flow                                                                                                                                                      |

| Power consumption   | Logic/circuit/physical: SOI power management                                                                                                                                 |

|                     | Logic/circuit/physical : Reliability and resilience- and temperature-constrained 3D physical implementation flows                                                            |

| Manufacturability   | Uncontrollable threshold voltage variability                                                                                                                                 |

|                     | Advanced analog/mixed signal DFT (digital, structural, radio), "statistical" and yield-improvement DFT                                                                       |

|                     | Thermal BIST, system-level BIST                                                                                                                                              |

| Reliability         | Autonomic computing, robust design, SW reliability and resilience                                                                                                            |

| Interference        | Interactions between heterogeneous components (optical, mechanical, chemical, bio, etc.)                                                                                     |

ATE—automatic test equipment BISR—built-in self repair BIST—built-in self test DFT—design for testability EMI—electromagnetic interference ESL—Electronic System-level Design HW/SW—hardware/software MTTF—mean time to failure SOI—silicon on insulator

## 4.9 Interconnect, SoC integration

The function of an interconnecting or wiring system is to distribute clock and other signals and to provide power/ground, to and among, the various circuit/system functions on a chip. The fundamental development requirement for interconnect is to meet the high-bandwidth low-power signalling needs without introducing performance bottlenecks as scaling continues.

One of the grand challenges for interconnect is the result of the rapid introductions of new materials/processes that are necessary to meet conductivity requirements and reduce the dielectric permittivity. These create integration, cost, and reliability challenges.

Another of the grand challenges is the variability associated with line edge roughness, trench and via depth and profile, etch bias, thinning due to cleaning and CMP as well as size effects. Traditional interconnect scaling will no longer satisfy performance requirements. Defining and finding solutions beyond copper and low  $\kappa$  will require material innovation, combined with accelerated design, packaging and unconventional interconnect.

Highlighting and differentiating the five key challenges in the near term (> 16 nm) and long term (< 16 nm) it's possible to say: in the near term, the most difficult challenge for interconnects is the introduction of new materials that meet the wire conductivity requirements and reduce dielectric permittivity; in the long term, the impact of size effects on interconnect structures must be mitigated.

Future effective κ requirements preclude the use of a trench etch stop for dual damascene structures. Dimensional control is a key challenge for present and future interconnect technology generations and the resulting difficult challenge for etch is to form precise trench and via structures in low-κ dielectric material to reduce variability in RC. The dominant architecture, damascene, requires tight control of pattern, etch and planarization. To extract maximum performance, interconnect structures cannot tolerate variability in profiles without producing undesirable RC degradation. These dimensional control requirements place new demands on high throughput imaging metrology for measurement of high aspect ratio structures. New metrology techniques are also needed for in-line monitoring of adhesion and defects. Larger wafers and the need to limit test wafers will drive the adoption of more in situ process control techniques. Dimensional control, a challenge now, will become even more critical as new materials, such as porous low-κ dielectrics and ALD metals, play a role at the tighter pitches and higher aspect ratios (A/R) of intermediate and global levels.

Table Interconnect Difficult Challenges

| Difficult Challenges ≥ 16 nm                                                                                    | Summary of Issues                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Material Introduction of new materials to meet conductivity requirements and reduce the dielectric permittivity | The rapid introductions of new materials/processes that are necessary to meet conductivity requirements and reduce the dielectric permittivity create integration and material characterization challenges. |

| Manufacturable Integration Engineering manufacturable interconnect structures, processes and new materials*     | Integration complexity, CMP damage, resist poisoning, dielectric constant degradation.  Lack of interconnect/packaging architecture design optimization tool                                                |

| Reliability Achieving necessary reliability                                                                     | New materials, structures, and processes create new chip reliability (electrical, thermal, and mechanical) exposure. Detecting, testing, modeling, and control of failure mechanisms will be key.           |

| Metrology Three-dimensional control of interconnect features (with its associated metrology) is required to achieve necessary circuit performance and reliability. | Line edge roughness, trench depth and profile, via shape, etch bias, thinning due to cleaning, CMP effects. The multiplicity of levels combined with new materials, reduced feature size, and pattern dependent processes create this challenge.                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cost & Yield for Manufacturability Manufacturability and defect management that meet overall cost/performance requirements                                         | As feature sizes shrink, interconnect processes must be compatible with device roadmaps and meet manufacturing targets at the specified wafer size. Plasma damage, contamination, thermal budgets, cleaning of high A/R features, defect tolerant processes, elimination/reduction of control wafers are key concerns. Where appropriate, global wiring and packaging concerns will be addressed in an integrated fashion. |

| Difficult Challenges < 16 nm                                                                                                                                       | Summary of Issues                                                                                                                                                                                                                                                                                                                                                                                                          |

| Material Mitigate impact of size effects in interconnect structures                                                                                                | Line and via sidewall roughness, intersection of porous low-κ voids with sidewall, barrier roughness, and copper surface roughness will all adversely affect electron scattering in copper lines and cause increases in resistivity                                                                                                                                                                                        |

| Metrology Three-dimensional control of interconnect features (with its associated metrology) is required                                                           | Line edge roughness, trench depth and profile, via shape, etch bias, thinning due to cleaning, CMP effects. The multiplicity of levels, combined with new materials, reduced feature size and pattern dependent processes, use of alternative memories, optical and RF interconnect, continues to challenge.                                                                                                               |

| Process Patterning, cleaning, and filling at nano dimensions                                                                                                       | As features shrink, etching, cleaning, and filling high aspect ratio structures will be challenging, especially for low- $\kappa$ dual damascene metal structures and DRAM at nanodimensions.                                                                                                                                                                                                                              |

| Complexity in Integration Integration of new processes and structures, including interconnects for emerging devices                                                | Combinations of materials and processes used to fabricate new structures create integration complexity. The increased number of levels exacerbates thermomechanical effects. Novel/active devices may be incorporated into the interconnection.                                                                                                                                                                            |

| Practical Approach for 3D Identify solutions which address 3D structures and other packaging issues*                                                               | 3 dimensional chip stacking circumvents the deficiencies of traditional interconnect scaling by providing enhanced functional diversity. Engineering manufacturable solutions that meet cost targets for this technology is a key interconnect challenge.                                                                                                                                                                  |

## 4.10 Modelling and Simulation

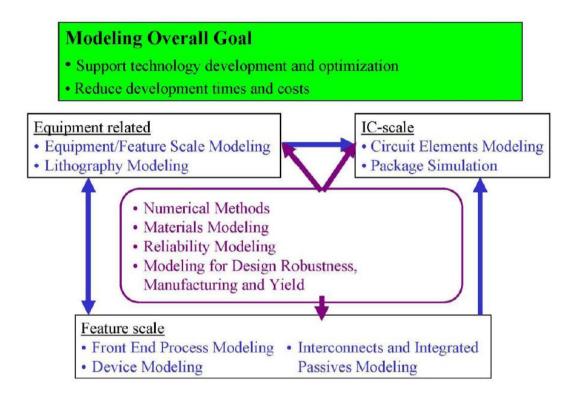

This is intended to further promote the usefulness of Modelling and Simulation to improve the physical understanding in semiconductor technology and to reduce development times and costs.

Technology Modelling and Simulation covers the region of the semiconductor modelling world called extended TCAD, and it is one of the few enabling methodologies that can reduce development cycle times and costs. Extended TCAD covers the following topical areas: 1) Equipment/feature scale modelling—hierarchy of models that allows the simulation of the local influence of the equipment (except lithography) on each point of the wafer, especially in deposition, etching and CMP processes, starting from the equipment geometry and settings; 2) Lithography modelling—modelling of the imaging of the mask by the lithography equipment, the photoresist characteristics and processing; 3) Front end process modelling—the simulation of the physical effects of manufacturing steps used to build transistors up to metallization, but excluding lithography; 4) Device modelling—hierarchy of physically based models for the operational description of active devices; 5) Interconnect and integrated passives modelling the operational response (mechanical, electro-magnetic, and thermal properties) of back-end architectures; 6) Circuit element modelling—compact models for active, passive, and parasitic circuit components, and new circuit elements based on new device structures; 7) Package simulation—electrical, mechanical, and thermal modelling of chip packages; 8) Materials modelling—simulation tools that predict the physical properties of materials and, in some cases, the subsequent electrical properties; 9) Reliability modelling—the modelling of reliability and related effects on process, device and circuit level; 10) Modelling for design robustness, manufacturing and vield—the development of additional models and software to enable the use of TCAD to study the impact of inevitable process variations and dopant fluctuations on IC performance and in turn design parameters, manufacturability and the percentage of ICs that are within specifications; 11) Numerical methods—all algorithms needed to implement the models developed in any of the other sections, including grid generators, surface-advancement techniques, (parallel) solvers for systems of (partial) differential equations, and optimization routines. As shown in Fig. 9, these areas can be grouped into equipment, feature and IC-scale. Items 8 to 11 are unique because they in fact cross-cut almost all other topics in Modelling and Simulation. Material and reliability issues are becoming more and more important in all processes as well as for active devices and interconnect. Design robustness, manufacturing and yield are affected by all areas simulated. Numerical algorithms are shared by most of the areas in simulation.

Fig. 10 Extended TCAD areas.

#### Concerning the short-term challenges:

Lithography simulation including EUV—Various tricks have been introduced to extend the applicability of optical lithography to even smaller dimensions, with substantial support from lithography simulation. The further technological development also requires large additional improvements in the area of lithography simulation, among others because the number of available resolution enhancement techniques increases.

Front-end process modelling for nanometer structures—This is the key challenge for the prediction of result from device fabrication. It overlaps to some extent with the challenge "Ultimate nanoscale CMOS simulation capability," which also includes materials and device simulation. Most important and challenging in the area of front-end process modelling is the modelling of ultra-shallow junction formation, which starts from very low energy implant and especially focuses on the thermal annealing and diffusion of dopants, and especially on activation and deactivation

Integrated modelling of equipment, materials, feature scale processes, and influences on devices—Variations of the results of a process step caused by the fabrication process and equipment used are key issues for manufacturability and yield of a technology. This refers especially to variations between neighbouring devices or non-homogeneities across the wafer or between different wafers, and to drifts of process results between maintenance of equipment, for example, due to coating of chamber walls.

Nanoscale device simulation capability: Methods, models and algorithms—A fundamental question of the microelectronics industry continues to be what are the ultimate limits of CMOS technology and devices. The key requirement to deal with this challenge is predictive simulation of materials, processes, and device behaviour including reliability.

Electrical-thermal-mechanical- modelling for interconnections and packaging—Performance and reliability of integrated circuits is increasingly affected by interconnects and packaging. Electrical, thermal, and mechanical properties highly interact with each other and must therefore be simulated together. Reliability issues requiring modelling include electromigration, stress voiding, integrity and adhesion of thin films, surface roughness, package fracture, and corrosion. Through Silicon Vias and thin stacked dies request new or largely extended simulation tools. Size effects (microstructure, surfaces) and variability of thinned wafers are important issues to be simulated. The capability to withstand the heat produced in the IC and to transport it off the chip is getting a top-level concern with further increasing densities.

Table Modeling and Simulation Difficult Challenges