Confidential

|                                                  | WP no.             | Deliverable no.         | Lead participant |  |

|--------------------------------------------------|--------------------|-------------------------|------------------|--|

| Cherminator                                      | WP7                | D7.1.1                  | NXP-NL           |  |

| Validation and standardization of thermal models |                    |                         |                  |  |

| Prepared by                                      | M. Willemsen       |                         |                  |  |

| Issued by                                        | THERMINATO         | <b>R</b> Project Office |                  |  |

| Document Number                                  | THERMINATO         | R/D7.1.1/v1             |                  |  |

| Dissemination Leve                               | <b>CONFIDENTIA</b> | L                       |                  |  |

| Date                                             | 01/02/2013         |                         |                  |  |

© Copyright 2010-2013 STMicroelectronics, Intel Mobile Communication, NXP Semiconductors, GRADIENT DESIGN AUTOMATION, MUNEDA, SYNOPSYS, BUDAPESTI MUSZAKI ES GAZDASAGTUDOMANYI EGYETEM, CSEM, FRAUNHOFER, IMEC, CEA-LETI, OFFIS, Politecnico di Torino, ALMA MATER STUDIORUM -Universita' Di Bologna, ST-Polito.

## Document

| mt i           |                                                                                                                                                                                                                                 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title          | Validation and standardization of thermal models                                                                                                                                                                                |

| Туре           | Deliverable CO                                                                                                                                                                                                                  |

| Ref            | D7.1.1                                                                                                                                                                                                                          |

| Target version | V1_1                                                                                                                                                                                                                            |

| Current issue  | V0_1                                                                                                                                                                                                                            |

| Status         | released                                                                                                                                                                                                                        |

| File           |                                                                                                                                                                                                                                 |

| Author(s)      | W. Moering (NXP-D), A. Burenkov (FHG), J. Lorenz (FHG), M. Willemsen (NXP-NL), S. Sque (NXP-NL), G. Greco (ST), H. Oprins (IMEC), S. Stoffels (IMEC), R. Mahnkopf (IMC), C. Fiegna (UNIBO), T. Cilento (SNPS-CH), S. Ress (BME) |

| Reviewer(s)    | V. Melikyan (SNPS-AM), D. Rossi (UNIBO)                                                                                                                                                                                         |

| Approver(s)    | G.Gangemi(ST)                                                                                                                                                                                                                   |

| Approval date  | 01/02/2013                                                                                                                                                                                                                      |

| Release date   |                                                                                                                                                                                                                                 |

# **Distribution of the release**

| Dissemination level | СО |

|---------------------|----|

| Distribution list   |    |

|                     |    |

# History

| - J        |                                                |

|------------|------------------------------------------------|

| DATE       | Comment                                        |

| 22-01-2013 | Initial version                                |

| 29-01-2013 | Revised version, approved by all partners      |

| 01/02/2013 | Check and ship out                             |

|            |                                                |

|            |                                                |

|            |                                                |

|            | DATE           22-01-2013           29-01-2013 |

## References

- [1] M. Ciappa, F. Carbognani, W. Fichtner: "Lifetime Prediction and Design of Reliability Tests for High Power Devices in Automotive Applications ", IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, Vol 3, NO. 4,December 2003.

- [2] Letor, S. Russo, R. Crisafulli "Life time prediction and design for reliability of Smart Power devices for automotive exterior lightining "CIPS2008" proceedings"

- [3] Therminator Deliverable D1.3.1 "Technical specification of testcases and distribution to partners of concern"

- [4] Therminator Deliverable D1.1.1 "Preliminary measurement data for various types of devices"

- [5] Therminator Deliverable D2.1.2 "Model based comparison of temperature effects on device parameters for different technology nodes"

- [6] Therminator Deliverable D7.2.1 "Demonstration of thermal-aware design techniques

- [7] A. Burenkov, J. Lorenz, Fraunhofer IISB, D2.1.4: Evaluation of self-heating effects in devices and compact thermal models for advanced device structures, THERMINATOR project office, 2012

- [8] ITRS, International Technology Roadmap for Semiconductors. 2009 Update. <www.itrs.net>, 2009.

- [9] Sentaurus TCAD, Version G-2012.06, Synopsys Inc., Mountain View, CA, USA, 2012.

- [10] C. Fiegna, Y. Yang, E. Sangiorgi, A. G. O'Neill, Analysis of self-heating effects in ultrathin-body SOI MOSFETs by device simulation, IEEE Trans. Electron. Dev. 55 (2008) pp. 233–244.

- [11] T.-Y. Chiang, K. Banerjee, K. C. Saraswat, Analytical thermal model for multilevel VLSI interconnects incorporating via effect, IEEE Electron Device Lett. 23 (2002) pp. 31–33.

- [12] M. Hinz, O. Marti, B. Gotsmann, M. A. Lantz, U. Dürig, High resolution vacuum scanning thermal microscopy of HfO<sub>2</sub> and SiO<sub>2</sub>, Appl. Phys. Lett. 92 (2008) pp. 43122–43123.

- [13] Therminator deliverable D2.1.3 "Numerical comparison of self heating in traditional (bulk, SOI) CMOS technologies & advanced (GaN) ones"

- [14] Sentaurus Synopsis, ver.X-2005.10

- [15] A. J. Scholten et al., IEEE IEDM 2009 Proceedings

- [16] L. T. Su et al., IEEE TED, vol.41(1), pp.69, 1994

- [17] J. D. Bude, Proc. Int. Conf. SISPAD, pp.23, 2000

- [18] W. Liu et al., IEEE TED, vol.53(8), p.1868, 2006

- [19] Beyne, E. "The Rise of the 3rd Dimension for System Integration", Proc. IEEE IITC, pp. 1-5, 2006.

- [20] Garrou, Ph. (ed.), Handbook of 3D-Integration, Wiley-VCH, 2008.

- [21] Leduc, P.; de Crecy, F.; Fayolle, M.; Charlet, B.; Enot, T.; Zussy, M.; Jones, B.; Barbe, J.-C.; Kernevez, N.; Sillon, N.; Maitrejean, S.; Louisa, D.; , "Challenges for 3D IC integration: bonding quality and thermal management," International Interconnect Technology Conference, IEEE 2007, vol., no., pp.210-212, 4-6 June 2007.

- [22] Lau, J. H.; , "Evolution and outlook of TSV and 3D IC/Si integration," Electronics Packaging Technology Conference (EPTC), 2010 12th , vol., no., pp.560-570, 8-10 Dec. 2010.

- [23] Agonafer, D.; Kaisare, A.; Hossain, M.;., Lee, Y.; Dewan-Sandur, B.; P., Dishongh, T.; Pekin, S.; "Thermo-Mechanical Challenges in Stacked Packaging", Heat Transfer Engineering, Vol. 29(2), 134 – 148, 2008.

- [24] Rencz, M.; Székely V.; "Structure function evaluation of stacked dies", Proceedings of the XXth SEMI-THERM Symposium, March 9-11, San Jose, CA, USA, pp 50-55, 2004.

- [25] Zhang, L.; Howard, N.; Gumaste, V.; Poddar, A.; Nguyen, L.; "Thermal Characterization of Stacked-Die Packages", 20th IEEE SEMI-THERM Symposium, pp. 55-63, 2004.

- [26] Van der Plas, G.; Limaye, P.; Loi, I.; Mercha, A.; Oprins, H.; Torregiani, C.; Thijs, S.; Linten, D.; Stucchi, M.; Katti, G.; Velenis, D.; Cherman, V.; Vandevelde, B.; Simons, V.; De Wolf, I.; Labie, R.; Perry, D.; Bronckers, S.; Minas, N.; Cupac, M.; Ruythooren, W.; Van Olmen, J.; Phommahaxay, A.; de Potter de ten Broeck, M.; Opdebeeck, A.; Rakowski, M.; De Wachter, B.; Dehan, M.; Nelis, M.; Agarwal, R.; Pullini, A.; Angiolini, F.; Benini, L.; Dehaene, W.; Travaly, Y.; Beyne, E.; Marchal, P.;, "Design Issues and Considerations for Low-Cost 3-D TSV IC Technology," Solid-State Circuits, IEEE Journal of , vol.46, no.1, pp.293-307, Jan. 2011.

- [27] Swinnen, B.; Ruythooren, W.; De Moor, P.; Bogaerts, L.;Carbonell, L.; De Munck, K.; Eyckens, B.; Stoukatch, S.; Sabuncuoglu Tezcan, D.; Tokei, Z.; Vaes, J.; Van Aelst, J. and Beyne, E.; "3D integration by Cu-Cu thermo-compression bonding of extremely thinned bulk Si die containing 10μm pitch through Si vias", Proc. IEDM Conference, December 11-13, 2006, San Fransisco.

- [28] Swinnen, B.; Jourdain, A.; De Moor, P.; Beyne E.; Chapter in Wafer Level 3-D ICs Process Technology; edited by S. Tan, R.J. Gutmann, and L.R. Reif (Eds), Springer, ISBN 978-0-387-76532-7, 2008.

- [29] Jourdain, A.; Soussan, P.; Swinnen, B.; Beyne, E.; , "Electrically yielding Collective Hybrid Bonding for 3D stacking of ICs," Electronic Components and Technology Conference, 2009. ECTC 2009. 59th , vol., no., pp.11-13, 26-29 May 2009.

- [30] http://www.mentor.com/products/mechanical/products/t3ster/

- [31] Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device) JEDEC Standard JESD51

- [32] Transient dual interface test method for the measurement of the thermal resistance junction-to-case of semiconductor devices with heat flow through a single path. JEDEC Standard JESD51-14, Nov 2010

- [33] P.Szabo, O.Steffens, M.Lenz, and G.Farkas, "Transient junction-to-case thermal resistance measurement methodology of high accuracy and high repeatability", Proc. 10th THERMINIC, Sofia-Antipolis, pp. 145-150, 2004

This page was intentionally left blank.

# Contents

| Document                                                                             |

|--------------------------------------------------------------------------------------|

| Distribution of the release                                                          |

| References                                                                           |

| 1 Introduction                                                                       |

| 2 Compact electro-thermal modelling (NXP-NL)                                         |

| 2.1 Introduction                                                                     |

| 2.2 Technical results                                                                |

| 2.2.1 Validation of the thermal models for RF-LDMOS and GaN-HEMT with measurements   |

| 2.2.2 Validation of the electro-thermal compact model with numerical calculations 19 |

| 2.2.3 Validation on different types of device                                        |

| 2.2.3.1 GaN Schottky diodes                                                          |

| 2.2.3.2 SOI-LDMOS                                                                    |

| 2.3 Conclusions                                                                      |

| 3 Verification of TCAD (SNPS-CH, together with IMC, IMEC, ST, NXP-D)                 |

| 3.1 Introduction                                                                     |

| 3.2 Verification of TCAD Models and Methodologies                                    |

| 3.2.1 Bulk CMOS 3D TCAD Model                                                        |

| 3.2.2 GaN HEMT TCAD Model / Compact Model Parameter Extraction                       |

| 3.2.3 Si power MOSFET unit cell TCAD Model                                           |

| 3.2.4 3D TCAD Electro-Thermal Modeling Methodology                                   |

| 3.3 Conclusions                                                                      |

| 4 Modelling and Simulation of discrete components for automotive (ST)                |

| 4.1 Introduction                                                                     |

| 4.2 Electrical operating conditions                                                  |

| 4.3 Layout modelling and mapping                                                     |

| 4.4 Thermal simulations                                                              |

| 4.5 Conclusions                                                                      |

| 5 Contactless identification ICs (NXP-D, together with FHG)                          |

| 5.1 Introduction                                                                     |

| 5.2           | Technical results                                                                                        | . 50 |

|---------------|----------------------------------------------------------------------------------------------------------|------|

| 5.3           | Conclusions                                                                                              | . 53 |

| 6 PSP-        | based advanced CMOS modelling (IMC)                                                                      | . 54 |

| 6.1           | Introduction                                                                                             | . 54 |

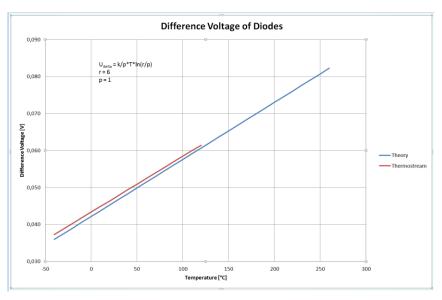

| 6.1.1         | Testcase 3: Datapath Macrocell (digital circuit)                                                         | . 54 |

| 6.1.2         | 2 40nm versus 28nm technology                                                                            | . 54 |

| 6.1.3         | 3 SOI-FinFETs and self-heating                                                                           | . 55 |

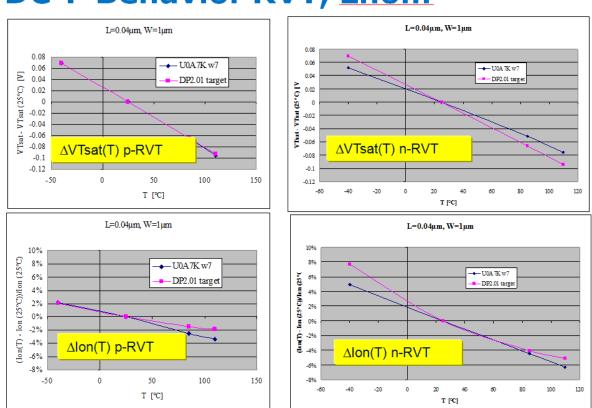

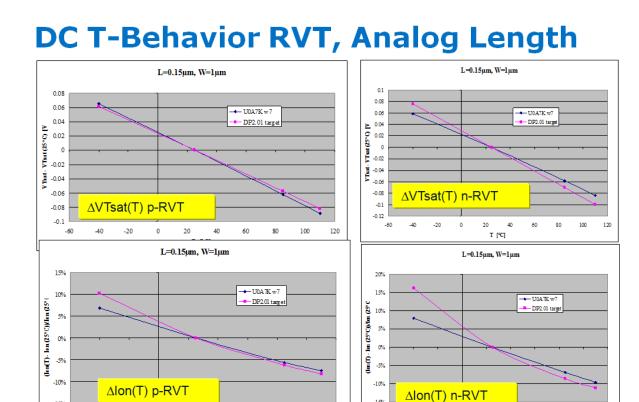

| 6.1.4         | 4 Temperature Inversion trend                                                                            | . 55 |

| 6.1.5         | 5 Therminator project objectives                                                                         | . 57 |

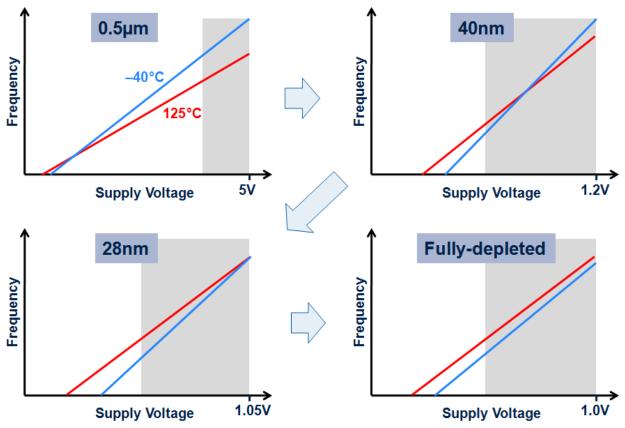

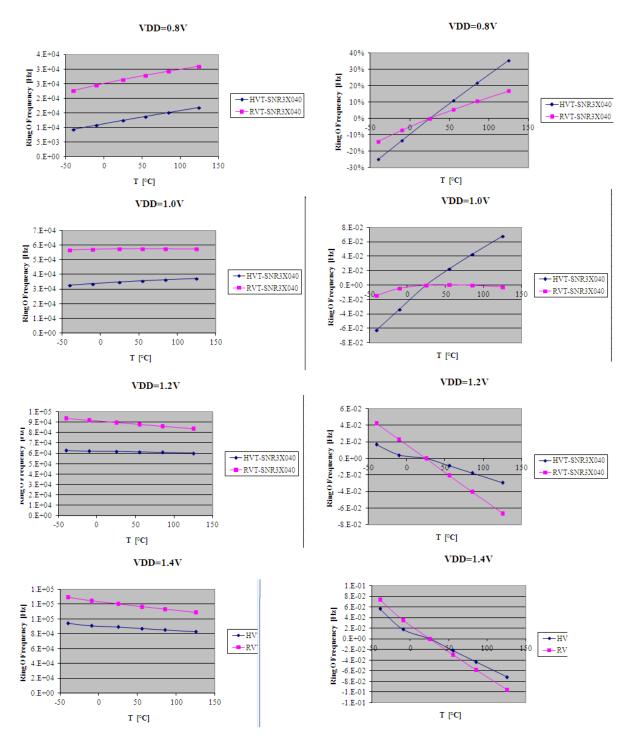

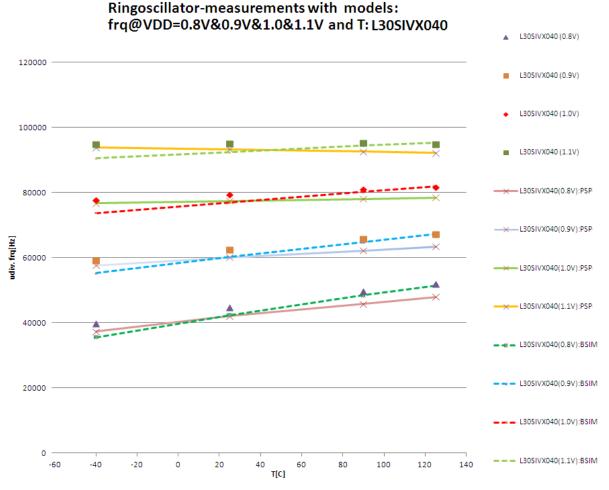

| 6.2           | 40nm Model-Hardware-Correlation (MHC) results                                                            | . 57 |

| 6.2.1         | Device level model to hardware correlation including devices for analog usage                            | 57   |

| 6.2.2         | 2 Self-heating                                                                                           | . 64 |

| 6.2.3<br>appl | 3 Circuit level Model to Hardware Correlation for digital and library standard centrations - performance |      |

| 6.2.4         | T-dependent Model Hardware Correlation for a large number of library cells                               | . 68 |

| 6.2.5<br>appl | 5 Circuit level Model to Hardware Correlation for digital and library standard ce<br>ications – leakage  |      |

| 6.3           | 28nm Model-Hardware-Correlation (MHC) results                                                            | . 72 |

| 6.3.2         | l Test structures                                                                                        | . 72 |

| 6.3.2         | 2 Findings                                                                                               | . 73 |

| 6.4           | Conclusions                                                                                              | . 81 |

| 7 TCA         | D of advanced and future MOSFETs (FHG, together with IMC)                                                | . 83 |

| 7.1.1         | I Introduction                                                                                           | . 83 |

| 7.2           | Impact of high-k gate isolation on temperature sensitivity of advanced MOSFETs                           | . 83 |

| 7.2.1         | l Conclusions                                                                                            | . 88 |

| 8 DC a        | and AC thermal-characterization of FinFETs (UNIBO)                                                       | . 90 |

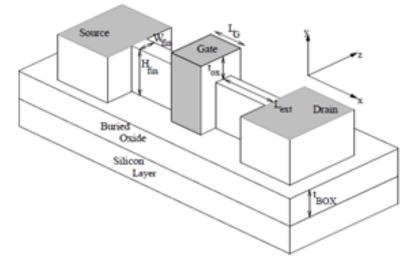

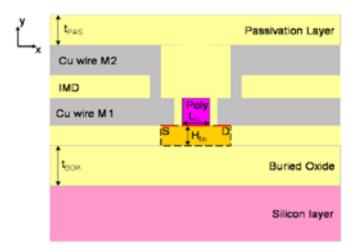

| 8.1           | Introduction                                                                                             | . 90 |

| 8.2           | Simulated devices                                                                                        | . 90 |

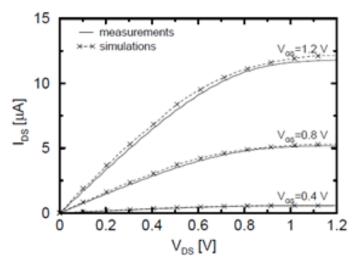

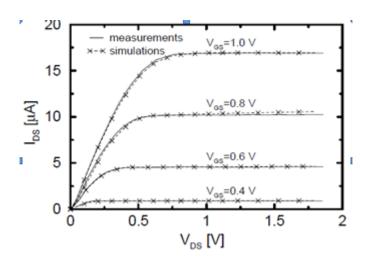

| 8.3           | Model verification                                                                                       | . 92 |

| 8.4           | Conclusions                                                                                              | . 96 |

| 9 Valio       | dation thermal compact models for 3D-ICs (IMEC)                                                          | . 97 |

| 9.1           | Introduction                                                                                             | . 97 |

| 9.2           | Technical results                                                                                        | . 98 |

|               |                                                                                                          |      |

| 9.2.1      | 3D-SIC technology                                                                   | 98  |

|------------|-------------------------------------------------------------------------------------|-----|

| 9.2.2      | Test structures description                                                         | 98  |

| 9.2.3      | Experimental validation of the thermal models                                       | 100 |

| 9.2.3      | 3.1 Test structures without TSVs                                                    | 100 |

| 9.2.3      | 3.2 Test structures with TSVs                                                       | 102 |

| 9.3 C      | Conclusions                                                                         | 103 |

|            | al resistance measurements and modeling of packaged discretes (BME, togethe<br>P-D) |     |

| 10.1 S     | amples                                                                              | 104 |

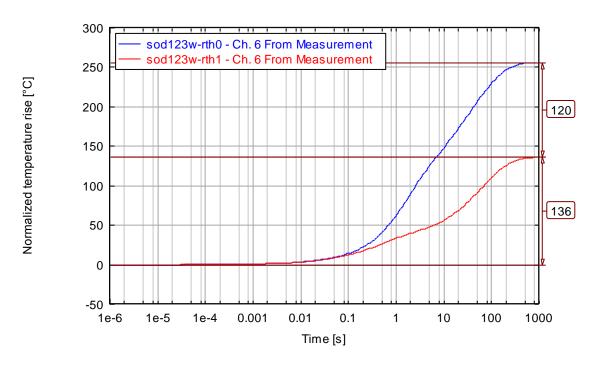

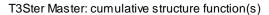

| 10.2 T     | Thermal transient measurements                                                      | 104 |

| 10.3 E     | Evaluation of the measurements                                                      | 105 |

| 10.4 O     | Overview measurement results                                                        | 108 |

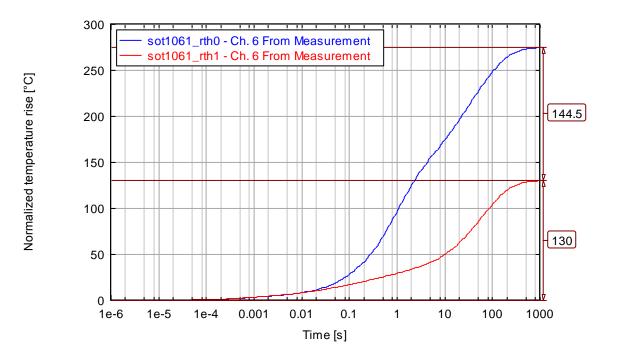

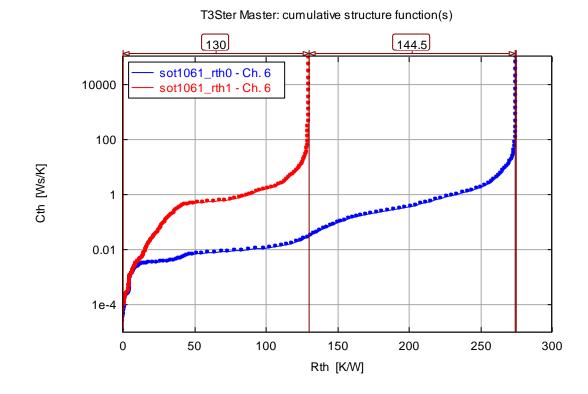

| 10.4.1     | The Z <sub>th</sub> (t) and the structure functions of the measured devices.        | 108 |

| 10.4.      | .1.1 SOD123W                                                                        | 108 |

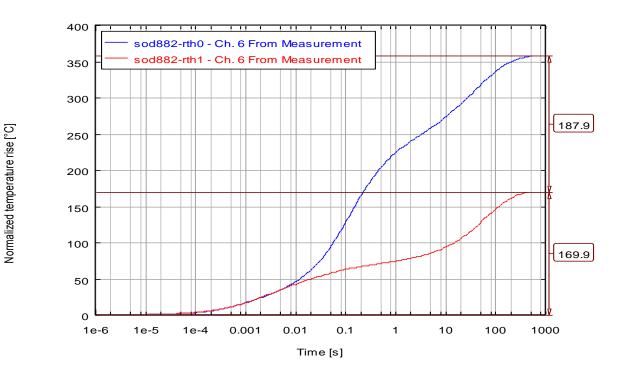

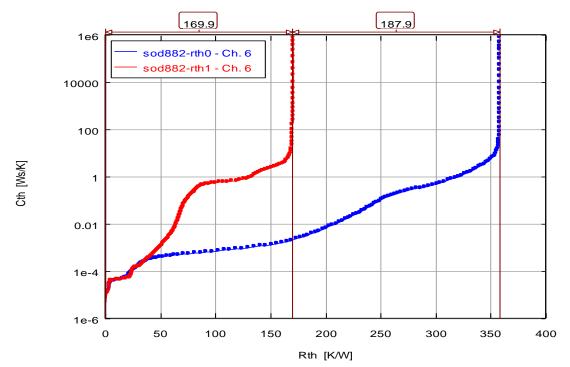

| 10.4.      | .1.2 SOD882                                                                         | 108 |

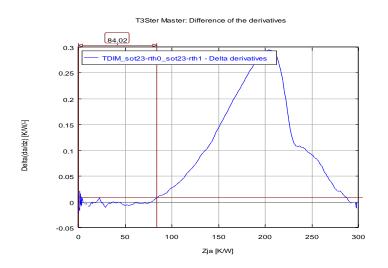

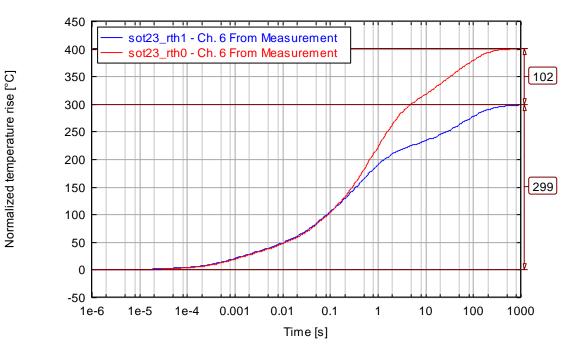

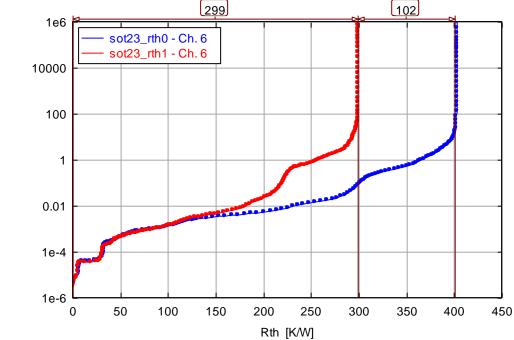

| 10.4.      | .1.3 SOT23                                                                          | 109 |

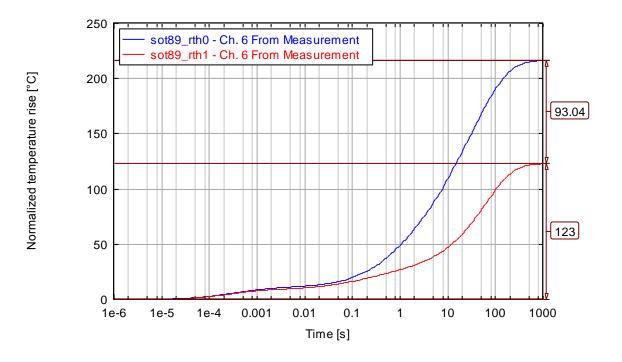

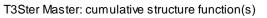

| 10.4.      | .1.4 SOT89                                                                          | 111 |

| 10.4.      | .1.5 SOT1061                                                                        | 112 |

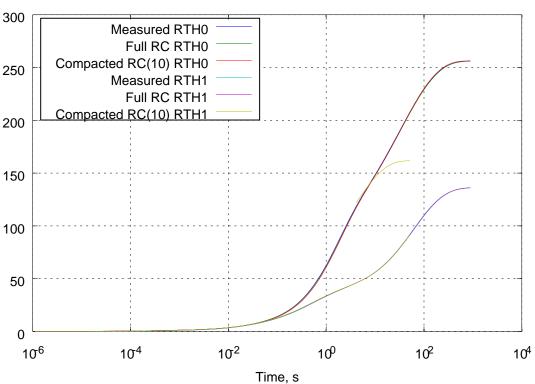

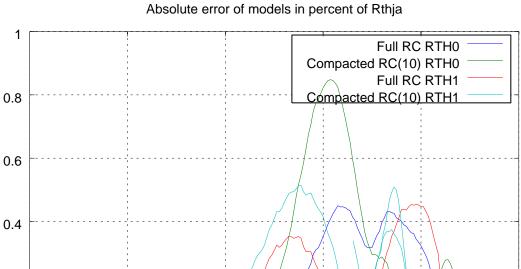

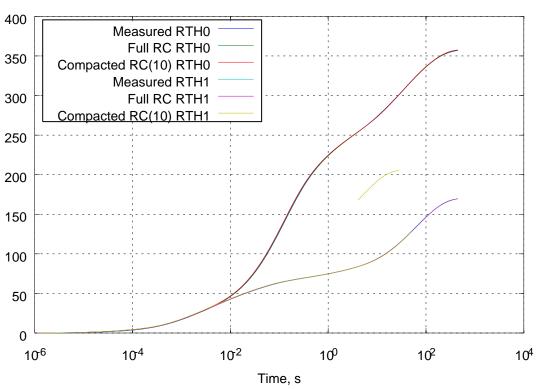

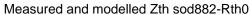

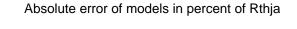

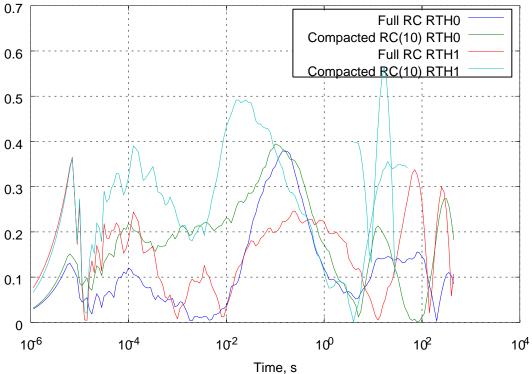

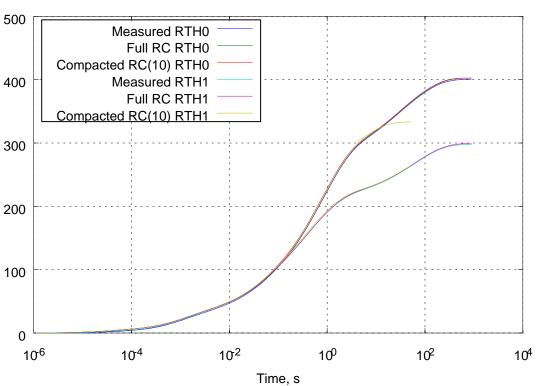

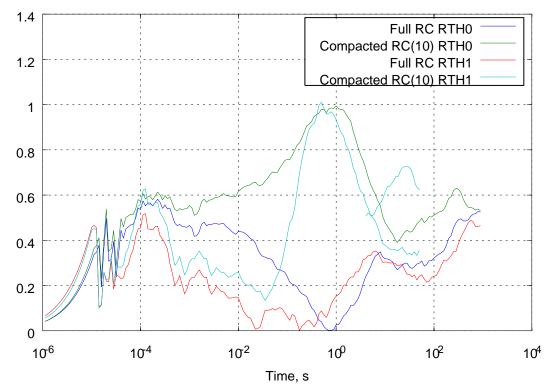

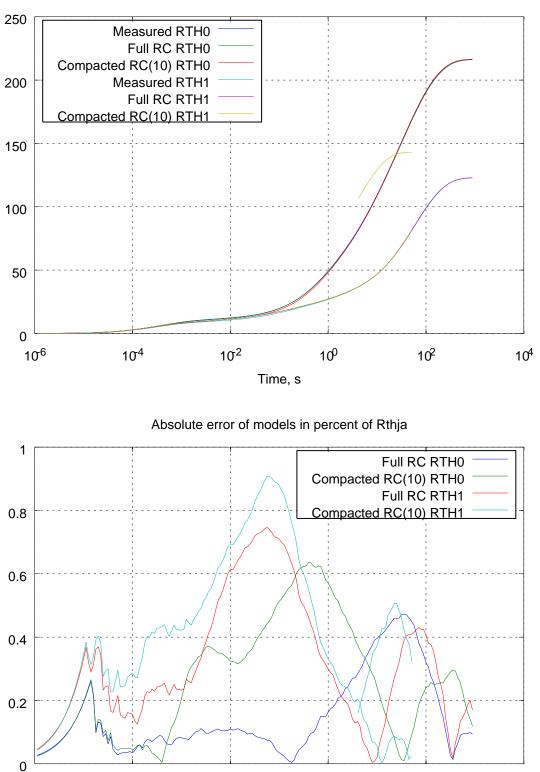

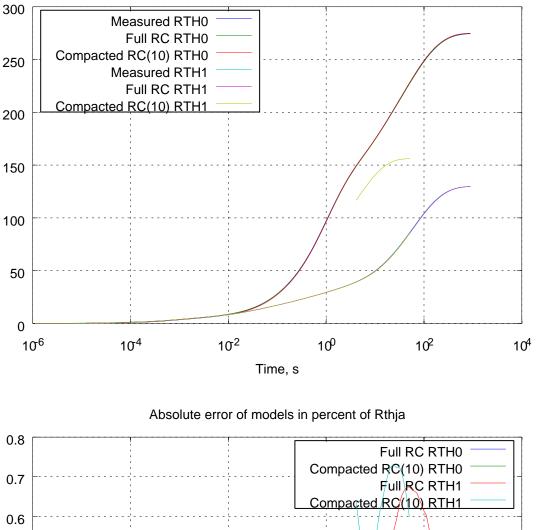

| 10.4.2     | The measured and modelled thermal transients                                        | 113 |

| 10.4.      | .2.1 SOD123W                                                                        | 113 |

| 10.4.      | .2.2 SOD882                                                                         | 114 |

| 10.4.      | .2.3 SOT23                                                                          | 115 |

| 10.4.      | .2.4 SOT89                                                                          | 116 |

| 10.4.      | .2.5 SOT1061                                                                        | 117 |

| 10.5 C     | Conclusions                                                                         | 118 |

| 11 Conclu  | isions                                                                              | 119 |

| 12 Measur  | rable objectives                                                                    | 120 |

| 13 Publica | ations and presentations                                                            | 123 |

# 1 Introduction

The main objective of WP7 is to validate the models, design techniques, and tools developed within the Therminator project. WP7 is divided into three tasks. In T7.1, validation of the thermal models of new devices, materials, and technologies will be done. The focus will be on device level, and the level of elementary building blocks to be used in large(r) circuits. The effectiveness and usability of design techniques is addressed in T7.2. In T7.2, larger building blocks, parts of circuits, and test chips are used as test cases. Finally, benchmarking and demonstration of the effectiveness of the developed EDA tools is done in T7.3. In this task, the validation addresses test chips and prototypes.

The validation results of T7.1 are presented in this deliverable. The validation activities are done with models and tools developed in WP2, 3, 4, 5, and 6. For demonstration, the test case of WP1 and examples provided by individual partners are used. The test cases of WP1 come from various fields relevant to today's European semiconductor industry. Examples are in digital, analog, RF, discretes, and power technologies, covering a wide range of devices from advanced CMOS to high-voltage devices in automotive, and addressing different technologies from silicon-on-insulator (SOI) technologies to GaN HEMTs. Since the validation activities are carried out mainly on device level, major attention is given to demonstrating the accuracy and predictability of TCAD tools, and verification of the developed compact models for circuit design. The value of calibrating thermal models in TCAD tools on test cases, in particular measurements, is that these tools can then be used as a reliable source for future device improvements and roadmap activities. In other words, validated TCAD tools allow the European semiconductor industry to improve their devices and make realistic roadmaps for the future. Several examples of these calibration and validation activities between TCAD vendors and Research institutes together with partners from the industry are presented in this report. Examples include power MOSFET (SNPS-CH, ST), advanced CMOS (FHG, SNPS-CH, IMC), and bipolar (SNPS-CH, NXP-D). Verification of compact models is important, since these models are the starting point for circuit design. Inaccurate or improperly validated compact models will result in additional hardware spins and product delays. Examples of the validation of these models for circuit design are on advanced CMOS (IMC), discretes (BME, NXP-D) and RF-LDMOS (NXP-NL). Devices of the future, such as FinFETs (UNIBO), advanced CMOS (FHG), 3D ICs (IMEC), and GaN-HEMTs (NXP-NL) are also addressed. Finally, the major industrial partners show the usefulness of the tools developed in Therminator by demonstrating the compatibility with their design flows.

In detail, the compact models for RF-LDMOS and GaN-HEMTs developed in WP2 by NXP-NL are validated in chapter 2. In chapter 3, the TCAD models developed by SNPS-CH are compared to measurement data provided by partners. The validation of the models developed in WP5 for discrete components for automotive is presented in chapter 4 by ST. NXP-D compares measurements on devices used in their contactless identification ICs with models from FHG in chapter 5. An overview of the PSP-based modelling of advanced CMOS is presented by IMC in chapter 6. TCAD of advanced CMOS and FinFETS compared to measurements is presented in chapters 7 and 8 by FHG and UNIBO, respectively. In chapter 9, the thermal models for 3D ICs developed by IMEC in WP6 are compared to and validated against measurements. BME compares their thermal measurements and compact models to packaged discretes provided by NXP-D in chapter 10. The results of T7.1 are quantified in terms of measurable objectives. An overview of all of these measurable objectives is given in chapter 12 of this report. In this chapter, the measurable objectives are also linked to Therminator's project objectives. The novelty of the work is addressed in chapter 13, where all of the output in terms of journal papers and conference contributions is collected.

## 2 Compact electro-thermal modelling (NXP-NL)

## 2.1 Introduction

High-voltage transistors are used as RF-power amplifiers in wireless communication systems. Examples of these communication systems are TV broadcast, radar, and base-stations. In most of these communication systems, Silicon RF-LDMOS transistors are used for power amplification. For future systems, gallium-nitride (GaN) technology will be increasingly used; GaN has already been introduced in some high-performance systems. The advantages of gallium nitride in power applications are due to a combination of material properties and device architecture. The material advantages are a large band gap, high critical electrical breakdown field, and high electron velocity. In the high-electron-mobility-transistor (HEMT) architecture of GaN transistors no insulator is used, avoiding mobility reduction due to scattering at the insulator interface. The benefits in material properties and device architecture can be exploited to achieve higher switching speeds and lower losses in power amplification applications.

**Figure 1** A packaged RF-LDMOS transistor is shown in the figure on the left. One of the major applications of RF-LDMOS transistors is wireless communication in base-stations. A base-station is shown in the figure on the right.

In both silicon RF-LDMOS and GaN-HEMT devices, the high applied voltages in combination with large currents lead to high dissipated powers, which in turn result in significant amounts of self-heating. In order to optimize the performance of these power amplifiers in applications, compact models for circuit simulation, accurately describing the electro-thermal behaviour, are needed. In deliverables D2.2.1 and D2.2.3, compact models for electro-thermal circuit simulation for silicon RF-LDMOS and GaN-HEMT (respectively) have been developed. The developed models are physics-based, using physical scaling rules. The advantage of these physics-based models is that the model extraction is done on a small device, while the physical scaling rules are used for larger devices. This approach allows one to extract all of the different device layouts in an efficient way. In this deliverable, these models will be validated using measurements and numerical calculations. More specifically, we will validate the electro-thermal compact models for circuit simulation developed in the

Therminator deliverables D2.2.1 and D2.2.3 using pulsed and non-pulsed IV measurements in Section 2.2.1. Furthermore, the integration of the electro-thermal models into the design flow will be demonstrated, and validation on measurement data under application conditions will be presented. In Section 2.2.2, the physical scaling of the thermal resistance in the compact thermal models will be validated against numerical calculations using a Green's function method. The results of applying the S-parameter method to determine the thermal resistance on different device types are given in Section 2.2.3. In this section, we apply the thermal characterization to different device types not studied in the previous Therminator deliverables, *i.e.* silicon-on-insulator (SOI) LDMOS and GaN Schottky diodes. The measurement results are compared to the developed models.

### 2.2 Technical results

# 2.2.1 Validation of the thermal models for RF-LDMOS and GaN-HEMT with measurements

The conventional approach in the development of electro-thermal compact models is to use a combination of pulsed and DC IV measurements in the temperature range of interest. Both pulsed and (non-pulsed) DC IV measurements are needed in order to be able to separate electrical, temperature-dependent, and self-heating effects. The pulsed measurements are done with pulses fast enough so that self-heating doesn't occur. For the parameter extraction in the compact model, the pulsed IV measurements are used to extract the electrical model parameters. Subsequently, the temperature sensitivities of these electrical parameters are obtained from the pulsed IV measurements at other temperatures. The final step is to fit the thermal resistance, and its temperature dependence, on (non-pulsed) DC IV measurements at different temperatures. Note that in this approach the thermal resistance is only a fitting parameter in the model that accounts for the differences between pulsed and (non-pulsed) DC IV measurements. Furthermore, there is no direct validation of the thermal resistance, since it is not measured directly.

In order to measure the thermal resistance of a device directly, S-parameter measurements can be used. Using this S-parameter measurement technique, pulsed IV measurements are also not needed in the parameter extraction of the model. The thermal resistance is measured directly, and can be set to the correct value in the compact model. The (non-pulsed) DC IV characteristics at different temperatures are used to extract the electrical model parameters and the corresponding temperature dependence. In Therminator deliverables D2.2.1 and D2.2.3, this novel S-parameter technique for direct extraction of the thermal resistance was applied to RF-LDMOS and GaN-HEMT power technologies. The thermal resistance was characterized directly. These S-parameter measurements were used to set the thermal resistance to the correct value in the corresponding compact models. Next, the model parameters were extracted on the (non-pulsed) DC IV characteristics.

In this part of the deliverable, we will validate the models developed in deliverable D2.2.3 and D2.2.1 using pulsed and (non-pulsed) DC IV measurements over a wide range of temperatures. Note that the pulsed IV measurements have not been used in the model development and parameter extraction.

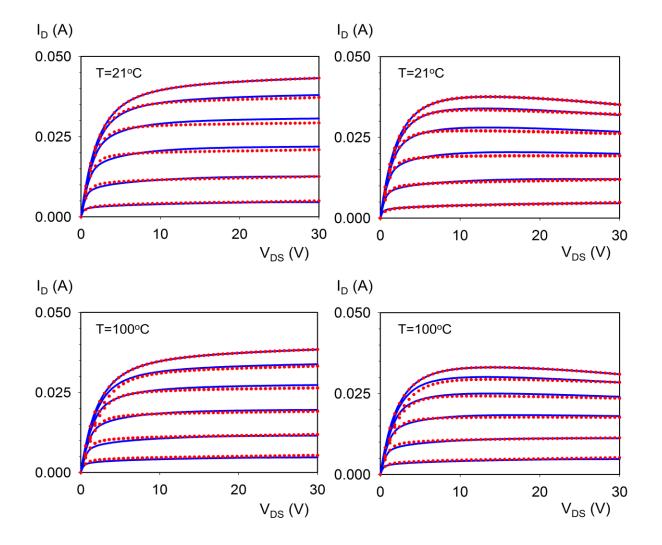

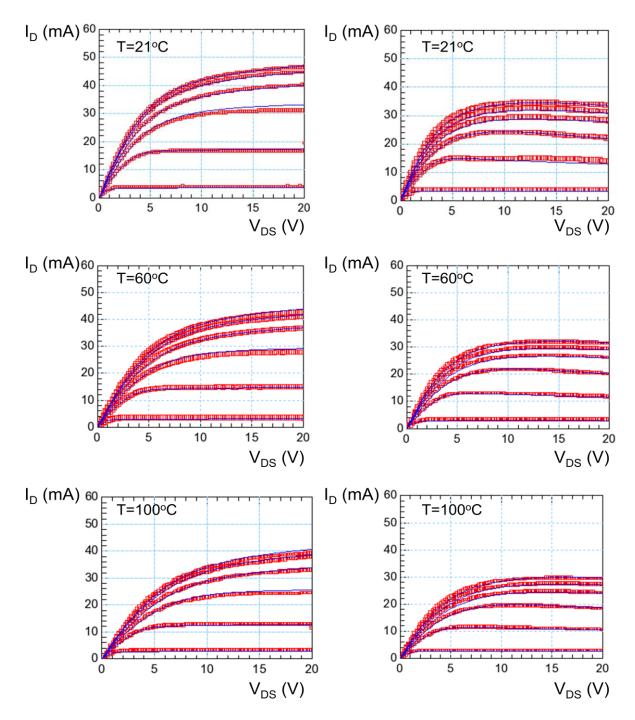

#### The results of this validation for the RF-LDMOS technology are collected in

Figure 2, Figure 3, and Figure 4. The measured pulsed and DC  $I_DV_{DS}$  characteristics of an RF-LDMOS transistor at different temperatures are compared to the compact electro-thermal model in

Figure 2. The pulsed measurements were done with a pulse width of 50 ns. It was checked, by variation of the pulse width, that the applied pulses were fast enough such that self-heating didn't occur. Comparison of pulsed measurement data at different temperatures shows that the amount of current decreases with increasing temperature (see left column of

Figure 2), and the developed RF-LDMOS model correctly describes this temperature dependence. In the right column of

Figure 2, the (non-pulsed)  $I_DV_{DS}$  characteristics are shown. These IV characteristics clearly exhibit self-heating, as the current is smaller in comparison to pulsed IV characteristics, and the current decreases with increasing bias. The developed model accurately describes the DC IV measurement data.

**Figure 2**  $I_DV_{DS}$  characteristics at  $V_{GS} = 2.5, 3, 3.5, 4, 4.5$ , and 5 V of the RF-LDMOS device measured at temperatures of T = 21 and 100 °C. The figures in the left column show the pulsed IV characteristics, using a pulse width of 50 ns. The figures in the right column show

the DC IV characteristics. The scaling of the y-axis has been kept the same in all figures in order to demonstrate the impact of the ambient temperature and self-heating on the device characteristics. The measurements (red markers) and developed model (blue solid lines) are in good agreement for the measured bias conditions and temperature range.

The IV characteristics of a larger RF-LDMOS device are shown in Figure 3 and Figure 4. The reason for showing these characteristics as well is that the compact thermal model, derived in deliverable D2.2.1, has physics-based scaling rules for the thermal resistance. Only S-parameter measurements of the smallest geometry, of which the IV characteristics are shown in

Figure 2, are needed to determine the thermal resistance. Using the physical scaling rules of our model, the thermal resistance for larger devices are calculated. Comparison of the measured pulsed and (non-pulsed) DC IV characteristics of such a larger device, shown in Figure 3 and Figure 4, to the model demonstrates that these scaling rules give the correct results. Furthermore, it should be noted that for larger devices, with larger currents, it becomes more difficult to supply fast pulses and measure the pulse IV characteristics without self-heating. Compare the small device of

Figure 2, where pulses of 50 ns are applied, to the larger device of Figure 3 and Figure 4, where pulses of 0.5  $\mu$ s had to be applied. Although in both cases the pulses were checked to be fast enough to eliminate self-heating, it is known that the equipment has difficulty in supplying these pulses, fast enough to prevent self-heating, to larger devices. The reasons are the higher currents of these larger devices and the lower impedances of these larger devices with respect to the reference impedance of 50  $\Omega$  used in the equipment. In the conventional modelling approach, in which pulsed and (non-pulsed) IV characteristics are used, this becomes a problem. However, in our S-parameter method, together with the physics-based scaling rules, characterized at once with the tools developed in WP2 of Therminator. The problems with characterization of larger devices are now circumvented.

**Figure 3**  $I_DV_{DS}$  characteristics of a larger RF-LDMOS device measured at temperatures of T = 21, 60, and 100 °C. The figures in the left column show the pulsed IV characteristics, using a pulse width of 500 ns. The figures in the right column show the DC IV characteristics. The scaling of the y-axis has been kept the same in all figures in order to demonstrate the impact of the ambient temperature and self-heating on the device characteristics. The measurements (red markers) and developed model (blue solid lines) are in good agreement for the measured bias conditions and temperature range.

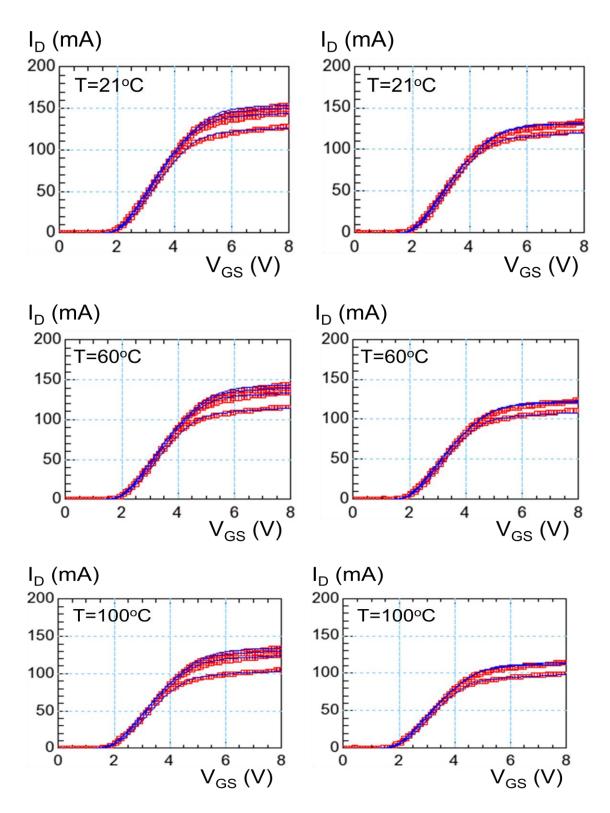

**Figure 4**  $I_DV_{GS}$  characteristics of a larger RF-LDMOS device measured at temperatures of T = 21, 60, and 100 °C. The figures in the left column show the pulsed IV characteristics, using a pulse width of 500 ns. The figures in the right column show the DC IV characteristics. The scaling of the y-axis has been kept the same in all figures in order to demonstrate the impact of the ambient temperature and self-heating on the device characteristics. The measurements (red markers) and developed model (blue solid lines) are in good agreement for the measured bias conditions and temperature range.

**Figure 5**  $I_DV_{DS}$  characteristics of a GaN-HEMT device measured at temperatures of T = 21, 60, and 100 °C. The figures in the left column show the pulsed IV characteristics, using a pulse width of 500 ns. The figures in the right column show the DC IV characteristics. The scaling of the y-axis has been kept the same in all figures in order to demonstrate the impact of the ambient temperature and self-heating on the device characteristics. The measurements (red markers) and developed model (blue solid lines) are in good agreement for the measured bias conditions and temperature range

Validation on the GaN-HEMT devices was done in the same way. A comparison of measured pulsed and (non-pulsed) IV characteristics to the corresponding electro-thermal GaN-HEMT model developed in Therminator deliverable D2.2.3 is shown in Figure 5. Measurements and model were found to agree.

In summary, a detailed validation of the electro-thermal compact models for power technologies developed in WP2 of Therminator on pulsed and non-pulsed IV-characteristics has been presented (see

Figure 2–Figure 5) demonstrating our measurable objective MO7.1.1 of validation of thermal models for RF-LDMOS and GaN-HEMT.

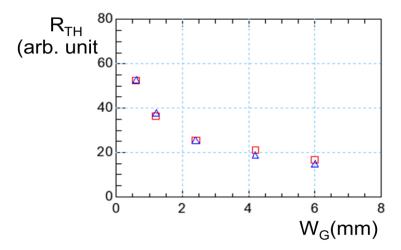

In Figure 6, the S-parameter measurement technique for directly determining the thermal resistance is validated for other types of device, *i.e.* larger RF-LDMOS transistors as used in Therminator deliverable 2.2.1. Measurements and simulations are in agreement. This comparison demonstrates the accuracy of the physical scaling rules derived in WP2 of Therminator. Thermal characterization of the smallest geometry is sufficient. Benefits of this approach include (i) time-efficient characterization of all geometry variants within a technology, and (ii) no need to measure large devices, which are difficult to characterize.

**Figure 6** Validation of the S-parameter measurement technique for other type of device, *i.e.* larger RF-LDMOS transistors as used before. The RF-LDMOS transistors used in deliverable D2.2.1 had a maximum total gate width  $W_G$  below 2.5 mm. Measurements are shown as red squares, and the electro-thermal compact model results are shown as blue triangles.

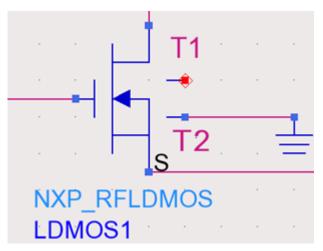

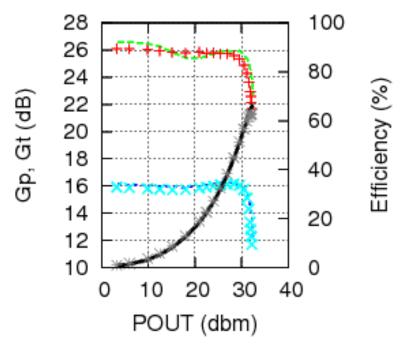

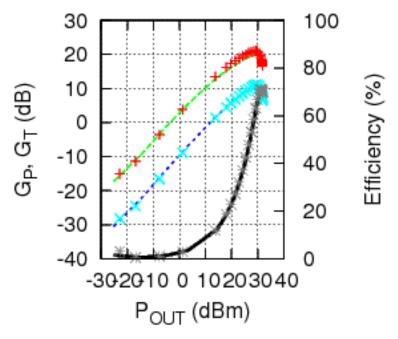

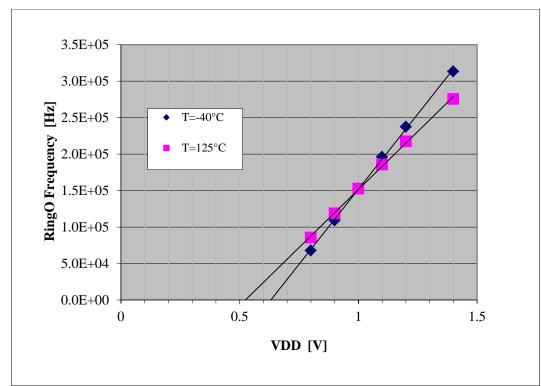

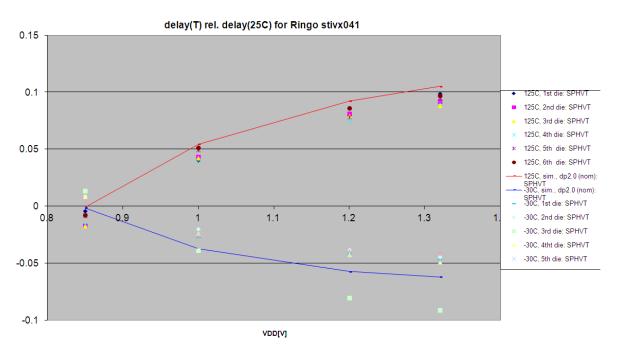

The thermal compact model for RF-LDMOS developed in Therminator has been integrated into a commercial design flow, as shown in the snapshot of Figure 7. The model integrated into the commercial simulator has been used to do large-signal simulation, and validation with measurements under application conditions. The results of these simulations and validation activity are reported in Figure 8 and Figure 9. The large signal measurements were done on a load-pull system, with active tuning of the load impedances. This active tuning of the load impedances allows one to accurately measure the transistors for optimum performance, in this case efficiency. In Figure 8, the comparison of large signal measurements and simulations for optimum efficiency in class-AB operation is shown. The comparison of large signal measurements and simulations, the electro-thermal model accurately matches the measurements. In conclusion, we have embedded the RF-LDMOS model into our design flow and compared it to measurement data taken under typical application conditions (see Figure 7–Figure 9), demonstrating our

measurable objective MO7.1.3 of integration of the electro-thermal model for RF-LDMOS into design tools and validation on large-signal application data.

**Figure 7** Schematic representation of the electro-thermal RF-LDMOS model in a commercial design tool, *i.e.* the Agilent ADS simulator. The nodes T1 and T2 are the nodes of the thermal compact model derived in Therminator deliverable D2.2.1.

**Figure 8** Large-signal validation in class-AB operation of the RF-LDMOS model. The power gain ( $G_P$ ), transducer gain ( $G_T$ ), and efficiency are shown as a function of the output power. The red markers and green line correspond to the measured and simulated power gain ( $G_P$ ), whereas the light blue markers and dark blue line correspond to the measured and simulated transducer gain ( $G_T$ ), both displayed on the left y-axis. The grey markers and black line correspond to the measured and simulated efficiency, displayed on the right y-axis.

**Figure 9** Large-signal validation in class-C operation of the RF-LDMOS model. The power gain ( $G_P$ ), transducer gain ( $G_T$ ), and efficiency are shown as a function of the output power. The red markers and green line correspond to the measured and simulated power gain ( $G_P$ ), whereas the light blue markers and dark blue line correspond to the measured and simulated transducer gain ( $G_T$ ), both displayed on the left y-axis. The grey markers and black line correspond to the measured and simulated efficiency, displayed on the right y-axis.

#### 2.2.2 Validation of the electro-thermal compact model with numerical calculations

In Therminator deliverable D2.2.1, a compact thermal model was derived for arrayed power transistors. In this section, the physical scaling rules of the thermal resistance of this compact thermal model will be validated with numerical calculations. Since a complete mathematical derivation of the thermal resistance of the compact thermal model was already given in deliverable D2.2.1, we will only highlight the approach followed, and summarize the main approximations.

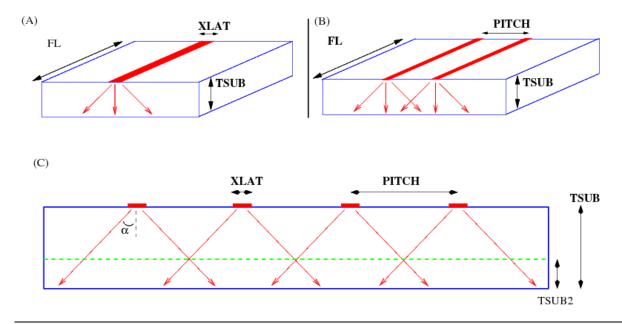

**Figure 10** A power device with finger length FL and lateral dimensions XLAT is represented by a heat source at the surface of the substrate shown in figure A. In practice, multiple devices are organized in arrays, and thermal cross-talk or mutual heating will occur, as shown as in figure B. A compact thermal model for transistors, separated by a distance PITCH in an array, was derived in Therminator deliverable D2.2.1 by assuming that the heat flows within an angle  $\alpha$  into the substrate. In the upper layer of the substrate, no mutual heating occurs, whereas in the bottom layer the heat conduction is proportional to the total area of the array (see figure C).

In a power device, the heat is generated at the surface of the substrate, where the current is transported. For a single transistor, the heat is generated in a rectangular area. The dimensions of this area are the finger length FL and the lateral dimension of current flow XLAT. The finger length is the width of the device. XLAT corresponds to the distance from the source to the drain. Since the finger length ( $\sim 0.1-1$  mm) is much longer than the lateral dimension (~2–5  $\mu$ m), thermal effects at the end of the finger were neglected in the compact thermal model. For this reason, the heat source of a single transistor was modelled as a uniform strip, as shown in Figure 10A. In practical devices, multiple transistors are arranged in arrays (see Figure 10B), and thermal cross-talk or mutual heating will occur. In the compact thermal model, it was assumed that the heat flows within an angle  $\alpha$  into the substrate, as shown in Figure 10C. The thermal resistance of the arrayed devices was calculated in the compact thermal model by assuming that (i) no mutual heating in the top layer of the substrate occurs, and (ii) the heat conduction is proportional to the area of the total array in the bottom layer of the substrate (see Figure 10C). With the aforementioned approximations, it was demonstrated in deliverable D2.2.1 that it is possible to derive an analytical expression for the thermal resistance depending on all relevant geometry variables for power technologies, *i.e.* finger length, lateral device dimension, pitch, and substrate thickness.

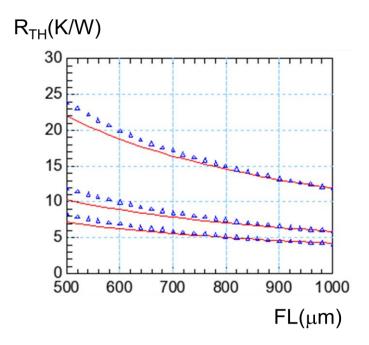

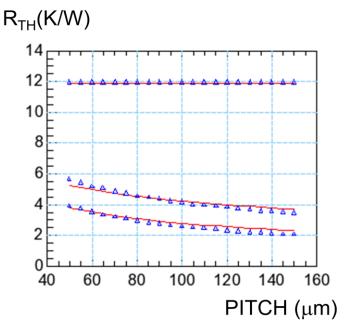

In order to validate the compact thermal model, numerical calculations of the thermal resistance were done using an in-house software tool. These numerical calculations are based on directly solving the heat equation using a Green's function approach. This numerical approach is of course too time-consuming to be integrated within a compact device model of the transistor for fast circuit simulations. However, directly comparing the results of these numerical calculations using the Green's function approach to the derived compact thermal model for different layout variations is possible. The main results of this comparison are collected in Figure 11 to Figure 14. In Figure 11, the thermal resistance of the thermal compact model is compared to the results of the numerical calculations using a Green's function method as a function of finger length.

**Figure 11** Validation of the thermal compact model (blue markers) with numerical calculations using a Green's function method (solid red line). The thermal resistance is shown as a function of finger length FL for a single-cell device, 3 devices, and 5 devices in parallel.

A similar type of validation is shown in Figure 12, where both methods are compared for different pitches.

**Figure 12** Validation of the thermal compact model (blue markers) with numerical calculations using a Green's function method (solid red line). The thermal resistance is shown as a function of PITCH, for a single-cell device, 5 devices, and 9 devices in parallel. The PICTH has no meaning in the case of a single-cell device, and the thermal resistance is constant.

Finally, the thermal resistance of the thermal compact model is compared to the numerical results of the Green's function method as a function of the number devices in parallel, as

shown in Figure 13, and Figure 14. In summary, Figure 11–Figure 14 demonstrate that the approximations made in the thermal compact model are validated by the numerical calculations using the Green's function method for all the relevant geometry variations in a power technology.

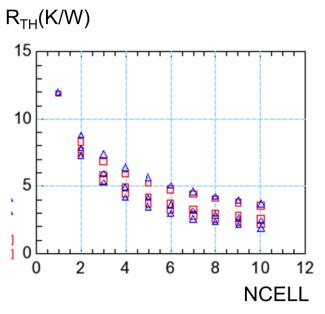

**Figure 13** Validation of the thermal compact model (blue markers) with numerical calculations using a Green's function method (red markers). The thermal resistance is shown as a function of the number of cells for PITCHES of 50, 100, and 150  $\mu$ m.

**Figure 14** Validation of the thermal compact model (blue markers) with numerical calculations using a Green's function method (red markers). The thermal resistance is shown as a function of the number of cells for PITCHES of 50, 100, and 150  $\mu$ m.

#### 2.2.3 Validation on different types of device

In this section, the S-parameter method for determining the thermal resistance is applied to different device types not studied in the previous Therminator deliverables (D2.2.1 and D2.2.3). For the silicon devices, silicon-on-insulator (SOI) LDMOS devices are studied

instead of the RF-LDMOS devices. For GaN devices, Schottky diodes instead of GaN HEMTs are measured and validated with a model.

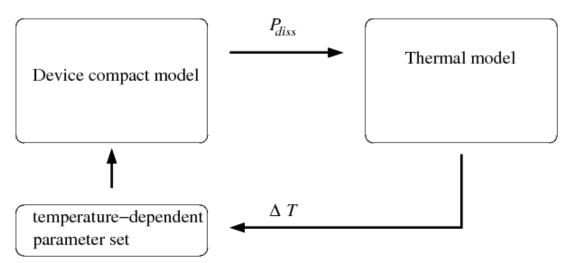

The basic working principle of the physics-based electro-thermal compact model is shown in Figure 15. The total dissipated power in the device,  $P_{diss}$ , is calculated from the compact model describing the electrical characteristics of the device. The thermal network calculates the temperature increase with respect to the ambient temperature using the dissipated power. The calculated temperature increase results in a different parameter set for the compact model of the device, which in turn results in a different amount of dissipated power. The final transistor temperature and dissipated power are known after the compact device model and thermal model have converged in the circuit simulator.

**Figure 15** Schematic overview of the working principle of a device compact model in combination with a thermal model. For modelling the GaN Schottky diode, the device compact model of the GaN HEMT, developed in deliverable D2.2.3, will be replaced by a developed GaN Schottky diode model. For modelling the SOI-LDMOS, the thermal model for RF-LDMOS, developed in deliverable D2.2.1, will be adapted for SOI.

To study and compare measurements with models for the different device types, appropriate changes need to be made in existing models developed in WP2 of Therminator. These changes can be in the device compact model and/or in thermal model of Figure 15. In order to study the GaN Schottky diodes, the GaN-HEMT compact device model as developed in D2.2.3 needs to be replaced by a Schottky diode model. The thermal model can be reused, because the Schottky diodes are organized in arrays in the same way as the RF-power devices (see Figure 10). For SOI-LDMOS, the silicon RF-LDMOS model approach can be used as a starting point. In this case, the main modifications are in thermal model where the different substrate, *i.e.* oxide instead of silicon, requires adaptation.

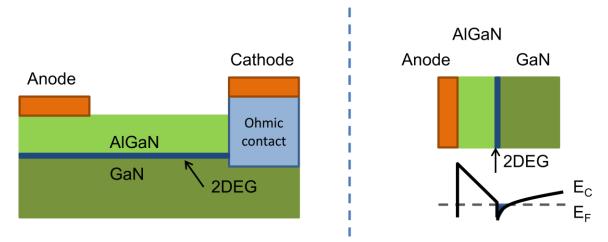

#### 2.2.3.1 GaN Schottky diodes

A schematic cross-section of the GaN Schottky diode is shown in Figure 16. The material layers on top of the substrate are the main GaN layer and an AlGaN layer. A thin layer of electrons, *i.e.* a two-dimensional electron gas (2DEG), is formed at the AlGaN-GaN hetero-junction, *i.e.* the interface between the AlGaN and GaN layers. The anode makes a Schottky contact to the 2DEG layer, whereas the cathode contact of the diode is made by a metal with an Ohmic contact to the 2DEG layer.

Figure 16 Schematic cross-section of the GaN Schottky diode (left), and schematic band diagram (right), showing the Fermi level ( $E_F$ ) and the conduction-band minimum ( $E_C$ ) at equilibrium.

In order to characterize the GaN Schottky diode, the S-parameter characterization technique (as described as part of Therminator deliverable D1.1.1) is used. The S-parameter technique allows one to determine the thermal resistance directly from measurements. The measurement results are compared to the developed electro-thermal compact model for the Schottky diodes. The model parameters have been extracted on the measurements of the smallest device only. The physical scaling rules have been used to compute the thermal resistances for the larger devices with more devices in parallel, different finger length, and variations in device separation (pitch).

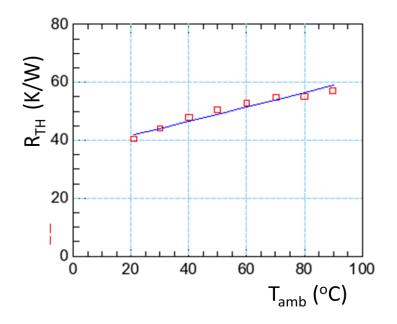

The thermal resistance of the Schottky diode as measured with the S-parameter characterization technique is compared to the developed Schottky model in Figure 17. The thermal resistance was extracted under forward operation of the diode. Measurements and

model were found to be in good agreement over the measured temperature range from 20  $^{\circ}$ C to 90  $^{\circ}$ C.

**Figure 17** Thermal resistance  $R_{TH}$  versus ambient temperature  $T_{amb}$ , comparing direct characterization of the thermal resistance using S-parameters (red rectangles) to the Schottky diode model (blue line).

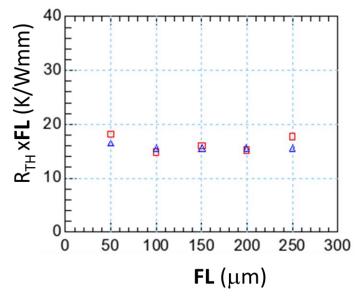

The thermal resistance as a function of finger length FL is shown in Figure 18. In the compact thermal model derived for GaN-HEMT in deliverable D2.2.3 of Therminator WP2, and now reused for the GaN Schottky diodes, thermal effects at the edges of the fingers were assumed to be small enough to be neglected. From symmetry it follows that the resulting thermal resistance has to be inversely proportional to the finger length **FL**. The measurements, as shown in Figure 18, demonstrate this dependence.

**Figure 18** Thermal resistance times finger length ( $R_{TH} \times FL$ ) versus the finger length (FL), comparing direct characterization using S-parameters (red rectangles) to our Schottky diode model (blue triangles). The measurements demonstrate that the thermal resistance of the

Schottky diodes is inversely proportional to the finger length, which demonstrates that the impact of thermal effects at the ends of the fingers is marginal.

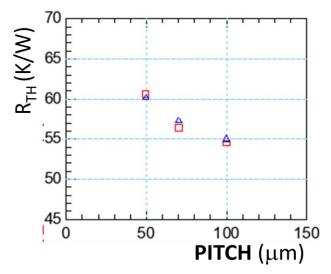

**Figure 19** Thermal resistance  $R_{TH}$  versus PITCH, comparing measurements obtained with the S-parameter technique (red rectangles) to our Schottky diode model (blue triangles). The thermal resistance decreases for larger pitches due to less mutual heating between devices. Model parameters have been extracted only on a small reference device (not shown). The physical scaling equations have been used to compute the thermal resistances for the larger devices.

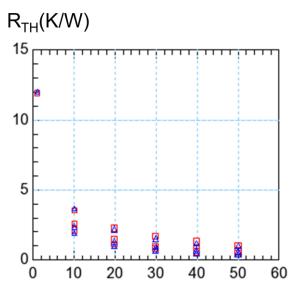

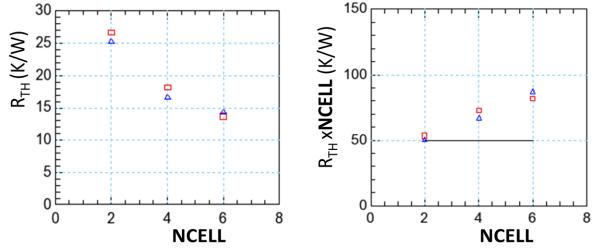

In Figure 19, the measured and modelled thermal resistance as a function of pitch is shown. For a larger pitch, the thermal resistance decreases because there is less mutual heating between devices in the array of Schottky diodes. The measured and modelled thermal resistance as a function of the number of Schottky diodes in an array is shown in Figure 20. The characterization with the S-parameter technique gives a thermal resistance decreasing with the number of devices or cells. However, the measured thermal resistance was not found to be inversely dependent on the number of cells, due to mutual heating. The compact thermal model gives an accurate description of the mutual heating of Schottky diodes.

**Figure 20** The thermal resistance  $R_{\text{TH}}$  versus the number of cells **NCELL**, comparing direct characterization of  $R_{\text{TH}}$  using S-parameters (red rectangles) to our Schottky diode model (blue triangles), is shown in the figure on the left. The parameters have been extracted directly on a small reference device, and then the

physical scaling equations have been used in order to obtain the thermal parameters for the other devices. In the figure on the right, the same thermal resistance data has been scaled with **NCELL**. In the absence of mutual heating between cells, this scaled thermal resistance should be constant, as shown by the solid black line. However, the scaled thermal resistance obtained from direct characterization (red rectangles) is not constant due to mutual heating. The derived compact thermal model with mutual heating and its physical scaling (blue triangles) is in good agreement with the measurements.

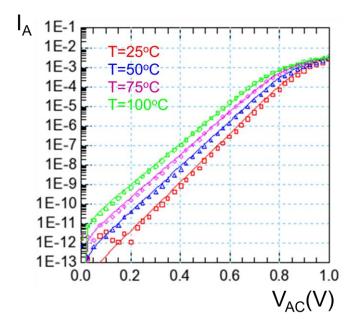

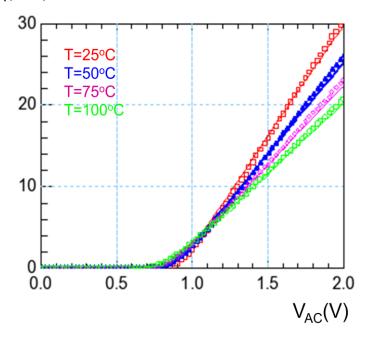

Finally, the developed electro-thermal GaN Schottky diode model is validated on IV measurements. In Figure 21, measurements of the forward diode IV characteristics are compared on a logarithmic scale.

**Figure 21** Validation of the developed GaN Schottky diode model on forward diode IV characteristics for temperatures in the range of T = 25 °C to T = 100 °C. Measurements (markers) are in good agreement with the model (solid lines).

Pulsed and DC IV characteristics as a function of temperature are shown in Figure 22. The pulsed measurements were taken with a pulse width of 0.5  $\mu$ s. By variation of the pulse width, it was confirmed that no self-heating effects are present in the pulsed measurements. The developed GaN Schottky diode model gives a good description of the temperature dependence in the pulsed measurements, and the self-heating in the DC IV characteristics.

**Figure 22** Validation of the developed GaN Schottky diode model on pulsed IV measurements in the figure on the left, and DC IV measurements in the figure on the right. Measurements (markers) are in good agreement with the model for measured temperatures in the range of T = 25 °C to T = 100 °C.

Figure 23 shows a detail of the forward Schottky diode IV characteristics with a temperature inversion point. The temperature inversion point exists because at low forward voltages  $V_{AC}$  the current increases with temperature, as shown in Figure 21, whereas at higher forward voltages  $V_{AC}$  the current decreases with temperature. At lower forward voltages, the current increases with temperature because of the diode characteristics ( $I \sim \exp(V_{AC}/(k_B \cdot T))$ )). The decrease of current at higher forward voltages occurs because the series resistance of the 2DEG increases with temperature.

**Figure 23** Detail of the forward Schottky diode IV characteristics. The measurements show a temperature inversion point around a forward voltage  $V_{AC} = 1.1$  V. The temperature inversion is the result of diode IV characteristics, which increase with temperature at low forward voltages (see also Figure 21), and decrease with temperature due to an increasing series

resistance. The temperature inversion effect in the measured IV characteristics (markers) is described accurately by our GaN Schottky diode model.

The overall accuracy of the GaN Schottky diode model, as shown in Figure 17–Figure 23, was found to be within 15%.

#### 2.2.3.2 SOI-LDMOS

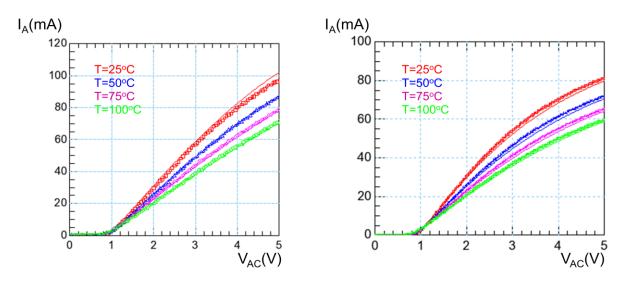

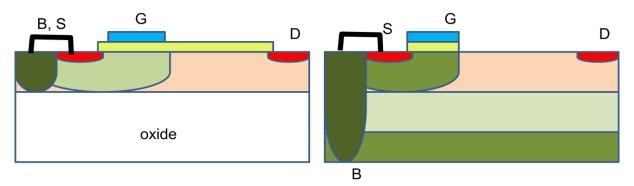

A schematic cross-section of the SOI-LDMOS transistor is shown in Figure 24. Similar to the RF-LDMOS transistor, which is also shown schematically in Figure 24, the SOI-LDMOS transistor comprises a channel region in combination with a drift region, or drain extension. The purpose of the drift region is to protect the channel region from high voltages. The important difference between the SOI-LDMOS and RF-LDMOS transistors for thermal behaviour is the substrate.

**Figure 24** Schematic cross-sections of the SOI-LDMOS transistor (figure on the left) and the RF-LDMOS transistor (figure on the right).

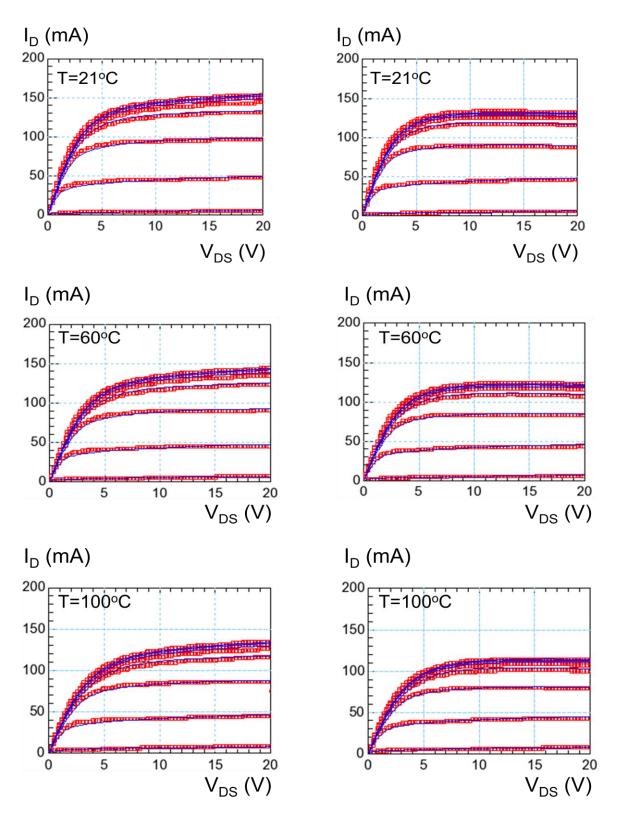

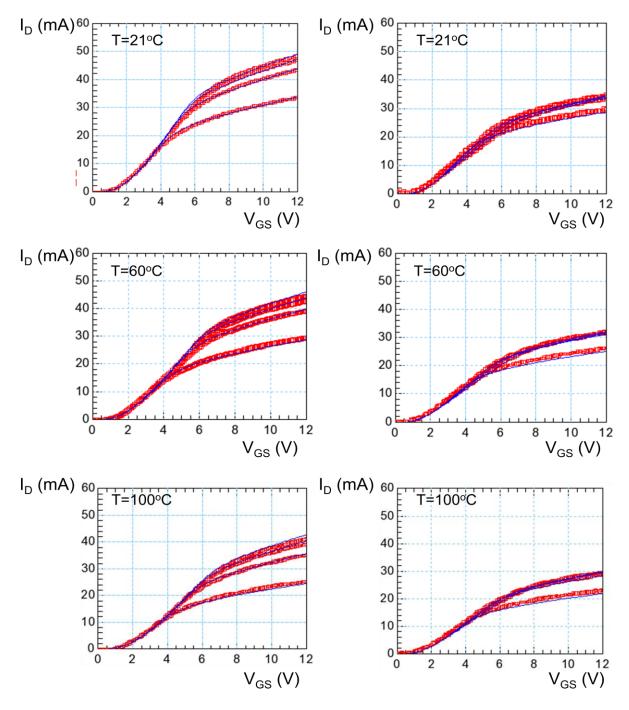

In the case of the SOI-LDMOS transistor, a substrate consisting of an oxide layer is used. The thermal conductivity of the silicon oxide is much smaller than that of silicon. For this reason, the SOI-LDMOS device will exhibit more self-heating. The advantages of the oxide layer in the substrate of the SOI-LDMOS device are electrical isolation and improved vertical breakdown. Comparing the thermal conductivity of the silicon oxide of 1.4 W/(K $\cdot$ m) to the thermal conductivity of silicon of 150 W/( $K \cdot m$ ) shows that the thermal conductivity of silicon oxide is much smaller. In the SOI-LDMOS transistor, heat flow to the edges of the device becomes important and needs to be included in the thermal model. For this reason, the thermal model as used for the RF-LDMOS model has been modified. The overall results, in which the electro-thermal SOI-LDMOS model is compared to corresponding measurements, are shown in Figure 25 and Figure 26. Figure 25 shows the measured pulsed and DC  $I_DV_{DS}$ characteristics of the SOI-LDMOS device, measured at three temperatures (T = 21, 60, and100 °C). The pulsed  $I_D V_{DS}$  characteristics have been measured with a pulse width of 0.5 µs. It was checked experimentally (by varying the pulse width) that, for the used pulse width of  $0.5 \,\mu s$ , self-heating can be excluded. The reduction in current in the pulsed  $I_D V_{DS}$ characteristics as a function of increasing temperature (left column of Figure 25) can be attributed to the temperature dependence of the transistor parameters, e.g. the mobility in the channel region and the on-resistance of the drift region. Comparison of the measured to the simulated pulsed  $I_D V_{DS}$  characteristics demonstrates that the transistor parameters have the correct temperature dependence. The impact of self-heating in the SOI-LDMOS device becomes clear by comparing the pulsed to DC I<sub>D</sub>V<sub>DS</sub> characteristics at each temperature in Figure 25. Comparison of the measured and simulated DC I<sub>D</sub>V<sub>DS</sub> characteristics in the right column of Figure 25 demonstrates that the model also accurately describes the self-heating in the transistor over the measured temperature range. The corresponding  $I_D V_{GS}$  transfer

characteristics are shown in Figure 26. The accuracy of the electro-thermal SOI-LDMOS model, shown in Figure 25 and Figure 26, was found to be within 15%.

**Figure 25**  $I_DV_{DS}$  characteristics of the SOI-LDMOS device measured at temperatures of T = 21, 60, and 100 °C. The figures in the left column show the pulsed IV characteristics, using a pulse width of 0.5 µs. The figures in the right column show the DC IV characteristics. The scaling of the y-axis has been kept the same in all figures in order to demonstrate the impact of the ambient temperature and self-heating on the device characteristics. The measurements (red markers) and developed model (solid blue lines) are in good agreement for the measured bias conditions and temperature range.

**Figure 26**  $I_DV_{GS}$  transfer characteristics of the SOI-LDMOS device measured at temperatures of T = 21, 60, and 100 °C. The figures in the left column show the pulsed IV characteristics, using a pulse width of 0.5 µs. The figures in the right column show the DC IV characteristics. The scaling of the y-axis has been kept the same in all figures in order to demonstrate the impact of the ambient temperature and self-heating on the device characteristics. The measurements (red markers) and developed model (solid blue lines) are in good agreement for the measured bias conditions and temperature range.

In conclusion, we have shown that (i) the scalable electro-thermal model developed for the GaN-HEMT can be reused for GaN Schottky diodes by using the same scalable thermal model of deliverable D2.2.1 and replacing the device models, and (ii) good modelling results are obtained for SOI-LDMOS by adapting the thermal model for the substrate. These results

demonstrate our measurable objective MO7.1.2 of reuse by adapting electro-thermal models developed on RF power technologies for other types of devices.

## 2.3 Conclusions

Compact electro-thermal models for silicon RF-LDMOS and GaN-HEMT devices have been developed in WP2 of Therminator (deliverable D2.2.1 and D2.2.3). These models derived in WP2 are physics-based and have a scalable model for the thermal resistance. In this deliverable, these models have been validated using measurements and numerical calculations. The validation against measurement data has demonstrated that the compact models give an accurate description of the pulsed and DC IV characteristics over a wide temperature range for both silicon RF-LDMOS and GaN-HEMT. In addition, the models have been shown to be in good agreement with large-signal application measurements. Next, the thermal compact model has been compared to numerical calculations using a Green's function approach. This comparison has resulted in validation of the approximations made in the derivation of the compact thermal model in WP2, as well as validation of the compact thermal model over a wide range of geometries.

Furthermore, the developed models have been validated on different device types, *i.e.* larger geometries as used in WP2 for RF-LDMOS and other device types. The other device types are SOI-LDMOS and GaN Schottky diodes. The S-parameter method for determining the thermal resistance has been used to characterize the thermal device properties. By making the appropriate changes in the device or thermal models in the models for the RF-power devices developed in WP2, accurate modelling of the SOI-LDMOS and GaN Schottky diodes was demonstrated.

# In conclusion, the measurable objective MO7.1.1 of validation of the thermal RF-LDMOS and GaN-HEMT models has been demonstrated in Section 2.2.1 (

Figure 2–Figure 5). The measurable objective MO7.1.2 of reusing and adapting the electrothermal models developed for RF-devices on other device types has been shown in Section 2.2.3 (Figure 17–Figure 23 and Figure 25–Figure 26), and the integration of the RF-LDMOS model into design tools and validation on large-signal application data (MO7.1.3) was demonstrated in Section 2.2.1 (Figure 7–Figure 9).

## 3 Verification of TCAD (SNPS-CH, together with IMC, IMEC, ST, NXP-D)

### 3.1 Introduction

This section reports about the verification of Technology CAD (TCAD) calibrated simulation decks that were developed in WP2 and WP6 by SNPS-CH with and for supporting different partners for studying thermal effects at the very low end of the abstraction hierarchy. The model details are described in the respective WP2 and WP6 deliverable reports.

TCAD simulation includes is the modelling of process steps (such as diffusion and ion implantation), and modelling of the electro-thermal behaviour of the devices based on fundamental physics, such as the doping profiles of the devices.

TCAD enables in-depth analysis of device behaviour, i.e. self-heating, that is relevant to modelling at higher levels of abstraction by running virtual experiments, and allows separation of physical effects that would not be possible with measurements only.

## **3.2** Verification of TCAD Models and Methodologies

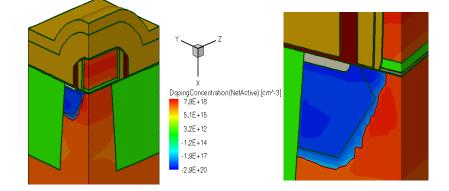

#### 3.2.1 Bulk CMOS 3D TCAD Model

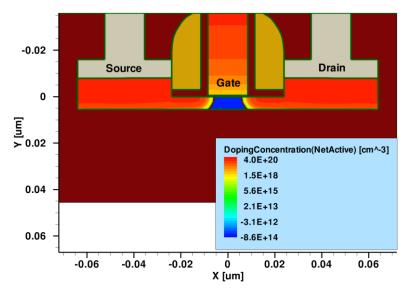

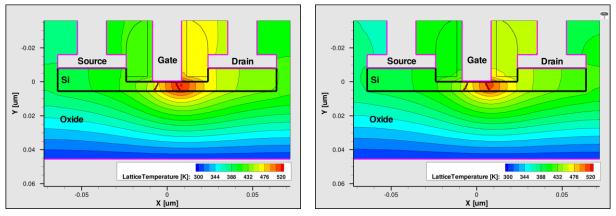

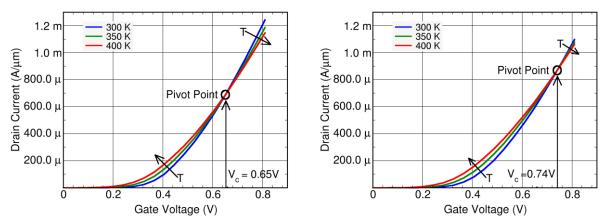

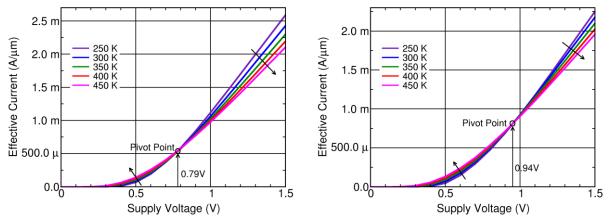

We report about the verification of a 3D TCAD model (Figure 27) for advanced (28/32nm) bulk CMOS technology developed in WP2 and described in detail in D2.1.5. The model was developed with partner IMC technology and measurement / compact model data.

Figure 27: Snapshot showing a 3D pMOS transistor. A zoom on the SiGe pockets of the device is shown in the right picture.

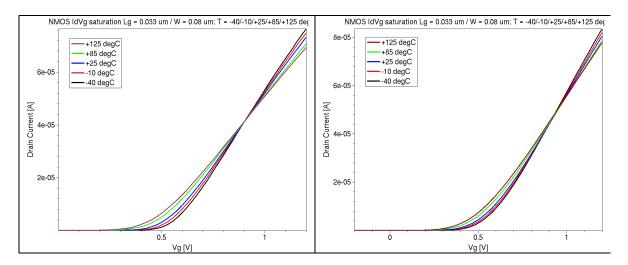

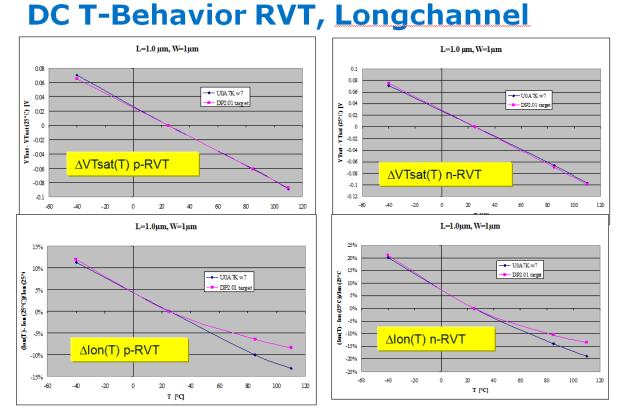

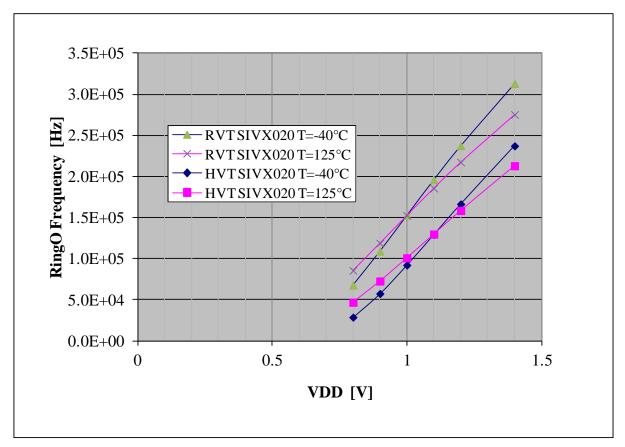

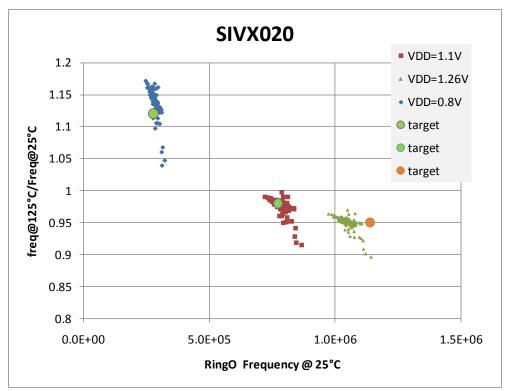

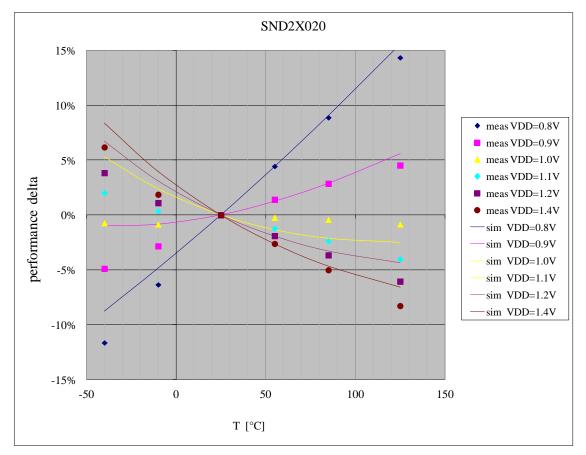

The measureable objective MO7.1.5:

Calibration against available experimental / compact model data within 20% for saturation regime threshold voltages and saturation on–currents, and to obtain the right trends with regard to temperature variation.

was fully achieved for NMOS (10%), whereas for PMOS the accuracy achieved was Vtsat within 30%, Ion within 35%. However, for both NMOS and PMOS cases the Vtsat temperature trend (deltaVtsat/deltaT) is captured with an accuracy of better than 20%. In order to improve the PMOS absolute accuracy, more detailed process flow and geometry description need to be available. However, because of IMCs data and IP protection requirements neither device geometry information nor process flow description was available for this implementation.

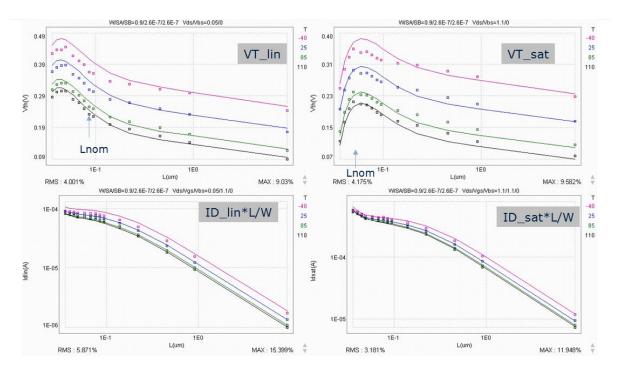

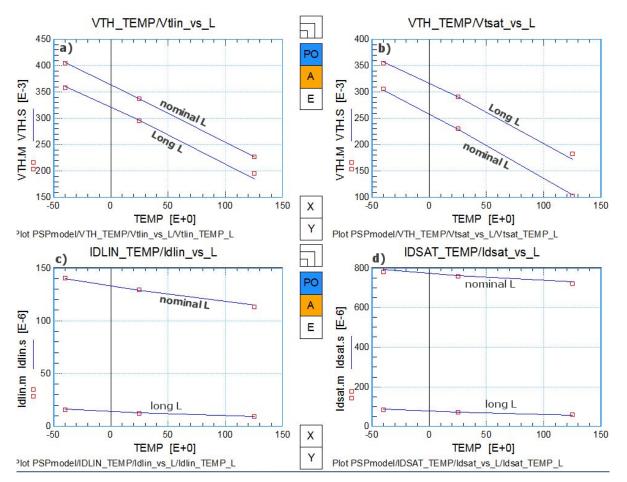

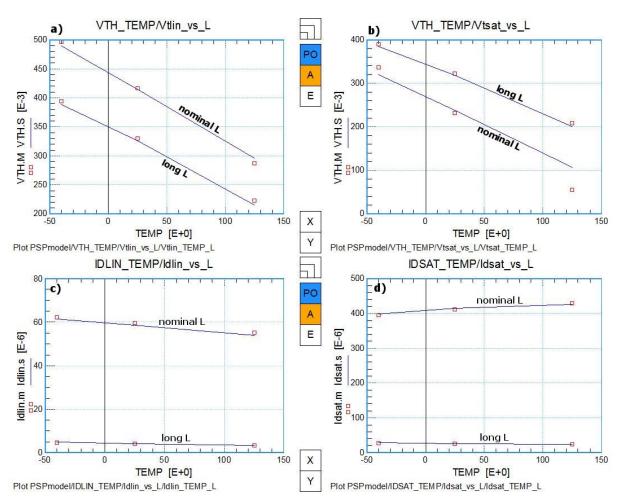

This is shown in Figure 28 and Figure 29 for the saturation on-currents, and in Figure 30 for the saturation regime threshold voltage Vtsat.

Figure 28: Comparison of the nMOS IdVg in saturation regime of the 3D TCAD model (left) with the data extracted from the compact model provided by IMC (right). The device geometry is L/W=33nm/80nm. The saturation on-currents agree within 10% over the temperature range from -40deg.C up to 125deg.C.

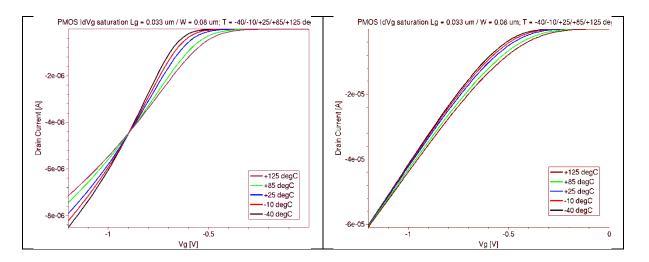

Figure 29: Comparison of the pMOS IdVg in saturation regime of the 3D TCAD model (left) with the data extracted from the compact model provided by IMC (right). The device geometry is L/W=33nm/80nm. The saturation on-currents agree only within 35% over the temperature range from -40deg.C up to 125deg.C. In particular, the crossing point at Vg = -1.2V is not well captured in the TCAD model.

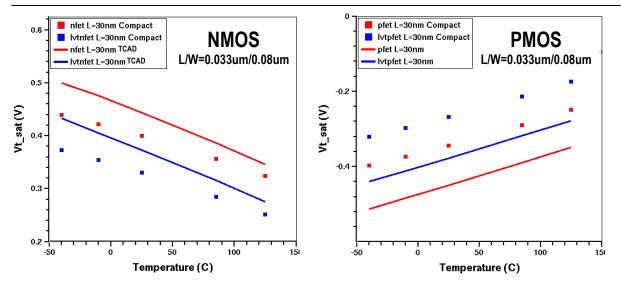

Figure 30: Saturation regime threshold voltage Vtsat temperature dependence of 3D TCAD model (solid lines) compared to data extracted from compact model provided by IMC (squares). The trends ( $dVt_sat/dT$ ) are correctly captured with an accuracy of <20% for both nMOS and pMOS cases, but in case of pMOS the absolute accuracy target of 20% was not achieved. Comparison for both regular (nfet, pfet) and low voltage (lvnfet, lvpfet) devices is shown.

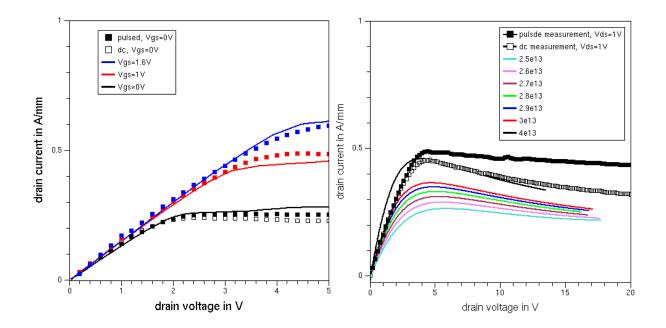

#### 3.2.2 GaN HEMT TCAD Model / Compact Model Parameter Extraction

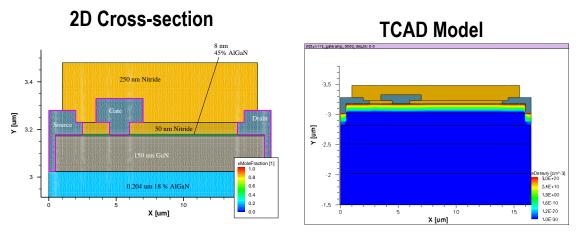

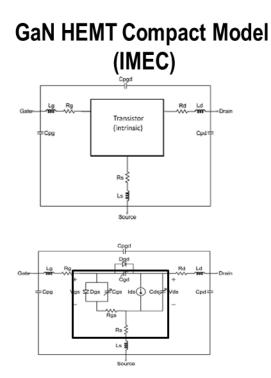

We report about the verification of our calibrated TCAD model (Figure **31**) and TCAD-based compact model parameter extraction methodology for discrete GaN HEMTs developed in WP2 and described in detail in D2.2.2, and about the comparison with measurement-based extraction done by IMEC. The GaN HEMT compact model itself (Figure **32**) was developed by IMEC.

Figure 31: 2D cross section sketch (right) and 2D TCAD model (left) of the GaN HEMT showing the electron density in on-state.

The measurable objective:

Model matches device data (error within 10%) for the maximum drain current in IdVd characteristics at different gate bias, and for drain current at max. drain bias, and for Rout at drain bias zero.

was achieved (Figure 33).

The compact model parameters extracted by IMEC give a very good agreement to measurement data. For the TCAD based extraction simulations with non-calibrated parameters are done to make the difference to the measured data larger. IMEC's parameters are taken as initial compact model parameters. After parameter extraction the compact model results based on the extraction of parameters done with TCAD match the TCAD simulation results.

Figure 32: GaN HEMT compact model provided by IMEC. Details are described in D5.1.1b.

Figure 33: TCAD model IdVd simulation results compared to measurement data provided by IMEC. The figure on the right shows the effect of self-heating (negative differential resistance) for Vgs=1V, and the effect of different AlGaN/GaN interface trap densities. Solid lines = TCAD, Symbols = measurement.

Figure 34: IdVd characteristics comparison. Vgs=1.6V.

#### 3.2.3 Si power MOSFET unit cell TCAD Model

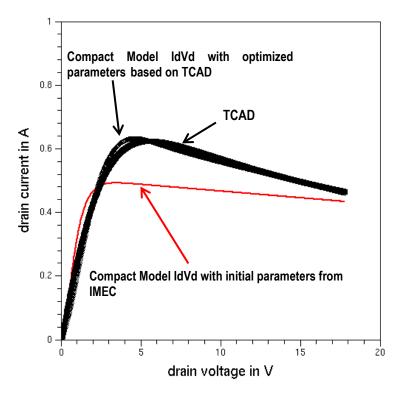

We report about the discrete power MOSFET TCAD unit cell model verification. The model was developed in WP2 with partner ST and its details are presented in D2.2.2.

The measurable objective MO7.1.4:

Model matches device data (error within 10%) for the maximum drain current in IdVd characteristics at different gate bias, and for drain current at max. drain bias, and for Rout at drain bias zero.

was essentially achieved.

Rout matches the reference data from ST mostly within an error < 10% in IdVd characteristics at different gate bias and temperatures (Figure **35**). Only at Vgs=10V and at the low temperatures boundary we were not able to meet the objective (<15%). In accordance

with partner ST we preferred to preserve predictability and consistency over the Vgs and temperature range, rather than do a "brute force" fitting to measurements.

The maximum drain current (Ids) objective was not applied to the power MOSFET TCAD model. The bias conditions for Ids@Vds=20V would correspond to an operating point well beyond static (and dynamic) safe operating area (SOA) for all Vgs>3V.

Figure 35 Top: 2D TCAD model of the power MOSFET unit cell.

Bottom: Measured (\_m) vs. Simulated (\_s) Rdson at two different Ids current values (Ids=10A, 80A) for Vgs=4.5V (left) and Vgs=10V (right), and temperatures -50C, 0C, 25C, 100C, 175C. Rdson (Rout) increases with temperature. The Inset shows the accuracy of TCAD with respect to measurement.

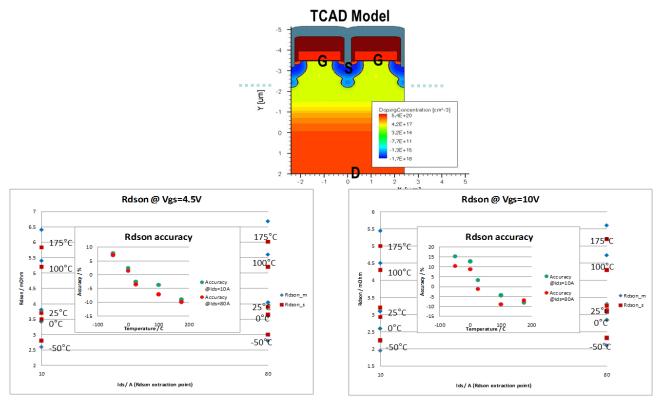

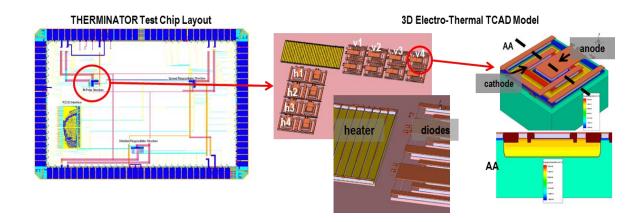

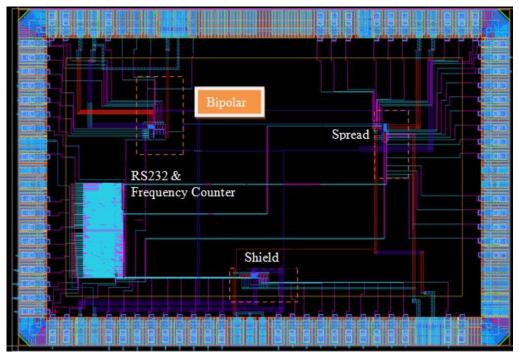

#### 3.2.4 3D TCAD Electro-Thermal Modeling Methodology

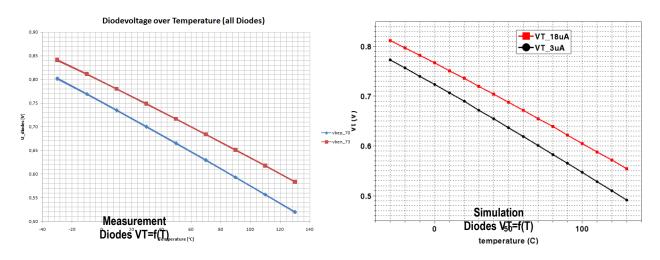

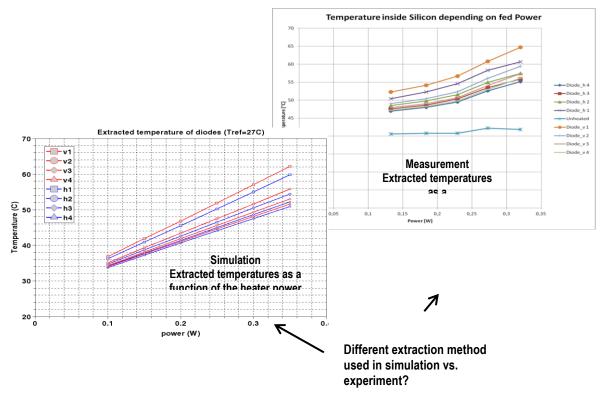

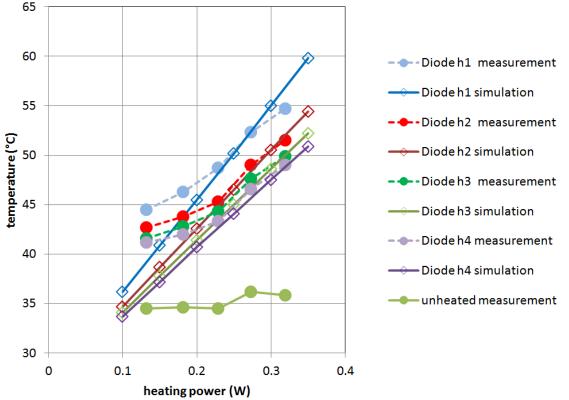

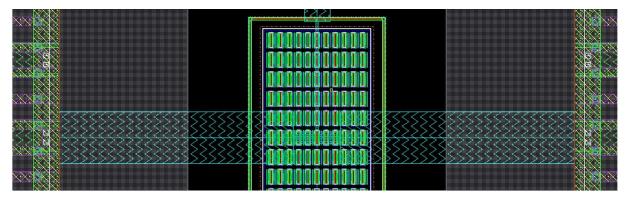

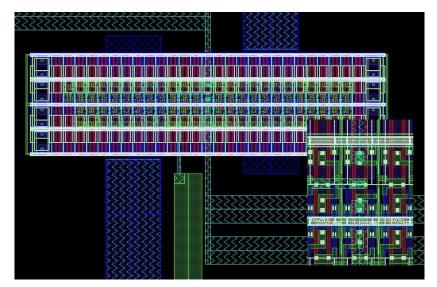

We report about the verification of the electro-thermal 3D TCAD Modeling Methodology for discrete devices developed in WP6 with partner NXP-D. The model details are presented in the deliverable report D6.1.1. The verification is performed against NXP test chip (

Figure 36) measurement data. We are focusing on the bipolar structure on the test chip (encircled red). The aim of the test structure is the monitoring of the silicon temperature by using sense diodes ("horizontal": h1,h2,h3,h4 and "vertical": v1,v2,v3,v4). The heat source is a transistor. The TCAD model details were set as follows in accordance with NXP information about test chip:

Silicon substrate = 300um STI = 0.4 um Tungsten via = 0.4 um Copper Line = 0.125 um Oxide passivation = 1.725 + 5 um Thermal conductivity: Silicon: 1.0/(0.03+1.56e-3xT+1.65e-6xT2) (=1.55 W.cm-1.K-1 at T=300K) Tungsten: 1.73 W.cm-1.K-1 Copper: 4.0 W.cm-1.K-1 Oxide: 0.014 W.cm-1.K-1

> Heat Capacity: Silicon: 1.63 J.cm-3.K-1 Tungsten: 2.55 J.cm-3.K-1 Copper: 3.45 J.cm-3.K-1 Oxide: 1.67 J.cm-3.K-1

Diodes and transistor are based on layout and doping information provided by NXP. Thermal boundary conditions are defined on top, bottom, and sides of the domain.

The measurable objective:

Model matches device data within 10%

was only partly achieved, as shown in

Figure 37, Figure 38, and Figure 39. Possible reasons for the discrepancy reported in Figure 38 and Figure 39 could be on one hand a different temperature extraction method used in the experiment with respect to TCAD that extracts the temperatures at steady-state (temperature of every diode is extracted by comparing the diode's voltage drop against voltage drop simulated with uniform temperature), and on the other hand parasitic effects not taken into account in TCAD. An evidence for the second hypothesis is shown in Figure 13, where simulation data and measurement results are shown in one picture. The measurement data has been shifted by 6 degrees downward. This value has been chosen so that the measurement where no heating was applied has the same temperature as in the simulations. A non-ideal layout, possibly due to the incorporation of a parasitic resistance far away from the heater and the surrounding probing diodes there might cause such an offset. Once subtracted from the measurement at high heating power. At lower heating power the slope of the measured curves becomes lower. It seems that in the real test chip this additional effect starts to dominate. This effect becomes smaller at higher heating powers

Figure 36: NXP test chip with transistor heater and various sensor elements for temperature sensing purpose (left part). 3D TCAD model of the heater and diode sensor elements (right part).

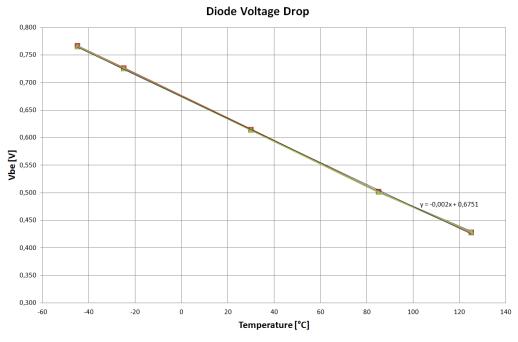

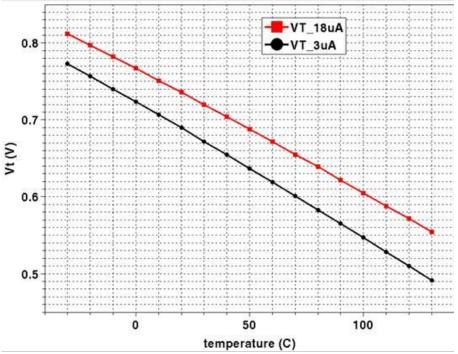

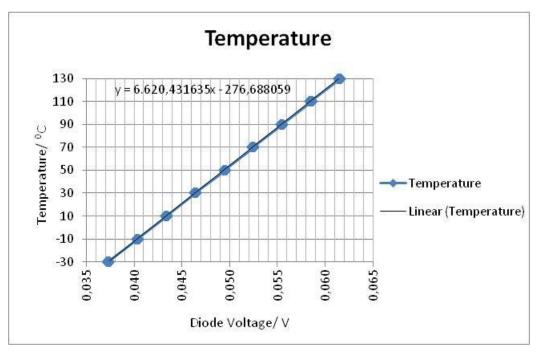

Figure 37: The average diodes voltage as a function of temperature extracted at two different forward current levels (top curve 18uA, bottom curve 3uA). Left: Measurement. Right: TCAD. Accuracy is better than 10%.

Figure 38: Temperature at different sensor locations (refer to

Figure 36) as a function of heater power. Left: TCAD simulation. Right: Measurement performed on test chip. TCAD shows a linear dependency on the power whereas the measurements show a non-linear behaviour that is hard to explain if one considers the linear relationship VT=f(T) shown in

Figure 37. The discrepancy may be attributed to a different extraction method in TCAD, where extraction at steady-state is performed, vs. experiment. On the other hand, the absolute temperature differences between the various sense diode positions (h1...h4, v1...v4) are correctly reproduced in TCAD.

Figure 39: Temperature at different sensor locations (refer to

Figure **36**) as a function of heater power. The filled circles indicate measurements negatively offset by 6 degrees and the open diamonds are simulation results. One can see that at lower heating powers the measurement data seem to converge to a fixed value. A parasitic effect due to a non-ideal layout could cause this behaviour. At higher heating powers the effect of heater starts to dominate and a good agreement between simulation and measurement can be observed.

#### 3.3 Conclusions

We have reported on the verification of various 2D and 3D electro-thermal TCAD models and modelling methodologies developed in work packages 2 and 6. The defined measurable objectives are essentially met. The cases where the defined objectives were not fully met are described in sections 3.2.1, 3.2.3, and 3.2.4.

## 4 Modelling and Simulation of discrete components for automotive (ST)

#### 4.1 Introduction

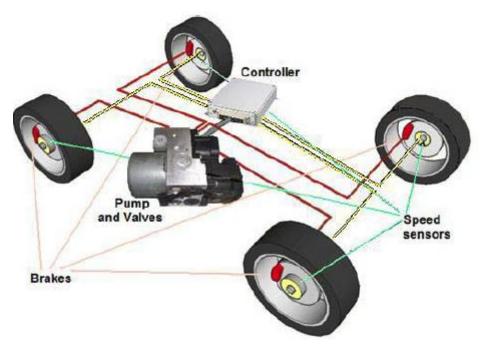

Nowadays electronics play a key role in the automotive sector; several equipments made in the past decades by pure mechanical parts now have been blurred with electronics. Amongst the most critical applications there is the Anti-lock Braking System (ABS) that in recent years, in several countries has become mandatory equipment on all new cars. The main objective of this device is to improve the safety of the vehicle by avoiding car skidding while braking and allows driver to maintain the directional control.

In Figure 40 the scheme of an ABS system with all its main parts is reported.

Figure 40 - ABS system basic scheme.

Featured elements are:

- Speed sensors, which allow detecting if any wheel is about to lock up.

- Valves, which allow controlling the fluid pressure in each brake line independently from the strength exerted on the brake pedal.

- Pump, which maintains constant the pressure in the brake system, compensating losses due to valves activation.

- Controller, which acts on the valves on the basis of information provided by speed sensors.

Since the pump represents a critical part of the system which needs to manage significant amounts of energy by adsorbing power peaks up to 1000W, the internal design of its

semiconductor power devices is very critical. The key device is a Power MOSFET expected to perform at least 60 millions of activations during its lifetime.

Once defined the typical working conditions for the device, a fundamental parameter that we will investigate in this context is the temperature variation  $\Delta T$  inside the silicon junction during a thermal cycle. It has been demonstrated that there is a strong relationship between  $\Delta T$  and the number of thermal cycle that the device could guarantee in its lifetime [1,2].

Several methods for measuring the thermal variation inside a discrete power device have been described in deliverable 5.1.2 and one of them has been used to retrieve a series of thermal measurements which will be used as reference data for the validation of the thermal simulation framework developed in work package 5. The main objective of this conclusive activity is to prove an error between thermal simulations and thermal measurements below 10% taking as device under investigation the discrete Power MOSFET already described in deliverable 1.1.2.

#### 4.2 Electrical operating conditions

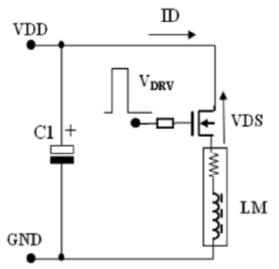

A simplified electrical scheme describing the operating configuration of the Power MOSFET has been reported in Figure 41.

Figure 41– ABS break pump test circuit

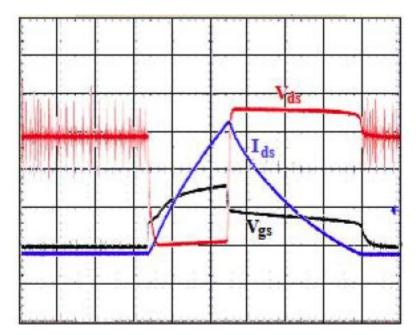

Typical electrical waveforms retrieved during a thermal cycle have been shown in Figure 42. As can be deduced from the waveforms reported in the picture, the power MOSFET device that is switching in linear operating condition must dissipate a significant amount of energy. This phenomenon will imply a considerable thermal impact that should be carefully taken into account by designers.  $V_{gs}$  profile well shows the behaviour described.

Figure 42 – Voltages and currents measurements during an inductive discharge. Vgs (5V/div), Vds (5V/div), and Ids (20A/div), time (400 us/div) during a cycle (down).

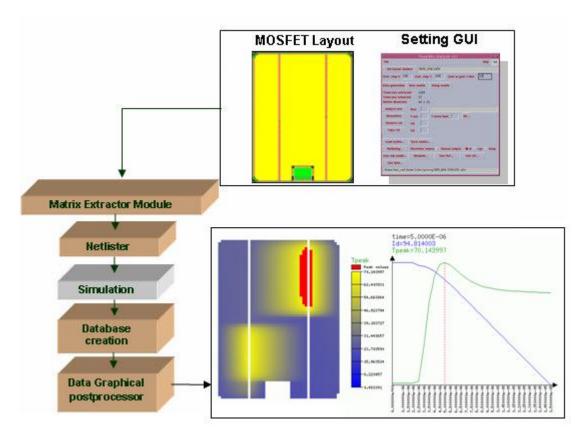

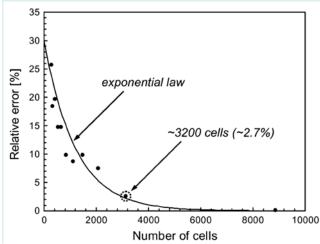

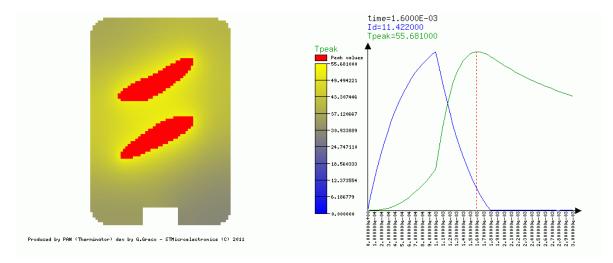

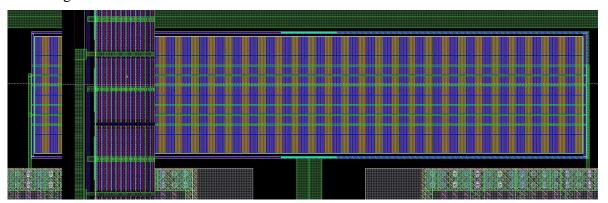

#### 4.3 Layout modelling and mapping

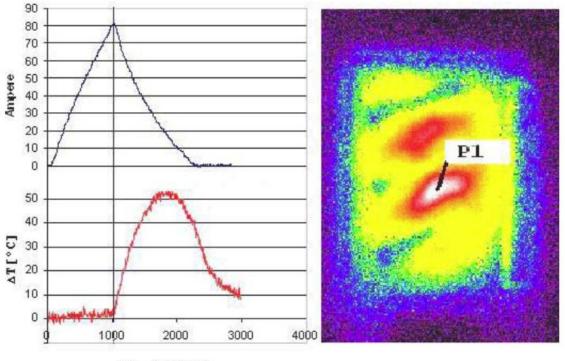

The measurement equipment used for retrieving temperature information has already described in deliverable 5.1.2 and is able to acquire thermal maps with a time resolution of 5us, more than enough for the test case under investigation.

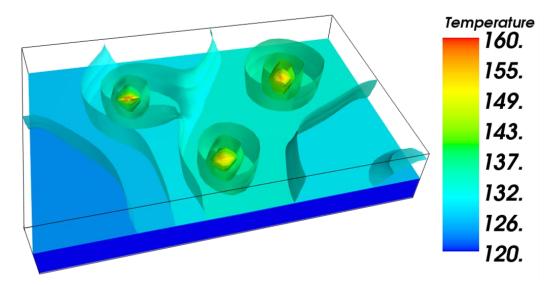

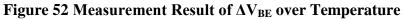

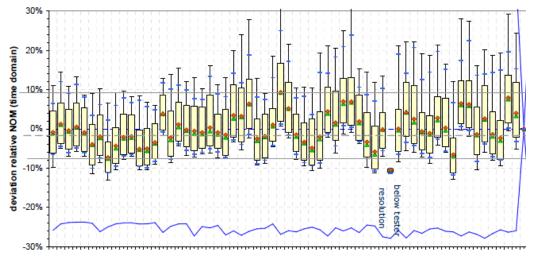

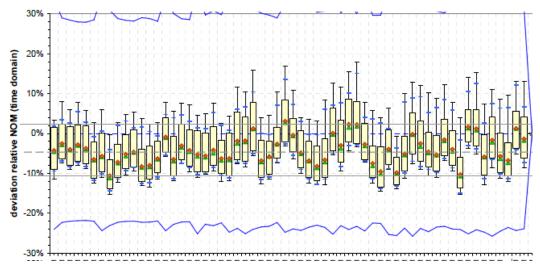

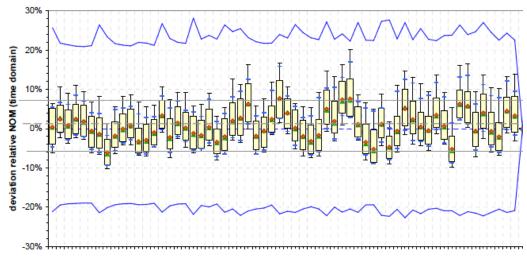

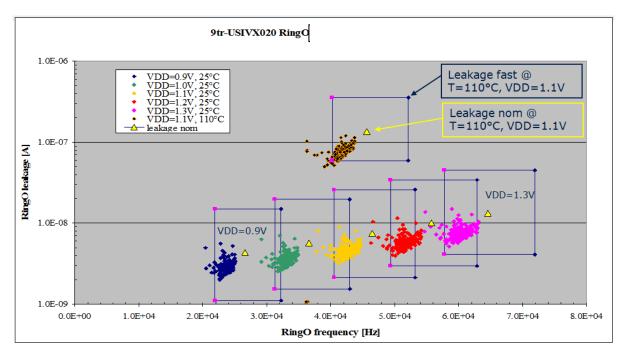

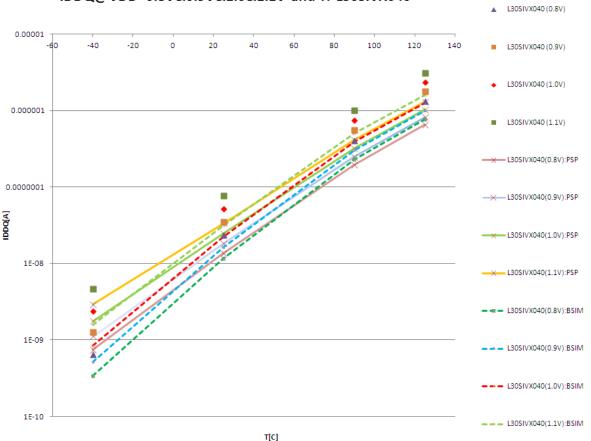

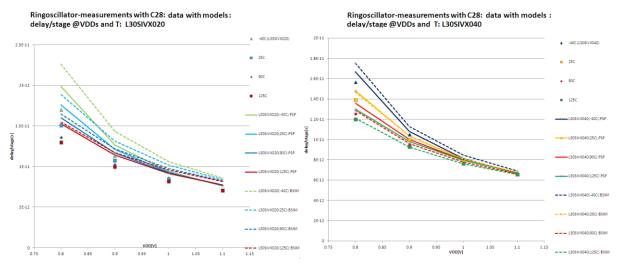

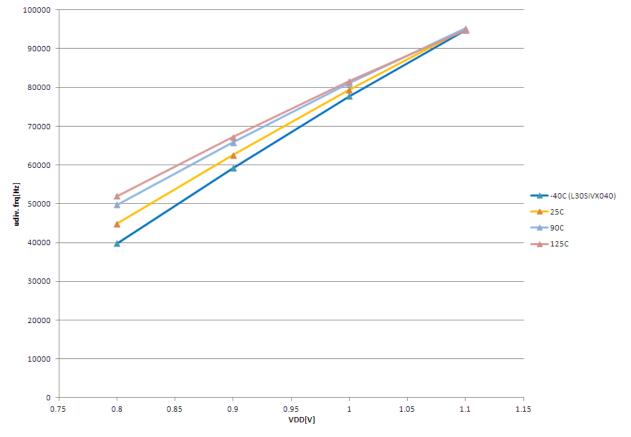

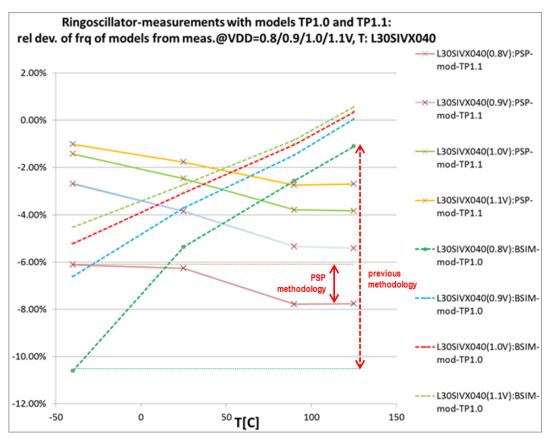

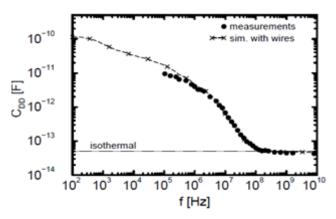

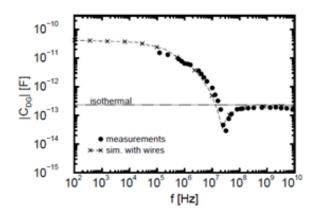

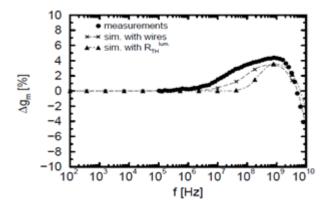

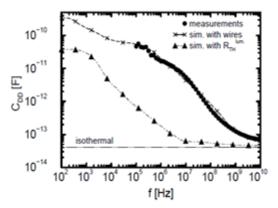

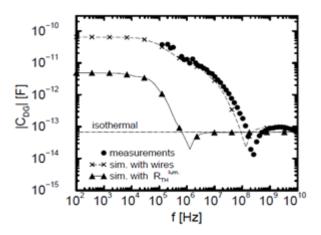

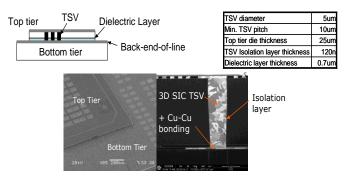

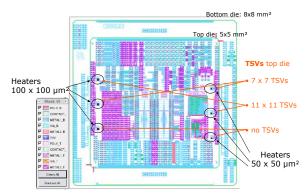

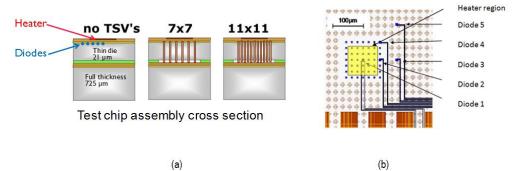

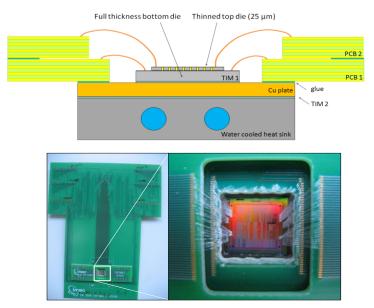

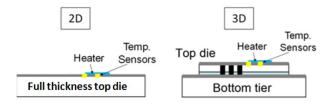

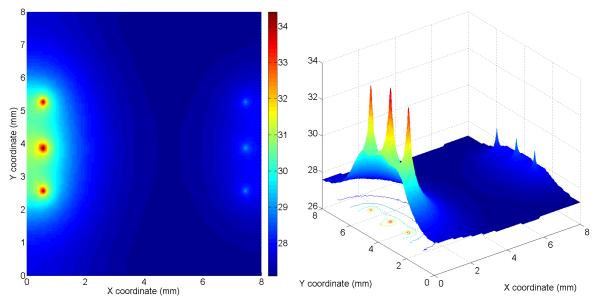

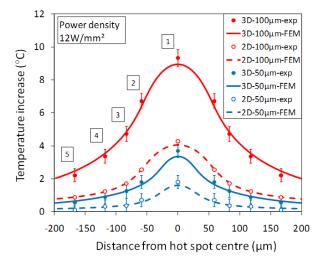

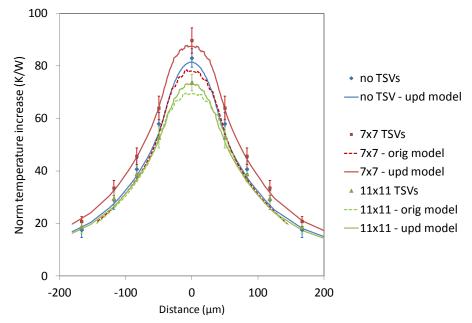

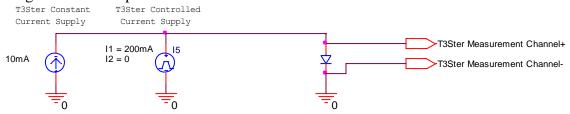

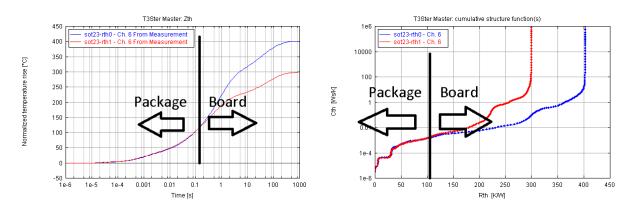

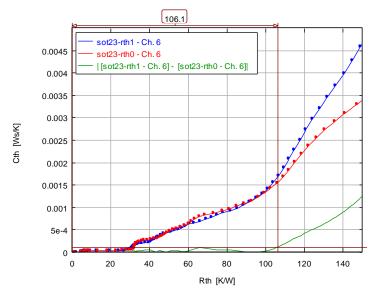

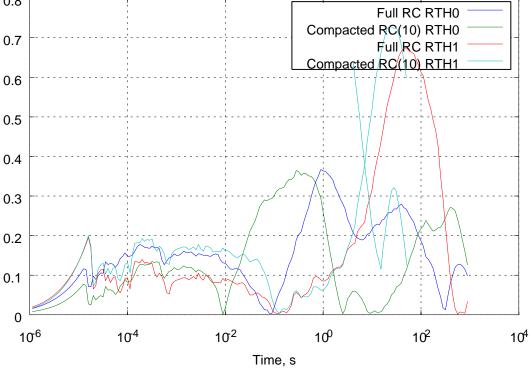

An acquisition of the temperature in a cycle under operating conditions described in the previous chapter has been reported in Figure 43 where a current peak of about 82A and a  $\Delta T$  peak of 53 °C have been recorded.