# **WiserBAN**

Project Acronym: WiserBAN

Project Title: Smart miniature low-power wireless microsystem for Body Area Networks

Call: FP7-ICT-2009-5, Collaborative project

**Grant Agreement no.:** 257454

**Project Duration:** 36 months

**Coordinator:** CSEM

#### **Beneficiaries:**

| CSEM Centre Suisse D'Electronique et de Microtechnique SA – Recherche et Development | CSEM       | СН |

|--------------------------------------------------------------------------------------|------------|----|

| Commissariat a L'Energie Atomique et aux Energies Alternatives                       | CEA        | FR |

| Fraunhofer-Gesellschaft zur Foerderung der Angewandten Forschung E.V.                | FRAUNHOFER | DE |

| Valtion Teknillinen Tutkimuskeskus                                                   | VTT        | FI |

| Technische Universitat Berlin                                                        | TUB        | DE |

| Alma Mater Studiorum-Universita di Bologna                                           | UNIBO      | IT |

| Sorin CRM SAS                                                                        | SORIN      | FR |

| EPCOS SAS                                                                            | EPCOS      | FR |

| MED-EL Elektromedizinische Geraete GmbH                                              | MED-EL     | AT |

| Siemens Audiologische Technik GmbH                                                   | DE-SAT     | DE |

| Debiotech S.A.                                                                       | DEBIOTECH  | СН |

| SignalGenerix Ltd                                                                    | SG         | CY |

| RTD TALOS Ltd                                                                        | TALOS      | CY |

# WiserBAN

# Smart miniature low-power wireless microsystem for Body Area Networks

**Deliverable identifier:** D1.2

Deliverable title:-Final platform specification and architecture

Due date of deliverable: M16 (12/2011)

Actual submission date: M19 (03/2012)

Start day of project: 01/09/2010

**Duration:** 36 months

WP Number: WP 1 Scenarios, architecture & specifications

Organization name of lead partner for this deliverable (partner name): CSEM

Author(s): Erwan Le Roux, Jean-François Debroux

**Document Status:**

|    | Project funded by the European Commission within the Seventh Framework Programme Dissemination Level |   |  |

|----|------------------------------------------------------------------------------------------------------|---|--|

|    |                                                                                                      |   |  |

| PU | Public                                                                                               | X |  |

| PP | Restricted to other programme participants (including the Commission Services)                       |   |  |

| RE | Restricted to a group specified by the consortium (including the Commission Services)                |   |  |

| СО | Confidential, only for members of the consortium (including the Commission Services)                 |   |  |

# **Revision History**

| Version | Date          | Changed page(s) | Cause of change      | Partner |

|---------|---------------|-----------------|----------------------|---------|

| V0      | Feb14 2012    |                 | Creation             | CSEM    |

| V1      |               |                 | Pre-final version    | SORIN   |

| V2      | March 28,     |                 | Reviewed version,    | CSEM    |

|         | 2012          |                 | unified D1.2 vs D1.3 |         |

| V3      | April 9, 2012 |                 | Final review         | CSEM    |

|         |               |                 |                      |         |

|         |               |                 |                      |         |

|         |               |                 |                      |         |

Disclaimer: The information in this document is subject to change without notice. Company or product names mentioned in this document may be trademarks or registered trademarks of their respective companies.

# All rights reserved.

The document is proprietary of the WiserBAN consortium members. No copying or distributing, in any form or by any means is allowed without the prior written agreement of the owner of the property rights.

This document reflects the authors' view. The European Community is not liable for any use that may be made of the information contained herein.

# **Contents**

| E> | cecutive | Summary                                              | 8  |

|----|----------|------------------------------------------------------|----|

| 1  | Intro    | oduction                                             | 9  |

| 2  | Plat     | form hardware architecture                           | 10 |

|    | 2.1      | From scenarios to demonstrators                      | 10 |

|    | 2.2      | 3D SiP                                               | 12 |

|    | 2.3      | 2D SiP                                               | 13 |

|    | 2.4      | microSD SiP                                          | 14 |

|    | 2.5      | SiP IOs                                              | 16 |

|    | 2.5.     | 1 Common interface                                   | 16 |

|    | 2.5.     | 2 microSD SiP specific interface                     | 18 |

|    | 2.5.     | RF interfaces and 3D SiP specific antenna interface  | 18 |

|    | 2.6      | Generic design specifications                        | 20 |

|    | 2.6.     | 1 Temperature                                        | 20 |

|    | 2.6.     | 2 Voltage supplies                                   | 20 |

|    | 2.6.     | 3 Leakages                                           | 20 |

|    | 2.7      | Antennas                                             | 21 |

|    | 2.7.     | 1 Overview                                           | 21 |

|    | 2.7.     | 2 Active L-antenna to be mounted on 3D SiP           | 22 |

|    | 2.7.     | Agile slotted-dipole antenna to be mounted on 3D SiP | 24 |

|    | 2.7.     | 4 Passive microSDantenna                             | 25 |

|    | 2.7.     | 5 Passive antenna for cochlear implant               | 26 |

|    | 2.7.     | 6 Antenna for cardiac implant                        | 27 |

|    | 2.8      | Piezoelectric components                             | 28 |

|   | 2.8.1  | Ove      | erview                                     | 3 |

|---|--------|----------|--------------------------------------------|---|

|   | 2.8.2  | RF f     | Front-end filter                           | 3 |

|   | 2.8.3  | IF1      | filter                                     | 3 |

|   | 2.8.4  | BAV      | N resonator                                | õ |

|   | 2.8.5  | LF r     | esonator                                   | 3 |

|   | 2.9    | Radio Sy | stem-on-Chip                               | ) |

|   | 2.9.1  | Ove      | erview39                                   | ) |

|   | 2.9.2  | Tra      | nsceiver39                                 | ) |

|   | 2.9.3  | Con      | itroller42                                 | L |

|   | 2.9.4  | Digi     | ital peripherals42                         | 2 |

|   | 2.9.5  | Osc      | illator and clocks43                       | 3 |

|   | 2.10   | nvRAM .  | 45                                         | 5 |

|   | 2.11   | Power m  | nanagement                                 | õ |

|   | 2.11.  | 1 Ove    | erview                                     | 5 |

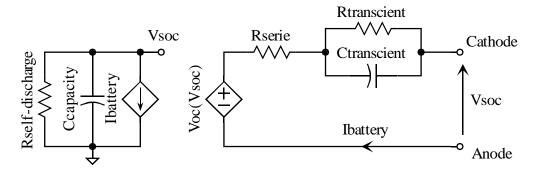

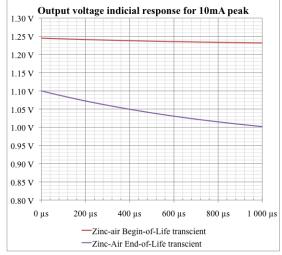

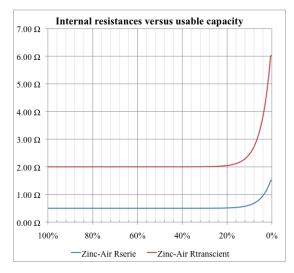

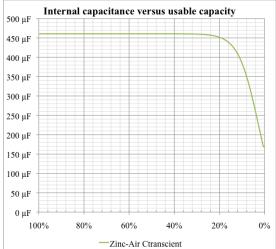

|   | 2.11.  | 2 Bat    | tery model47                               | 7 |

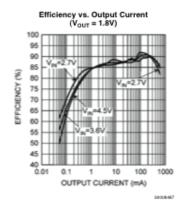

|   | 2.11.  | 3 1.08   | 8V to 1.32V primary voltage supply case 48 | 3 |

|   | 2.11.  | 4 2.7    | V to 3.63V primary voltage supply case48   | 3 |

|   | 2.11.  | 5 Rad    | lio SoC voltage reference49                | ) |

|   | 2.11.  | 6 Pov    | ver-on-Reset and EEPROM programming49      | ) |

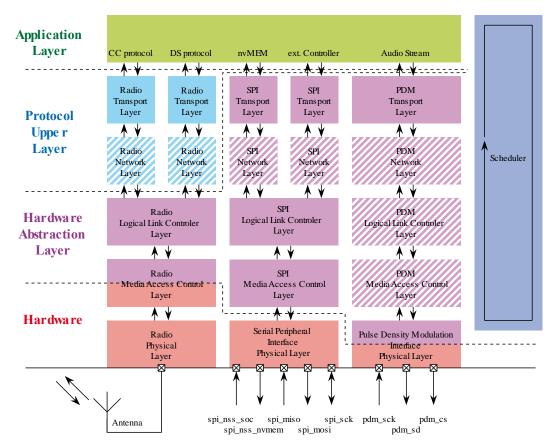

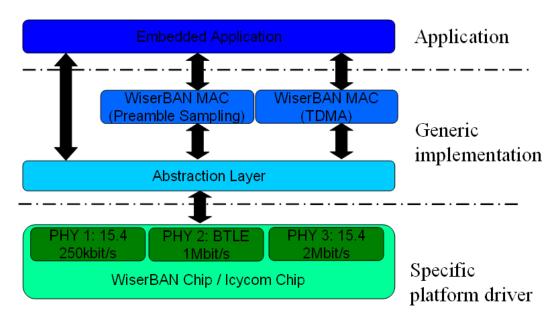

| 3 | Platfo | orm Soft | ware architecture50                        | ) |

|   | 3.1    | Overviev | v50                                        | ) |

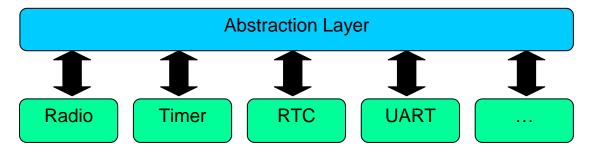

|   | 3.2    | Boot     | 51                                         | L |

|   | 3.3    | Hardwar  | re Abstraction layer 51                    | L |

|   | 3.4    | Radio Pr | otocol stack                               | L |

|   | 3.4.1  | Ove      | erview                                     | L |

|   | 3 4 2  | Ma       | dia Access Control laver                   | ) |

|            | 3.4.3      | Logical Link Control layer                     | . 55         |

|------------|------------|------------------------------------------------|--------------|

| 4          | Radio C    | ommunication                                   | . 57         |

| 4          | .1 Co      | mmunication range                              | . 57         |

|            | 4.1.1      | Overview                                       | . 57         |

| 4          | .2 Co      | mmunication latencies versus current tradeoff  | . 58         |

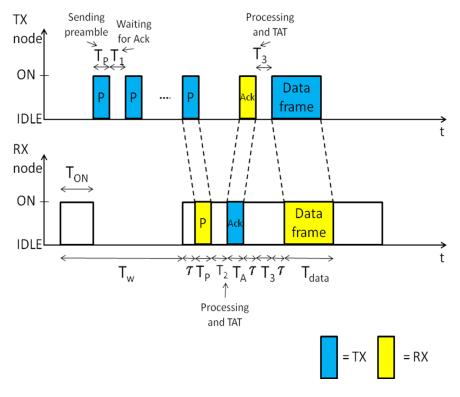

|            | 4.2.1      | Control-commands communication principle       | . 58         |

|            | 4.2.2      | Data-streaming type of communication principle | . 60         |

|            | 4.2.3      | Other important aspects                        | . 62         |

| <u>Anı</u> | nexes 1: I | EEPROM                                         | . 70         |

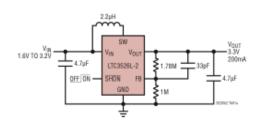

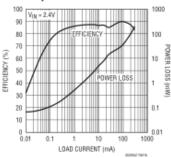

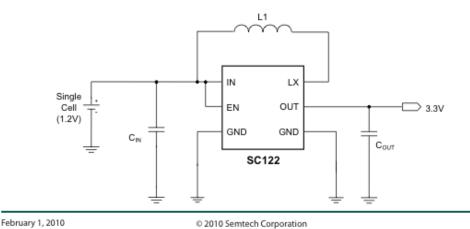

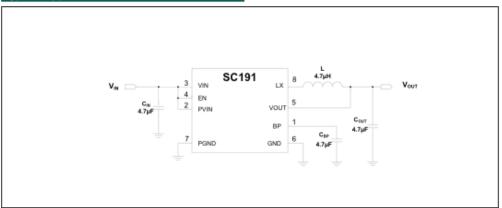

| Anı        | nexes 2: I | Boost DC-DC converter                          | . 71         |

| Anı        | nexes 3: I | Boost DC-DC converter                          | . 72         |

| Anı        | nexes 4: I | Buck DC-DC converter                           | . <b>7</b> 3 |

| Anı        | nexes 5: I | Buck DC-DC converter                           | . 74         |

| Anı        | nexes 6: I | Low-voltage LDO                                | . 75         |

| Anı        | nexes 7: I | Low-voltage LDO                                | . 76         |

| Anı        | nexes 8:   | Varactor                                       | . 77         |

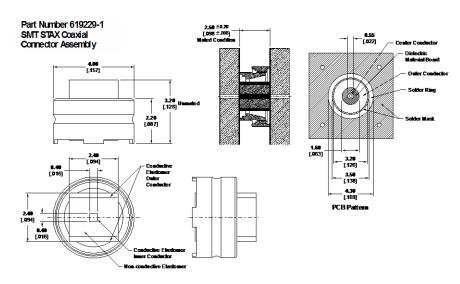

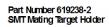

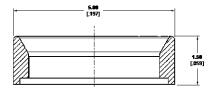

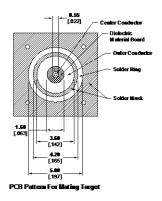

| <u>Anı</u> | nexes 11:  | Compression coax board-to-board STAX®          | . 81         |

| 1          | Transm     | ission                                         | . 82         |

|            | 1.1.1      | Channel requirements                           | . 82         |

|            | 1.1.2      | Channel parameters                             | . 83         |

| 1          | .2 Da      | ta rate                                        | . 83         |

|            | 1.2.1      | Data rate requirements                         | . 83         |

|            | 1.2.2      | Data rate parameters                           | . 84         |

| 1          | .3 Lat     | ency and delays                                | . 86         |

|            | 1.3.1      | Latency and delays requirements                | . 86         |

|            | 1.3.2      | Latency and delays parameters                  | . 86         |

|   | 1.4  | Net   | working                                    | 90  |

|---|------|-------|--------------------------------------------|-----|

|   | 1.4. | 1     | Networking requirements                    | 90  |

|   | 1.4. | 2     | Networking parameters                      | 92  |

|   | 1.5  | Link  | range                                      | 93  |

|   | 1.5. | 1     | Link range requirements                    | 93  |

|   | 1.5. | 2     | Link range parameters                      | 93  |

|   | 1.6  | Elec  | tromagnetic compatibility                  | 94  |

|   | 1.6. | 1     | Electromagnetic compatibility requirements | 94  |

|   | 1.6. | 2     | Electromagnetic compatibility parameters   | 95  |

| 2 | Sup  | ply   |                                            | 95  |

|   | 2.1  | Sup   | ply requirements                           | 95  |

|   | 2.2  | Sup   | ply parameters                             | 95  |

| 3 | Inte | rface | 2                                          | 99  |

|   | 3.1  | RF ii | nterface                                   | 99  |

|   | 3.1. | 1     | RF interface requirements                  | 99  |

|   | 3.1. | 2     | RF interface parameters                    | 101 |

|   | 3.2  | Syst  | em and interface                           | 102 |

|   | 3.2. | 1     | System and interface requirements          | 102 |

|   | 3.2. | 2     | System and interface parameters            |     |

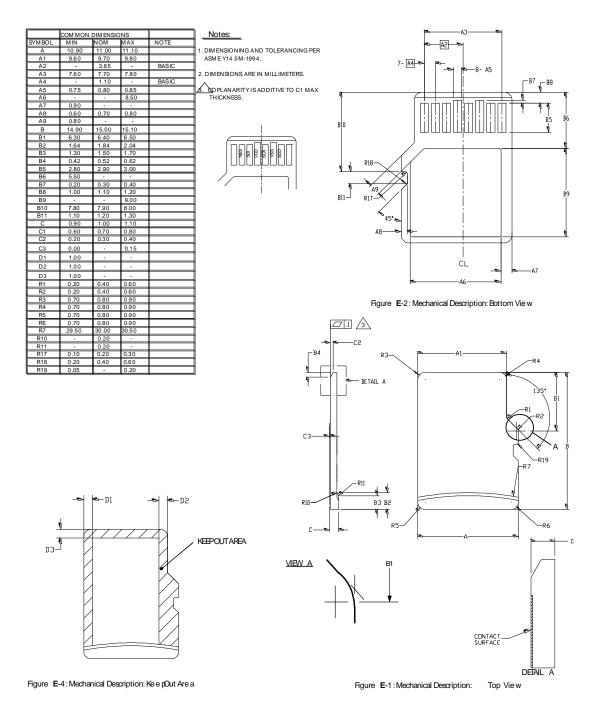

|   | 3.3  |       | chanical interface                         |     |

|   | 3.3. |       | Mechanical interface requirements          |     |

|   | 3.3. |       | Mechanical interface parameters            |     |

| 4 |      |       | nd reliability                             |     |

| 7 | 4.1  | -     | ility and reliability requirements         |     |

|   |      |       | , , ,                                      |     |

|   | 4.2  | Qua   | llity and reliability parameters           | ттт |

# **Executive Summary**

D1.2 is a deliverable from WP1 which is the workpackage that focuses on the selection and description of the platform applications which will be enabled by the WiserBAN BAN radio modules, on the derivation of the associated platform requirements, and on the definition of the radio system architecture.

In particular, D1.2 concerns Task 1.2 Platform architectures: the main objective of this task is to specify the requirements for the WiserBAN platform, based on the use cases derived in Task 1.1. In addition, other important requirements which are not directly related to the analysed applications may be considered here in order to maintain the generic character of the platform.

This formal deliverable "D1.2 Final platform specification and architecture" is the result of the evolution of the internal deliverable "IR1.2 Target radio platform and specification" that has evolved along the specification process up to be able to be delivered externally:

- The platform specification is derived from the use cases requirements and parameters that have been described in deliverable "D1.1 Report about WiserBAN platform applications". Details comments are associated to each particular demand in Annex 11. User point of view is described in the "IR1.1 (M4) Target platform specification and architecture" document and a more detailed designer point of view is described in this document.

- This document can be seen as a top-level PLATFORM specification. Detailed specifications for different sub-parts are associated to different specific documents to allow a distribution of specification work and update of those documents during the design.

### 1 Introduction

This formal deliverable "D1.2 Final platform specification and architecture" is the result of the evolution of the internal deliverable "IR1.2 Target radio platform and specification" that has evolved along the specification process up to be able to be delivered externally. As master specification of the platform, this document may still evolve to precise some points that have been considered unclear or to add some discovered points during the rest of the project.

The platform specification is derived from the use cases requirements and parameters that have been described in deliverable "D1.1 Report about WiserBAN platform applications". Details comments are associated to each particular demand in Annex 11. User point of view is described in the "IR1.1 (M4) Target platform specification and architecture" document and a more detailed designer point of view is described in this document.

This document can be seen as a **top-level PLATFORM specification**. Detailed specifications for different sub-parts are associated to different specific documents to allow a distribution of specification work and update of those documents during the design. This document is a readable, standalone and synthetic concatenation of the following sub-documents used the design teams on an internal basis:

- IR1.3 Target radio System-on-Chip architecture and specifications (CSEM), evolving to the D1.3 Final radio system architecture and specification.

- IM2.1 Target RF specifications (CSEM).

- IM2.2 RF\_IF\_MEMS Target Specs (CSEM).

- IM2.3 LF MEMS and Oscillator target specs (CSEM).

- IR3.2 Intermediate report on smart antenna-to-radio interface for the active tunable antenna (VTT).

- IR3.2 Intermediate report on smart antenna-to-radio interface for the active tunable antenna (VTT).

- IR4.1 Reconfigurable baseband and protocol draft architecture description (CEA).

- IR5.1 3D SiP platform architecture proposal (TUB).

- D6.1 Implementation of wearable and implantable BAN demonstrators (DE-SAT & SORIN)

Note that in case of inconsistency between those documents and this top-level specification, the correct values are the ones presented in the sub-part specification document listed above.

# 2 Platform hardware architecture

#### 2.1 From scenarios to demonstrators

For sake of clarification, the following terminology is used when discussing about the demonstrators:

- Scenarios (or use-cases), established in WP1: Deliverable "D1.1 Report about WiserBAN

platform applications" sketched several scenarios, among which four principal scenarios related

to the four industrial end-users: Audio case (SAT), Insulin pump case (DEBIOTECH), Cardiac

implant case (SORIN), cochlear implant (MEDEL).

- Demonstrator Platforms, to be realized in WP6: According to the DoW, there are two

demonstrator platforms, namely the "Wearable BAN demonstrator" and the "Implanted BAN

demonstrator". The former concentrates inputs related to the SAT and the DEBIOTECH

scenarios, the later towards the SORIN and the MEDEL scenario. The Demonstrator Platforms

collects the technology bricks from WP2 to WP5 and assembles them into prototypes for

validating and demonstrating the WiserBAN concepts.

At this stage, the precise architectural break-down of the demonstrator platforms needs yet to be defined, under the lead of the industrial end-user partners. For the sake of channelizing the discussions, the following table shows the relation between the two Demonstrator Platforms and the four principal end-user-driven Scenarios (or use-cases).

The color codes are the following:

## Blue is for the Wearable Demonstrator platform:

- Dark blue for the principal items of the demonstrator: this targets a full demonstration based on the complete set of building bricks from WiserBAN (SoC/SiP, antenna, protocol) jointly with other end-user components (housing, other chips, power-management, applicative software, etc).

- Light blue for secondary items of the demonstrator: this concerns only a "limited" validation with only selected building bricks:

### Purple is for the Implanted Demonstrator platform:

- **Dark purple** for the principal items of the demonstrator: this targets a full demonstration based on the complete set of building bricks from WiserBAN (SoC/SiP, antenna, protocol) jointly with other end-user components (housing, other chips, power-management, applicative software, etc).

- **Light purple** for secondary items of the demonstrator: this concerns only a "limited" validation with only selected building bricks.

| Demo.                                                                     | Scenario                            |                                              | Platform                                  |                          |                                      |                |  |  |

|---------------------------------------------------------------------------|-------------------------------------|----------------------------------------------|-------------------------------------------|--------------------------|--------------------------------------|----------------|--|--|

| Platform                                                                  | (use-case)                          | BAN node type                                | SiP Antenna                               |                          | Available<br>Supplies <sup>(2)</sup> | Used interface |  |  |

|                                                                           | Audio Case                          | Behind-The-Ear<br>Hearing Instrument         | 3D                                        | VTT active               | Zinc-air +                           | I2S, GPIO      |  |  |

|                                                                           | (SAT)                               | In-The-Ear Hearing Instrument <sup>(3)</sup> | 3D                                        | CEA Active               | Voltage step-up                      |                |  |  |

| Wearable                                                                  |                                     | Remote Control (1)                           | Micro                                     | SD card, see line at     | bottom of table                      |                |  |  |

| BAN demo                                                                  | Insulin Pump Case (DEBIOTECH)       | Insulin Pump <sup>(4)</sup>                  | 2D                                        | Debiotech                | Zinc-air +<br>2.3V                   | UART, GPIO     |  |  |

|                                                                           |                                     | Remote Control (1)                           | MicroSD card, see line at bottom of table |                          |                                      |                |  |  |

|                                                                           | Cardiac<br>Implant Case<br>(SORIN)  | Cardiac Pump                                 | 2D                                        | Sorin                    | Lithium +<br>Voltage step-down       | SPI            |  |  |

| Implanted                                                                 |                                     | Remote Control (1)                           | Micro                                     | SD card, see line at     | bottom of table                      |                |  |  |

| BAN demo                                                                  | Cochlear<br>Implant Case<br>(MEDEL) | Cochlear Implant (5)                         | <b>2</b> D                                | CSEM                     | Li-ion +<br>Voltage step-down        | 12, SPI        |  |  |

|                                                                           |                                     | Remote Control (1)                           | Micro                                     | SD card, see line at     | bottom of table                      |                |  |  |

| Both demo platforms MicroSD card Remote control for several Scenarios (1) |                                     | 2D                                           | CEA LETI passive                          | 2.0-3.6V + on-SiP<br>LDO | SPI                                  |                |  |  |

Table 1: Demo. platforms vs SiP type, antenna, supply and IOs. C.f. text above for color code.

#### **Notes:**

- 1. The remote control node is the same for all scenarios and demonstrators

- 2. The SiP necessitates a 1.2V±10% supply for its core and a max. 3.6V supply for its digital IOs. The voltage of this IOs voltage supply depends on the voltage supply of the circuitry connected to these digital IOs (e.g. 1.8 is the M95M01 EEPROM min. voltage supply).

- 3. The In-The-Ear platform case is redundant with the Behind-The-Ear demonstration platform for its functionality: its study is then limited to its dedicated antenna and propagation environment.

- 4. The budget link associated to the Insulin Pump is less constrained than the others. The product, with especially an embedded antenna, already exists: its study is then more theoretical and concentrated on the improvement in term of functionality and current consumption.

The Cochlear Implant platform case is redundant with the Behind-The-Ear demonstration platform for its functionality aspects: its study is then limited to its dedicated antenna and propagation environment.

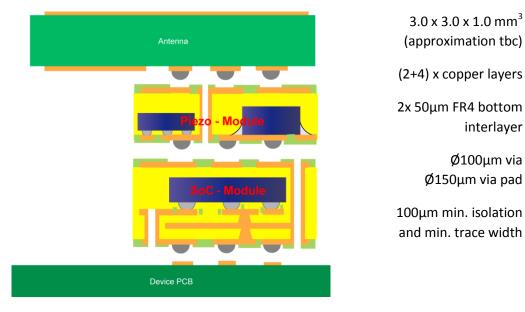

# 2.2 3D SiP

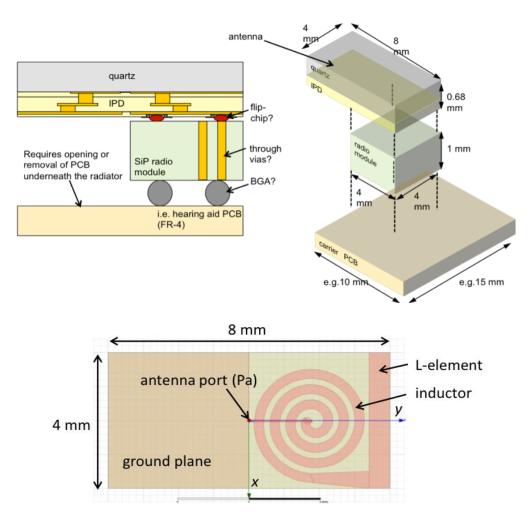

The 3D SiP try to reduce as much as possible the overall volume of the SiP.

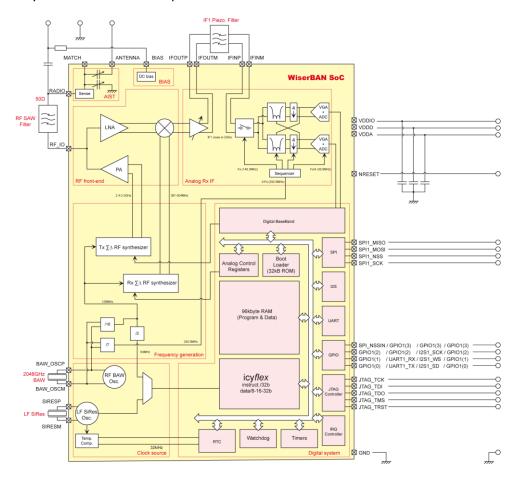

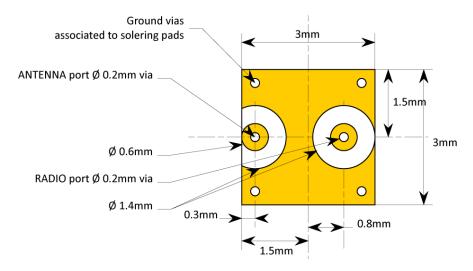

Figure 1: 3D SiP Schematic

Figure 2: 3D SiP layers stacking principle

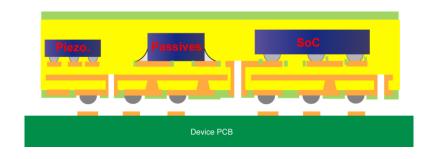

## 2.3 2D SiP

The 2D SiP try to reduce as much as possible the thickness of the SiP.

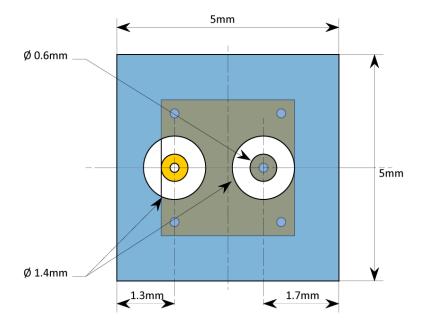

Figure 3: 2D SiP Schematic

5.0 x 3.5 x 0.8mm<sup>3</sup> (approximation tbc)

3x copper layers

2x 50µm FR4 interlayer

$Ø100\mu m$  via  $Ø150\mu m$  via pad

100µm isolation and min. trace width

Figure 4: 2D SiP layers stacking principle

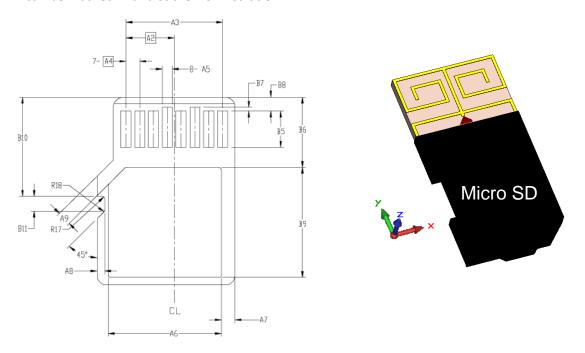

# 2.4 microSD SiP

The microSD SiP embed a complete RF modem including the antennain a microSD card.

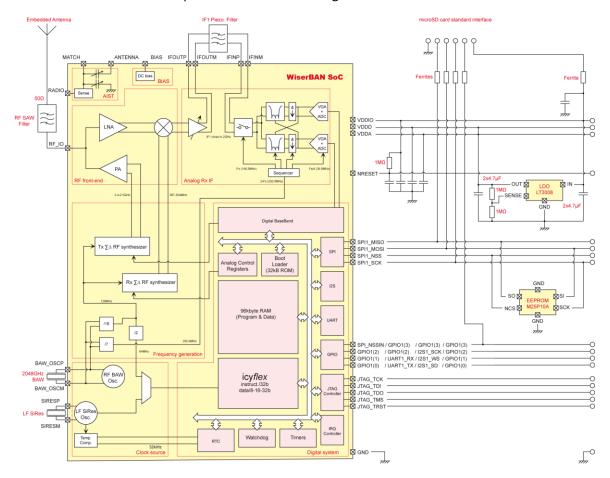

Figure 5: microSD SiP schematic

22.0 x 11.0 x 1.0mm<sup>3</sup>

4x copper layers

2x 50μm FR4 interlayer

Ø100μm via Ø150μm via pad

100µm isolation and min. trace width

Figure 6: microSD SiP layers stacking principle

The microSD card SiP supports the common SiP interface (described in section2.5) on one side for test and programming purpose together with a SPI interface to the SOC, mechanically and electrically compatible with standard microSD card SPI interface. Once programmed, the common SiP interface can be masked with a sticker for insulation.

Figure 7: microSD card mechanical description

The microSD card SiP embeds an antenna in the 11x7mm extension from the standard mechanical format (c.f. section 2.7.4 and annex 10). The host microSD cardholder necessitates then an opening in order to place this antenna extension out of the host case (e.g. smartphone).

## 2.5 SiP IOs

#### **2.5.1** Common interface

The electrical interfaces are described in the table below:

| Name      | I/O    | Description                                         |

|-----------|--------|-----------------------------------------------------|

| VDDA      | supply | Core analog positive voltage supply (1.2V±10%) (1)  |

| VDDD      | supply | Core digital positive voltage supply (1.2V±10%) (1) |

| VDDIO     | supply | Digital interface positive voltage supply (<3.6V)   |

| GND       | supply | Ground of the platform and negative voltage supply  |

| RADIO     | analog | Antenna port for 2D SiP, unused for other SiP       |

| NRESET    | in     | Platform reset, active low, pull-down by default    |

| JTAG_TCK  | in     | JTAG Test ClocK                                     |

| JTAG_TDI  | in     | JTAG Test Data Input                                |

| JTAG_TDO  | out    | JTAG Test Data Output                               |

| JTAG_TMS  | in     | JTAG test Mode Select                               |

| JTAG_TRST | in     | JTAG Test ReSeT, actif low                          |

| SPI1_NSS  | in     | SPI Not Slave Select of external used by bootloader |

| SPI1_SCK  | in-out | SPI Serial Clock                                    |

| SPI1_MOSI | in-out | SPI Master-Out Slave-In                             |

| SPI1_MISO | in-out | SPI Master-In Slave-out                             |

| GPIO1(3)  |        |                                                     |

| GPIO1(2)  | in out | General Purpose Input-Output, with multiplexed      |

| GPIO1(1)  | in-out | functionalities as described in the table below     |

| GPIO1(0)  |        |                                                     |

Table 1: List of supply and ports of the SiP.

1. Present on microSD card SiP interface but an implemented voltage regulator elaborates the VDDA and VDDD from VDDIO inside of microSD card SiP (become then output instead of input).

Different serial communication interfaces are multiplexed on the GPIO as describe in the table below:

| 10       | <b>SPI (</b> 11)        | <b>UART</b> (10) | <b>GPIO</b> <sup>2</sup> (00) |          |  |  |

|----------|-------------------------|------------------|-------------------------------|----------|--|--|

| GPIO1(3) | SPI1_NSSIN <sup>1</sup> | GPIO1(3)         |                               |          |  |  |

| GPIO1(2) | GPIC                    | 01(2)            | I2S1_SCK                      | GPIO1(2) |  |  |

| GPIO1(1) | GPIO1(1)                | UART1_RX I2S1_WS |                               | GPIO1(1) |  |  |

| GPIO1(0) | GPIO1(0)                | UART1_TX         | I2S1_SD                       | GPIO1(0) |  |  |

Table 2: description of multiplexed serial interface on GPIOs.

- 1. The SPI1\_NSSIN is used for SPI interface when SoC in slave mode.

- 2. GPIO is the «by default» functionality of the pad, each pad can be configured independently.

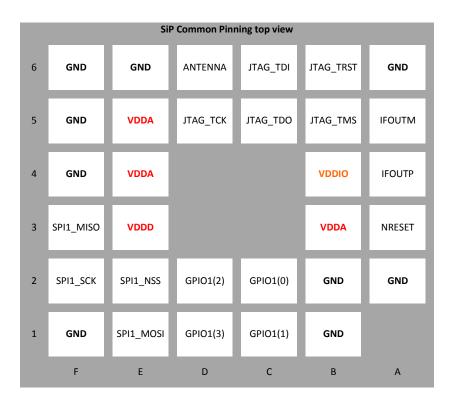

To facilitate the test of different SiP and use a common programming tool, they are all sharing a common interface with same "bottom" PCB footprint that is described below:

|   | SiP Common Pinning bottom view |           |          |          |           |           |

|---|--------------------------------|-----------|----------|----------|-----------|-----------|

| 6 | GND                            | JTAG_TRST | JTAG_TDI | ANTENNA  | GND       | GND       |

| 5 | IFOUTM                         | JTAG_TMS  | JTAG_TDO | JTAG_TCK | VDDA      | GND       |

| 4 | IFOUTP                         | VDDIO     |          |          | VDDA      | GND       |

| 3 | NRESET                         | VDDA      |          |          | VDDD      | SPI1_MISO |

| 2 | GND                            | GND       | GPIO1(0) | GPIO1(2) | SPI1_NSS  | SPI1_SCK  |

|   |                                |           |          |          |           |           |

| 1 |                                | GND       | GPIO1(1) | GPIO1(3) | SPI1_MOSI | GND       |

Table 3: SiP common interface pinning.

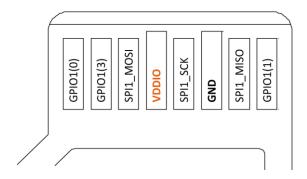

#### 2.5.2 microSD SiP specific interface

An additional interface part described below is added only on microSD card (in operation, a sticker to insulate the common interface may be needed):

Figure 8: microSD card SPI mode compatible interface (NSS on GPIO&(3)).

## 2.5.3 RF interfaces and 3D SiP specific antenna interface

## 2.5.3.1 For the 2D SiP

The RF interface is implemented as RADIO footprint pad on the "bottom" common interface described in preceding section 2.5.1. This is a  $50\Omega$  connection to an out-of-SiP antenna.

#### **2.5.3.2** For the 3DSiP

There are two possible active antennas described in section 2.7.2 and 2.7.3 that are mounted on "top" of SiP, i.e. at opposite side of "bottom" common interface described in preceding section 2.5.1. Because the two considered antennas are using different tuning scheme, they are connected to two different nodes of the SoC, the unused connection needing to remain unconnected on antenna side. A common physical bottom SiP interface is described below in Figure 9 below:

Figure 9: top 3D SiP interface to active antennas.

Note that attention has been paid to not miniaturize too much the RF interface in order to facilitate the testing (of SiP as well as antennas), for example with RF connector described in annexes 11.

Figure 10: example of antenna superposition with antenna bottom footprint.

# 2.5.3.3 For the microSD SiP

The RADIO pad of the "bottom" common interface described in preceding section 2.5.1 remained unconnected because the antenna is embedded into the SiP as described in the section 2.7.4. There is then no RF signal at SiP interface.

## 2.6 Generic design specifications

## 2.6.1 Temperature

Because the targeted applications are Body-Area-Network, the temperature range should be limited to commercial grade, i.e. **0°C to 60°C** range. But we also want to enlarge the possible application of the platform to Wireless-Sensor-Network type of applications. For this reason and even if exceptions are always possible to not overstress the design, we are targeting the industrial grade, i.e. the **-40°C to 85°C** range.

## 2.6.2 Voltage supplies

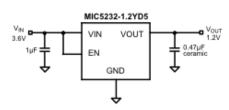

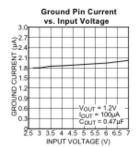

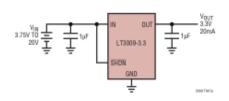

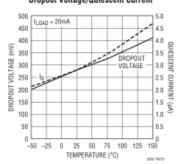

The 65nm CMOS core voltage is fixed to 1.2V±10%, i.e. in the **1.08V to 1.32V** range. This voltage range is well aligned with the voltage provided by Zinc-air type of battery. When possible (to not overstress the design), it is interesting to **note min. 0.9V compliance** for possible enlargement to alkaline cell type of supply. This voltage can be further referred as "low-voltage" or "SoC core" supply.

On one hand, the 65nm CMOS thick gate transistors for digital IOs can handle up to 3.3V+10%. On the other hand, for large choice of EEPROM (or sensor, controller, etc), it is interesting to maintain the IOs voltage above 2.7V (even if the chosen one for the microSD card is 1.8V compatible). The voltage range, also well aligned with primary lithium cell (i.e. Li-SOCl2 or Li-MnO2) is then **2.7V to 3.6V**. This voltage can be further referred as "high-voltage" or "SoC IOs" supply.

### 2.6.3 Leakages

Because of important leakage variations with respect to temperature and technological cases, we only consider typical cases at 25°C for leakages calculations.

For long-autonomy scenarios (e.g. cardiac implant), the current consumption in standby may outbalance the active current consumption because of very low activity duty cycling to achieve multivears of autonomy. For such applications a standby current in the order of  $1\mu$ A is typically needed. The 65nm CMOS technology has been chosen for best active current performances and miniaturization but it can, certainly in this first integration, induce higher leakage current because of non-optimized digital library and memory. A special mode with a complete platform supply disconnection controlled by an external controller would be needed to reduce the leakage current.

However, to anticipate the use of low-leakages libraries and SRAM, it is important to maintain the leakages of the designed analog blocs at a low level.

#### 2.7 Antennas

#### 2.7.1 Overview

Several antennas are considered depending on the physical dimensions of the demonstrator.

All considered antennas are small and then induce close to isotropic radiation pattern, not considering their environment.

For the tiniest antenna cases, because of the associated low bandwidth, impedance-tuning schemes have to be considered in order to re-align the optimum frequency and, in general, optimize the antenna efficiency.

The precise specifications of the different antennas are described in the "IR3.2 Intermediate report on smart antenna-to-radio interface for the active tunable antenna" document from which the formal deliverables of the project Documents D3.2 and D3.3 will be derived.

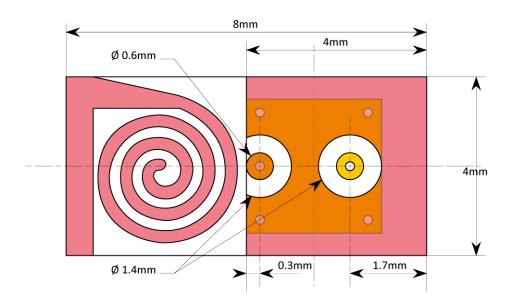

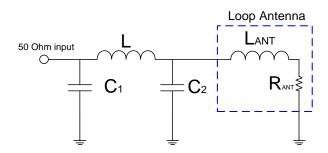

## 2.7.2 Active L-antenna to be mounted on 3D SiP

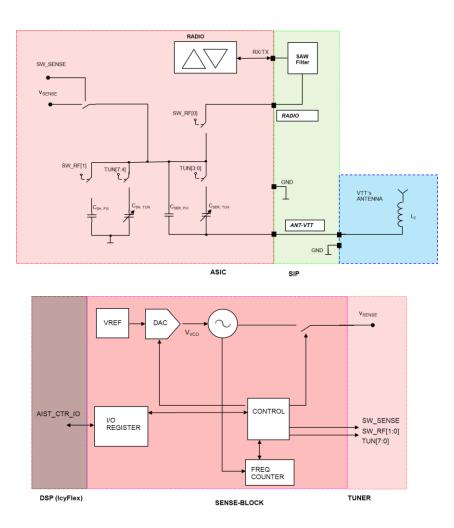

The active tuning scheme is implemented in the SoC, placed between the RF front-end SAW filter and the antenna. It involves digitally tunable serial capacitor and a sensing mechanism controlled via a SPI-like interface by the on-chip controller (i.e. software algorithm).

Figure 11: Active L-antenna

Typical specification are at 25°C, voltage supply=1.2V, unless otherwise noted.

| Parameter         | Test conditions, comments Min. Typ. Max U |           |           | Unit            |     |

|-------------------|-------------------------------------------|-----------|-----------|-----------------|-----|

| Antenna Frequency |                                           | 2400      | 2400 2484 |                 | MHz |

| Antenna Bandwidth | 50Ω matched, -10dB  s11                   |           | 10        |                 | MHz |

| Antenna Gain      | 50Ω matched, including losses             | -12       | -10       | -8              | dBi |

| Antenna size      |                                           | 8.0 x 4.0 |           | mm <sup>2</sup> |     |

| Antenna height    |                                           | 0.7       |           |                 | mm  |

**Table 4: Active L-antenna specifications**

Figure 12: Antenna tunable matching network and impedance sensing

Typical specification are at 25°C, voltage supply=1.2V, unless otherwise noted.

| Parameter              | Test conditions, comments            | Min. | Тур. | Max  | Unit |

|------------------------|--------------------------------------|------|------|------|------|

| Voltage supply         |                                      | 1.08 | 1.2  | 1.32 | V    |

| Fixed capacitance      | Shunt capacitor (C <sub>SH</sub> )   |      | 0.41 |      | pF   |

| Tuning step            |                                      |      | 0.10 |      | pF   |

| Max. capacitance       |                                      |      | 5.60 |      | pF   |

| Fixed capacitance      |                                      |      | 1.05 |      | pF   |

| Tuning step            | Serial capacitor (C <sub>SER</sub> ) |      | 0.21 |      | pF   |

| Max. capacitance       |                                      |      | 4.20 |      | pF   |

| Capacitor Q value      |                                      |      | 270  |      |      |

| RF switch Ron          |                                      |      |      | 1    | Ω    |

| Sensing active current |                                      |      | 1    |      | mA   |

| Sensing leakages (2)   | Including tuned capacitors           |      |      | 1    | nA   |

**Table 5: Active L-antenna specifications**

Note that the active tuning scheme is described in the "IR3.2 Intermediate report on smart antennatoradio interface for the active tunable antenna" Document.

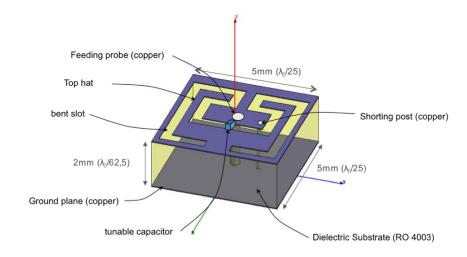

#### 2.7.3 Agile slotted-dipole antenna to be mounted on 3D SiP

This antenna is the tinier antenna.

The agility scheme involves a discrete varactor, such as the one described in the annex 8, implemented directly on the antenna and an associated DC biasing voltage introduced via the antenna feed interface.

Figure 13: Agile slotted-dipole antenna

Typical specification are at 25°C, voltage supply=1.2V, unless otherwise noted.

| Parameter             | Test conditions, comments      | Min. | Тур.      | Max  | Unit            |

|-----------------------|--------------------------------|------|-----------|------|-----------------|

| Antenna Frequency (1) |                                | 2400 |           | 2484 | MHz             |

| Antenna Bandwidth     | 50Ω matched, -10dB  s11        |      | 10        |      | MHz             |

|                       | Without considering ground     |      |           |      |                 |

|                       | plane extension in antenna     |      | 1         |      |                 |

| Total efficiency      | integration and the human      |      |           | %    |                 |

|                       | body effect                    |      |           |      |                 |

|                       |                                |      |           |      |                 |

|                       | 50Ω matched, included losses   |      |           |      |                 |

| Antenna Gain          | and without considering        |      | -17.7     |      | dBi             |

|                       | human body effects             |      |           |      |                 |

| Tuning active current | 1μA DC leakages at RF port     |      |           | 10   | μΑ              |

|                       | Estimation from simulation     |      |           |      |                 |

| Voltage control       | results and varactor datasheet | 1    |           | 2    | V               |

|                       | (by step of 0.02V)             | 1    |           | 2    | V               |

|                       |                                |      |           |      |                 |

| Antenna size          |                                |      | 5.0 x 5.0 |      | mm <sup>2</sup> |

| Antenna height        |                                |      | 2         |      | mm              |

Table 6: Agile slotted-dipole antenna specifications

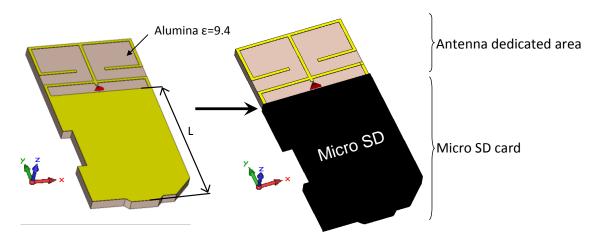

# 2.7.4 Passive microSDantenna

The preliminary design of the passive antenna is a folded T-shaped monopole antenna as shown in the figure 4. It is designed to be integrated on  $11 \times 7 \times 1 \text{ mm}^3$  micro SD extension.

Figure 14: Preliminary design of the passive antenna

| Parameter             | Test conditions, comments                                              | Min. | Тур.       | Max  | Unit            |

|-----------------------|------------------------------------------------------------------------|------|------------|------|-----------------|

| Antenna Frequency (1) |                                                                        | 2400 |            | 2484 | MHz             |

| Antenna Bandwidth     | 50 $\Omega$ matched, -10dB  s11                                        |      | 35         |      | MHz             |

| Antenna Gain          | $50\Omega$ matched, including losses For L=15mm (micro SD card length) |      | 0          |      | dBi             |

|                       | For L=3mm                                                              |      | -4         |      |                 |

|                       | For L=15mm                                                             |      | 63         |      | _,              |

| Total efficiency      | For L=3mm                                                              |      | 25         |      | %               |

| Antenna size          |                                                                        | -    | 11.0 x 7.0 | 0    | mm <sup>2</sup> |

| Antenna height        |                                                                        |      | 1          |      | mm              |

**Table 7: Passive antenna specifications**

The results presented in this table do not consider the Micro-SD antenna insertion into the remote control

# 2.7.5 Passive antenna for cochlear implant

This antenna is large but need to be extremely flat because implanted between the skull and the skin. The very special environment needs to be taken into account in order to maximize the RF power radiated to the outside of the body.

Figure 15: Passive cochlear implant antenna

| Parameter         | Test conditions, comments             | Min. | Тур.    | Max  | Unit            |

|-------------------|---------------------------------------|------|---------|------|-----------------|

| Antenna Frequency |                                       | 2400 |         | 2484 | MHz             |

| Antenna Bandwidth | 50 $\Omega$ matched, -10dB $ s11 $    |      | 210     |      | MHz             |

| Antenna Gain      | 50 $\Omega$ matched, including losses |      | -0.1    |      | dBi             |

| Antenna size      |                                       |      | 28 x 28 |      | mm <sup>2</sup> |

| Antenna height    |                                       |      | 3.8     |      | mm              |

Table 8: Passive cochlear implant antenna specifications

Because the antenna alone impedance is quite low, a matching network is necessary between the SoC with a  $50\Omega$  interface and the antenna. To obtain a wide enough bandwidth, a  $\Pi$  network is proposed as described in the Figure 16 below:

Figure 16: Proposed ∏ impedance matching network

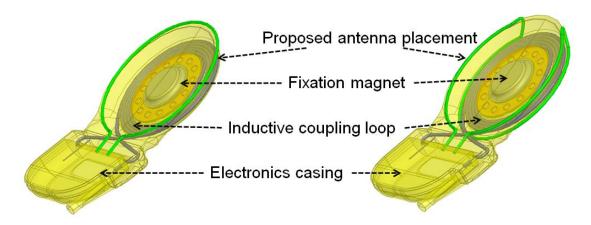

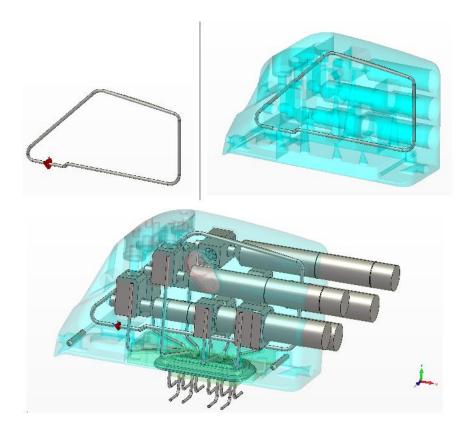

# 2.7.6 Antenna for cardiac implant

This antenna is the bigger antenna but need to be installed outside the cardiac implant titanium package, inside the connector's head. The very special environment with metal parts needs to be taken into account in order to maximize the RF power radiated to the outside of the body. Because of compatibility with MICS standard (402-405 MHz) this antenna is dual band. However, in WiserBAN, only the 2.4-2.5 GHz band will be used and is specified here.

This antenna is not developed in WiserBAN project: existing design isreused. Antenna characteristics are given below for information.

Figure 17: Cardiac implant passive antenna

Picture shows loop antenna (top left), loop antenna in plastic molding (top right) and complete assembly including cardiac probes metal inserts (bottom).

| Parameter         | Test conditions, comments              | Min. | Тур.   | Max  | Unit            |

|-------------------|----------------------------------------|------|--------|------|-----------------|

| Antenna Frequency |                                        | 2400 |        | 2500 | MHz             |

| Antenna Bandwidth | 50 $\Omega$ matched, -10dB $ $ s11 $ $ |      | 40     |      | MHz             |

| Antenna Gain      | 50 $\Omega$ matched, including losses  | -6.6 |        | +2.7 | dBi             |

| Antenna size      |                                        |      | 10 x 4 |      | mm <sup>2</sup> |

| Antenna height    |                                        |      | <1     |      | mm              |

Table 9: Cardiac implant passive antenna specifications

# 2.8 Piezoelectric components

#### 2.8.1 Overview

The precise specifications of the different piezoelectric components are described in the "IM2.2 Internal Milestone: RF, IF MEMS Target specifications" and "IM2.3 Internal Milestone: LF MEMS and oscillator target specifications" documents from which the D2.2 and D2.3 prototypes as deliverables of the project will be derived.

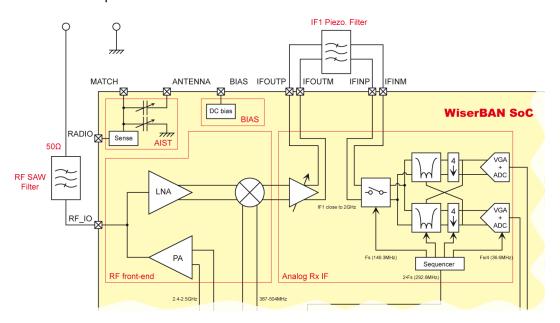

#### 2.8.2 RF front-end filter

The front-end filter is a SAW filter realizing a filtering between the antenna and the transceiver. In transmission, this filter reduces the output level of harmonics at multiples of the RF frequency. In reception, more importantly, it reduces the level of out-of-band interferer reducing the probability of jamming and then improving the quality of service. This filtering is especially important because the low current consumption is obtained with linearity tradeoff in the receiver chain that may make the receiver more sensitive to strong interferers.

Figure 18: transceiver signal paths

Two different filters are required to cover the full range of applications. One standard filter will cover the 2.4 to 2.4835 GHz ISM band while the other one will cover the 2.483 to 2.5 GHz

## 2.8.2.1 2.4 – 2.4835 GHz RF Front end filter

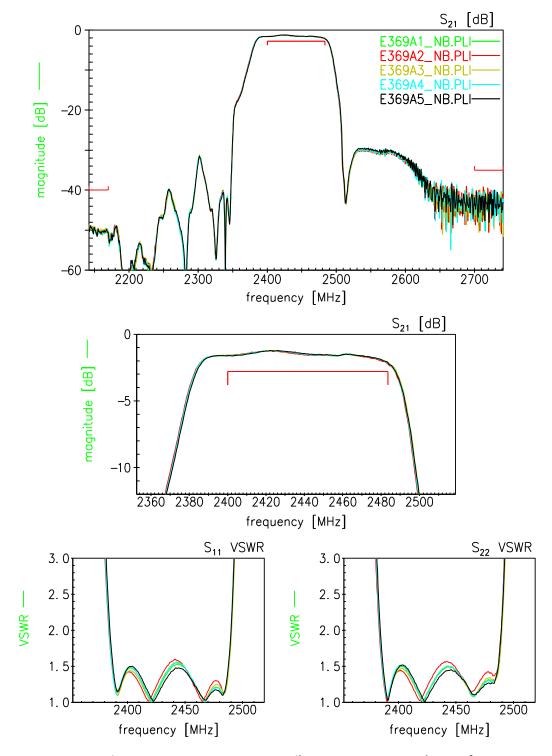

This filter (EPCOS reference E369A) is intended to reject the out of band strong interferers especially from the 1.8 GHz and 2.5 GHz bands.

|                                                  | Specifications E369A        |         |      |      |

|--------------------------------------------------|-----------------------------|---------|------|------|

| Parameter                                        | Min.                        | Тур.    | Max. | Unit |

| Operating temperature range                      | 0                           | -       | 60   | °C   |

| Center Frequency                                 | -                           | 2441.75 | -    | MHz  |

| Passband Width                                   | 83.5                        | -       | -    | MHz  |

| Max Insertion Loss over 83.5 MHz band @ Fc       | -                           | 2.2     | 2.8  | dB   |

| Relative attenuation                             |                             |         |      |      |

| 880 - 960 MHz                                    | 40                          | 43.5    | 1    | dB   |

| 960 - 1800 MHz                                   | 34                          | 42      | 1    | dB   |

| 2110 - 2170 MHz                                  | 40                          | 47      | -    | dB   |

| 2700 - 2800 MHz                                  | 35                          | 39      | 1    | dB   |

| 3600 - 5000 MHz                                  | 28                          | 44      | -    | dB   |

| Amplitude Ripple over 83.5 MHz band @ Fc         | -                           | 1.0     | 2.0  | dB   |

| Input V.S.W.R. over Passband                     | -                           | 1.5     | 2.0  |      |

| Output V.S.W.R. over Passband                    | -                           | 1.5     | 2.0  |      |

| Source Impedance (single - no external matching) | -                           | 50      | -    | Ω    |

| Load Impedance (single - no external matching)   |                             | 50      | -    | Ω    |

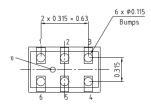

| Package size                                     | DSSP 0.95 x 0.6 mm (CBT06A) |         |      |      |

| Package height                                   | 0.2 mm + 0.085 mm (bumps)   |         |      |      |

Pinout configuration:

Input:1

Output: 4

To be grounded: 2, 3, 5, 6

Table 10: 2.4-2.4835GHz RF Saw Filter specification

Figure 19: 2.4-2.4835GHz RF Saw Filter measurement results at 25°C

Note that the 2.4835-2.5GHz band is not covered even if the associated losses should be limited and should make the wiserband system functional over the 2.4835-2.5GHz band.

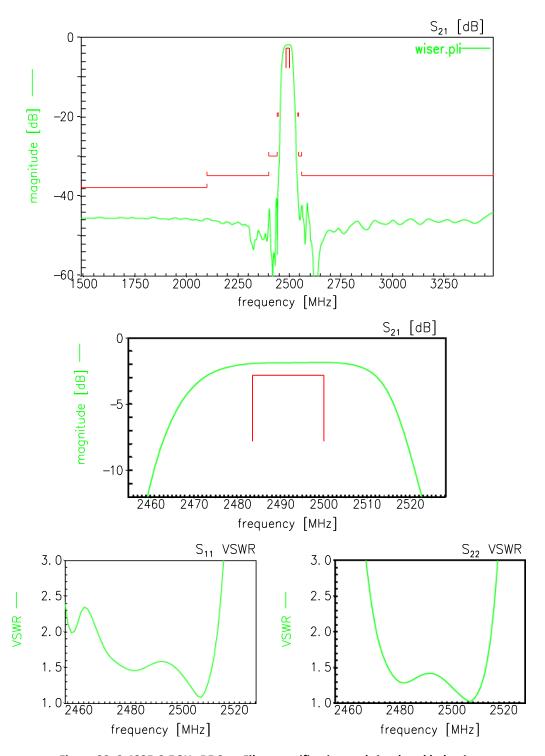

#### 2.8.2.2 2.4835-2. 5GHz RF front-end filter

The 2.4835-2.5GHz is an alternate frequency band of operation, not considered in the project proposal. The first usage of this band is the downlink of the Globalstar satellite modile phone service. A secondary usage, presently in discussion, may be Low Power Active Medical Implant operation.

If this dedicated band is targeted, a dedicated optimized filter should be designed, i.e. rejecting as much as possible the interferers in the crowded ISM 2.4-2.4835GHz band. Such a RF front-end filter could be defined as below:

This filter is intended to reject the out of band strong interferers especially from the 1.8 GHz, 2.4 GHz and 2.5 GHz bands.

|                                                  | Specifications proposal     |         |      |      |

|--------------------------------------------------|-----------------------------|---------|------|------|

| Parameter                                        | Min.                        | Тур.    | Max. | Unit |

| Operating temperature range                      | 0                           | -       | 60   | °C   |

| Center Frequency                                 | -                           | 2491.75 | -    | MHz  |

| Passband Width                                   | 16.5                        | -       | -    | MHz  |

| Max Insertion Loss over 16.5 MHz band @ Fc       | -                           | 2.0     | 2.8  | dB   |

| Relative attenuation                             |                             |         |      |      |

| 880 - 960 MHz                                    | 40                          | -       | -    | dB   |

| 960 - 2110 MHz                                   | 38                          | -       | -    | dB   |

| 2110 - 2400 MHz                                  | 35                          | -       | -    | dB   |

| 2400 - 2440 MHz                                  | 27                          | -       | -    | dB   |

| 2440 - 2450 MHz                                  | 18                          | -       | -    | dB   |

| 2535 - 2545 MHz                                  | 18                          | -       | -    | dB   |

| 2545 - 2560 MHz                                  | 25                          | -       | -    | dB   |

| 2560 - 3600 MHz                                  | 35                          | -       | -    | dB   |

| 3600 - 5000 MHz                                  | 28                          | -       | -    | dB   |

| Amplitude Ripple over 16.5 MHz band @ Fc         | -                           | -       | 1.0  | dB   |

| Input V.S.W.R. over Passband                     | -                           | -       | 2.2  |      |

| Output V.S.W.R. over Passband                    | -                           | -       | 2.2  |      |

| Source Impedance (single - no external matching) | -                           | 50      | -    | Ω    |

| Load Impedance (single - no external matching)   | -                           | 50      | -    | Ω    |

| Package size                                     | DSSP 0.95 x 0.6 mm (CBT06A) |         |      |      |

| Package height                                   | 0.2 mm + 0.085 mm (bumps)   |         |      |      |

Table 11: 2.4835-2.5GHz RF Saw Filter specification

The pinout configuration and mechanical are the same as for E369A (c.f. preceding section 2.8.2.1).

Figure 20: 2.4835-2.5GHz RF Saw Filter specification and simulated behavior

#### **2.8.3** IF1 filter

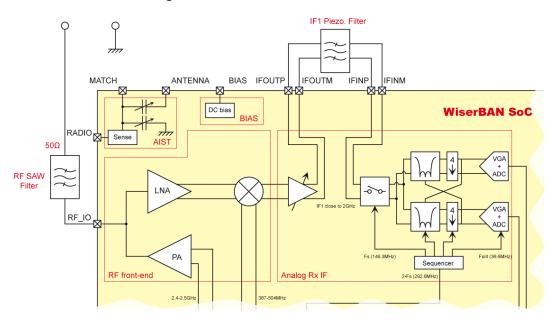

Two IF1 filters are considered at the beginning of the project. One can consider the BAW filter as a better choice for the current consumption. But this is a risky solution because involving a less mature technology than SAW filter that can be considered as a fold-back solution. The two solutions could be reduced to one choice for the realization of the demonstrators, once the IF1-Filters are evaluated after the first test-chip silicon characterization.

Figure 21: transceiver signal paths

#### **2.8.3.1** BAW IF1 filter

This is a 2 GHz narrow-band filter designed together with a dedicated on-chip interface implemented in the SoC.

| Parameter          | Test conditions, comments | Min. | Тур. | Max  | Unit |

|--------------------|---------------------------|------|------|------|------|

| BAW IF filter size |                           |      |      |      |      |

| Width              |                           | 1.03 | 1.09 | 1.15 | mm   |

| Length             |                           | 1.14 | 1.20 | 1.26 | mm   |

| Height             | +85μm bump height         |      |      | 250  | μm   |

| BandWidth          | Measured at 3 dB          |      | 10   |      | MHz  |

| Impedance          |                           |      | 1.5  |      | kΩ   |

Table 12: BAW IF1 filter specifications

The IF1 filter is an out-of-chip piezoelectric passive filter with a narrow bandwidth intended to filter out in-band interferers, especially at multiples of the sub-sampling frequency. An important characteristic of this filter is to present a high impedance above which allow slow drive current.

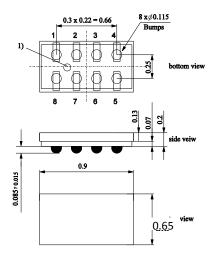

## **2.8.3.2** SAW IF1 filter

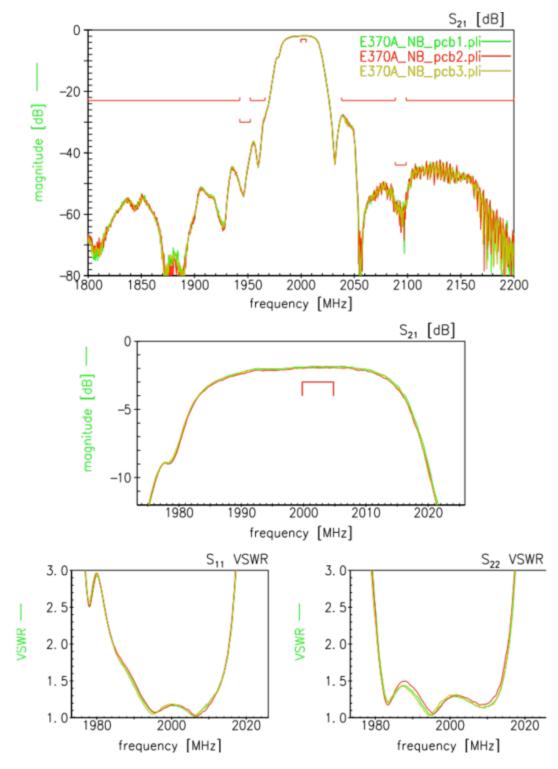

The IF1 filter (EPCOS reference E370A) is an out-of-chip piezoelectric passive filter with a narrow bandwidth intended to filter out in-band interferers, especially at multiples of the sub-sampling frequency.

|                                                  | Specification E370A |                           |      | A    |

|--------------------------------------------------|---------------------|---------------------------|------|------|

| Parameter                                        | Min.                | Тур.                      | Max. | Unit |

| Operating temperature range                      | 0                   | -                         | 60   | °C   |

| Center Frequency                                 | -                   | 2002.29                   | -    | MHz  |

| Passband Width                                   | 5.0                 | -                         | -    | MHz  |

| Max Insertion Loss over 5MHz band @ Fc           | -                   | 1.8                       | 3.0  | dB   |

| Relative attenuation                             |                     |                           |      |      |

| 0.1 - 1942.5 MHz                                 | 23                  | 44                        | -    | dB   |

| 1942.4 - 1952.4 MHz                              | 30                  | 40                        | -    | dB   |

| 1952.4 - 1966.0 MHz                              | 23                  | 29                        | -    | dB   |

| 2038.0 - 2088.7 MHz                              | 23                  | 27.5                      | -    | dB   |

| 2088.7 - 2098.7 MHz                              | 44                  | 50                        | -    | dB   |

| 2098.5 - 5000.0 MHz                              | 23                  | 43                        | -    | dB   |

| Amplitude Ripple over 5MHz band @ Fc             | -                   | 0.1                       | 0.5  | dB   |

| Phase Variation over 5MHz band @ Fc              | -                   | 1.5                       | 10   | deg  |

| <b>Group Delay Variation</b> over 5MHz band @ Fc | -                   | 5.6                       | 20   | ns   |

| Input V.S.W.R. over 5MHz band @ Fc               | -                   | 1.15                      | 1.4  |      |

| Output V.S.W.R. over 5MHz band @ Fc              | -                   | 1.25                      | 1.5  |      |

| Source Impedance (differential)                  |                     | 200                       |      | Ω    |

| Load Impedance (differential)                    |                     | 200 Ω                     |      |      |

| Package size                                     |                     | DSSP 0.9 x 0.65 mm        |      |      |

| Package height                                   | 0.2 m               | 0.2 mm + 0.085 mm (bumps) |      |      |

Pinout configuration:

Input : 1, 8

Output : 4, 5

To be grounded: 2, 3, 6, 7

Table 13: SAW IF1 filter specifications

Table 14: SAW IF1 filter specifications and measurement results at 25°C

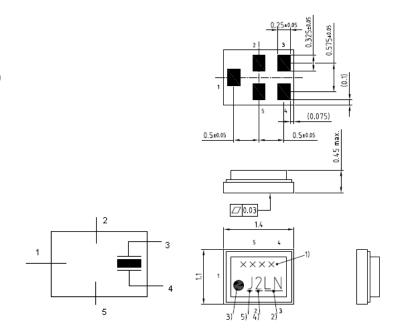

#### 2.8.4 BAW resonator

This BAW resonator (EPCOS reference E349C) is used, in conjunction with a dedicated on-chip oscillator, to provide a high frequency low-phase-noise reference to the transceiver. The associated relative low-current consumption and unique fast settling time is a key characteristic for the transceiver architecture and the associated low-current consumption.

Two mechanical versions are considered: the first one corresponds to its implementation in a standard (SAW filter) package whereas the second one is a Chip-Scale-packaging, optimized in size.

| Parameter                     | Test conditions, comments                                     | Min Typ    | Max   | Unit    |

|-------------------------------|---------------------------------------------------------------|------------|-------|---------|

| $(f_s+f_p)/2$                 | f <sub>s</sub> , f <sub>p</sub> series and parallel resonance | 204        | 8     | MHz     |

| Qs                            |                                                               | 150        | 0     |         |

| Qp                            |                                                               | 150        | 0     |         |

| $k^2 (C_m/C_0)$               |                                                               | 6          |       | %       |

| $C_0$                         | (140Ω @ f <sub>s</sub> )                                      | 0.5        |       | pF      |

| C <sub>m</sub>                |                                                               | 30         |       | fF      |

| R <sub>m</sub>                |                                                               | 1.1        |       | Ω       |

| $R_0$                         |                                                               | 0.4        |       | Ω       |

| Initial frequency             |                                                               |            | ± 400 | ppm     |

| Temperature coeff.            |                                                               |            |       |         |

| α                             |                                                               |            | ±0.6  | ppm/°C  |

| β                             |                                                               |            | -30   | ppb/°C² |

| $\Delta T_0 = -\alpha/2\beta$ |                                                               |            | ±10   | °C      |

| Frequency drift               |                                                               |            |       |         |

| over -40 to 85°C              |                                                               | -150       | +3    | ppm     |

| over 0 to 50°C                |                                                               | -40        | +3    | ppm     |

| Package size                  | First version                                                 | 1400 x 1   | 1100  | μm      |

| Package height                | 11130 VE131011                                                | 450        | μm    |         |

| Package size                  | Second version                                                | 800 x 6    | μm    |         |

| Package height                | Second version                                                | 200 + 85 ( | bump) | μm      |

**Table 15: BAW resonator specifications**

Pinout configuration:

Inputs: 3 and 4

(any of them can be grounded)

Not connected: 1, 2, 5

(any or all of them can be grounded)

Figure 22: BAW resonator mechanical description

An important feature of this component necessary to provide a low-noise frequency reference is that it is potentially tinier than classical AT-cut quartz crystals.

#### 2.8.5 LF resonator

This low-frequency silicon resonator is used in conjunction with an on-chip oscillator to provide an ultra-low power and precise frequency reference for long-term time scheduling (Real-Time-Clock).

| Parameter          | Test conditions, comments                                         | Min         | Тур      | Max  | Unit   |

|--------------------|-------------------------------------------------------------------|-------------|----------|------|--------|

| $(f_s+f_p)/2$      | f <sub>s</sub> , f <sub>p</sub> series and parallel resonance (1) | 0.5         |          | 1    | MHz    |

| FoM                | $Q \times k^2$                                                    |             | 30       |      |        |

| C <sub>0</sub>     |                                                                   |             |          | 2    | pF     |

| Initial frequency  | Not critical (2)                                                  |             |          |      | ppm    |

| Temperature coeff. |                                                                   |             |          |      |        |

| α                  | (3)                                                               |             | -30      |      | ppm/°C |

| Package size       | First version                                                     | 2100 x 1230 |          | μm   |        |

| Package height     | First version                                                     |             | 500      |      | μm     |

| Package size       | Second version                                                    | 660 x 660   |          | μm   |        |

| Package height     | Second version                                                    | 150         | + 85 (bu | ımp) | μm     |

**Table 16: LF Silicon Resonator specifications**

#### Notes:

- 1. A 32kiHz is flexibly formed from any resonance frequency at the given range.

- 2. Not critical: correction factors to be used within the oscillator IC will be determined by calibration measurements.

- 3. It is not desirable to have a TCF of smaller magnitude since the LF MEMS resonator has a role of a temperature sensor as well.

- 4. Any parasitic resonance should have FoM<2.

Both BAW resonator and LF silicon resonator have too wide production tolerances and temperature drift. But using the fact that they are uncorrelated, both frequencies can be compensated at system level using calibrations.

An important characteristic of this component necessary to provide a low frequency reference is that it is potentially tinier than classical fork quartz crystals (e.g. 32kiHz wristwatch crystal).

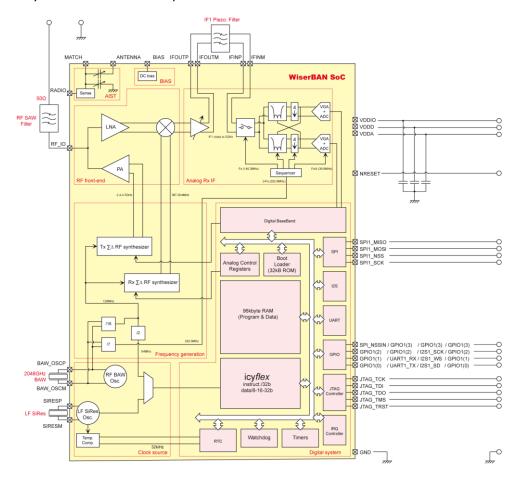

# 2.9 Radio System-on-Chip

The Radio SoC specification is the objective of deliverable D1.3. For sake of easy reading, a summary is provided in this section.

#### 2.9.1 Overview

The radio SoC integrates the 2.45GHz radio transceiver and the controller that handles the software part of the radio communication protocol.

The precise specification is described in the "D1.3 Final radio system architecture and specification" document.

## 2.9.2 Transceiver

Typical specification are at 25°C, voltage supply=1.2V, unless otherwise noted.

| Parameter                  | Test conditions, comments | Min.     | Тур.     | Max  | Unit            |

|----------------------------|---------------------------|----------|----------|------|-----------------|

| Voltage supply             | Core analog and digital   | 1.08     | 1.2      | 1.32 | V               |

| Temperature                | Operating                 | -40      | 25       | 85   | °C              |

| RF frequency (1)           |                           | 2400     |          | 2500 | MHz             |

| PeakDatarate (2)           |                           |          |          | 2000 | kbit/s          |

| Modulation index (3)       | 2-FSK                     | 0.3      | 0.5      |      |                 |

| Channel bandwidth (4)      | -3dB                      |          |          | 2    | MHz             |

| Sensitivity                | 1‰ BER, for 2Mbit/s MSK   |          | -87      |      | dBm             |

| Rejection                  |                           |          |          |      |                 |

| Adjacent channel (5)       | ±5MHz for 2Mbit/s MSK     |          | 0        |      | dB              |

| Alternate channel (5)      | ±10MHz for 2Mbit/s MSK    |          | -30      |      | dB              |

| Intermodulation (5)        | Adjacent & alternate      |          | 0        |      | dB              |

| Transmitted power (6)      | 2Mbit/s MSK               |          | -2       | 0    | dBm             |

| Turnaround time            | Rx to Tx or opposite      |          | 10       |      | μs              |

| RF&analog current          |                           |          |          |      |                 |

| Receiver <sup>(2)</sup>    | Steady state              |          | 7.5      |      | mA              |

| Transmitter <sup>(3)</sup> | Steady state              |          | 7.5      |      | mA              |

| Digital current            |                           |          |          |      |                 |

| Receiver                   |                           |          | 200      |      | μΑ              |

| Transmitter                |                           |          | 100      |      | μΑ              |

| Startup overhead (7)       | Rx or Tx                  |          | 0.25     |      | μC              |

| Leakage                    |                           |          | 50       |      | nA              |

| SoC dimensions             |                           | 2.3 x 2. | 0 x 0.25 |      | mm <sup>3</sup> |

**Table 17: transceiver specifications**

## Notes:

1. The RF frequency range is limited by RF the front-end filter and IF1 filter frequencies for maximum performances (e.g. interferer rejection). Other frequency ranges in the vicinity, such as

2360MHz to 2400MHz for 802.15.4j or 24835MHz to 2500MHz for 802.15.6 are also possible but require different piezoelectric components.

- 2. The peakdatarate can be digitally tuned to integer fractions of the maximum raw datarate in order to increase the budget link. But note that the sensitivity improvement is not linear because it is also depending on the channel bandwidth. Note also that the effective datarate is affected by the protocol overhead (preamble, sync. word, address, CRC, etc).

- 3. Thanks to the modulation through the RF synthesizer in transmission, the modulation index is only limited by the digital settings.

- 4. There is no real interest to lower the channel bandwidth below this minimum because it has to handle the reference frequencies misalignment. Thanks to  $\Sigma \Delta$  RF synthesis, the channel center frequencies can be freely fixed.

- 5. The rejections are defined as the energy of interferer over the sensitivity plus 3dB at which the BER is 1‰. For intermodulation, both adjacent and alternates are at same level and only one of them is modulated.

- 6. At 2.4GHz, there is a 40dB free-space path loss associated to the first 1m-communication range with 0dBi antennas. The 1/d² radiated energy density adds 6|20dB free-space propagation losses every factor of 2|10 in distance.

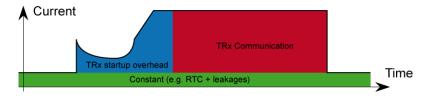

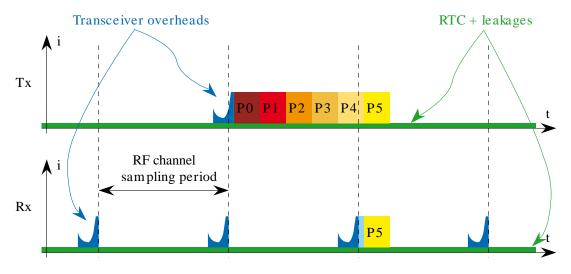

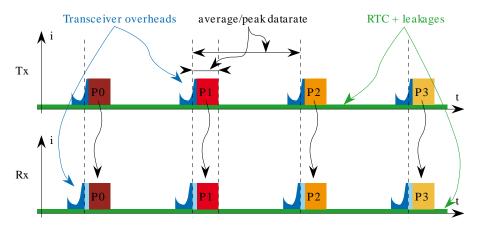

- 7. This startup overhead is a very important specification because of the preferred duty cycling scheme for average current reduction: for intermittent communication, the ultra-low-power receiver has an average current consumption directly proportional to this value and to the RF channel sampling frequency. For continuous streaming of information, the average current is proportional to the average datarate only if this overhead can be neglected versus the transceiver steady-state current multiplied by the packet duration. The shorter is this packet duration, the shorter are the latency and the easier is the associated supply noise filtering. Note that to minimize this overhead, the different sub-blocks are powered on "just in time" depending on their different startup time inducing a non-constant current profile as described in the Figure 23 below:

Figure 23: standby, radio start-up and active currents

#### 2.9.3 Controller

The controller is a 32bit RISC general-purpose controller with additional DSP-oriented instruction set using two MAC engine.

Typical specification are at 25°C, voltage supply=1.2V, unless otherwise noted.

| Parameter            | Test conditions, comments     | Min. | Тур. | Max  | Unit   |

|----------------------|-------------------------------|------|------|------|--------|

| Voltage supply       |                               | 1.08 | 1.2  | 1.32 | V      |

| IO voltage range (1) |                               | 1.8  |      | 3.6  | V      |

| Temperature          | Operating                     | -40  | 25   | 85   | °C     |

| Clock frequency      |                               | 0.1  |      | 32   | MHz    |

| Memory               | Program + Data memory         |      | 96   |      | kByte  |

| SoC wakeup time      |                               |      |      |      |        |

| Power-up             | 96kB SPI-loading at 5Mbit/s   |      | 1    |      | S      |

| From sleep (2)       | Using GPIO based IRQ or Timer |      | 10   |      | μs     |

| Active current       |                               |      |      |      |        |

| CPU                  |                               |      | 50   |      | μA/MHz |

| Sleep                | RTC running, 25°C             |      | 12   |      | μΑ     |

| Leakages (3)         |                               |      |      |      |        |

| Digital              |                               |      | 2    |      | μΑ     |

| RAM                  | Typical case 25°C             |      | 9    |      | μΑ     |

| RTC current          |                               |      | 1    |      | μΑ     |

Table 18: transceiver specifications

#### **Notes:**

- 1. Depends in practice of voltage supply of components that are outside of the SoC, e.g. nvRAM used for the boot (c.f. section 2.10).

- 2. The sleep state is triggered by a μController instruction. The wake-up is triggered by an event (typ. a RTC IRQ). During the sleep state, the major part of the digital system is unclocked to minimize the current consumption. Of course, also to minimize the current consumption, the BAW oscillator is preferably switched off and then the only available digital clock is coming from the Silicon resonator oscillator, typically limited to 100kHz. The BAW oscillator starts up very quickly, i.e. in less than one cycle of the 100kHz clock that limits the frequency switching time: an instructionwakes up the BAW oscillator and another instruction is necessary to switch the digital frequency.

- 3. Without RAM and digital libraries optimized for low leakage.

## 2.9.4 Digital peripherals

In addition with the transceiver with its digital baseband several digital peripherals of the controller have been implemented:

- **ReQuest Controller** manages the interrupt triggered by other peripherals.

- **GPIOs** are general purpose digital Input-Output with push-pull output, selectable pull-up, input with Schmidt trigger.

- SPI with a dedicated NSSOUT pin for selection of nvRAM used by bootloader.

- **I2S** multiplexed on GPIO pin as secondary functionality.

- **UART** multiplexed on GPIO pins as third functionality.

- JTAG interface for debug and possible interface for external nvRAM.

- 4x Timers and Watchdog, mainly to generate interrupts.

- RTC, mainly for Real Time counting whatever is the state of the system, e.g during sleep mode.

#### 2.9.5 Oscillator and clocks

Oscillator and clocks

Two oscillators are integrated:

- An ultra-low-power low-frequency oscillator based on silicon resonator for time precision (c.f. chapter 2.8.5). An associated 32.768kHz derived clock is used for long-term scheduling (RTC) and tuning of the BAW resonator.

- A low-power high-frequency oscillator based on a BAW resonator (c.f. chapter 2.8.4). The

derived clocks are used by the transceiver as low phase noise frequency reference and by the

controller as high-frequency clock source.

Typical specification are at 25°C, voltage supply=1.2V, unless otherwise noted.

| Parameter          | Test conditions, comments | Min. | Тур. | Max  | Unit |

|--------------------|---------------------------|------|------|------|------|

| Voltage supply     |                           | 1.08 | 1.2  | 1.32 | V    |

| Temperature        | Operating                 | -40  | 25   | 85   | °C   |

| Si resonator osc.  |                           |      |      |      |      |

| Frequency (1)      |                           | 0.5  |      | 1    | MHz  |

| Startup time       |                           |      | 50   |      | ms   |

| Startup current    |                           |      | 0.1  |      | μC   |

| Active current     |                           |      | 1    |      | μΑ   |

| Leakages           |                           |      | 0.01 |      | nA   |

| BAW resonator osc. |                           |      |      |      |      |

| Frequency (2)      |                           |      | 2048 |      | MHz  |

| Startup time       |                           |      | 20   |      | μs   |

| Startup current    |                           |      | 0.12 |      | μC   |

| Active current     |                           |      | 500  |      | μΑ   |

| Leakages           |                           |      | 5    |      | nA   |

| RTC precision (3)  | 32kiHz, 0°C to +70°C      |      | ±60  |      | ppm  |

**Table 19: oscillators specifications**

#### Notes:

- 1. This frequency is divided by fractional ratio to provide a compensated 32.768kHz frequency.

- 2. This frequency is divided by fixed integer ratio to provide lower clock frequencies (typ. 32MHz) to the controller.

- 3. This Real Time Clock frequency is derived by division of Si resonator LF frequency. The division factor is programmable in order to implement a compensation scheme using both resonator frequencies and multiple temperature calibrations.

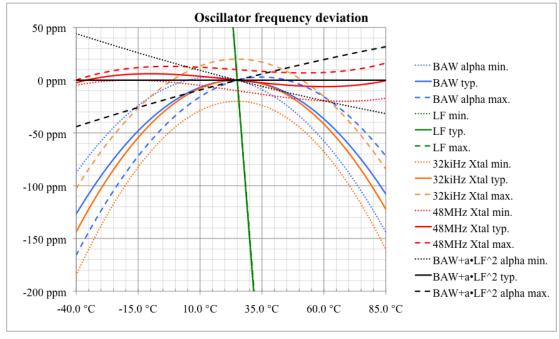

Compared to more classical frequency references based on bulkier quartz crystal, both oscillators are less accurate. We rely on a calibration scheme using the relative non-correlation of specific drifts to obtain state of the art frequency precision.

The BAW frequency reference has less temperature drift than the Silicon resonator frequency reference that have a monotonic temperature drift. The relative measurement of the low-frequency reference using the high-frequency reference provides then a temperature measurement that can be used to compensate both frequency references.

The equations (1) and (2) describes the temperature dependence with polynomial approximation:

$$f_{BAW}(t) = f_{BAW}(25^{\circ}C) + \alpha_{BAW} \cdot (t - 25^{\circ}C) + \beta_{BAW} \cdot (t - 25^{\circ}C)^{2} + \gamma_{BAW} \cdot (t - 25^{\circ}C)^{3}$$

(1)

$$f_{LF} = f_{LF}(25^{\circ}C) + \alpha_{LF} \cdot (t - 25^{\circ}C) + \beta_{LF} \cdot (t - 25^{\circ}C)^{2} + \gamma_{LF} \cdot (t - 25^{\circ}C)^{3}$$

(2)

$$\alpha_{\scriptscriptstyle BAW} << \alpha_{\scriptscriptstyle LF}$$

(3)

The Figure 24 below compares the BAW and LF frequency deviations with standard quartz crystal frequency deviations and illustrates a first-order temperature compensation of the BAW frequency:

Figure 24: example of oscillator frequency temperature deviations

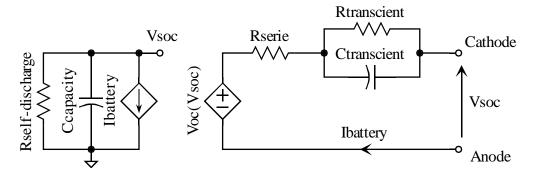

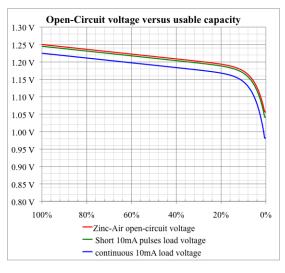

#### **2.10** nvRAM