# **Final Assessment of Demonstrator Concept and Implementation** D5.2

'5GNOW\_D5.2\_final.docx'

Version: 1.0

Last Update: 05/03/2015

Distribution Level: PU

Distribution level

RE = Restricted to a group of the specified Consortium,

PP = Restricted to other program participants (including Commission Services),

CO= Confidential, only for members of the 5GNOW Consortium (including the Commission Services)

# The 5GNOW Project Consortium groups the following organizations:

| Partner Name                                           | Short name | Country |

|--------------------------------------------------------|------------|---------|

| FRAUNHOFER-GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN |            |         |

| FORSCHUNG E.V.                                         | нні        | Germany |

| ALCATEL LUCENT DEUTSCHLAND AG                          | ALUD       | Germany |

| COMMISSARIAT À L'ENERGIE ATOMIQUE ET AUX ENERGIES      |            |         |

| ALTERNATIVES                                           | CEA        | France  |

| IS-WIRELESS                                            | ISW        | Poland  |

| NATIONAL INSTRUMENTS                                   | NI         | Hungary |

| TECHNISCHE UNIVERSITÄT DRESDEN                         | TUD        | Germany |

# **Abstract:**

"This deliverable provides a comparison of SoTA OFDM and the proposed non-orthogonal PHY design with respect to the KPIs. An outcome will be the evaluation and quantification, to which extent the expected advantages of non-orthogonal modulation (e.g. robustness) could be shown under realistic side conditions. The deliverable will conclude on critical implementation components for asynchronous 5G systems, which might become a showstopper for practical application."

| Partner | Author name                                                       |

|---------|-------------------------------------------------------------------|

| HHI     |                                                                   |

| ALUD    |                                                                   |

| CEA     | Vincent Berg, Jean-Baptiste Doré, Dimitri Kténas and Xavier Popon |

| ISW     |                                                                   |

| NI      | Michael Löhning, Peter Vago                                       |

| TUD     | Ivan Simões Gaspar, Nicola Michailow                              |

Fage: 2 of 77

"The research leading to these results has received funding from the European Community's Seventh Framework Programme (FP7/2007-2013) under grant agreement n° 318555"

5GNOW Page: 3 of 77

# **Document Identity**

Title: Final Assesment of Demonstrator Concept and Implementation

WP: WP5 – Proof-Of-Concept

WP Leader TUD

Main Editor Dimitri Kténas

Number: D5.2

File name: 5GNOW\_D5.2\_final.docx

Last Update: Thursday, March 05, 2015

# **Revision History**

| No.                              | Version   | Edition                                                          | Author(s)                                                      | Date     |

|----------------------------------|-----------|------------------------------------------------------------------|----------------------------------------------------------------|----------|

| 1                                | 0.1       |                                                                  | Dimitri Kténas (CEA)                                           | 19.10.14 |

|                                  | Comments: | Providing initial template, skeleton and initial inputs from CEA |                                                                |          |

| 2                                | 0.2       |                                                                  | Ivan Simoes Gaspar (TUD)                                       | 11.11.14 |

| Comments: Inputs from TUD        |           | Inputs from                                                      | TUD                                                            |          |

| 3                                | 0.3       |                                                                  | Michael Löhning (NI), Peter Vago (NI) and Dimitri Kténas (CEA) | 24.11.14 |

| Comments: Inputs from NI and CEA |           | NI and CEA                                                       |                                                                |          |

| 4                                | 0.4       |                                                                  | Dimitri Kténas (CEA)                                           | 28.11.14 |

|                                  | Comments: | Consolidate                                                      | d version                                                      |          |

| 5                                | 0.5       |                                                                  | Dimitri Kténas (CEA) and Ivan Simoes Gaspar (TUD)              | 10.12.14 |

|                                  | Comments: | Review rour                                                      | nd and finalization.                                           |          |

| 6                                | 1         |                                                                  | Gerhard Wunder                                                 | 05.03.15 |

| Comments: Final Review           |           | · ·                                                              |                                                                |          |

| 7                                |           |                                                                  |                                                                |          |

|                                  | Comments: |                                                                  |                                                                |          |

| 8                                |           |                                                                  |                                                                |          |

|                                  | Comments: |                                                                  |                                                                |          |

| 9                                |           |                                                                  |                                                                |          |

|                                  | Comments: |                                                                  |                                                                |          |

| 10                               |           |                                                                  |                                                                |          |

|                                  | Comments: |                                                                  |                                                                |          |

| 11                               |           |                                                                  |                                                                |          |

|                                  | Comments: |                                                                  |                                                                |          |

| 12                               |           |                                                                  |                                                                |          |

|                                  | Comments: |                                                                  |                                                                |          |

| 13                               |           |                                                                  |                                                                |          |

|                                  | Comments: |                                                                  |                                                                |          |

| 14                               |           |                                                                  |                                                                |          |

|                                  | Comments: |                                                                  |                                                                | -        |

| 15                               |           |                                                                  |                                                                |          |

|                                  | Comments: |                                                                  |                                                                |          |

5GNOW Page: 4 of 77

# **Table of Contents**

| 1 | INTRO               | ODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7       |

|---|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 2 | SCEN                | ARIOS, PHY PARAMETERS AND KPIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9       |

|   | 2.1                 | REFERENCE SCENARIOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | c       |

|   | 2.2                 | LOW LATENCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

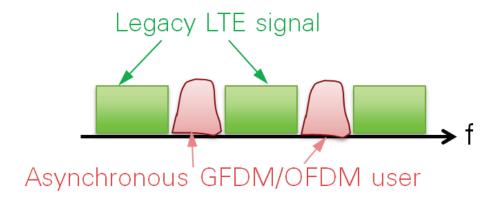

|   | 2.3                 | MULTI-USER FRAGMENTED SPECTRUM ACCESS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

|   | 2.4                 | KPIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _       |

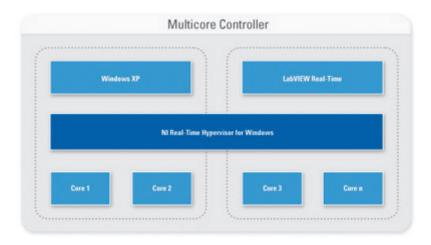

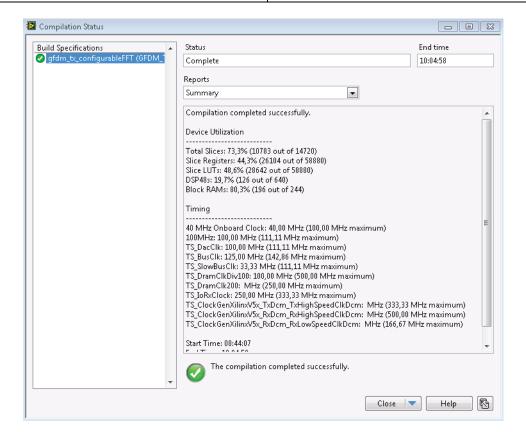

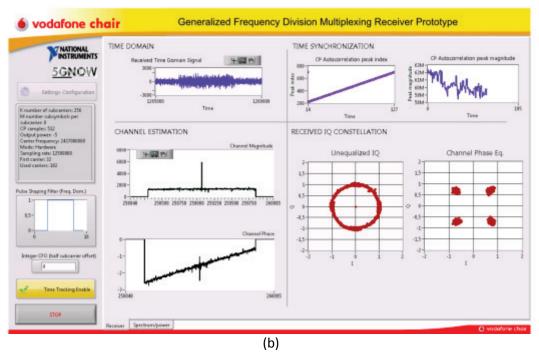

| 3 |                     | SIDERED PLATFORMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

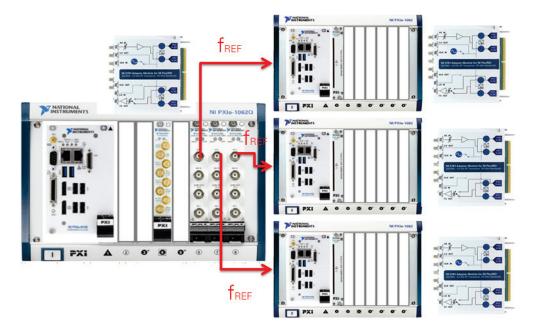

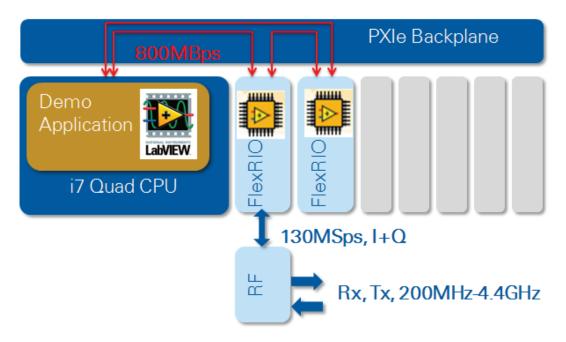

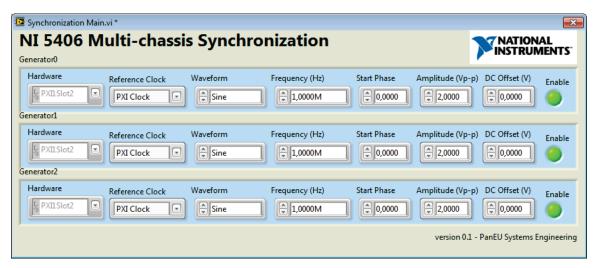

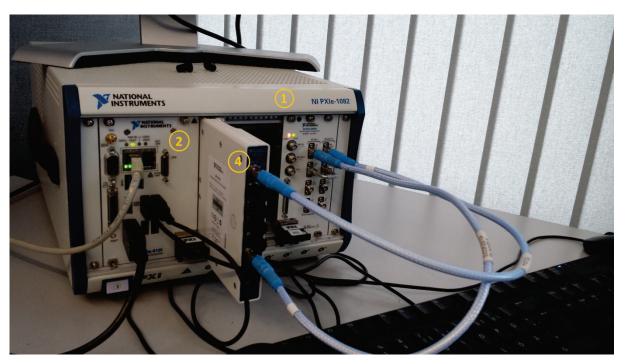

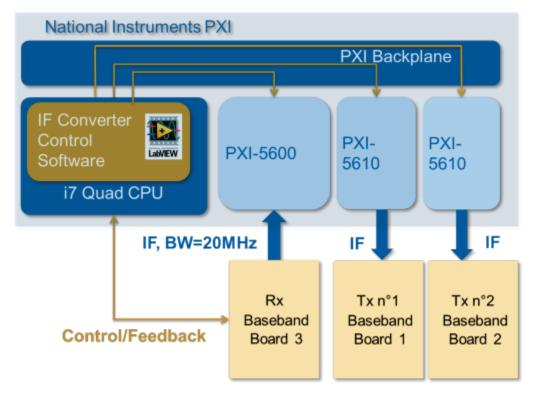

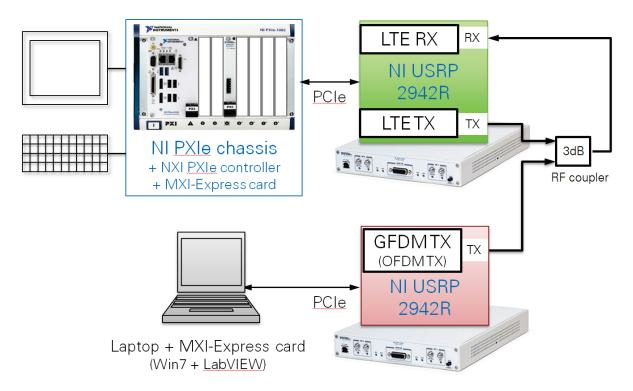

|   | 3.1                 | NI PXI PLATFORM FOR PROTOTYPING RF TECHNOLOGIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16      |

|   | 3.1.1               | Platform Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

|   | 3.1.2               | , and the second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

|   | 3.1.3               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

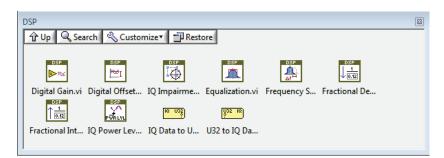

|   | 3.1.4               | Software development environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

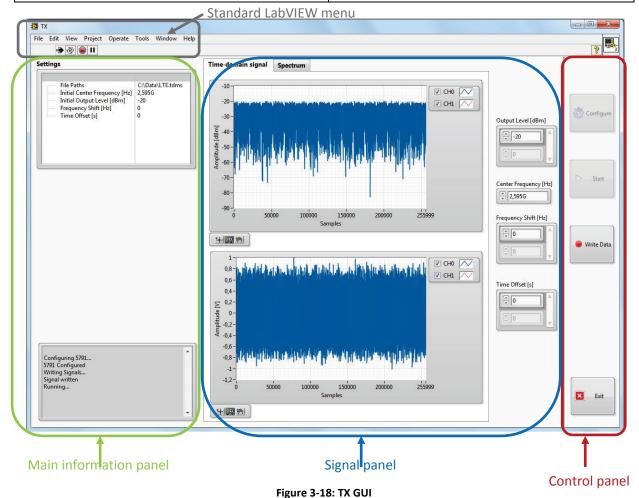

|   | 3.1.5               | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

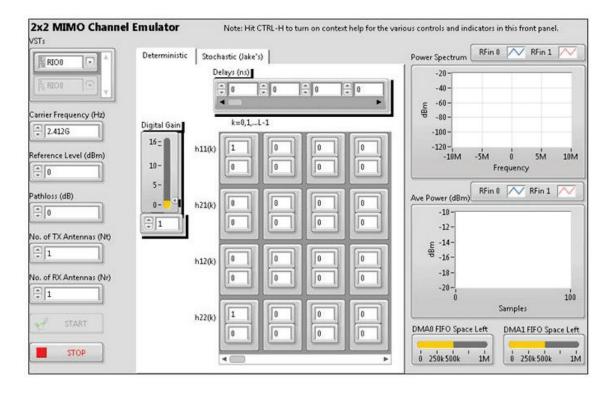

|   | 3.1.6               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

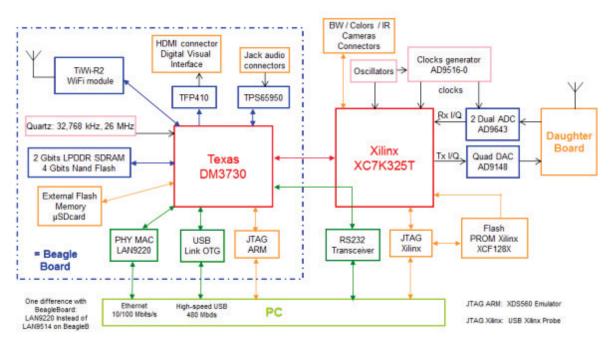

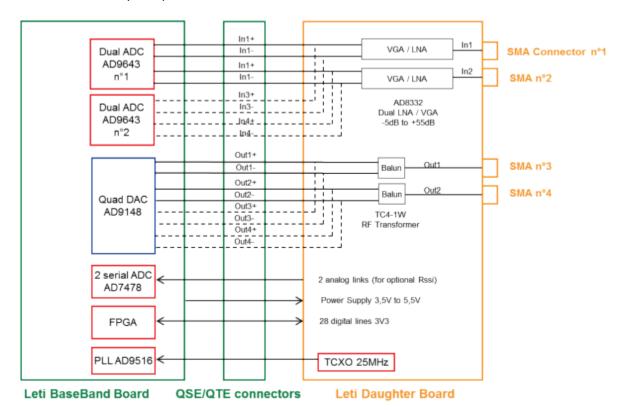

|   | 3.2                 | CEA-LETI BASE BAND PLATFORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

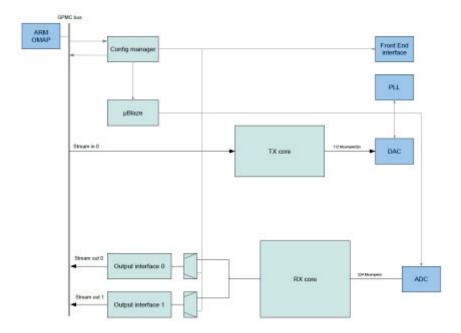

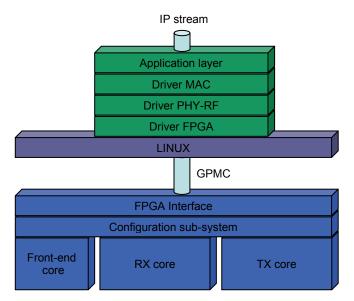

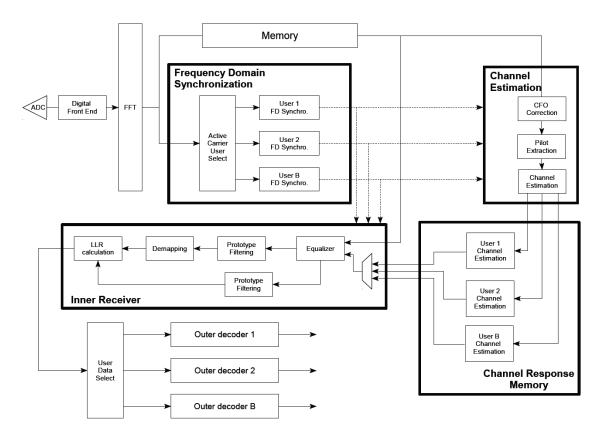

|   | 3.2.1               | Architecture of 5GNOW FBMC Demonstrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

|   | 3.2.2               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

|   | 3.2.3               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

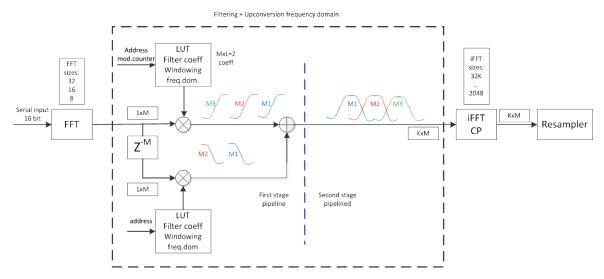

|   | 3.2.4               | FBMC baseband transceiver implementation architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

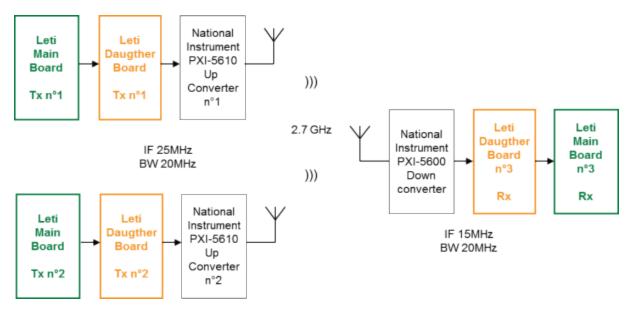

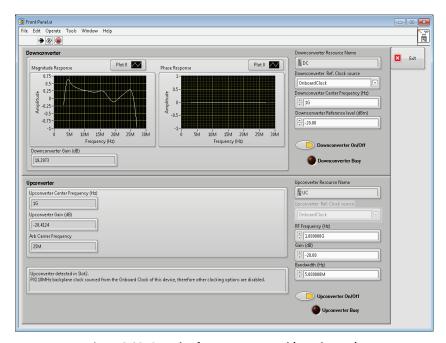

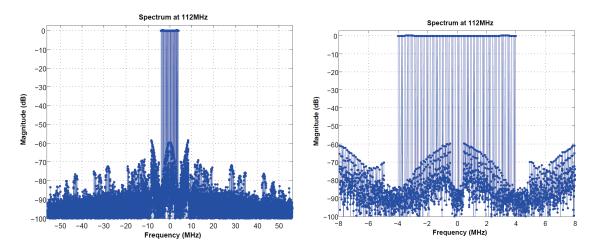

|   | 3.2.5               | RF Up-conversion and Down-conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

| 4 | FINΔI               | L IMPLEMENTATION OF TRANSCEIVER ALGORITHMS AND CONTROL FUNCTIONALITY IN TI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | HE      |

|   |                     | OC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

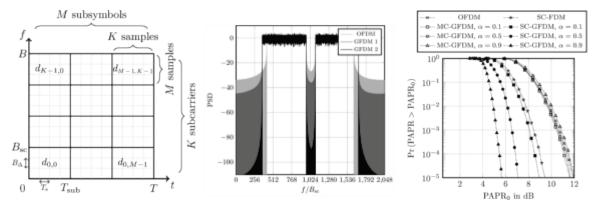

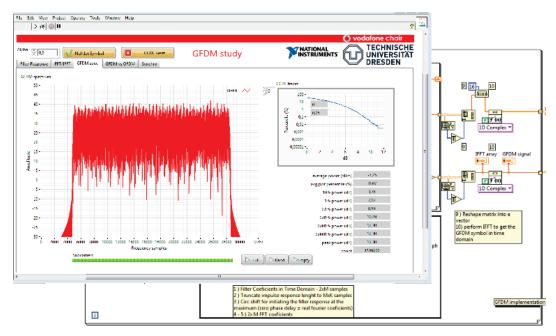

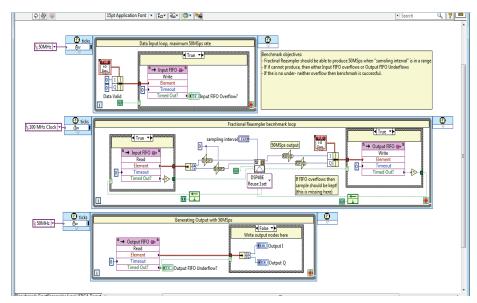

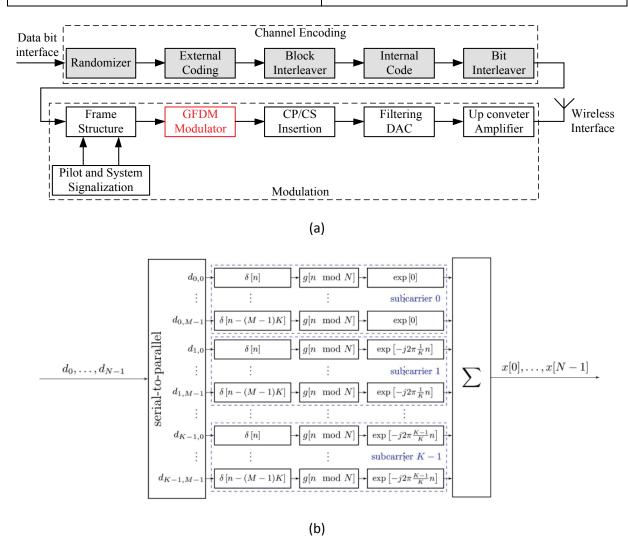

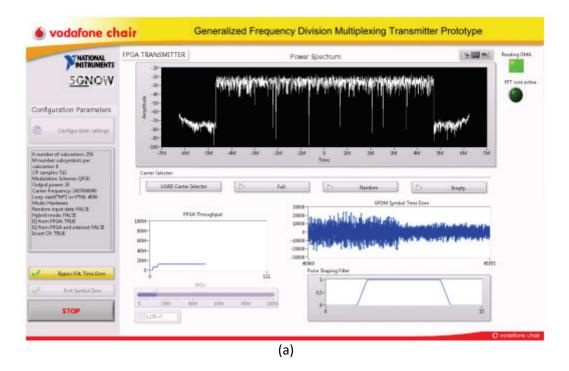

|   |                     | GFDM transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

|   | 4.1<br><i>4.1.1</i> | Low complex TX model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

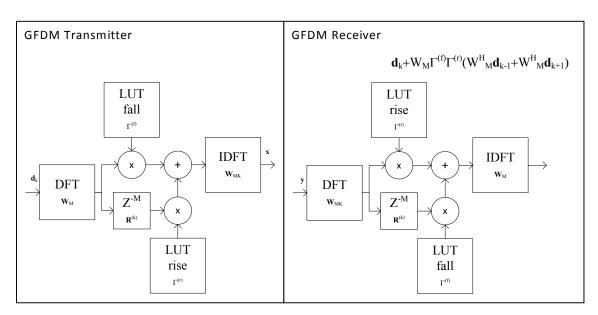

|   | 4.1.1<br>4.1.2      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

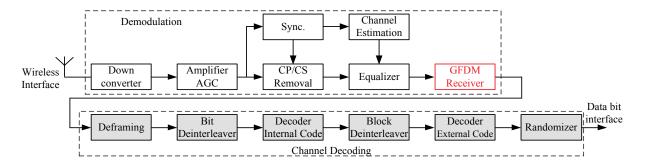

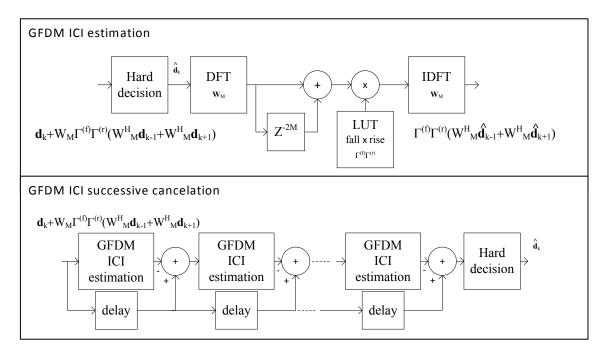

|   | 4.1.2               | Low complex RX model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

|   | 4.1.3               | FBMC transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

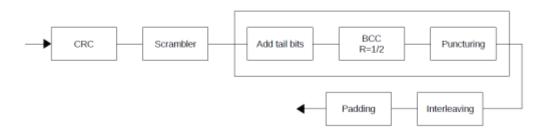

|   | 4.2.1               | FBMC transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

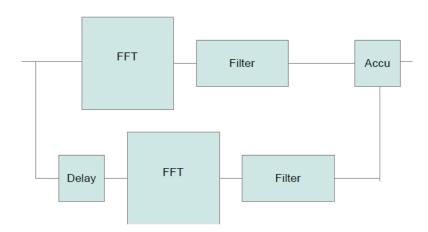

|   | 4.2.2               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

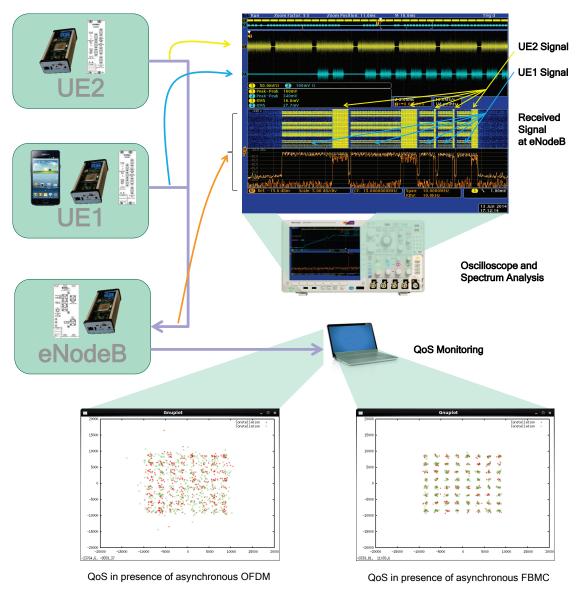

| 5 |                     | UATION OF HW DEMONSTRATOR CONCEPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| , |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

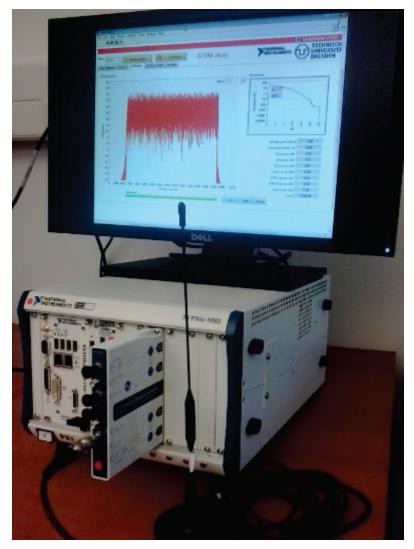

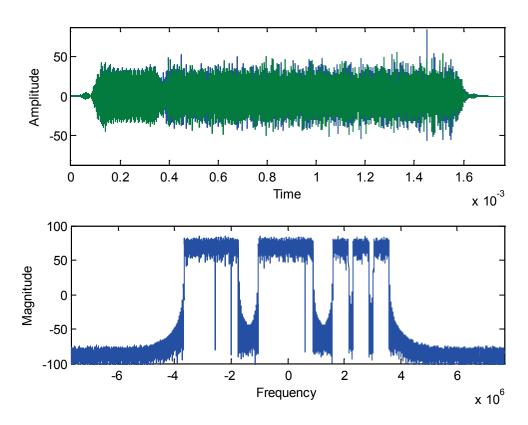

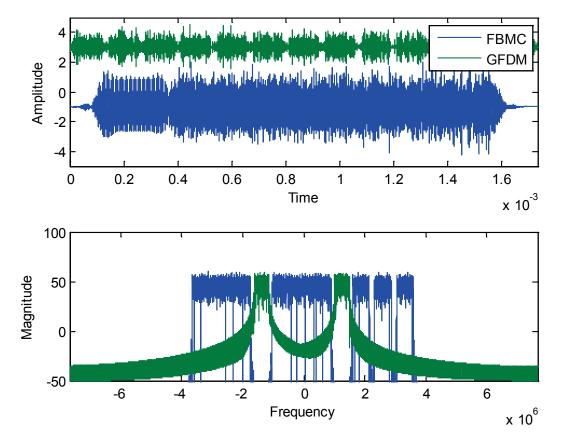

|   | 5.1                 | GFDM DEMONSTRATOR PLATFORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |