# D2.11 Final user manual for the industry-ready RTOS multicore solutions Version 1.1

# **Document Information**

| Contract Number      | 611085                             |

|----------------------|------------------------------------|

| Project Website      | www.proxima-project.eu             |

| Contractual Deadline | M36, 30-November-2016              |

| Dissemination Level  | RE                                 |

| Nature               | О                                  |

| Author               | Francis Vatrinet (SYS)             |

| Reviewer             | Iain Bate (UoY)                    |

| Keywords             | RTOS baseline, User manual, PikeOS |

### Notices:

The research leading to these results has received funding from the European Community's Seventh Framework Programme [FP7/2007-2013] under grant agreement n° 611085.

© 2013 PROXIMA Consortium Partners. All rights reserved.

# **Change Log**

| Version | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v0.1    | Initial Draft released for internal review at BSP v1.2.3 delivery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V0.2    | Draft Add FPGA bitstream identification and constraint at installation section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V0.3    | Draft New Built In Test API and Time Composability Checker tool for BSB v1.3.0  Add configuration info about FPGA serial line in section 4.1.  PR#1399-Projects FPGA-HW-Randomization: configurable seeds initiali,  PR#1400-Projects Time Composability: remove PSSW and Lib APEX cache impact,  PR#1402-Projects PAK: add instrumentation for performance counters,  PR#1404-Projects PAK: add IBIT for WCET verification of APIs in CIC,  PR#1408-Projects FPGA-HW: L2 cache partitioning - flush on per way basis,  PR#1410-Projects PAK: add configuration info at init time,  PR#1430-Projects upgrade to FPGA version 1.7,                                                     |

| V0.4    | PR#1449-Projects Put kernel code and data into no cache area for time composability  PR#1452-Projects PAK: add PRNG for user level, PR#1465-Projects FPGA BSP - set workaround for bitstream v1.8 bug, split L1 and L2 seed management based on PSP TAG (PSP_L2_ENABLE)  update for v1.2.3 delay  Validated for BSP v1.2.4 on bitstream v1.9b, update the accordingly the table "Time Composability features availability"  PR#1447-Projects TC checker: added and documented calibration method.  PR#1450-Projects add the math library into the apex application PR#1468-Projects add the math library to the native application PR#1472-Projects [PROXIMA] add monitoring counters |

| Tersion 1.1         |                                                                                                                                                                                                                                                                                        |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                     | BSP v1.2.5:                                                                                                                                                                                                                                                                            |  |

| V0.5                | <ul> <li>Add P4080 PSP</li> <li>Update demonstration projects to be architecture independent</li> <li>Update LEON3 PSP (configuration only for stat driver declaration)</li> <li>Remove PikeOS 3.5 Support</li> <li>PR#1473-Projects Add math library (libm) for PikeOS 3.4</li> </ul> |  |

|                     | BSP v1.2.5 validated on FPGA bitstream v1.9b and PSP4080.                                                                                                                                                                                                                              |  |

|                     | BSP v1.2.5 provides invalid results on FPGA bitstream v1.9c when PTA mode is activated.                                                                                                                                                                                                |  |

|                     | BSP v1.2.5 validated on reference board P4080 (freescale QDS),                                                                                                                                                                                                                         |  |

|                     | Roadmap update due to FPGA availability                                                                                                                                                                                                                                                |  |

|                     | BSP v1.3.0 upgrades :                                                                                                                                                                                                                                                                  |  |

|                     | PR#1446-Projects [PROXIMA]APEX TC write queuing msg still provide a small variability (I_OS_01)                                                                                                                                                                                        |  |

|                     | PR#1464-Projects PROXIMA FPGA BSP - merge DRAM and scratchpad RAM PSPs into one for maintenance purpose                                                                                                                                                                                |  |

|                     | PR#1466-Projects FPGA BSP - provides a PSP kinfo page for user level fast access                                                                                                                                                                                                       |  |

|                     | PR#1467-projects: FPGA BSP - rework IBIT for better arch dependency support                                                                                                                                                                                                            |  |

|                     | PR#1469-projects: Provides TC Checker tool with editable scenario                                                                                                                                                                                                                      |  |

|                     | PR#1470-Projects [PROXIMA] port BSP 1.3.0 to P4080 target                                                                                                                                                                                                                              |  |

| V0.6 draft          | PR#1476-Projects [PROXIMA] port BSP 1.3.0 to FPGA bitstream v2.0 => The bitstream v2.0 does not work properly.                                                                                                                                                                         |  |

| , 0.0 <b>G</b> 2442 | PR#1478-Projects [PROXIMA] support for new PTA mode policy                                                                                                                                                                                                                             |  |

|                     | PR#1480-Projects [PROXIMA] performance counters support for TC tool checker for both FPGA and P4080                                                                                                                                                                                    |  |

|                     | PR#1481-Projects [PROXIMA] FPGA: Add kernel TAG 0x308 to run kernel with NO cache attribute                                                                                                                                                                                            |  |

|                     | BSP v1.3.0 has not been delivered:                                                                                                                                                                                                                                                     |  |

|                     |                                                                                                                                                                                                                                                                                        |  |

|                     | BSP v1.3.1 upgrades :                                                                                                                                                                                                                                                                  |  |

|                     | PR#1482-Projects [PROXIMA] upgrade to FPGA bitstream v2.1 including support for ABPRANDBANK v3                                                                                                                                                                                         |  |

|                     | PR#1403-Projects [PROXIMA] FPGA: add instrumentation callback for RVS ipoints. Ipoints are written to GPIO for RTBx capture or to configurable buffer through TAG 0x309.                                                                                                               |  |

|                     | PR#1483-Projects [PROXIMA] P4080: add instrumentation callback                                                                                                                                                                                                                         |  |

for RVS ipoints. Ipoints are written to configurable buffer through TAG 0x309

PR#1484-Projects [PROXIMA] P4080: Add kernel TAG 0x308 to run kernel with NO Cache attribute for Time Composability

PR#1487-Projects [PROXIMA] Time Composability : run tp0 into core 1 to reduce interference with running partition

PR#1488-Projects [PROXIMA] PRNG provides random value cross reboot using timer value at initialization time

BSP v1.3.1 crashes when running PTA mode with FPGA bitstream v2.1 (with or without L2).

— under investigation

BSP v1.3.1 does not support dynamic ticker with FPGA bitstream v2.1

— under investigation

To be fixed for v1.3.2:

PR#1471-Projects [PROXIMA] Time Composability tool checker shall provide apex and apexTC configuration.

PR#1477-Projects [PROXIMA] BSP - provides get\_MAF\_time() (requires dynamic ticker on FPGA)

### BSP v1.3.2 upgrades/fixes:

PR#1477-Projects [PROXIMA] BSP - provides get\_MAF\_time() (requires dynamic ticker on FPGA)

PR#1484-Projects [PROXIMA] BSP - P4080: add TAG 0x308 to run kernel with no cache

PR#1489-Projects [PROXIMA] BSP - Time Composability - upgrade perf DUMP event

V0.7 PR#1490-Projects [PROXIMA] BSP - Time Composability - print min, Max and average values

PR#1491-Projects [PROXIMA] BSP - provide Time Composable port provider as a native external port available for any personality.

PR#1492-Projects [PROXIMA] FPGA BSP: FIX: instrumentation exception raised writing a user event.

PR#1494-Projects [PROXIMA] FPGA BSP: add dynamic ticker mode

PR#1495-Projects [PROXIMA] FPGA BSP: enforce no seed support when NOPTA option selected

PR#1496-Projects [PROXIMA] FPGA BSP: PRNG shall return current seed; now get\_random() return current seed and then compute the next

|      | value                                                                                                                                                        |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|      | PR#1497-Projects [PROXIMA] FPGA BSP: pspkinfo now publishes the current seed values applied to hardware for quick access from user land                      |  |

|      | PR#1498-Projects [PROXIMA] PAK: FIX: now get/set prng from PAK works on the expected seed                                                                    |  |

|      | BSP v1.3.3 upgrades/fixes :                                                                                                                                  |  |

|      | BSP v1.3.3 is a patch delivered for validation of the PR#1505-Projects at user side but is not yet under CMS:                                                |  |

|      | PR#1505-Projects [PROXIMA] prng_set_BP2 is faulty.                                                                                                           |  |

|      | BSP v1.3.4 upgrades/fixes :                                                                                                                                  |  |

|      | BSP v1.3.4 is a patch delivered to Rapita integration support providing an upgraded demo proxima-pak (PR#1506-Projects)                                      |  |

| V0.8 | BSP v1.3.5 upgrades/fixes:                                                                                                                                   |  |

|      | BSP v1.3.5 is an official release taking into account validated results from BSP v1.3.3 and BSP v1.3.4.                                                      |  |

|      | PR#1500-Projects [PROXIMA] partial fix by PSP modification that is no more dependent of the property file content computing at runtime the physical address. |  |

|      | PR#1505-Projects [PROXIMA] prng_set_BP2 is faulty.                                                                                                           |  |

|      | PR#1506-Projects [PROXIMA] add writing events and perf measurement to proxima-pak demo.                                                                      |  |

|      | BSP v1.4.0 upgrades/fixes :                                                                                                                                  |  |

|      | BSP v1.3.5 is an early release taking into account integration findings and new requirements for VICI step:                                                  |  |

|      | PR#1502-Projects [PROXIMA] Time Composability tool - Make install_tc fails                                                                                   |  |

| V0.9 | PR#1507-Projects [PROXIMA] fix cache coherency between kernel space and user space for SCUA demo on PPC p4080 board                                          |  |

|      | PR#1511-Projects [PROXIMA] MBTA – Exec Time variability when buffer is full                                                                                  |  |

|      | PR#1512-Projects [PROXIMA] MBTA - crashes when buffer size set to 0                                                                                          |  |

|      | PR#1513-Projects [PROXIMA] MBTA - undefined reference appears at link time                                                                                   |  |

PR#1514-Projects [PROXIMA] prng\_set\_BP2 shall now support 8 bits command for 8 bits window size

PR#1515-Projects [PROXIMA] MBTA - loss of events in SMP race conditions

#### To be fixed for BSP v1.4.1:

PR#1471-Projects [PROXIMA] Time Composability tool checker shall provide apex and apexTC configuration.

PR#1499-Projects [PROXIMA] Time Composability tool - reduce Guest OS dependency to support APEX;

The Time Composabiliy Checker tool need to be used from several personalities and some have restriction about the language and available services.

The client side of the tool has been reworked to reduce dependency on personality features:

- performance analysis moved to master/server side

- new design for use of breakpoint/watchpoint so that instrumentation code will be moved to PSP driver level that is not part of application code.

### Remaining issues for industrial version:

V1.0

The late availability of FPGA hardware features and thus the full tool chain at use case level has delayed the integration phase of the PikeOS into the overall one. Then there is some discrepancy that should have been fixed earlier if integration completed earlier but currently there is no more time in the frame of the project to complete this integration phase. So at the time of providing results, there is still issues that will be fixed later, out of PROXIMA scope, in the new PikeOS software baseline: v4.2:

PR#1500-Projects [PROXIMA] Allocate MBTA resource from external provider rather than BSP.

In BSP v1.3.2 the MBTA memory resource to record events is allocated by the BSP at an address that depends on image size. So generating the valid execution image first requires to run a first try, get the allocated area from PSP message on console and modify property accordingly in the integration project.

With BSP v1.4.0 there is no more need to get a first try to get correct initialization and allocation of MBTA support, but this is not implemented in the right way for maintenance and certification purpose.

With PikeOS 4.2 and higher the MBTA support will be encapsulated into an external file provider that will allocate from memory requirement in the

### Version 1.1

| - add<br>cont<br>=> r<br>- ned<br>V1 1 were | d more gentle introduction on "how to read this document in the text of PROXIMA" rework Executive Summary section red to provide clear, itemized list of the technology features that re added to the SYSGO technology to meet the PROXIMA needs |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| corre                                       | uld appear early on in the document with pointers to where to find the responding descriptions. rework section 5, change some sections' title accordingly.  dd sub section "How to populate HW with a given seed value from test                 |

# Table of Content

| 1 Executive Summary                                            | 12            |

|----------------------------------------------------------------|---------------|

| 2 Installation                                                 | 13            |

| 3 Installation verification                                    | 13            |

| 3.1 For PikeOS BSP v1.4.0 for FPGA running with PikeOS 3.4:    | 13            |

| 3.2 For PikeOS BSP v1.4.0 for COTS P4080 running with PikeOS   | 3.4:14        |

| 4 SYSGO documentation                                          | 15            |

| Table 3.1-1 – PikeOS and ELinOS Release Notes.                 | 15            |

| Table 3.1-2 – PikeOS/ELinOS User Manuals.                      | 16            |

| Table 3.1-3 – PikeOS Reference Manuals.                        | 16            |

| Table 3.1-4 – PikeOS / ELinOS Platforms Manuals                | 17            |

| Table 3.1-5 – PikeOS Personality Manuals.                      | 17            |

| 5 PikeOS features developed for PROXIMA                        | 18            |

| 6 PikeOS tool chain specific documentation for PROXIMA         | 24            |

| 6.1 PROXIMA-FPGA board                                         | 24            |

| 6.1.1 PSP PROXIMA-FPGA TAGS                                    | 24            |

| 6.1.2 Application debug support                                | 28            |

| 6.1.2.1 Setting Hardware Breakpoint                            | 28            |

| 6.1.3 Running FPGA board in PTA mode                           | 29            |

| 6.1.4 Running FPGA board in non PTA mode                       | 29            |

| 6.2 PROXIMA-COTS board                                         | 30            |

| 6.2.1 PSP PROXIMA-COTS TAGS                                    | 30            |

| 6.2.2 Application debug support                                | 33            |

| 6.3 Board independent Tool chain UM                            | 34            |

| 6.3.1 PAK specific APIs                                        | 34            |

| 6.3.1.1 Memory allocation API                                  | 34            |

| 6.3.1.2 Timer API                                              | 34            |

| 6.3.1.3 PRNG User level support                                | 35            |

| 6.3.1.3.1.1 How to get a PRNG that differs on each reset/reb   | oot:36        |

| 6.3.1.3.1.2 How to populate HW with a given seed value from 38 | om test code: |

| 6.3.2 MBPTA support documentation                              | 39            |

| 6.3.2.1 Probabilistic Timing Analysis support                  | 39            |

| 6.3.2.1.1 PRNG support                                         | 39            |

| 6.3.2.1.2 Hardware support for PTA                             | 40            |

7

| 6.3.2.1.3 BSP implementation                               | 40                    |

|------------------------------------------------------------|-----------------------|

| 6.3.2.2 Software randomization                             | 41                    |

| 6.4 Measurement support for Timing Analysis                | 41                    |

| 6.4.1 Rapita IPOINTS                                       | 42                    |

| 6.4.2 Running kernel in TC mode                            | 44                    |

| 6.4.3 Using libsupc++                                      | 44                    |

| 6.4.4 Using math library (libm) on PikeOS 3.4              | 45                    |

| 6.4.4.1 Overview                                           | 45                    |

| 6.4.4.2 Use libm library                                   | 46                    |

| 6.4.4.3 Redefine errno variable                            | 46                    |

| 6.4.5 Running scua with software randomization             | 46                    |

| 6.4.6 Built In Test and Time Composability checker tool    | support47             |

| 6.4.6.1 Test automaton library support                     | 47                    |

| 6.4.6.2 Performance measurement support                    | 49                    |

| 6.4.6.2.1 Calibration of Execution Time Measurement        | nt52                  |

| 6.4.6.2.2 Performance counters configuration               | 52                    |

| 6.4.6.2.3 FPGA L3STAT implementation                       | 52                    |

| 1.1.1.1.1 P4080 implementation                             | 56                    |

| 6.4.7 Moving a project from PikeOS3.5 back to PikeOS 3     | 3.466                 |

| 6.4.8 ARINC653                                             | 67                    |

| 6.4.8.1 APEX P1s2                                          | 67                    |

| 6.4.8.2 APEX Time Composable                               | 67                    |

| 6.4.8.2.1 Overview                                         | 67                    |

| 6.4.8.2.2 Create a new Time Composable integration demo 67 | project using project |

| 6.4.8.2.3 Create a new Time Composable APEX app project 68 | lication using demo   |

| 6.4.8.2.4 Build and run the project demo                   | 70                    |

| 6.4.8.2.5 Configure APBRANDBANK driver (option             | nal)70                |

| 6.4.8.3 APEX NG                                            | 72                    |

| 6.4.9 RTEMS v4.10                                          | 72                    |

| 6.4.10 ELinOS                                              | 73                    |

| 6.4.11 Time Composable Queuing and Sampling port           | 73                    |

| 6.4.12 Writing measurements and events to host file        | 74                    |

| PikeOS Time Composability and MBPTA                        | 76                    |

| 7.1 | Overview    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76    |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7.2 | Safety gu   | idance elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77    |

| 7.3 | PikeOS al   | llows Cache jitter reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78    |

| 7.3 | 3.1 PikeOS  | allows Cache flush at time partition switch time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 78    |

| 7.3 | 3.2 PikeOS  | allows Cache partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 79    |

|     | 7.3.2.1 P   | ikeOS allows per core L1/L2 cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79    |

|     | 7.3.2.1.1   | PSP PROXIMA-FPGA allows per core L1/L2 cache separa 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ition |

|     | 7.3.2.1.2   | PSP P4080 has per core L1/L2 cache separation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79    |

|     | 7.3.2.2 P   | ikeOS allows L2 cache partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 79    |

|     | 7.3.2.2.1   | PROXIMA -FPGA does not support L2 cache partitioning.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 79    |

|     | 7.3.2.2.2   | P4080 does not support L2 cache partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80    |

|     | 7.3.2.3 P   | ikeOS allows non-cacheable L3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80    |

| 7.3 | 3.3 PikeOS  | allows cache history impact reduction at user level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80    |

|     | 7.3.3.1 N   | Noving PikeOS kernel code and datato a no cache area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80    |

|     | 7.3.3.1.1   | Using dedicated Sratchpad/Static RAM with PikeOS 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80    |

|     | 7.3.3.1.2   | Running kernel in no cache area from PSP TAG option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81    |

|     | 7.3.3.2 N   | Ioving pssw level code and data to no cache area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 81    |

|     | 7.3.3.3 N   | In a source of the state of the | 81    |

|     | 7.3.3.3.1   | Moving APEX-TC code/data to no-cache area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 81    |

|     | 7.3.3.3.2   | Moving Native code/data to no-cache area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82    |

|     | 7.3.3.3.3   | Moving RTEMS code/data to no-cache area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 83    |

|     | 7.3.3.3.4   | Moving ELinOS code/data to no-cache area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83    |

| 7.3 | 3.4 PikeOS  | provides support for cache randomization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84    |

|     | 7.3.4.1 H   | Tardware Cache Randomization support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 84    |

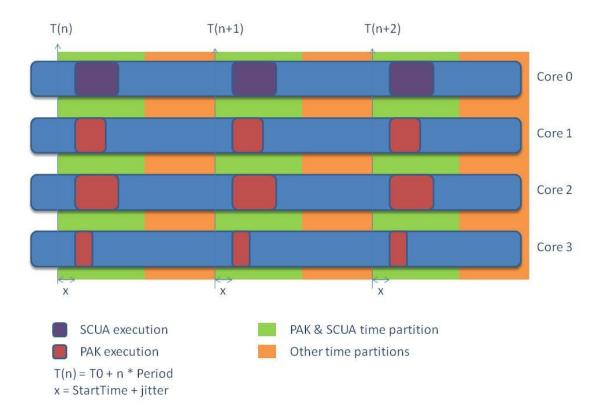

|     | 7.3.4.1.1   | Changing Hardware seed at Partition switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84    |