# D2.12 Evaluation report on research-oriented software-only multicore solutions Version 1.0

# **Document Information**

| Contract Number      | 611085                                             |

|----------------------|----------------------------------------------------|

| Project Website      | www.proxima-project.eu                             |

| Contractual Deadline | m36, 31-September-2016                             |

| Dissemination Level  | PU                                                 |

| Nature               | R                                                  |

| Authors              | Leonidas Kosmidis (BSC), Tullio Vardanega (UPD)    |

| Contributors         | Enrico Mezzetti (UPD/BSC), Davide Compagnin        |

|                      | (UPD), Luca Bonato (UPD), David Morales (BSC), Ed- |

|                      | uardo Quinones (BSC)                               |

| Reviewer             |                                                    |

| Keywords             | RTOS, Timing Composability, Software Randomisa-    |

|                      | tion, Multicore, PTA                               |

#### Notices:

The research leading to these results has received funding from the European Community's Seventh Framework Programme [FP7/2007-2013] under grant agreement no 611085.

© 2013 PROXIMA Consortium Partners. All rights reserved.

# **Change Log**

| Version | Description of change              |

|---------|------------------------------------|

| v0.1    | Initial Draft for internal review  |

| v0.2    | Internal review comments addressed |

|         |                                    |

|         |                                    |

|         |                                    |

|         |                                    |

|         |                                    |

|         |                                    |

|         |                                    |

|         |                                    |

# **Contents**

| $\mathbf{E}_{2}$ | Executive Summary 5 |         |                | 5                                            |          |

|------------------|---------------------|---------|----------------|----------------------------------------------|----------|

| 1                | Intr                | oducti  | on             |                                              | 6        |

| 2                | Res                 | earch-c | riented RTC    | OSes                                         | 8        |

|                  | 2.1                 | FPGA    | COTS           |                                              | 10       |

|                  |                     | 2.1.1   | Task Manager   |                                              | 11       |

|                  |                     | 2.1.2   | Evaluation     |                                              | 12       |

|                  |                     | 2.1.3   | Semaphore M    | anager                                       | 13       |

|                  |                     | 2.1.4   | Evaluation     |                                              | 14       |

|                  |                     | 2.1.5   | Event Manage   | er                                           | 19       |

|                  |                     | 2.1.6   | Evaluation (li | mited to per-core events)                    | 21       |

|                  |                     | 2.1.7   | Utilities      |                                              | 23       |

|                  | 2.2                 | AURI    |                |                                              | 26       |

|                  |                     | 2.2.1   | System Config  | gurations                                    | 26       |

|                  |                     | 2.2.2   | Cyclic Tasks . |                                              | 28       |

|                  |                     | 2.2.3   | Sporadic Task  | S                                            | 29       |

|                  |                     | 2.2.4   | Time-Compos    | able Implementation                          | 30       |

|                  |                     | 2.2.5   | Evaluation by  | PAKs                                         | 33       |

|                  |                     | 2.2.6   | Using Erika-T  | °C                                           | 37       |

| 3                | Soft                | word I  | andomisatio    | n                                            | 39       |

| J                | 3.1                 |         |                |                                              | 40       |

|                  | 5.1                 | 3.1.1   |                | escription of Dynamic Software Randomisation | 40       |

|                  |                     | 3.1.1   | 0              | scription of Dynamic Software Randomisation  | 40       |

|                  |                     | 3.1.2   |                | Dynamic Software Randomisation Port at m18   | 40       |

|                  |                     | 5.1.2   | and their solu | · ·                                          | 41       |

|                  |                     |         |                | cation Scheme:                               | 41       |

|                  |                     |         |                | amic Memory Consumption                      | 43       |

|                  |                     |         |                | lom Cache line Selection:                    | 43       |

|                  |                     | 3.1.3   |                |                                              | 44       |

|                  |                     | 0.1.0   |                | e line Randomisation                         | 44       |

|                  |                     |         |                | ory overheads                                | 49       |

|                  |                     |         |                | r vs Lazy relocation                         | 52       |

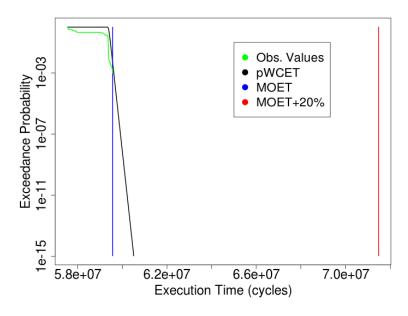

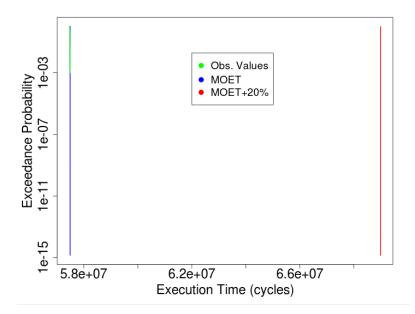

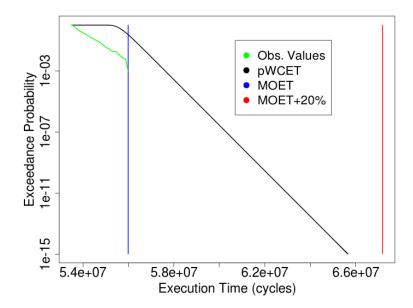

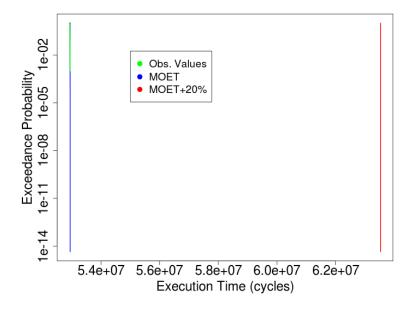

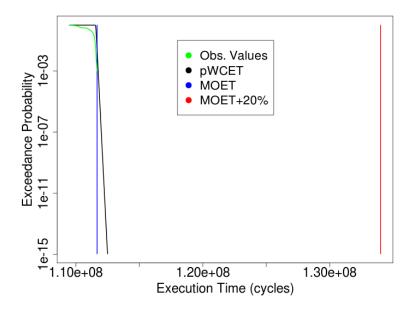

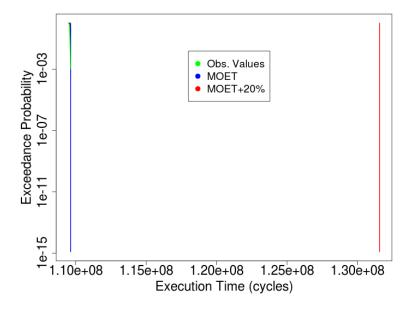

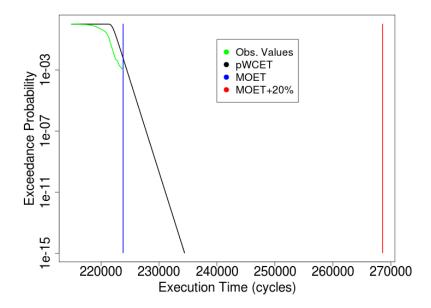

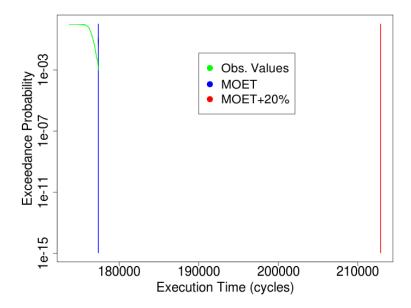

|                  |                     |         | _              | CET Estimations                              | 54       |

|                  |                     |         | -              | age Performance                              | 54       |

|                  |                     |         |                | t distributions in isolation                 | 55       |

|                  | 3.2                 | P4080   |                |                                              | 58       |

|                  | 0.2                 | 3.2.1   |                | S                                            | 58       |

|                  |                     | 3.2.2   | 0              |                                              | 58       |

|                  |                     | 0.4.4   |                | te line Randomisation                        | 59       |

|                  |                     |         |                |                                              |          |

|                  |                     |         |                | ory Overheads                                | 111      |

|                  |                     |         |                | ory Overheads                                | 62<br>64 |

|                  | 3.3   | AURI    | X                                                         | 74 |

|------------------|-------|---------|-----------------------------------------------------------|----|

|                  |       | 3.3.1   | High Level Description of Static Software Randomisation/- |    |

|                  |       |         | TASA at m18                                               | 74 |

|                  |       | 3.3.2   | Limitations of TASA at m18 and their solutions            | 76 |

|                  |       |         | 3.3.2.1 typedef and dependent declarations                | 76 |

|                  |       |         | 3.3.2.2 Vendor-Specific/Non-ANSI Extensions               | 76 |

|                  |       |         | 3.3.2.3 preTASA                                           | 77 |

|                  |       | 3.3.3   | Evaluation                                                | 77 |

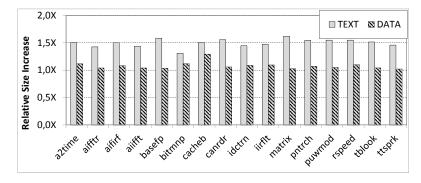

|                  |       | 3.3.4   | Cache line Randomisation                                  | 78 |

|                  |       | 3.3.5   | Memory Overheads                                          | 79 |

|                  |       | 3.3.6   | Average Performance                                       | 81 |

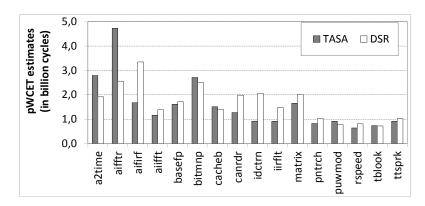

|                  |       | 3.3.7   | pWCET Estimations                                         | 82 |

| 4                | Cor   | nclusio | n                                                         | 83 |

| A                | crony | yms ar  | nd Abbreviations                                          | 84 |

| $\mathbf{R}_{0}$ | efere | nces    |                                                           | 85 |

# **Executive Summary**

This deliverable reports on the research-oriented part of the work performed in the task T2.6 as well as the refinement of the tasks T2.3 and T2.4 as reported in D2.5, D2.6 and D2.7 at m18.

In particular, this document presents the updates achieved in the last reporting period in the research-oriented work carried out in WP2, for rendering time-composable the research-oriented RTOSes considered in PROXIMA, and for providing software-only solutions to timing randomisation for the COTS processors targeted in the project. The material presented in document includes the evaluation of all proposed solutions on the multi-core processors of interest.

The research-oriented software stacks consists of three distinct RTOSes, one for each COTS platform (FPGA, P4080, AURIX) and two Software Randomisation tool chains, one dynamic variant (i.e., with randomization performed at run time) for the FPGA and the P4080, and one static variant (i.e., with randomization performed at compile time on a per executable basis) addressing the specific needs of the AURIX processor and of its application domain.

The combination of the elements of this software stack on each of the target platforms provides the desired properties required to perform MBPTA analysis on COTS platforms namely timing composability and time-randomisation.

This document is organized as follows: Section 1 provides a general introduction to this line of action in the wider context of the project; Section 2 presents the implementation and evaluation work performed on the research-oriented RTOSes; Section 3 illustrates all software randomisation tool chains for all processor targets, along with the corresponding evaluation results, obtained with synthetic kernels (programs) or benchmarks. The use of these technologies in the industrial case studies is presented in the WP4 reports due at M36, in particular D4.8. Section 4 concludes the document.

# 1 Introduction

In order to address the complexity of modern architectures, the PROXIMA approach has been centred around capturing, understanding and taming sources of jitter (SoJ).

In the base case of a single task executing on a single-core architecture without an operating system, the only identified SoJ arises from the memory layout of the software and its interaction with cache memory hierarchies. Previous studies have shown that the **memory layout** impacts significantly the execution time [12] even in the presence of a single cache used for instructions [13]. In order to control this SoJ, we employ software randomisation means in order to randomise the memory layout of the task. This further provides a time-randomised behaviour in the task's execution time, with independent and identically distributed (i.i.d.) characteristics, which enables the use of MBPTA. This enables arguing on the jitter caused by the cache in probabilistic terms, giving each potential cache layout a probability of appearance [8].

In more complex and more realistic scenarios involving a real-time operating system (RTOS), the operating system itself adds other SoJ to the problem domain. When the task calls an RTOS service, the RTOS activity alters the hardware state and especially the cache contents, that may cause a severe impact on the task timing after the service has been completed. This complicates the timing analysis process since it requires that the application has to be analysed together with the RTOS. As a solution to this problem, we use an RTOS design which provides constant-time services, thus enabling timing composability. This means that the application and the RTOS can be analysed in isolation and each component represents a simple additive factor in the total execution time.

Moving towards a single-core system with multiple tasks, other SoJ stem from the interactions between the tasks, which time-share the processor resources. The most evident example of that kind is **preemption**, which we address by modifying the RTOS scheduling to provide run-to-completion semantics.

Finally, in a system with multiple tasks and multiple CPUs, there are additional SoJs. Some arise from task migration that introduces various types of delays (at the ends of the migration and, potentially for all cores owing to cache pollution effects in memory) and considerably complicates timing analysis. This issue is addressed by modifications in the scheduling and adoption of partitioned solutions, which favours time composability. Further SoJ emerge from hardware resource sharing between tasks executing in different processors, such as shared buses and caches. For resources that provide hardware features for segregation such as partitioning in shared caches, we employ them in order to create per core partitions to enable time composability. On the other hand, for resources without such features as shared buses, we rely on the time-randomised behaviour provided by software randomisation methods in order to probabilistically characterise the worst-case behaviour of each task (see D3.8).

Overall, when all these solutions are combined together, they enable the use of MBPTA on the multicore COTS platforms used in PROXIMA and allow yielding time-composable estimates, while they further help keeping the whole analysis process simple.

In this deliverable report we provide updates on the employed solutions designed to address the SoJ summarised above in the last reporting period of the project, and their experimental evaluation.

In the presentation of this material, we follow a two-level organisation: Chapter 2 describes the RTOS features devised in the project to obtain time-composable execution behaviour in the RTOS, for the research-oriented RTOSes considered in PROXIMA, and presents the experimental evaluation of the goodness of fit of the proposed modifications; Chapter 3 focuses on software randomisation solutions, their modifications and their experimental evaluation. Each chapter is further subdivided per target platform to address the specific requirements in each case.

# 2 Research-oriented RTOSes

PROXIMA set itself the ambition of pursuing its overall goals across two parallel lines of software development action: one centred around industrial-quality technology, which warranted faster exploitation paths; the other centred research-type technology prototypes, which were meant to explore more innovative solutions with more agility, risking less resistance friction than with industrial-quality product baselines.

This ambitious plan rested on two critical assumptions:

- sufficient availability of the processor boards to both development groups (the industrial-ready one and its research-type parallel) for the port and the refinement of their respective technology.

- sufficient energy at the industrial users to port their use cases and repeat the MBPTA experiments on both technology solutions.

As the project had a clear, undisputed slant on industrial exploitation, precedence was systematically given to the industrial-quality technology development, both in access to the processor boards and in interacting with the industrial users in WP4. This arrangement caused two distinct contingencies.

- 1. The exposure of the research-type prototypes to the industrial use cases was limited to the automotive use case, thanks to the fact of it having no industrial-ready RTOS solution to consider.

- 2. The P4080 processor boards quickly became a scarce resource, which owing to the extraordinary complexity of internal architecture and its very steep learning curve could not conceivably be physically time shared in short rounds, but had to reside at the designated user for long time spans. Remote access was also not a viable back-up route as porting, debugging and consolidating an RTOS on a processor board need numerous and very fast turn-around runs, which cannot be conceivably warranted with a limited-time remote-access resource.

As a result of the above contingencies:

- The development of the research-type RTOS for the P4080 (which was a task of UPD) was discontinued before its port could reach an implementation status apt for worthwhile experimental evaluation owing to insufficient availability of the processor board and the inability of the WP4 industrial member that was the intended user of it to devote energy for the port of an (avionics) application to it.

- The development of the research-type RTOS targeted for the FPGA COTS (also in charge to UPD) was successfully completed, but its evaluation was performed outside of PROXIMA, as the WP4 industrial member that was the intended user of it was unable to devote energy to adapting a (space) application to it. The proceedings of that line of action are discussed in Section 2.1.

For this reason, this report does not include material on the research-type RTOS destined for use on the P4080. The UPD effort detracted from the RTOS development for the P4080 was transferred to supporting the development and execution of the automotive use case on the AURIX processor, in addition to bringing to completion the time-composable adaptations of Erika Enterprise, the research-type RTOS selected to that end. The proceedings of that line of action are discussed in Section 2.2.

# 2.1 FPGA COTS

The research-oriented that was singled-out in PROXIMA for use with the FPGA COTS was the SMP (symmetric multiprocessor) version of RTEMS<sup>1</sup>, owing to its industrial relevance to ADS and to the European Space Agency) in the space domain.

The expectation, for PROXIMA and for UPD, was that ADS would be able to replicate some of their use-case experiments using an RTEMS-SMP based execution stack and therefore provide feedback on the usefulness of the modifications developed to it by UPD in PROXIMA, with the intent to facilitate the use of the PROXIMA timing analysis solutions for the FPGA COTS target. Unfortunately, this proved not possible as ADS spent all of its available energy to complete their planned set of use-case experiments using the industrial RTOS option. Luckily however, the proceeds of the work done in WP2 on RTEMS-SMP are going to be reflected back in the RTEMS-SMP refinement project that is being conducted by the European Space Agency.

In this section we provide an update on the evaluation of the effectiveness of the modifications that UPD developed to the RTEMS-SMP code-base to improve the composability of its timing behaviour and therefore have very small, if not null, perturbation effects on the measurement observations performed by the user on the application programs subject of worst-case execution time analysis.

RTEMS was a big and complex operating system. Its SMP version is considerably bigger and more complex. Interestingly, in the process of developing the SMP adaptations of RTEMS a number of modifications to the way of working of single-CPU RTEMS had to be implemented, which culminated in the slow and complex process of removing the so-called "giant lock" that the old code-base used to protect access to internal data against reentrant code.

The process of rendering RTEMS-SMP fully time-composable was not sustainable within PROXIMA, which had the energy to focus only on a central subset of services. To prove the goodness of fit of our modifications (or re-implementations), we compare the timing behaviour of our modified version of RTEMS-SMP<sup>2</sup> against the original version of it.

To give more room to the presentation of the evaluation results, we omit discussing details of the implementation, whenever that omission does not negatively affect the reader's understanding.

RTEMS offers the end user a lot of freedom, which however often is a double-edged sword. To prevent misuse of kernel primitives and to ensure conformance with the intention of our changes, we describe how those primitives should be used to obtain sound and analysable applications.

Our changes to RTEMS have not been merged yet in the master branch of RTEMS at the time of this writing. We are pursuing that merge outside of PROXIMA. For the purposes of this report we describe how to obtain a working version of our modified RTEMS code-base.

Unless otherwise stated, our evaluation experiments have been performed in the

<sup>&</sup>lt;sup>1</sup>RTEMS was originally designed for single-CPU processors and, until very recently, lacked a solid version fit for working on multi-core processors. UPD participated in the initiative the created the first SMP code-base for RTEMS, under funding from the European Space Agency.

<sup>&</sup>lt;sup>2</sup>In the following we use the RTEMS acronym as a synonym for RTEMS-SMP.

LEON3 PROXIMA FPGA<sup>3</sup> without randomisation. We did indeed perform some initial experiments to evaluate the impact of hardware randomisation on our modifications for time composability; we could not complete that evaluation in the time-frame of PROXIMA, but we plan to continue it outside of the project. We chose however to not include those initial results in this report.

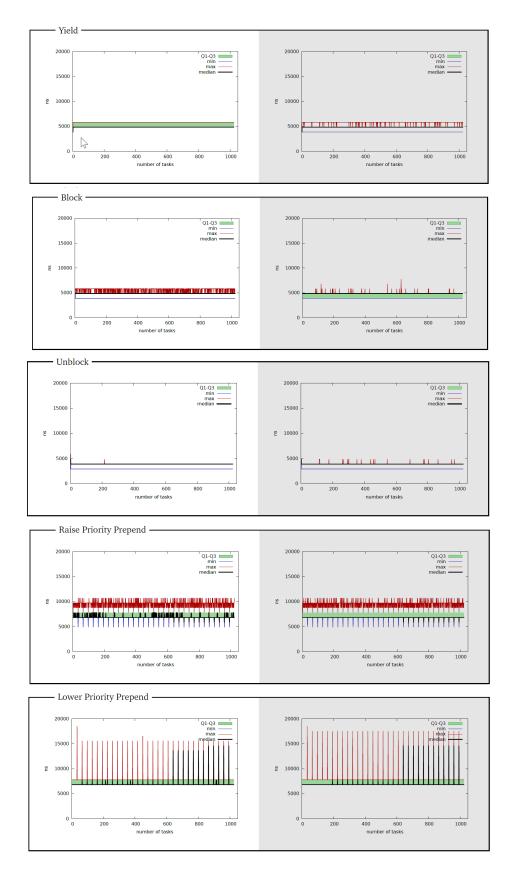

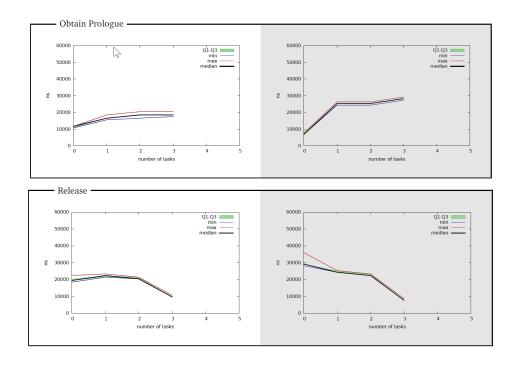

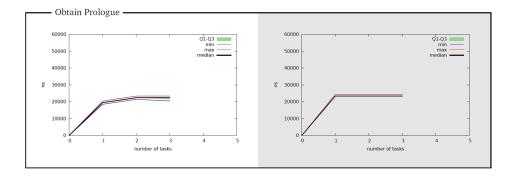

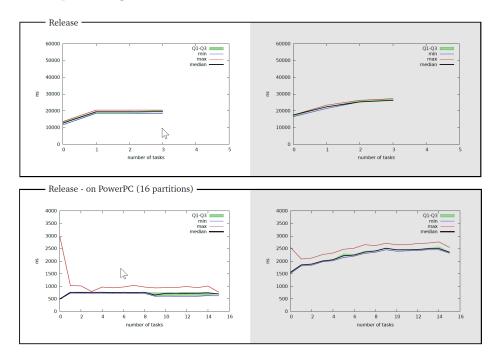

Unless otherwise stated, our experimental results are presented with comparative charts. All numerical values are reported in nanoseconds. The left part of each chart depicts the measurements from our modified version, while the right chart (with gray background) depicts the measurements obtained with the original version of RTEMS (dated May 10th, 2015 at commit be0366bb62ed4a804725a484ffd73242cd4f1d7b). Each chart provides four pieces of information: the minimum observed value (blue line), the maximum observed value (red line), the median (black thick line) and the region spanning from the first and third quartile (green region)<sup>4</sup>. All measurements have been taken with lightweight ad-hoc tracing support developed in house.

# 2.1.1 Task Manager

The task manager comprises all those directives related to the management of tasks. Table 1 reports the primitives that we considered in our effort, which may induce significant runtime overhead, and are related to scheduling decisions. Interestingly, the first four primitives in Table 1 should not be used during runtime, but only during the initialisation phase of the system. Yet, their operation has repercussions on the runtime behaviour.

Table 1: Selected primitives of the Task Manager

| TASK_CREATE     |

|-----------------|

| TASK_IDENT      |

| TASK_SELF       |

| TASK_START      |

| TASK_SUSPEND    |

| TASK_RESUME     |

| TASK_WAKE_AFTER |

The runtime behaviour and overhead caused of such primitives is strictly determined by the scheduler used in the application. In order to cause those primitives to exhibit a time-composable behaviour, it is opportune to choose among the options supported by the RTEMS code-base a scheduling algorithm that can reproduce – in the SMP environment – the same execution conditions given in a single-CPU processor, which is partitioned fixed-priority scheduling (P-FP). In Listing 1 we show a possible configuration for an application that must run in a system with CPU\_COUNT processors and where each partition has PRIO\_COUNT priority levels.

Listing 1: Example configuration for a P-FP system

#define CONFIGURE.SMP\_MAXIMUM\_PROCESSORS CPU\_COUNT #define CONFIGURE\_SCHEDULER\_PRIORITY\_SMP

$<sup>^3{\</sup>rm The~LEON3~PROXIMA~FPGA}$  platform is a system-on-chip with four LEON3 SPARC V8 processors running at 80MHz, with 4x4KiB Data Cache and 4x4KiB Instruction Cache.

<sup>&</sup>lt;sup>4</sup>This is where 50% of the samples (centred around the median) are located.

As that the task set is statically defined at design time, performing a dynamic search of a task while the system is running based on the alphanumeric name of the task is definitely not a sound solution. The identifier of each task is produced as side effect of the TASK\_CREATE primitive. It is therefore opportune to save that identifier in a specific location so that every other task that needs it can find it directly without using the TASK\_IDENT primitive.

In order to create a periodic task, the user should call the TASK\_WAKE\_WHEN primitive, as depicted in Listing 2. That primitive should be used to set the time of the next release of the current task, and the call to this primitive results in the task to suspend its execution.

Listing 2: Body of a periodic task

```

static void periodic_task(rtems_task_argument arg){

while(true){

//... do some work ...

rtems_task_wake_when(...);

}

```

The implementation of sporadic tasks should be based on the TASK\_WAKE\_WHEN primitive in order to guarantee the minimum inter-arrival time. As shown in Listing 3, after the wait there should be a barrier that blocks the execution of the task until some external trigger arrives. The usage of events for this purpose is further discussed later in this section.

Listing 3: Body of a sporadic task

```

static void sporadic_task(rtems_task_argument arg){

while(true){

//... do some work ...

rtems_task_wake_when(...);

rtems_event_receive_sporadic_activation(...);

}

}

```

#### 2.1.2 Evaluation

We chose to not directly evaluate the primitives, but to concentrate instead on the internal operations of the scheduler:

- yield (yielding a task)

- block (blocking a task)

- unblock (unblocking a task)

- priority prepend (changing the priority of a task)

- priority append (changing the priority of a task).

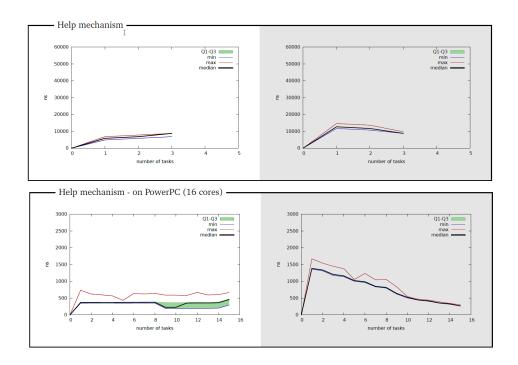

In all cases, we varied the number of tasks in the system (the variation is shown on the X axis of the chart in Figure 1) and observed that the macroscopic behaviour of those internal operations did not change after our modifications. In fact, the original implementation of the scheduler was sufficiently time composable of its own. The good news however, was that the modifications we applied to enable the implementation of novel, SMP-capable, synchronisation problem for sharing global resources across tasks pinned to cores (which we discus separately later in this report) did not negatively affect the good properties of the scheduler.

# 2.1.3 Semaphore Manager

The semaphore manager comprises all those directives related to the management of semaphores. Table 2 reports the primitives that we considered in PROXIMA.

Table 2: The semaphore manager operations

| SEMAPHORE_CREATE  |

|-------------------|

| SEMAPHORE_IDENT   |

| SEMAPHORE_OBTAIN  |

| SEMAPHORE_RELEASE |

| SEMAPHORE_FLUSH   |

We focused only on those primitives that can actually produce runtime overhead. In this regard, the first two primitives of Table 2 should not be used during run time, but only at system initialisation. Our focus on this group of primitives was entirely centred on the implementation of the SMP-capable semaphore support known as MrsP [4].

RTEMS exposes several types of semaphores through the same interface. A specific type of semaphore is selected based on the input parameters that the user supplies to the SEMAPHORE\_CREATE primitive. Listing 4 shows the parameters to use to issue the creation of an MrsP semaphore.

Listing 4: Creation of an MrsP Semaphore

```

rtems_semaphore_create(

name_of_the_semaphore,

1, /*mustbeone*/

RTEMS_MULTIPROCESSOR_RESOURCE_SHARING|RTEMS_BINARY_SEMAPHORE,

ceiling_priority, /* initial and temporary ceiling priority for all

partitions. Should be updated locally with

rtems_semaphore_set_priority */

&resource_id);

```

An MrsP semaphore is a way to synchronise several tasks such to consistently use some shared object in mutual exclusion. If such tasks reside in the same partition, then the behaviour of MrsP is the same as the well-known ceiling semaphore SRP (uniprocessor Stack Resource Protocol), in its adaptation for single-CPU fixed-priority scheduling systems [3]. If such tasks reside in different partitions, then MrsP provides a helping mechanism that is crucial to reduce the wait time of tasks pending on the semaphore.

Obtaining and releasing an MrsP semaphore does not come for free. In case the critical section is very short, it may be more convenient to make critical sections non-preemptive. In an SMP environment, this means disabling dispatching in the specific partition and then acquiring a spin-lock (to prevent the parallel execution of the critical section from a task in a different partition). In RTEMS, this can be

achieved by enclosing the critical section between \_Thread\_Disable\_dispatch and \_Thread\_Enable\_disaptch primitives. Notably, however, the spinlock acquired in that way is the notorious "giant lock" that protects most of the kernel structures of RTEMS (from reentrant calls in the single-CPU version and from parallel calls in the initial SMP version. At the time of this writing, an ESA-funded activity is currently removing the giant lock from the SMP codebase). It therefore follows that the use of such primitives can lead to delays in the execution of the kernel primitives in any partition, which is a rather bad perturbation.

We reckon that for critical sections longer than 30  $\mu s$  it is advisable to use our MrsP semaphores. Indeed, this maximum duration that we have observed that is spent inside the kernel in non-preemptive mode while trying to acquire or release an MrsP resource. After obtaining the resource, the task remains preemptive (while running at ceiling priority), meaning that all other tasks in the same partition can be unconditionally delayed at most for the time spent by that tasks while being non-preemptive inside the SEMAPHORE\_OBTAIN primitive. Using non-preemptive critical sections longer than 30  $\mu s$  means that all the tasks in the same partition will unconditionally suffer for the whole execution of the critical section.

For MrsP semaphores, the SEMAPHORE\_FLUSH operation is not defined, hence not used.

At the time of this writing, there are the following limitations with the time-composable version of MrsP:

- an application can use at most 32 MrsP semaphores. This is a temporary limit since the time-composable version is based on bit-masks of uint32\_t (therefore 32 bits). This means that the macro CONFIGURE\_MAXIMUM\_MRSP\_SEMAPHORES cannot be greater than 32.

- some scheduling primitives have been changed in order to fit our version of MrsP. Not all the primitives of all schedulers have been changed. The only scheduler known to work for sure with our implementation of MrsP is the Deterministic Priority SMP Scheduler.

- our version of MrsP does not support timeouts (this has been an intentional choice).

- our version of MrsP forbids the use of blocking operations. For reference, the most common blocking operations are:

- rtems\_rate\_monotonic\_period

- o rtems\_task\_wake\_after

- o rtems\_task\_wake\_when

- o rtems\_task\_suspend

- rtems\_task\_set\_scheduler

- rtems\_event\_receive

#### 2.1.4 Evaluation

We used five tests to perform comparative measurements on the following primitives:

- Obtain: the body of the lock procedure, until either the resource is locked (when the resource is free) or the task start spinning (when the resource is already occupied). In the latter case, we omit our results for the time spent inside the kernel from the time a task stop spinning to its actual exit from the SEMAPHORE\_OBTAIN primitive since there are virtually no operations to perform.

- Release: the body of the unlock procedure.

- Help: the body of the helping protocol, called whenever a task holding a resource is preempted. This primitive must understand if and where are the tasks that can help the preempted resource holder.

Test 1 (see Figure 2) Goal: to determine the cost to obtain and release a resource while all pending tasks are active. The x-axis variation represents how many tasks are pending at the time of the obtain and release operation.

When the resource is free (x = 0), there are less operations to perform in order to obtain it. Otherwise, the time is mostly constant.

Our version of the protocol has a nearly-constant time behaviour, while the original version is linearly dependent on the number of tasks pending on the resource.

Test 2 (see Figure 3) Goal: to determine the cost to obtain an already occupied resource while its owner is not executing. The X-axis variation in Figure 3 represents the number of previous pending requests, whose tasks are not available to offer help (i.e., tasks that have already requested the resource and started spinning, but have been preempted since).

The chart shows no measurements for X=0, as this point in time captures the first task to request the resource, when the resource is free, which obviously obtains it at no cost. The behaviour we observe is similar to the one seen for Test 1, except that in this case we have to make a scheduling decision to launch the helping protocol when needed.

Figure 1: Comparative evaluation for Task Manager primitives after our modifications

Figure 2: Comparative evaluation for the Semaphore Manager primitives after our modifications: Test 1

Figure 3: Comparative evaluation for the Semaphore Manager primitives after our modifications: Test 2

Test 3 (see Figure 4) Goal: to determine the cost to release a resource and make the next-in-line pending task the new resource holder. All tasks are pending. The X-axis variation represents the number of pending tasks that are active (i.e., that are spinning). Specifically, the active tasks are counted backward, that is, if there are 2 active task, they are the last 2 tasks that have requested the resource. Therefore, while upgrading the first pending task to the role of resource owner, the release procedure must find the processor (if any) in which make the new holder execute. Samples are generated from task 0.

Figure 4: Comparative evaluation for the Semaphore Manager primitives after our modifications: Test 3

Our version of the protocol is mostly constant, while the original version is linearly dependent to the number of tasks pending on the resource. This is best seen on a platform where a higher degree of parallelism is available. The next chart represents the evaluation performed on a PowerPC with 16 cores.

Test 4 (see Figure 5) Goal: to determine the cost to select the task that must help the resource holder when it preempted. All tasks are pending.

The X-axis variation represents the number of pending tasks that are active (i.e., that are spinning). Specifically, the active tasks are counted backward, that is, if there are 2 active tasks, they are the last 2 tasks that have requested the resource. The chart shows no measurements for  $\mathbf{x}=0$ , as that point in time represents a lock-holder task that cannot help itself because it is alone in the waiting queue. Our version of the protocol exhibits a nearly-constant timing behaviour, while the original version is linearly dependent on the position of the spinning task that can offer help inside the FIFO queue of the MrsP resource. This improvement effect is best seen on a platform with a higher degree of parallelism than PROXIMA's FPGA

Figure 5: Comparative evaluation for the Semaphore Manager primitives after our modifications: Test 4

COTS. We show that in the lower chart in Figure 5, which plots the evaluation results obtained on a PowerPC with 16 cores.

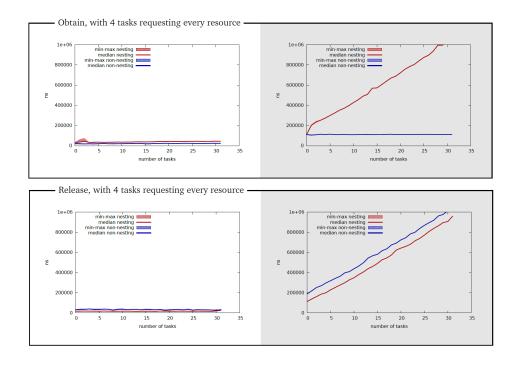

Test 5 (see Figure 6) Goal: to determine the cost to obtain and release a resource when tasks are transitively nesting resources.

Specifically, there are 2 tasks nesting resources (on CPU 0 and on CPU 3). These two tasks nest exactly 2 resources each. The other tasks (if any) only request one resource that is already being locked by the nesting task. Eventually, a chain of 32 nested resources forms, where the first task requesting resource 0 (at point X=0 in the chart) must wait for the last task that requested resource 31 (x=31).

Both versions do not have a time-constant behaviour. Our version is better, as it linearly depends on the depth of nesting, whereas the old version linearly depends on both the depth of nesting and the number of tasks in the wait queue (thus having two orthogonal traversals).

Interestingly, these considerations hold for both primitives. Furthermore, in the old version, not only the tasks that have nested resources pay the price of a high overhead, but also the tasks do not take any part in resource nesting pay a high toll too. This is in accord with what we saw in Test 3: the release of an MrsP resource in the original version of the protocol is linear dependent to the number of tasks that wait (directly or indirectly through nesting) on the same resource.

#### 2.1.5 Event Manager

The event manager comprises all those directives related to the signal passing. Table 3 reports the RTEMS original primitives we considered initially.

In the original semantic of RTEMS, a task can wait simultaneously for several

Figure 6: Comparative evaluation for the Semaphore Manager primitives after our modifications: Test 5

Table 3: Notable primitives of Event Manager

## EVENT\_RECEIVE EVENT\_SEND

events or a task can wait for one specific event. While this approach can support a variety of scenarios (e.g., simulate complex barriers based on AND/OR conditions), such a large extent of expressivity can cause problems for time-predictable real-time applications. We therefore largely streamlined the supported semantics: events are used solely to prompt the release of a sporadic task (see Listing 3 for the skeleton of a sporadic task envisioned within our semantics) or to synchronise two tasks on a simple event/notification/signal (e.g., wait for an external command, wait for the completion of an action). Other kinds of synchronisation must be achieved with other means (e.g., semaphores).

Interestingly, events are used a lot inside the kernel of RTEMS: we did not take the risk to directly change them in order to conform them to our stricter semantics. Instead, we chose to provide a novel interface to send or receive events, which would be free from intersections with the old RTEMS events. Table 4 reports the interface of the event manager that we defined.

Table 4: Revisited set of Event Manager primitives

| EVENT_RECEIVE_LOCAL               |

|-----------------------------------|

| EVENT_SEND_LOCAL                  |

| EVENT_RECEIVE_SPORADIC_ACTIVATION |

| EVENT_SEND_SPORADIC_ACTIVATION    |

As a first step, we differentiate between events sent to tasks residing in the same

partition (per-core events) and events sent to tasks residing in a remote partition (extra-core events). We do this because, in our scenario, when a task sends an event, it means that it is completing its execution: in our scenario an event is sent only as the last action of a thread, to notify that its work is complete and to resume the work of someone else, in the form of a classic work pipeline.

If the event is a per-core event, this signal will put a task of the same partition in the ready state: since the sending task is going to complete, it can directly manage the scheduling decision for the receiving task since such overhead must be paid in any case by the partition. However, when a task sends an extra-core event, we want to avoid the senders partition to pay for the overhead of the scheduling decision on the remote partition. In this case, we want the event to be asynchronous: the overhead produced by the scheduling decision must be paid by the remote partition. The only permitted extra-core events are those that cause the release of a sporadic task.

The evaluation and implementation of our customised events is still ongoing. With the supplied patch of RTEMS, we implemented support for per-core events:

- EVENT\_SEND\_LOCAL

- EVENT\_RECEIVE\_LOCAL

Listing 5 shows the interface that we provide for such events (this interface is identical to the one in the original RTEMS manager).

Listing 5: Per-core events API

```

rtems_status_code rtems_event_send_local(

rtems_id    id,

rtems_event_set    event_in

);

rtems_status_code    rtems_event_receive_local(

rtems_event_set    event_in,

rtems_option    option_set,

rtems_interval    ticks,

rtems_event_set    *event_out

);

```

At the time of this writing, the extra-core events are still not implemented inside the kernel, but a proof-of-concept implementation have been developed and trialled successfully. Listing 6 shows the interface we envisage for those events.

Listing 6: Extra-core events API

```

rtems_status_code rtems_event_send_sporadic_activation(

rtems_sporadic_event event

);

rtems_status_code rtems_event_receive_sporadic_activation(

rtems_sporadic_event event

);

```

# 2.1.6 Evaluation (limited to per-core events)

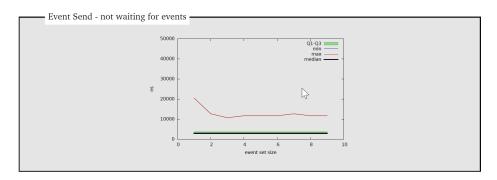

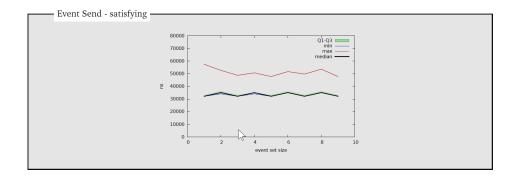

In this group of evaluation experiments we only considered the original SMP-version of the RTEMS because its codebase was good enough to only require very minor adaptations for our project, with virtually null effect on the execution-time behaviour. The X-axis variation in the charts represents the size of the event set: through a single primitive it is possible to send/receive simultaneously several events. Events set are built with bitwise-or of bit-masks.

Test 1 (see Figure 7) Goal: to determine the cost to send an event to a thread that is not waiting for any event.

Figure 7: Comparative evaluation for the Event Manager primitives after our modifications: Test 1

What we observe in this case is essentially constant-time behaviour.

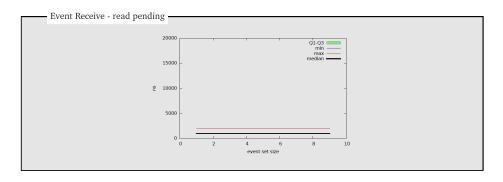

Test 2 (see Figure 8) Goal: to determine the cost to send an event to a thread that is waiting for an event, but without satisfying the condition on which the receiver is pending.

Figure 8: Comparative evaluation for the Event Manager primitives after our modifications: Test 2

Also in this case we see constant-time behaviour.

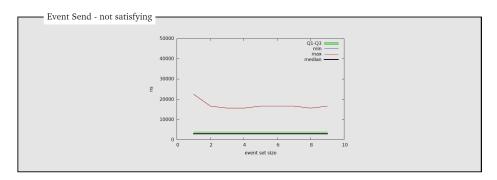

Test 3 (see Figure 9) Goal: to determine the cost to send an event to a thread that is waiting for an event, and satisfying the condition on which the receiver is pending.

Again, we see constant-time behaviour, but also greater overhead because the kernel has to unblock the receiver.

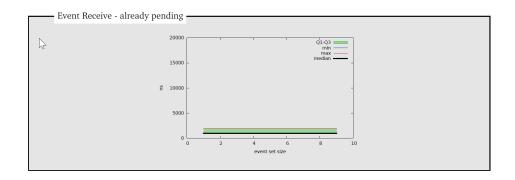

Test 4 (see Figure 10) Goal: to determine the cost to read the events pending on a task.

Not surprisingly, given the nature of the primitive, here we see perfect constanttime behaviour.

Figure 9: Comparative evaluation for the Event Manager primitives after our modifications: Test 3

Figure 10: Comparative evaluation for the Event Manager primitives after our modifications: Test 4

Test 5 (see Figure 11) Goal: to determine the cost to receive an event that is already pending on the task.

Again, constant-time behaviour.

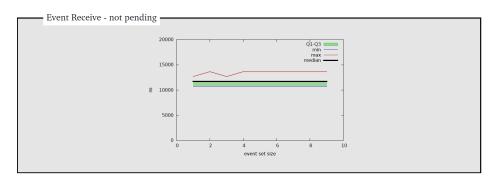

Test 6 (see Figure 12) Goal: to determine the cost to receive an event that is not already pending.

Symmetrically to Test 3, here we see constant-time behaviour, but also greater overhead because the kernel has to block the receiver.

# 2.1.7 Utilities

**Toolchain** The toolchain used to compile RTEMS (and our patch) is based on the rtems source builder (RSB). It is useful to note that the specific version of RTEMS relates to a specific version of the toolchain. In case the toolchain gets updated, it is necessary to work with the specific toolchain dating the same period of the specific commit of RTEMS in order to avoid problems. The specific toolchain can be obtained following the steps shown in Listing 7.

Listing 7: Obtaining the toolchain

\$git clone git://git.rtems.org/rtems-source-builder.git \$cd rtems-source-builder \$git checkout b65c131f2e11e352fde6efa0ec2fe5000dad3a4a

Figure 11: Comparative evaluation for the Event Manager primitives after our modifications: Test 5

Figure 12: Comparative evaluation for the Event Manager primitives after our modifications: Test 3

To compile the toolchain, please refer to https://devel.rtems.org/wiki/Developer/Tools/RSB.

RTEMS and Patch The supplied patch works against a specific (old) commit of RTEMS: 40d24d54ab59fdb2e4133128bf184ec8935f3545. Following the steps of Listing 8 to correctly apply the patch. There could be some warnings about trailing whitespaces: this is not an error.

Listing 8: Getting and patching RTEMS

```

$git clone git://git.rtems.org/rtems.git

$cd rtems

$git checkout -b timecomposable 40d24d54ab59fdb2e4133128bf184ec8935f3545

$git apply --check $PATH.TO.THE.PATCH/timecomposable.patch

$git am --signoff < $PATH.TO.THE.PATCH/timecomposable.patch

```

To avoid frustrations, we suggest following the steps specified below to compile RTEMS:

1. run the bootstrap inside the rtems folder;

```

cd $RTEMS_PATH

./bootstrap -g

```

2. export the path of the toolchain;

- 3. create a folder outside the source tree of RTEMS;

- 4. in that folder, run the following command:

```

$PATH_TO_YOUR_RTEMS_SOURCE_FOLDER/configure \

prefix=$PATH_TO_THE_TOOLCHAIN/toolchain \

target=sparc-rtems4.11 disable-itron enable-smp disable-cxx \

disable-docs disable-tests disable-posix CONSOLE_USE_INTERRUPTS=0 \

enable-rtemsbsp=leon3

```

5. run make -j<N> where <N> is the number of host processors you want to use during the compilation phase to speed up the process.

The repo includes the following three files:

- 1. timecomposable.patch: the patch that needs to be applied to RTEMS.

- 2. eventSporadic.c: an RTEMS application, showing the proof-of-concept of asynchronous events.

- 3. compileFile.sh: a bash script that can be used to compile an RTEMS application comprised of one single file. If the application has more files, then it is necessary to customise it. In all cases, it is necessary to update the path variables inside the script to point to the correct locations.

# 2.2 AURIX

The research-oriented RTOS that we selected for the AURIX was Erika Enterprise, a free-of-charge, open-source, certified OSEK/VDX-compliant RTOS distributed by Evidence (http://www.evidence.eu.com/), which targets various single-core and multi-core micro-controllers, including Infineon's Aurix Tricore by Infineon. At the time of this writing, the Erika Enterprise code-base also covers most of the Autosar 4 requirements concerning multi-core support at RTOS level.

In this section we report on the work we performed to make Erika timing-composable and to support the automated application and evaluation of TASA (the static software randomisation variant specifically developed for AURIX and is described later in Section 3.3) as part of the build automation framework. The time-composable version of Erika (nicked Erika-TC) and its build-chain automaton were instrumental to enabling the execution of the automotive use case in PROXIMA. It important to note that, in spite of the magnitude and complexity of the modifications to be applied to the build automation to serve the needs of the PROXIMA analysis, Erika-TC proved an excellent enabler to measurement observations, in the way of providing no disturbance for state, contention and timing jitter to the execution at the application level.

An overview of the automated build infrastructure that we developed for PROX-IMA including the time-composable version of Erika, the adaptations of its configuration utilities, and a number of artifacts that help the user run examples and evaluate various aspects of the execution-time behaviour of application programs running on the Aurix and Erika-TC is presented in [5].

#### 2.2.1 System Configurations

Erika Enterprise is a highly flexible RTOS that supports multiple system configurations. Understanding how system configurations are defined and deployed is therefore one key aspect for the user. In Erika, system configurations are passed in input to an automation build framework.

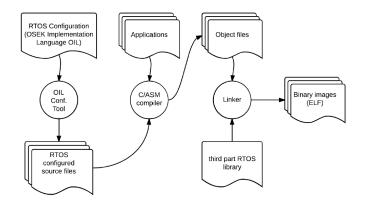

As required by the OSEK standard, system configurations are plain-text specification that conform with the OSEK Implementation Language (OIL). The system specification passed to the automation framework is then translated into a set of configured source files that are compiled and linked together with the RTOS library and applications to produce the final executable. Of that material, only the functional specification (i.e., the task bodies) needs to be provided by the user.

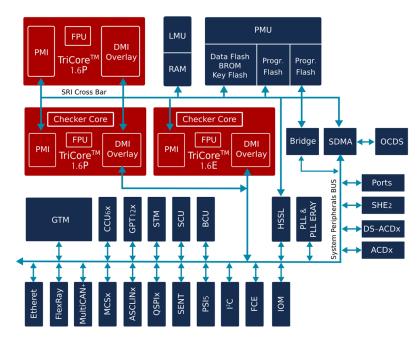

One or more ELF files can be produced by the build process, depending on the chosen configuration and the target architecture. For the AURIX, Erika assumes a fully-partitioned configuration, with one executable image per active core. Erikas build process is summarised in Figure 13.

The OIL file typically consists of a set of objects (i.e., tasks, alarms, events, software resources, interrupt service routines, system hooks, etc.) and object attributes. In the following we describe the basic structure of an OIL file in single and multi-core configuration, which uses only the OSEK-compliant part of Erika and targets the Aurix Tricore. We use the terms application and task interchangeably.

In a single-core configuration, a single ELF is generated and deployed to CPU0. At the top level of the specification, we find a CPU object, which is the container of all other objects declared in the OIL. One single level below in the hierarchical

Figure 13: Erikas build process

configuration we find the OS block, which selects and configures all RTOS related features. Listing 9 shows this part of the OIL file.

Listing 9: Single-core OIL configuration

```

CPU test_application {

OS EE{

MCUDATA=TRICORE{MODEL=TC27x;

};

CPU_DATA=TRICORE{CPU_CLOCK=100.0; APP_SRC="code.c"; COMPILER_TYPE=GNU; MULTLSTACK=TRUE;

};

KERNEL_TYPE=ECC1;

};

```

The CPU DATA object allows specifying core-specific parameters. The most important parameter is the file containing the functional application code (APP SRC). Listing 10 shows a simple example of application code, which – in this case – does nothing, as no application has been specified in the OIL, but it is sufficient to compile and cause the system to boot. More than one file can be included in the system configuration, but a single main function must be declared. The StartOs call never returns.

Listing 10: code.c: application code in single-core configuration

```

#include "ee.h"

StartOS(OSDEFAULTAPPMODE);

return 0;

}

```

Other useful parameters for the CPU DATA are: frequency of the core (CPU FREQ); compiler specific settings (COMPILER TYPE=GNU for the Hitech Tricore toolchain); the system stack configuration (the application stack can be either shared or private if the application needs its own private stack).

The OSEK standard defines four conformance classes to provide a fine-grained kernel configuration for kernel APIs and memory footprint. The KERNEL TYPE parameter specifies at which conformance class the kernel will be compiled, with values: BCC1, ECC1, BCC2, ECC2. The BCC1 and BCC2 classes only support basic applications that do not use synchronisation primitives (hence cannot enter a wait state) and do share the stack, therefore have a small RAM footprint. The ECC1 and ECC2 classes instead are for extended applications, which use synchronisation primitives and have their own private stack. In the latter case, some overhead is paid by the application owing to need to swap private stacks. Basic and extended applications can coexist in ECCx configurations; xCC2 classes allow

multiple application instances to be ready for execution at the same time, whereas xCC1 classes do not.

The multi-core configuration is similar to the single-core one, except that one full Erika instance is deployed onto each core. By default an ELF for each core is generated, even though a single-ELF configuration could be produced. Cores are activated according to the order specified in the Tricore specification manual. Adding multiple CPU DATA objects is sufficient to enable multi-core support. Different CPU DATA objects must be coherent on all parameters, except for the APP SRC one which includes code of applications assigned to the specific core. An ID discriminates objects associated to different cores and a master core must be elected specifying the MASTER CPU parameter.

Listing 11 shows an example using two cores (CPU0 and CPU1).

Listing 11: Multi-core OIL configuration

```

CPU test_application {

Os EE{

MASTER.CPU = "CPU0";

MCU.DATA = TRICORE{

MODEL=TC27x;

};

CPU.DATA = TRICORE{

ID = "CPU0";

CPU.CLOCK = 100.0;

APP.SRC = "ee_tc27x_tracing.c";

APP.SRC = "code.c";

COMPILER.TYPE = GNU;

};

CPU.DATA=TRICORE{

ID = "CPU1";

CPU.CLOCK=100.0;

APP.SRC = "ee_tc27x_tracing.c";

APP.SRC = "ee_tc27x_tracing.c";

COMPILER.TYPE = GNU;

APP.SRC = "eo_tc27x_tracing.c";

APP.SRC = "code1.c";

COMPILER.TYPE = GNU;

};

KERNEL.TYPE = BCC1;

};

};

```

For the multi-core configuration, small changes are also needed in the application code: the master must activate other cores before initialising the OS as shown in Listing 12.

Listing 12: code.c: Application code in multi-core configuration

```

# include "ee.h"

int main(void)

{

StatusType status;

StartCore(OS_CORE_ID_1,&status);

StartOS(OSDEFAULTAPPMODE);

return 0;

}

```

# 2.2.2 Cyclic Tasks

Cyclic tasks issue jobs regularly over a fixed time period. In Erika, the periodic behaviour of cyclic tasks is obtained by attaching the release to a recurrent alarm. Listing 13 provides an example of periodic task. The TASK and ALARM objects are declared on the CPU object. Besides the name and the id associated to the cpu (CPU ID), a task is characterised by: (i) a priority value (PRIORITY) as the scheduling policy assumes fixed priorities; (ii) an (AUTOSTART) value which specifies whether the task is automatically executed after the OS initialisation phase; (iii) a SCHEDULE value which makes the task fully preemptible or non preemptible; (iv) a STACK value which specify whether stack is private or shared. A private stack is required when the task can be waiting for an event or a logic resource, and the kernel must be in ECCX configuration.

Listing 13: Configuring a cyclic task

```

TASK Task1{

CPU.ID = "CPU0";

PRIORITY = 1;

AUTOSTART = FALSE;

SCHEDULE = NONE;

STACK = SHARED;

};

ALARM Alarm_TASK1{

COUNTER = system_timer;

ACTION = ACTIVATETASK{

TASK = Task1;

};

AUTOSTART = TRUE{

ALARMTIME = 1000;

CYCLETIME = 500;

APPMODE = OSDEFAULTAPPMODE;

};

};

```

The task activation is handled by the alarm object. Each periodic task must be associated to its own alarm object. The alarm is associated to a counter object that counts the hardware ticks from the system timer (residing in the STM peripheral). It is worth noting that the Tricore specification allows the STM peripheral to support two independent interrupt sources. The alarm starts counting immediately after system boot, and it is fired for the first time after the time specified by the ALARMTIME parameter. The period, instead, is specified by the CYCLETIME parameter.

Listing 14 shows the functional code associated to a cyclic task. Each such task must end with a TerminateTak call to release the CPU.

Listing 14: code.c: Cyclic task functional code

```

#include "ee.h"

volatile EE_UINT32 counter1 = 0;

TASK(Task1) {

counter1 ++;

TerminateTask();

}

int main(void) {

StatusType status;

StartCore(OS_CORE_ID_1, &status);

StartOS (OSDEFAULTAPPMODE);

return 0;

}

```

Task activation can also be chained to other tasks using the ActivateChainTask primitive. Tasks that neither activated by an alarm nor released by other tasks via a software signal (see below) are one-shot tasks.

## 2.2.3 Sporadic Tasks

Sporadic tasks are recurrent tasks whose activations are guaranteed to always be separated by no less than a minimum time span (also known as minimum interarrival time). Sporadic tasks are a key part of the automotive case study in PROX-IMA.

Erika does not natively support sporadic tasks, but it offers a timing protection system to prevent a task from being released before a given time span. This mechanism, however, is not yet implemented for the Tricore owing to the lack of hardware support.

To circumvent this limitation, we devised an alternative implementation out of a combination of periodic activation and conditional wait. Listing 15 provides a basic example of a sporadic task realised in that manner. A cyclic alarm periodically activates Task1 that immediately suspends itself on event Event1. Only when Event1 is issued by Task2, Task1 gets ready again. In this way, Task1 cannot be activated more frequently than its minimum inter-arrival time.

Listing 15: code.c: Sporadic task

```

#include "ee.h"

volatile EE_UINT32 counter1 = 0;

volatile EE_UINT32 counter2 = 0;

TASK(Task1) {

WaitEvent(Event1);

ClearEvent(Event1);

counter1++;

TerminateTask();

}

TASK(Task2) {

SetEvent(Task1, Event1);

counter2++;

TerminateTask();

}

int main(void) {

StartOS(OSDEFAULTAPPMODE);

return0;

}

```

The corresponding task configuration is reported in Listing 16. Events used by tasks must be declared in the OIL within the same scope of the task: the bit-mask associated to the event is automatically generated in this example. Each task that is expected to wait for an Event must declare it as a task property and use a private stack (hence an ECCX conformance class is required).

Listing 16: Configuring a sporadic task

```

TASK Task1 {

PRIORITY = 2;

AUTOSTART = FALSE;

SCHEDULE = FULL;

STACK = PRIVATE {

SYS_SIZE = 2048;

};

EVENT = Event1;

};

TASK Task2 {

PRIORITY = 1;

AUTOSTART = FALSE;

SCHEDULE = FULL;

STACK = PRIVATE {

SYS_SIZE = 2048;

};

};

EVENT Event1 {

MASK = AUTO;

};

```

## 2.2.4 Time-Composable Implementation

The property of time composability takes full meaning in single-core processor settings, to signify that the system is composable in the time domain; that is, the timing behaviour of a system component (an application) does not suffer the presence of other components. The key role of a time-composable RTOS in supporting the incremental development and verification of applications on modern processor architectures is well acknowledged [1].

Time-composability is generally hard to achieve, especially on multi-core processors, where parallel contention of shared hardware resources is the natural behaviour of the system, and in the absence of hardware modifications, which cannot be assumed for COTS processors requires changing the way RTOS services operate on the underlying hardware and are made available to user applications. In some cases, RTOS capabilities are severely limited, to meet time-composability requirements as well.

The original code-base in Erika assumes by default a strictly partitioned multicore configuration, where each core is associated to a system partition. Partitioning eases the process of making Erika time-composable as it allows the system to be regarded a set of partially independent single-core systems with inter-partition communications as the main source of interference determined by software characteristics of the application. For this reason, we first modified core Erika services to be time-composable within the core, similarly to what we did in [1], then we added a time-composable inter-partition communication support, which relies on an AUTOSAR IOC component we modified to use a TDM-based scheme to share the access to the LMU memory through the crossbar.

For this Erika-TC (for time-composable) release we injected time-composability into core Erika services, in terms of zero-disturbance<sup>5</sup> and steady timing behaviour<sup>6</sup>. In the following, we provide an overview of the Erika RTOS features that we rendered time-composable. Each feature is presented with particular attention to configuration guidelines and TC assessment results.

**Deployment configuration** In the Aurix processor, configuring the system to be deployed on specific memory segments is fundamental to guarantee zero-disturbance. As the Tricore hardware layout allows keeping a large amount of information in scratchpad memory, we force Erika code and data to be entirely deployed into them, thus excluding any cached memory areas. Erikas memory footprint is sufficiently small and this solution does not seem to be significantly restrictive. To enable this configuration, the EE EXECUTE FROM RAM option in the OIL is required, as shown in Listing 17.

The default Erika configuration tries to deploy also the user applications to the scratchpads. In some cases, however, applications might be deployed to different memory segments as, for example, they might not completely fit into the scratchpads. For example, options EE ENABLE TASA SUPPORT and EE TASKS ON PFLASH offload applications code to the PFlash cached segment.

Listing 17: Deploying to scratchpad memories

EE\_OPT = "EE\_EXECUTE\_FROM\_RAM";

Run-to-completion A simple but effective solution for minimising the disturbance effect of OS services and inter-task interference consists in enforcing run-to-completion execution semantics. Under this scheme, application jobs cannot be interrupted during execution and all scheduling decisions are deferred until job completion, even when higher priority tasks become ready for execution. Run-to-completion used non-preemptive scheduling, which is already supported by the Erika code-base, but which – for use in PROXIMA – also required removing any asynchronous source of interference originated, for example, by the tick-based time management whose disturbance breaks time composability.

In PROXIMA, to properly support time-composable run-to-completion semantics, we removed the tick-based scheduling in favour of a timer-based scheduling with deferred timer interrupts. In addition to that, we re-implemented some scheduling

<sup>&</sup>lt;sup>5</sup>Erika services must not in uence the application in presence of hardware with a history-dependent behaviour and because of time-triggered actions (i.e., the tick management) whose timing behaviour is not constant.

<sup>&</sup>lt;sup>6</sup>The jittery timing behaviour of Erika services, caused by the hardware/software status and input data, must be avoided.

primitives to make execute in constant time. We discuss both features later in this section.

The non-preemptive scheduling support implemented in Erika includes support for the priority ceiling protocol. Each task is therefore assigned a ready (static) priority and a dispatching (dynamic) priority. The latter is assigned to make tasks non-preemptive, so that they run at a priority higher than all premptable tasks. In practice, this is obtained by setting a system ceiling value to the dispatching priority, which causes the CPU to be released only at job completion. Non-preemptive tasks are characterised by the SCHEDULE parameter set to NONE, or by its absence, as shown in Listing 18. The FULL value, instead, designates fully-preemptive tasks.

Listing 18: Run-to-completion task specification

```

TASK Task1 {

CPU_ID = "CPU0";

PRIORITY = 1;

AUTOSTART = FALSE;

SCHEDULE = NONE;

STACK = SHARED;

};

```

We identified two situations where tasks should be non-preemptive: when they access cached memory areas (i.e., the cached PFlash), or when they use inter-core communication primitives. In all other cases, tasks can be preempted without breaking time-composability.

Non-preemptive scheduling might penalise the schedulability and responsiveness of the system. For this reason, non-preemptive execution should be as short as possible.

Constant-time scheduling We devoted significant effort to re-implement Erikas scheduling primitives to make them use bitwise operations on bit-masks to achieve constant-time execution behaviour in all of the four OSEK conformance classes. All conformance classes now use a 32-bit mask as ready queue (EE rq bitmask). Scheduling decisions are made on them on fixed-priority basis, with the following pre-class provisos:

- for BCC1 and ECC1 classes, each task is assigned a priority value that corresponds to a bit in the ready queue mask, so that all tasks have distinct priorities (obviously limited to 32 on the Aurix). Two arrays are used to map the task to the corresponding priority value (EE th ready prio) and vice-versa (EE prio link). The same principle used to set tasks in the ready queue has been also used to keep track of suspended tasks;

- for BCC2 and ECC2 classes, a task queue is associated to each priority level, so that, multiple tasks can be at the same priority level and pending task activations are allowed. When a task becomes ready, it is stored in the corresponding queue and the bit corresponding to its priority level is set on the ready bit mask. The scheduling policy applied to these conformance classes is FIFO within priorities.

This representation allows the ready queue to be updated in constant-time using bitwise operations. The task selection, for example, requires identifying the most significant bit in the ready queue bit-mask. To do so, we exploited the perfect

hashing of De Bruijn sequences [15]: the CLZ instruction of the Aurix provides the same semantics, but cannot guarantee constant-time latency.

To enable constant-time scheduling primitives, the EE SCHED 01 option have to be set in the OIL, as shown in Listing 19. When one of the BCC1 or ECC1 classes is selected, the EE prio link has to be declared, as shown in Listing 20. This array must contain tasks pinned to the specific core, at increasing priority order. The first priority level is reserved to the background task and the EE NIL value is required for it.

Listing 19: Constant-time scheduling option

$EE\_OPT = "\_\_EE\_SCHED\_O1\_\_";$

Listing 20: code.c: Priority level to task mapping array

```

#ifdef -_EE_SCHED_O1__

#define EE_MAX_PRIOEE_MAX_TASK + 1

const EE_TIDEE_prio_link [EE_MAX_PRIO] = {

EE_NIL,

Task1,

Task2,

// ... map priority level to task

};

#endif

```

So far, we presented how a single update operation, that is, the insertion of a task in the ready queue and electing the next task to be dispatched, has a constant execution time. As tasks are triggered by different alarms, however, the number of update operations on the ready queue depends on the number of alarms expiring at the same time. Moreover, alarms are maintained in an ordered list and each expiration times is expressed as the time span from the immediately preceding expiration time. Updating that list may take a variable amount of time, depending on the list state: inserting an alarm needs to find the correct position in the list. Cyclic alarms would allow determining a hyper-period and thus a recurring timeexpiration pattern that would permit to avoid the run-time update of alarms. This solution, however, is rather restrictive. Our re-implementation does not use this scheme and provides more flexibility. Therefore, we only partially achieve the desired steady execution time behaviour for all our scheduling primitives. Our choice reflects the needs of the automotive use case in PROXIMA, where the number of cyclic tasks is significantly lower than the number of sporadic tasks, which causes alarms to have to be maintained in an ordered list.

#### 2.2.5 Evaluation by PAKs

To gauge the gain obtained in terms of time-composability by our modifications, we evaluated the timing behaviour of the revised scheduling primitives, with PAKs, before releasing Erika-TC for use in the automotive use case. A PAK (short for PROXIMA Application Kernel) is an ad-hoc application program designed to stress specific parts of the system. PAKs have been specifically designed to compare the performance of scheduling operations, such as inserting a task into the ready queue and computing the context switch, of the original Erika release to those of the time-composable one.

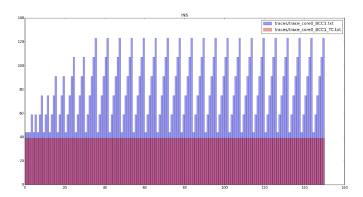

In our evaluation experiments, six tasks are assigned to the first core and one task on the second core. Tasks have the same period, but their first activation is offset by one second from each other: the second task starts one second later than the first; the third starts one second later than the second; and so forth.

Figure 14 reports the cost of the task activation primitive, where the original Erika implementation was incurring much jitter.

Figure 14: Task activation with insertion into the ready queue (processor set to 100 Mhz; kernel set to BCC1 configuration)

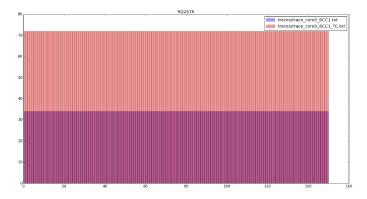

Figure 15 shows instead the cost to compute the context switch, between the task atop of the stack and the highest priority task on the ready queue.

Figure 15: Election of the next task to dispatch (processor set to 100 Mhz; kernel set to BCC1 configuration)

Our time-composable primitives behave as good as expected. Significant variations instead are incurred on task activation when the original insert primitive is used. Those variations are caused by the implementation of the ready queue, which requires tasks to be ordered when inserted. Conversely, constant execution time can be observed using the time-composable implementation, which uses only bitwise operations. No variations, instead, have been detected in the context switch, as popping the task is an O(1) operation by nature.

Interestingly, in force of partitioned scheduling and no preferential use of scratchpad memories in place of shared cacheable memory, all activity in both experiments occurs within the designated core, no inter-core interference is incurred.

**Events** Events are a fundamental RTOS feature for automotive applications. Unfortunately, their implementation in the original Erika may break the principle of time-composability.

Consider for example, Listing 15, where Task1 waits for Event1 and Task2 sets the corresponding event. Task1, which has higher priority than Task2 executes until the WaitEvent primitive is called, which causes the task to move into a waiting state and calls for dispatching. Task1 will be resumed as soon as Task2 calls the corresponding SetEvent primitive. When this happens, Task1 resumes its execution and immediately preempts Task2, owing to its higher priority, thus breaking the run-to-completion execution semantics for Task2.

We therefore modified Erika to prevent the running task from being preempted after setting an event.

To enable deferred events handling, you need to set the EE DEFERRED EVENT HANDLING option in the OIL.

Interestingly, the sporadic task model presented earlier includes two distinct invocation events: the periodic alarm on the one hand, and the resume from the waiting state on the other. Having multiple invocation events may complicate timing analysis and also expose dependence on the periodic alarm. We therefore explored an alternative model for sporadic tasks, which uses a single invocation event only. The idea is to make the call to WaitEvent the single invocation point, so that the sporadic tasks revolves in an infinite loop around it, as shown in Listing 21. To that end, we use a bit mask consisting of a TimingProtectionEvent and the original Event1 to resume Task1 when all the corresponding bits are up. At that moment in time, the required minimum inter-arrival time has elapsed and Task2 has called the SetEvent primitive.

Listing 21: code.c: Single-invocation sporadic task

```

#defineTASK1_MINIMUM_INTERARRIVAL_TIME500

TASK(Task1) {

for (;;) {

WaitEvent (TimingProtectionEvent | Event1);

ClearEvent (TimingProtectionEvent | Event1);

SetRelAlarm (Alarm_Task1, TASK1_MINIMUM_INTERARRIVAL_TIME, 0);

/* startofthetaskbody*/

counter1++;

/* endofthetaskbody*/

}

```

The OIL is updated accordingly. As shown in Listing 22, the alarm used to activate Task1 now sets the TimingProtectionEvent event when the prescribed minimum inter-arrival time is elapsed, and is armed by the task by means of the SetRelAlarm primitive. To initially activate the task, the AUTOSTART options is set to TRUE as well as the first alarm expiration.

A similar approach should be used when potentially blocking WaitEvent calls are in the functional specification of the task. Such a task should be split into multiple sub-tasks, each of which characterised by a single WaitEvent call, as a single activation point.

Listing 22: Events configuration

```

TASKTask1{

PRIORITY = 2;

AUTOSTART = TRUE;

SCHEDULE = FULL;

STACK = PRIVATE{

SYS_SIZE = 2048;

};

EVENT = Event1;

};

EVENT Event1{MASK = AUTO;};

EVENT TimingProtectionEvent{MASK = AUTO;};

ALARM Alarm_Task1{

COUNTER = system_timer;

```

```

ACTION = SETEVENT{

TASK = Task1;

EVENT = TimingProtectionEvent;

};

AUTOSTART = TRUE{

ALARMTIME = 1000;

APPMODE=OSDEFAULTAPPMODE;

};

};

```

The model presented so far assumes that the waiting task is resumed for execution only when all events have been set. However, this semantic is not warranted by the original WaitEvent primitive. We therefore specifically introduced it to support the scenario where tasks need to be activated by multiple events. In this case, the timing protection mechanism might result unnecessary for tasks whose activation depends on other cyclic tasks. To enable the all semantics, you need to use the EE CUMULATE EVENTS option.

**Time management** Erika's timing services originally relied on a tick-based implementation whose disturbance effect on user applications could completely break time-composability (particularly with finer tick granularity).

To abate this source of interference, we redesigned the timing services to use less intrusive interval timers.

Interestingly, interval timers alone are not sufficient to this end, as a running application might still be interrupted by timer interrupts. To restore run-to-completion execution semantics proper in this case, we need alarm expiration events to not interrupt the running application.

To this end, we defer all timing events, that otherwise would be triggered during execution, to right after the completion of the running job, that is until the next dispatching point. This modification ensures the task to run to completion, without being interrupted, and to keep the possibly jittery behaviour of scheduling primitives between two consecutive tasks execution. Notably, we apply this motification only to non-preemptive tasks: it is therefore important to mark each critical tasks as such in the OIL.

Inter-core communication Our proposal of time-composable inter-core communication builds on the AUTOSAR Inter OS-Application Communicator (IOC) layer, which we modified to support a software-enforced TDM-based arbitration mechanism for the Tricore crossbar. This time-composable inter-core communication framework is now part of the time-composable extension of Erika.

The details of the approach have been presented in [17], where we show how that mechanism can be exploited at the OS level to enforce timing isolation and to have predictable effects on the bus contention for all communications across applications which involves accessing a shared medium (e.g., LMU).

The original Erika implementation of the message-passing API has been extended to enforce a configurable arbitration policy by splitting the exchanged messages into chunks and arbitrate each chunk transfer in TDMA-like time slots. TDMA frame, slots and chunk size can be configured to better meet the application requirements. To address specific needs of mixed-criticality systems, the cited work also proposes a more flexible TDMA-based arbitration, which allows reserving more than one communication slot to selected cores. This enhanced version of TDMA enables the provision of better bandwidth levels to cores running high-criticality applications.

Further details on the proposal and the experimental evaluation of it are reported in [17] (which is a public-access document) and not included here.

## 2.2.6 Using Erika-TC

We now provide instructions to set up a working environment and build your own applications on top of our Erika-TC code-base.

The PROXIMA release of Erika-TC includes the following artefacts:

- erika-tc@3274.patch: the patch to make Erika time-composable and to enable the support for TASA (see Section 3.3 in this document);

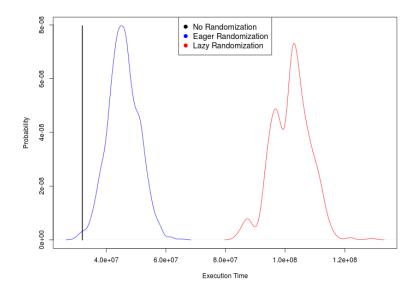

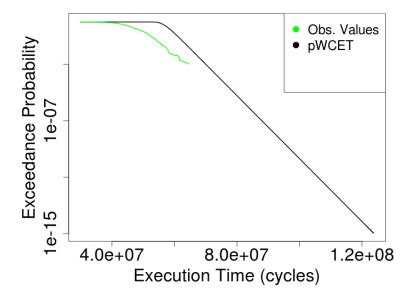

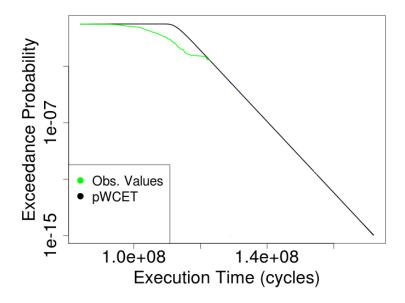

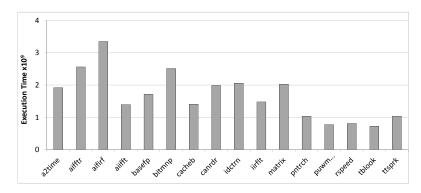

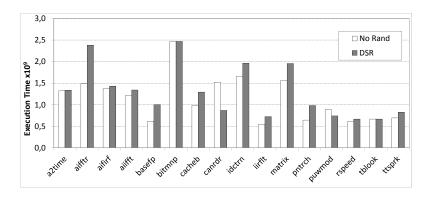

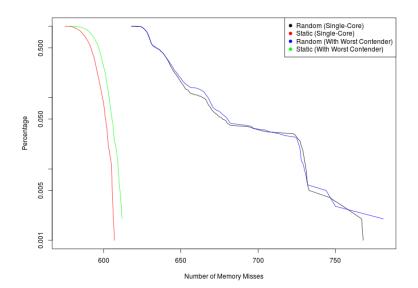

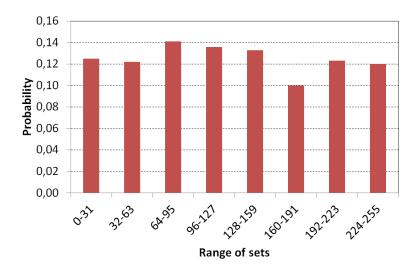

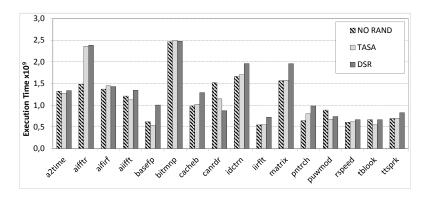

- Makefile: a makefile to build Erika and user applications;