# **Deliverable D10.11A**

# **FINAL SUMMARY REPORT**

Section A – "Publishable Report" including "Potential and Consolidated Impact"

Grant Agreement number: 247846

Project acronym: EURETILE

Project title: European Reference Tiled Architecture Experiment

Funding Scheme: Collaborative Project

Date of latest version of Annex I against which the assessment will be made: 2013 07 01 Period covered: from Jan 1<sup>st</sup>, 2014 to Sep 30<sup>th</sup>, 2014

Name, title and organisation of the scientific representative of the project's coordinator: dott. Pier Stanislao PAOLUCCI, INFN (Istituto Nazionale di Fisica Nucleare)

Tel: +39 338 53 48 980

E-mail:<u>pier.paolucci@roma1.infn.it</u>

Project website address: <u>www.euretile.eu</u>

v20141113c

## **About this document**

The "Final Summary Report" (deliverable D10.11) is composed of:

section A, this document, the "Final Publishable Report" (D10.11A), that includes an Executive Summary, a detailed report of R&D results, and a publishable section about the "Consolidated and Potential Impact" of the project.

Section B, document D10.11B, a "Plan for use and dissemination of foreground".

Section C, document D10.11C, about "Societal Implications"

Section D, document D10.11D, about the "Final Distribution of Contributions"

## **EURETILE Final Summary Report**

Pier Stanislao Paolucci<sup>1</sup>, Iuliana Bacivarov<sup>2</sup>, Andrea Biagioni<sup>1</sup>, Clément Deschamps<sup>3</sup>, Ashraf El-Antably<sup>3</sup>, Nicolas Fournel<sup>3</sup>, Gert Goossens<sup>4</sup>, Rainer Leupers<sup>5</sup>, Alessandro Lonardo<sup>1</sup>, Luis Gabriel Murillo<sup>5</sup>, Devendra Rai<sup>2</sup>, Frédéric Rousseau<sup>3</sup>, Lars Schor<sup>2</sup>, Francesco Simula<sup>1</sup>, Laura Tosoratto<sup>1</sup>, Lothar Thiele<sup>2</sup>, Piero Vicini<sup>1</sup>

<sup>1</sup>INFN Roma "Sapienza". <sup>2</sup>Computer Engineering and Networks Laboratory, ETH Zurich. <sup>3</sup>Université Joseph Fourier – TIMA Laboratory. <sup>4</sup>Target Compiler Technologies. <sup>5</sup>RWTH Aachen University – ISS & SSS

## TABLE OF CONTENTS

| 1 | Executive Summary                                                                           | 5  |

|---|---------------------------------------------------------------------------------------------|----|

| 2 | Project context and objectives - summary                                                    | 6  |

|   | 2.1 Experimental Hardware and Simulation Platforms for HPC and Embedded Systems             |    |

|   | 2.2 Definition of Software Tool-Chain for many-process dynamic workloads                    | 7  |

|   | 2.3 Fault-Tolerance and Scalability                                                         | 8  |

|   | 2.4 HdS and DNAOS                                                                           | 9  |

|   | 2.5 ASIP design tools and acceleration of computation and communication                     | 9  |

| 3 | Main scientific and technologic results and foregrounds                                     | 10 |

|   | 3.1 Many-Tile Platforms and Many-Process (Dynamic) Applications                             | 10 |

|   | 3.2 EURETILE Design Flow: Many-process, dynamic applications on Many-tile platforms         |    |

|   | 3.2.1 Description of applications and scenarios: process networks and finite state machines |    |

|   | 3.2.2 Optimization of the mapping using the VEP                                             |    |

|   | 3.2.3 The software stack generated by the EURETILE design flow                              |    |

|   | 3.3 Fault Management on EURETILE platforms                                                  | 12 |

|   | 3.3.1 Fault avoidance                                                                       | 12 |

|   | 3.3.2 Fault tolerance                                                                       |    |

|   | 3.3.3 Fault reactivity                                                                      |    |

|   | 3.3.4 Task migration between tiles                                                          |    |

|   | 3.4 Specification of the architecture of the target execution platform                      |    |

|   | 3.5 Programming model: applications plus scenarios                                          |    |

|   | 3.5.1 Application Specification                                                             |    |

|   | 3.5.2 Execution scenarios                                                                   |    |

|   | 3.6 Mapping strategy                                                                        |    |

|   | 3.6.1 Design time: analysis and optimization                                                |    |

|   | 3.6.2 Runtime management                                                                    |    |

|   | 3.7 Generation of the executable                                                            |    |

|   | 3.7.1 DNA-OS                                                                                |    |

|   | 3.7.2 Software Synthesis Front End                                                          |    |

|   | 3.7.3 Software Synthesis Back end                                                           |    |

|   | 3.7.4 Hierarchical Run-time manager                                                         |    |

|   | 3.7.5 Specificities of generation for VEP Simulated Platform                                |    |

|   | 3.7.6 Specificities of generation for QUonG Hardware Platform                               |    |

|   | 3.8 The Virtual EURETILE Platform and Supporting Simulation and Debugging Technologies      |    |

|   | 3.8.1 VEP characteristics and architecture                                                  |    |

|   | 3.8.1.1 Processor model abstractions and optimized variants                                 |    |

|   | 3.8.1.2 Abstract simulation                                                                 |    |

|   | 3.8.1.3 VEP use cases                                                                       |    |

|   | 3.8.1.4 Other speed optimizations                                                           |    |

|   | 3.8.2 Parallel Simulation Technologies                                                      |    |

|   | 3.8.2.1 parSC, SCandal and legaSCi                                                          |    |

|   | 3.8.2.2 SCope                                                                               |    |

|   | 3.8.3 Multicore Debugging Technologies                                                      | 20 |

|     | 3.8.3.1 The Whole-system Debugger – WSDB                                                      | 20   |

|-----|-----------------------------------------------------------------------------------------------|------|

|     | 3.8.3.2 SWAT: System-wide Assertions                                                          | 20   |

|     | 3.8.3.3 Concurrency analysis and behaviour exploration framework                              | 20   |

| 3.9 |                                                                                               |      |

| 3.1 | 10 LO FA MO: Fault Detection and systemic Awareness for QUonG and VEP                         | 21   |

|     | 3.10.1 LO FA MO implementation on VEP                                                         |      |

|     | 3.10.2 LOFAMO implementation on QUonG                                                         |      |

| 3.1 |                                                                                               |      |

| 3.1 |                                                                                               |      |

|     | 3.12.1 GPUDirect technology on APEnet+                                                        |      |

|     | 3.12.2 RDMA on APENet+                                                                        |      |

|     | 3.12.2.1 RDMA task implementation and acceleration                                            | 25   |

|     | 3.12.3 MPI on APENet+                                                                         |      |

| 3.1 | ASIP design tools applied to computation and interconnection                                  | 26   |

| 3.1 |                                                                                               |      |

|     | 3.14.1 Dynamic Multi-Media Many-Process Applications                                          |      |

|     | 3.14.1.1 DSP/Data-flow Kernels                                                                |      |

|     | 3.14.1.2 Multimedia Applications                                                              | 27   |

|     | 3.14.1.3 Other Streaming Applications                                                         |      |

|     | 3.14.1.4 Picture-In-Picture (PiP) Video Decoder                                               | 28   |

|     | 3.14.2 Distributed simulation of polychronous and plastic spiking neural networks             | 28   |

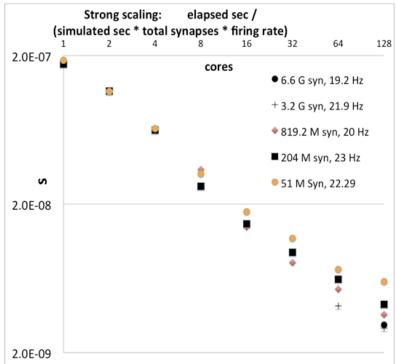

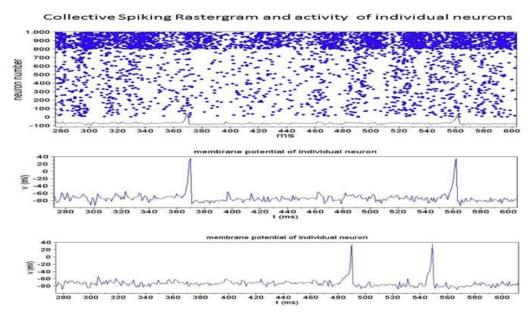

|     | 3.14.2.1 Validation of functionality and scaling of the many-process neuro-synaptic simulator | 29   |

| 3.1 | 15 Experimental results on VEP simulated platform                                             | 29   |

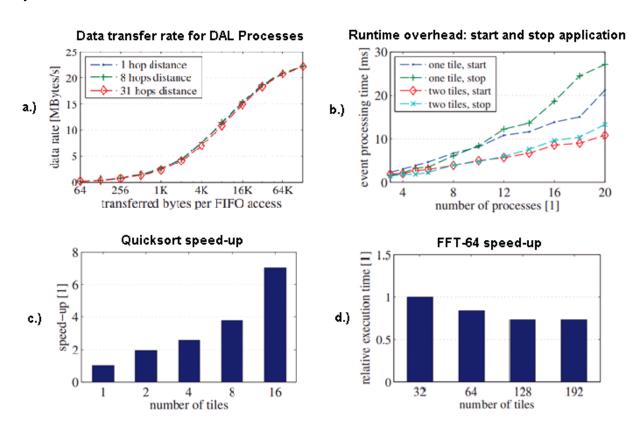

| 3.1 | 16 Experimental results on QUonG hardware platform                                            | 30   |

|     | 3.16.1 DNA-OS on QUonG                                                                        |      |

|     | 3.16.2 Executing the DAL version of the neural DPSNN benchmark on QUonG                       | 30   |

|     | 3.16.2.1 Efficiency of the EURETILE tool-chain (DAL on DNA-OS) vs "standard" (MPI on Lin      | ıux) |

|     | 31                                                                                            |      |

|     | 3.16.2.2 DAL on DNA-OS scaling to the full QUonG hardware platform                            |      |

|     | 3.16.3 APENet+ RDMA applied to DPSNN simulation                                               |      |

|     | 3.16.4 Demonstration of MPI for APENet+                                                       |      |

|     | 17 Discussion of limitations and possible related future work                                 |      |

|     | 3.17.1 Limitations of the Programming Model                                                   |      |

|     | 3.17.2 Limitations of the Fault Management Approach                                           |      |

|     | 3.17.3 Limitations of the Runtime System                                                      |      |

|     | 3.17.4 Limitations of the VEP Simulator                                                       |      |

| 4 C | Consolidated and Potential Impact                                                             |      |

| 4.1 |                                                                                               |      |

| 4.2 |                                                                                               | 36   |

| 4.3 |                                                                                               |      |

|     | ORTICONIC FET Project                                                                         |      |

| 4.4 |                                                                                               |      |

| 4.5 | 1                                                                                             |      |

| 4.6 |                                                                                               |      |

| 4.7 |                                                                                               |      |

| 4.8 | 1 66 6                                                                                        |      |

| 4.9 |                                                                                               |      |

|     | Acknowledgements                                                                              |      |

| 6 R | References                                                                                    | 41   |

## 1 Executive Summary

In the next decade, a growing number of scientific and industrial applications will require power-efficient systems providing unprecedented computation, memory and communication resources. Autonomous cars, for instance, will have to perform multi-sensorial data fusion to reach the required level of artificial intelligence, while high-impact scientific application, like brain-simulation, will require Exascale performances (10<sup>18</sup> operations per second). A promising paradigm is the use of heterogeneous many-tile architectures. The resulting computing systems are complex and 1- must be protected against several sources of faults and critical events, and 2- application programmers must be provided with programming paradigms, software environments and debugging tools adequate to manage such complexity. The EURETILE (European Reference Tiled Experiment) consortium conceived, designed and implemented: 1- an innovative many-tile, many-process dynamic faulttolerant programming paradigm and software environment (DAL), grounded over a lightweight operating system (DNA-OS) generated by an automated software synthesis mechanism (APES) that takes in account the architecture and application specificities; 2- a many-tile heterogeneous hardware system (QUonG), equipped with a high-bandwidth low-latency 3D-toroidal interconnect (APENet+). The inter-tile interconnect processor (DNP) is equipped with an experimental fault-tolerance, fault-awareness and fault-injection mechanism (LO|FA|MO); 3- a simulation environment (VEP), equipped with innovative parallelism and debugging facilities (add list). We also designed and coded a set of application benchmarks representative of requirements of future HPC and Embedded Systems, including: 4- a set of dynamic multi-media applications and 5- a large scale simulator of neural activity and synaptic plasticity (DPSNN-STDP) that will be used 1- for biological simulations; 2- to generate complex traffic patterns driving the design of future interconnect systems and computing nodes dedicated to brain simulation. One of the partner improved and experimented its: 6- tools for the cogeneration of ASIPs (TARGET). The application benchmarks, compiled through the EURETILE software tool-chain, have been efficiently executed on both the many-tile hardware platform and on the software simulator, up to a complexity of a few hundreds of software processes and hardware cores.

The consortium: The APE Parallel Computing Lab of INFN Roma is in charge of the EURETILE HW Design (QUonG system/APENet+ board/DNP (Distributed Network Processor) and Scientific Application Benchmarks. The Computer Engineering and Networks Laboratory (TIK) of ETH Zurich (Swiss Federal Institute of Technology) designs the high-level explicit parallel programming and automatic mapping tool (DAL) and a set of "Embedded Systems" benchmarks. The Software for Systems on Silicon (SSS) of the ISS institute of RWTH Aachen, investigates and provides the parallel simulation technology and scalable simulation-based profiling/debugging support. The TIMA Laboratory of the University Joseph Fourier in Grenoble explores and deploys the HdS (Hardware dependent Software) including the distributed OS architecture. TARGET Compiler Technologies, the Belgian leading provider of retargetable software tools and compilers for the design, programming, and verification of application-specific processors (ASIPs), is in charge of the HW/SW Co-design tools for custom components of the EURETILE architecture.

**Project Foreground (exploitable Intellectual Properties)** in alphabetic order: ASIC Design Tools, APENet+(3D toroidal fault-aware interconnect board), APES (OS generator), DAL (Distributed Dynamic Application Layer), DALipse (graphical software development environment for DAL), DNA-OS (lightweight operating system), HySim (Hybrid Simulation), LO|FA|MO (local hardware Fault Monitor), DNP (Distributed Network Processor), DPSNN-STDP (Distributed Simulator of Polychronous Spiking Neural Net with Spiking Time Dependent Plasticity), Peer-to-peer GPU Direct RDMA IP, QUonG (many-tile fault-tolerant heterogeneous experimental platform), SWAT (System Wide Assertion), Thermal-RTC (toolbox for thermal / performance evaluation), VEP (Virtual Execution Platform), WSDB (Whole system debugger).

Grant Agreement no. 247846 Call: FP7-ICT-2009-4 Obj. FET-ICT-2009.8.1

Scientific Coordinator: Pier Stanislao Paolucci, INFN, Roma, Italy.

Administrative Coordinator: Michela Giovagnoli, INFN, Roma, Italy

## 2 Project context and objectives - summary

The original objective of the EURETILE project (<a href="http://www.euretile.eu">http://www.euretile.eu</a>, FET FP7 grant no. 247846) was the investigations of innovations to the many-process software and to the many-tile hardware architecture of future fault-tolerant Embedded Systems and High Performance Computers (HPC), for dynamic applications requiring extreme numerical and DSP capabilities. The project planned to deliver:

- Experimental Many-tile Hardware and Simulation platforms, for the scenarios of dynamic many-process workloads to be run on future fault-tolerant Embedded Systems and HPC;

- A many-tile programming/optimization environment, exhibiting several foundational innovations, to be applied to such dynamic many-process workload;

- A set of application benchmarks, for both HPC and Embedded System domains, coded using the new programming environment, including 1- a benchmark representative of distributed simulation of neural activity and synaptic plasticity (the DPSNN-STDP application see [Paolucci, 2013b]) that generates complex inter-process traffic patterns and 2- a set of dynamic multi-media embedded applications including a picture-in-picture software for embedded video processing systems as well as distributed implementations of a ray-tracing algorithm and an H.264 codec pair (see [Paolucci, 2014b]).

See [Schor, 2014a] for a description of the proposed software-flow and [Paolucci, 2013a] for a summary of the project motivations and a report about the first three years of the project (2010-2012).

# 2.1 Experimental Hardware and Simulation Platforms for HPC and Embedded Systems

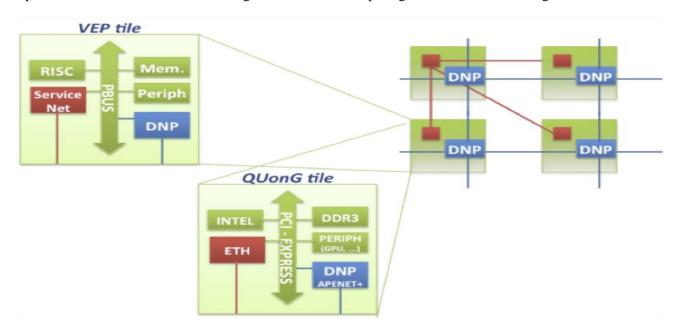

A simplified view of the two many-tile execution platform conceived by the EURETILE project plan as representative of the Embedded and High Performance Computing domain is the following:

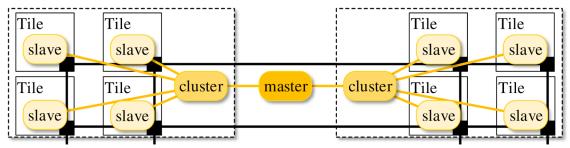

Simplified view of the EURETILE platforms (VEP and QUonG) used for experiments on innovations to many-tile hardware and many-process software of future fault-tolerant Embedded Systems and HPC platforms. The inter-tile communication is supported by a Distributed Network Processor (DNP)

1- The QUonG Hardware Platform for scientific High Performance Computing. We developed a custom interconnection board (APEnet+) that provides a 3D toroidal interconnection for many-tile systems and provides fault monitoring and fault tolerance features implemented by its DNP (Distributed Network Processors). Using the APEnet+ interconnect, the QUonG platform integrates off-the-shelf boards mounting multi-core CPUs and GPGPUs in a powerful many-tile hardware platform.

2- The VEP Embedded Systems many-tile simulation platform. VEP simulates the behaviour under-faults of many-tile systems and includes innovations to many-tile debugging and parallel simulation. The simulation framework includes many RISC based tiles, networked through a custom interconnect mesh composed of DNPs (Distributed Network Processors).

## 2.2 Definition of Software Tool-Chain for many-process dynamic workloads

From a software perspective, EURETILE aimed at providing a scalable and efficient extensive programming framework for many-tile platforms, by exploiting the underlying parallelism and investigating some key brain-inspired architectural enhancements specific to EURETILE.

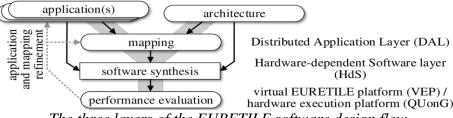

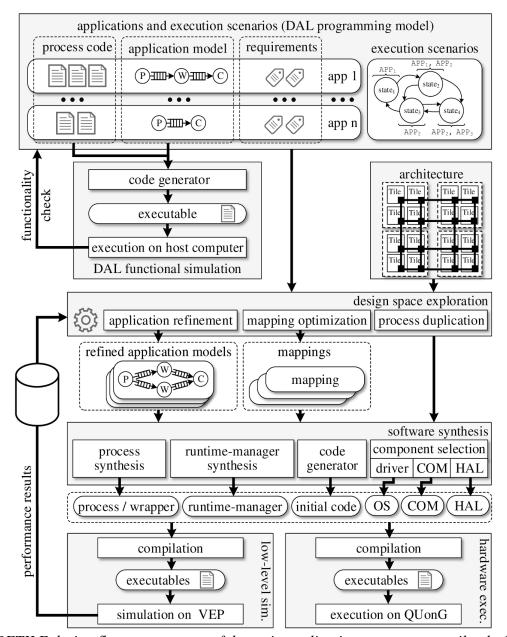

Schematic View of the EURETILE Software Tool-Chain.

The proposed programming environment is based on a new model of computation that explicitly exposes the coarse-grain and fine-grain parallelism present in applications. Then, automatic tools are aiming at obtaining predictable and efficient system implementations by optimally matching the concurrency and parallelism present in applications, with the underlying many-tile hardware. The figure sketches the software EURETILE tool-chain.

The EURETILE software tool-chain follows a well-known Y-chart (application, architecture, executable) approach and in EURETILE each design phases have been enriched with novel concepts for programming

efficiently the layers of hierarchy present in the EURETILE platform. The proposed software tool-chain aims at optimizing issues related to system throughput while still guaranteeing real-time constraints for applications that operate under such restrictions. Additionally, fault-tolerance aspects are considered, from system-level programming. The way of representing parallelism, concurrency, and fault tolerance at system level, the implementation of the distributed real-time operating system, and the efficient fast simulation environment have all a strong impact on the overall optimality of the system implementation. The proposed extensive software design framework, including all challenges described above, created a foreground, the reference EURETILE platform, that can be used a starting point for the next years road map in many-tile processing.

## 2.3 Fault-Tolerance and Scalability

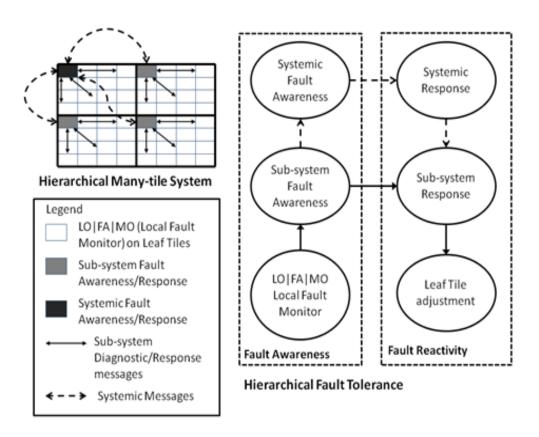

The "LO|FA|MO" design paradigm proposed by the project creates a *systemic awareness of faults and critical events*, thanks to a distributed approach that uses additional hardware components on each DNP, and needs dedicated software components running on each tile to create a *local awareness of faults and critical events*. This local awareness is then propagated along the system hierarchy. Onto such local and systemic fault awareness, a software approach to fault reactivity has been grounded. From a system-level perspective, two fault reactivity strategies have been investigated and implemented in the Distributed Application Layer (DAL), namely *fault recovery* and *fault tolerance*. On the one hand, the proposed fault recovery mechanism migrates processes that are assigned to faulty tiles to alternative tiles. On the other hand, to provide fault tolerance, applications with stringent performance requirements are duplicated during design space exploration.

The Network Processor of each leaf in the many-tile HW system is equipped with its own LO/FA/MO components. The Local Awareness of faults and critical events is propagated towards the upper hierarchy levels, creating Systemic Awareness. Reactions to faults and critical events are autonomously initiated by the sub-system controllers.

#### 2.4 HdS and DNAOS

The project planned to ground its execution on the services provided by DNA-OS: a light operating system that can be customized depending on the requirements of the application and the characteristics offered by the hardware resources. DNA-OS has been developed and ported on several architectures (ARM, MIPS, ...), and in the context of EURETILE had to be ported on the INTEL and RISC platform of the QUonG and VEP platforms. The plan was to develop a tool (APES) able to generate only the required services provided by DNA-OS regarding the application requirements for the target architecture. Based on this OS tool-chain, a main objective was to provide a tool-chain able to take as input the application model, as well as characteristics of the target architecture (multi-core, multi-tile) including a specific communication device (developed by INFN and called DNP) in order to generate all binary codes for all hardware computation resources. We planned to generate the software for both the execution platforms: 1- the many-tile hardware architecture for the HPC domain, and 2- the RISC-based simulation environment representative of the embedded domain.

## 2.5 ASIP design tools and acceleration of computation and communication

The new technologies of co-design of hardware architecture and programming tools of Application-Specific Processors that have been developed by TARGET and are being transferred from EURETILE will be an integral part of next-generation products of the leading EDA tools vendor Synopsys.

HW/SW co-design tools can operate at the level of elementary tiles. In EURETILE, Target Compiler Technologies, in cooperation with INFN investigated the application of its retargetable tools-suite for the design and programming of Application-Specific Processors (ASIPs). Building on this technology, Target contributed to the project in two major ways. First, new software-programmable accelerators can become part of the elementary tiles. These accelerators take the form of ASIPs optimised for the typical numerical kernels of the applications envisaged in the project. Architectural exploration is based on profiling of application code in the retargetable SDK. In addition, the tools generate efficient RTL hardware models of the ASIP, enabling a quick implementation on FPGAs. Secondly, Software Development Kits (SDKs) have been developed for the ASIP accelerators. Key elements of these SDKs are an efficient C compiler and an on-chip debugger. Third, TARGET investigated the application of ASIP to the acceleration of the DNP/APENet+ interconnection system.

## 3 Main scientific and technologic results and foregrounds

## 3.1 Many-Tile Platforms and Many-Process (Dynamic) Applications

Each hardware tile includes (a set of) general-purpose multi-core processors. The tile is equipped with a faulttolerant distributed network processor for inter-tile communications. The tile can also include specialized accelerators. The programming environment maps multiple dynamic applications onto the many-tile hardware architecture. This elaborated high-level programming model specifies each application as a network of autonomous processes, enabling the automatic generation and optimization of the architecture-specific implementation. Behavioral and architectural dynamism is handled by a hierarchically organized runtimemanager running on top of a lightweight operating system. To evaluate, debug, and profile the generated binaries, a scalable many-tile simulator has been developed. High system dependability is achieved by combining hardware-based fault awareness strategies with software-based fault reactivity strategies. We demonstrated the capability of the software design flow to exploit the parallelism of many-tile architectures, using a set of embedded and high performance computing benchmarks targeting both the simulated and the hardware platforms, for applications described by a few hundreds of software processes, mapped on a few hundreds of hardware and/or simulated processors. Our approach reduces the "accidental complexity" when programming many-process applications and facilitates the hardware/software co-optimization of many-tile, many process systems. It automatically synthesizes architecture specific implementations and assists in the validation of many-process application and dynamic scenarios on many-tile systems. The project delivered a proprietary hardware for 3D-toroidal interconnect, equipped with fault-awareness hardware mechanisms, that can be used in conjunction with off-the-shelf interconnects. We also delivered a simulator of neural activity and synaptic plasticity that will be used 1- for biological simulations; 2- to generate complex traffic patterns that can be used to drive the design of future interconnect systems and computing nodes dedicated to brain simulation.

At the highest level of abstraction, the proposed design flow is represented by the following Y-chart:

The three layers of the EURETILE software design flow

# 3.2 EURETILE Design Flow: Many-process, dynamic applications on Many-tile platforms

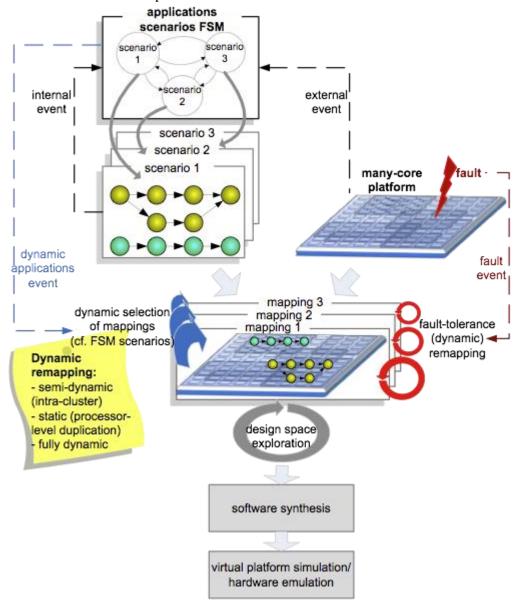

The EURETILE design flow maps a set of dynamic applications that are specified as a network of processes onto a many-tile platform in a number of steps, as illustrated in the following figure.

EURETILE design flow to map a set of dynamic applications onto a many-tile platform.

# 3.2.1 <u>Description of applications and scenarios: process networks and finite state machines</u>

The input to the design flow is an abstract specification of the target architecture and a set of applications. Each application is specified according to the DAL programming model that specifies each application as an Expandable Process Network (EPN) [Schor, 2013a]. An application that is specified as an EPN consists of a set of autonomous processes, which communicate through point-to-point FIFO channels. The functionality of each process is specified in C/C++. In addition, some processes might also have a structural specification that specifies the functionality of the process as another process network. By specifying each application as an EPN, the application's best degree of parallelism can be selected automatically by the design flow so that scheduling

and inter-process communication overheads are minimized. In addition, as EPNs can be considered as an extension of Kahn process networks (KPNs) [Kahn, 1974], data races, non-determinism, or the need for strict synchronization are avoided. Each application may have its own performance requirements that must be met independent of the other applications.

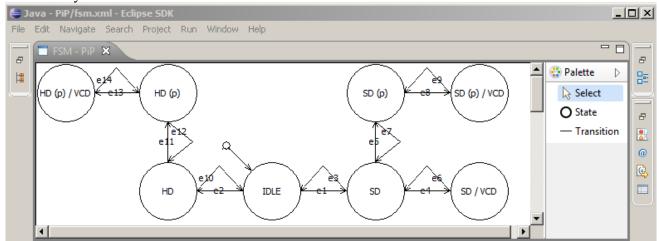

Interactions between applications are represented as a finite state machine (FSM) with each state representing an execution scenario, i.e., a certain set of applications running in parallel. Transitions between scenarios are triggered by events generated either by running applications or by the operating system (OS).

A first functionality check of the individual applications is realized using the DAL functional simulator. The DAL functional simulator executes each process as a POSIX thread on a host machine, thereby providing application-profiling data at a functional level. For more accurate performance results as, for instance, the runtimes of processes, the system must be simulated on the VEP.

#### 3.2.2 Optimization of the mapping using the VEP

During design space exploration, parallel processes are assigned to tiles and the applications are refined. Using the performance results derived from the VEP, the assignment of the processes (the so-called mapping) and the structure of the applications are iteratively improved until the performance requirements are fulfilled.

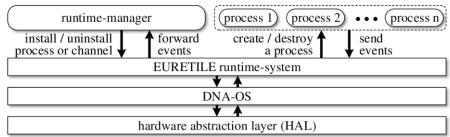

### 3.2.3 The software stack generated by the EURETILE design flow

During software synthesis, a four-layer software stack is generated that consists of application layer, runtime-system, OS, and hardware abstraction layer (HAL), see the subsequent figure for illustration. The employed tool chain first transforms the DAL processes to low-level threads that can be executed on top of DNA-OS [Guerin, 2009]. DNA-OS is a lightweight embedded OS that is used as OS in the proposed software stack. Afterwards, the tool chain generates one instantiation of the software stack for each tile.

Software stack generated by the EURETILE design flow.

## 3.3 Fault Management on EURETILE platforms

Integrated circuit technology scaling is increasingly making processors more vulnerable to faults. For instance, modern processors are more likely to experience single-event upsets, which were uncommon only a few years ago, and smaller transistors are responsible for higher power densities, which in turn cause temperature hotspots. In EURETILE, a high system dependability is achieved by combining fault avoidance, fault tolerance, and fault reactivity strategies. While the former two strategies are implemented at system-level by elaborating properties of the programming model, fault reactivity involves programming model, OS, and hardware. In the following, we will describe the key concepts of these fault management strategies.

#### 3.3.1 Fault avoidance

Temperature related reliability issues are avoided by applying thermal-aware optimization strategies [Schor, 2013b], [Thiele, 2013]. During design space exploration, system designs that do not conform to peak temperature requirements are ruled out using formal thermal analysis methods. The methods are based on real-time calculus that is widely used to analyze and optimize real-time systems.

#### 3.3.2 Fault tolerance

Applications with stringent performance requirements are duplicated during design space exploration [Rai, 2014]. In particular, the considered fault management strategy replicates critical sub-networks and inserts a special replicator channel that duplicates the stream to the corresponding input ports of the replicas. Similarly, a specially introduced selector channel arbitrates (merges) the data streams from the output ports of the replicas.

#### 3.3.3 Fault reactivity

While the first two fault management strategies are applied at design time, fault reactivity is employed at runtime as a mechanism to react to faults. The proposed fault reactivity mechanism does this in a number of steps. First, the occurrence of a fault is detected by a novel hardware design paradigm named LO|FA|MO [Ammendola, 2014], which is based on fault monitors that are added to each tile. Once they detect a fault, LO|FA|MO propagates the information along the system hierarchy to the runtime-manager, which reacts to the fault by migrating processes that are assigned to a faulty processor to an alternative processor. To include the evaluation of all possible failure scenarios in the design time analysis, spare processors and tiles are allocated during design space exploration and used by the runtime-manager as target for process migration.

## 3.3.4 Task migration between tiles

Task migration has been known for a while in symmetrical multi-processor (SMP) architecture, as a solution to balance the workload between the different computation resources. This may be as well an answer to temperature hotspots, by shifting the execution of a task to another core or tile. In case of multi-tile, there is no shared memory that may ease communications, and the task migration becomes a real challenge. The chosen solution is a light migration method, which does not require any modification of the OS, keeping the OS as simple as possible (no virtual memory support, no dynamic loading).

The specification in DAL integrates the tile where a given task is supposed to migrate. A copy of the task is generated, but the replica is not started anymore. In case of migration request, the original task is stopped, and the duplicate is launched. We garantee that no message or data are lost during the migration. This migration method is built with additional tasks running on the different tiles to manage all the changes when a migration request is called. The overhead in terms of code size or performance is only of few %, and could be considered as negligible for complex applications.

#### 3.4 Specification of the architecture of the target execution platform

In EURETILE, an abstract description of the architecture in terms of a hierarchically organized many-tile platform is elaborated. This representation is a generalization of the well-known tile-based multiprocessor model [Culler, 1999], which has been successfully applied in academia and industry.

The basic entities of the architecture model considered in the EURETILE project are the tiles. Each of them contains a distributed network processor (DNP), multiple general-purpose processors, and local memories. All processors in a tile might have access to commonly shared memory. Depending on the application usage, the tiles might also contain specialized hardware accelerators, like DSPs, ASIPs, FPGAs, or, in the latest hardware evolution, (GP)GPUs. The DNP is responsible for inter-tile communication and provides the interface to the network. The upper levels of the hierarchically organized architecture are constructed according to the distributed memory paradigm whereby multiple tiles together form an additional entity called cluster, which can be controlled autonomously.

As discussed in the previous section, spare processors and tiles are allocated at design time so that the runtime-manager can efficiently react to faults. The number of spare hardware elements depends on the number of faults that must be able to be tolerated. We call the abstract representation of the architecture without spare processors, tiles, and clusters the virtual representation of the architecture.

#### 3.5 Programming model: applications plus scenarios

Next, we describe the considered high-level specification of the system that we propose to specify applications and execution scenarios. The basic idea of the programming model is to specify each application individually as an expandable process network (EPN) [Schor, 2013a] and to specify the interactions between the applications

as a finite state machine [Schor, 2012]. With this programming model, complex and dynamic interactions between applications can be specified.

### 3.5.1 Application Specification

Each application is specified as an Expandable Process Network (EPN). The EPN semantics extends the KPN semantics [Kahn, 1974] by abstracting several possible granularities in a single specification. More detailed, an application specified as an EPN has a top-level process network that can be refined by hierarchically replacing individual processes by their structural specification. The structural specification describes the functionality of an application as another process network. This enables the automatic exploration of task, data, and pipeline parallelism by two refinement strategies, namely replication and unfolding. Replicating processes increases data parallelism and structural unfolding of a process increases the task and pipeline parallelism by hierarchically instantiating more processes in the process network. In addition, the functionality of each process is also specified in C/C++. The proposed application-programming interface (API) is composed of three procedures. The init procedure is executed once when the application is started. Afterwards, the execution of a process is split into individual executions of the fire procedure, which is repeatedly invoked. Finally, the finish procedure is called before the application is stopped. Each process can read from its input channels and write to its output channels by calling the high-level read and write procedures. Moreover, each process has the ability to request a scenario change by calling the send\_event procedure. In addition, the topology of the application, i.e., the connections between processes by FIFOs, is specified in an XML format.

#### 3.5.2 Execution scenarios

The dynamic behavior of the workload is captured by a set of execution scenarios forming a finite state machine (FSM). Each state represents a set of concurrently running or paused applications and each state transition corresponds to an application start, stop, pause, or resume request. Starting an application involves the installation of all processes and all FIFO channels of the application. After executing the init procedure of all processes of the application once, the fire procedures are iteratively executed by the scheduler. On the other hand, when an application is stopped, the fire procedure of all processes is aborted and the finish procedure is executed once. Finally, all processes and all FIFO channels are removed.

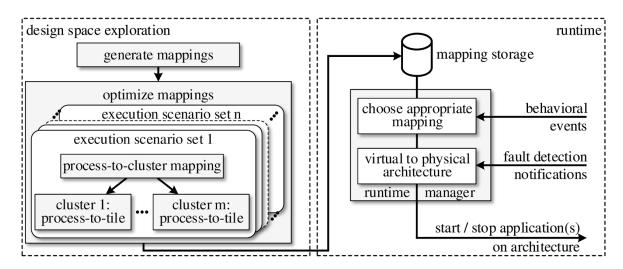

#### 3.6 Mapping strategy

The mapping decides on the distribution of the processes on the architecture. As typical mapping strategies that calculate a single mapping are no longer capable of efficiently utilizing the hardware if the functionality of the system can change at runtime, a hybrid design time / runtime mapping strategy is elaborated in EURETILE [Schor, 2012]. At design time, an optimal mapping is calculated for each application and scenario where the application is running, whereby the virtual representation of the architecture is used as target architecture. Then, a runtime-manager controls the dynamic behavior of the system. Whenever an application is started or stopped, it first selects the appropriate mapping (onto the virtual representation) and then maps the virtual representation onto the physical architecture. This enables the runtime-manager to react to faults without recalculating the mapping by just adjusting the binding of the virtual representation onto the physical architecture. In the following, we will detail the design time analysis and the runtime management. The overall hybrid mapping strategy is illustrated below.

Hybrid mapping environment.

#### 3.6.1 Design time: analysis and optimization

At design time, an optimal mapping for each pair of application and scenario, where the application is running, is calculated [Kang, 2012]. Therefore, the output of the design space exploration is a collection of optimal mappings and exactly one mapping is valid for a pair of application and scenario. To minimize the reconfiguration overhead, an application has the same mapping in all connected execution scenarios so that a running application is not affected by the start or stop of another application.

More detailed, a two-step procedure is applied during design space exploration in order to efficiently calculate the mappings. First, it is calculated, which pairs of application and scenario must use the same mapping so that no process migration is required. We do that by calculating for each application separately the maximally connected components of a sub graph, which only contains the scenarios where the application is running. At the end of this step, one mapping is allocated for each component of the sub graph. Second, the previously allocated mappings are optimized so that the objective function is minimized and additional architectural constraints (e.g., processor utilization, link bandwidth, and chip temperature) are fulfilled. The objective function depends on the intended use and may include more than one objective.

However, multi-objective meta-heuristics, that have been successfully applied to solve the mapping problems of multi-tile systems, are no longer effective for many-tile systems due to the scale of the investigated problem. Therefore, a multi-objective mapping optimization technique is used that overcomes this shortcoming by decomposing the mapping problem into independent sub-problems. As illustrated in the figure above, two different problem decompositions are considered: the execution scenarios are decoupled into independent sets and an architecture-based decomposition is applied that first assigns processes to clusters. Afterwards, and for each cluster separately, the processes are assigned to the tiles.

#### 3.6.2 Runtime management

The task of the runtime-manager is to send commands to the runtime-system so that the execution semantics of the system is ensured. To this end, the runtime-manager receives and processes behavioral events and fault detection notifications. A behavioral event is sent by an application and triggers a scenario change. A fault detection notification is sent by LO|FA|MO if a hardware fault has occurred. The latter only changes the binding of the virtual representation onto the physical architecture, but not the mapping of the applications onto the virtual representation.

Consequently, the runtime-manager consists of two components. The first component is responsible to handle behavioral events and ensures the execution semantics. It is just aware of the virtual representation of the architecture. The second component processes the fault events and redirects the commands to the corresponding physical network. If the runtime-manager receives a fault event, it migrates the processes that are assigned to the faulty processor (tile) to a spare processor (tile) and changes the binding of the virtual representation onto the physical architecture by reconfiguring the second component to redirect the commands to the new target.

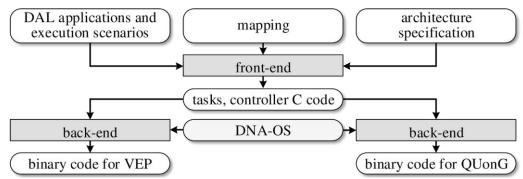

#### 3.7 Generation of the executable

We have defined a SW tool-chain that is able to accept as input a DAL model and generates a binary code that runs on different architectures: x86 simulator and QUonG, and iRiSC based VEP simulator. We can split this tool-chain in two parts, the front-end part transforms DAL model to a multi-threaded C code application, and then the back-end part compiles and links the code obtained in the front-end part on top of DNA-OS and generates the binary code for the targeted processors and architecture.

Overview of the software synthesis tool-chain as elaborated in the EURETILE design flow.

#### 3.7.1 DNA-OS

DNA-OS operating system implements exokernel architecture. The MIT defines exokernels as follows: "An exokernel eliminates the notion that an operating system should provide abstractions on which applications are built. Instead, it concentrates solely on securely multiplexing the raw hardware: from basic hardware primitives, application-level libraries and servers can directly implement traditional operating system abstractions, specialized for appropriateness and speed". DNA-OS supports or is based on traditional features of OS: Hardware abstraction layer (processor specific routines or low level boot code, ...), cores services (scheduling, synchronization...), device drivers (based on the POSIX.1-2001 standard concerning the files and devices access), memory management (system and user map)

#### 3.7.2 Software Synthesis Front End

The tool-chain starts with the following DAL input files:

- The platform description (in xml format)

- The mapping file (in xml format)

- All application network descriptions for each application (in xml format)

- C code of the application tasks (including the 3 required functions of the DAL model for each application: app\_init, app\_fire and app\_finish)

Moreover, we take as input the C code of the controller (master and slave tasks) which manages the overall behaviour of applications. The parsing of all these files determines the need in terms of communication channels as well as all tasks which are executed on each computing unit. By this way, we can produce a main C code for each processing unit with all the possible running tasks and all possible communication channels. The controller explicates for each state tasks that are running on each processing unit. When all tasks are created, all of them that are not supposed to be executed in the initial state are paused. When entering in a new state, some of them are resumed, and some of them are paused to fit with the state task execution specification.

#### 3.7.3 Software Synthesis Back end

The back-end part of the tool-chain consists in taking the C code (tasks, controller), the generated DNA-OS, and then to compile and link to get binaries. The two different target architectures (iRiSC-based for embedded domain and x86 QUONG machine for HPC) leads to two different tool-chain for what concerns the back-end.

## 3.7.4 <u>Hierarchical Run-time manager</u>

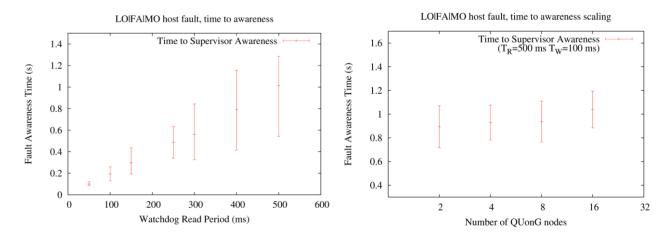

The dynamic behavior of the system is captured by a set of scenarios, formally described as a finite state machine (FSM). A hierarchically control mechanism is proposed. This hierarchy follows the architecture structure and is represented in DAL as a process network including three different types of controllers:

- slave controllers responsible just for the activity inside a cluster,

- interlayer controllers responsible for a network,

- master controller responsible for the upper level network that processes all events that cannot be handled by any other controllers.

The controller explicates for each state tasks that are running on each processing unit. When all tasks are created, all of them that are not supposed to be executed in the initial state are paused. When entering in a new state, some of them are resumed, and some of them are paused to fit with the state task execution specification.

Illustration of a hierarchically organized runtime manager.

### 3.7.5 Specificities of generation for VEP Simulated Platform

The IRISC processor is the main programmable processing unit used in the embedded flavour of the Virtual EURETILE Platform (VEP). This core was developed by RWTH Aachen following an ADL-based (Architecture Design Language) methodology, which is supported by a centralized processor model. From this centralized model, it is possible to generate a set of software development tools in a (semi-)automatic way, which is guaranteed to comply with the processor specification. The most notable tools among the IRISC toolchain are: lasm (LISA assembler), llnk (LISA linker), lcc (LISA C compiler) and ldb (LISA GDB). lasm, llnk and lcc enable creating binary executable objects for the IRISC processor. All tools provide a command line interface, which allows their integration into the DNA-OS (ported on the iRiSC) code generation process. These tools are already integrated into the EURETILE tool-chain, thus allowing the compilation and linking of the hardware-dependent software and the DAL applications for IRISC.

Additionally, there are IRISC tools, which support programmers during development and debugging. An application can be debugged either by using the command line GDB tool for the IRISC (ldb) or the Synopsys Processor Debugger GUI (pdbg). The former provides a traditional source-level debugger whereas the latter provides advanced features for low-level debugging of the processor (e.g. pipeline stages and registers). Both debuggers have been used for porting the DNA/OS version to IRISC and for verifying the tool-chain.

Finally, the IRISC tool-chain also provides a set of basic C libraries for software programming, namely the ISO C library (LIBC), a C runtime support library (LIBRT), a floating point emulation library (LIBFPE) and an abstraction layer library for retargeting to different OSs (LIBOS). It is worth to mention that LIBOS was ported to support DNA/OS as host operating system.

#### 3.7.6 Specificities of generation for QUonG Hardware Platform

DNA-OS has first been ported on x86 and QUonG hardware platform. The PCI is a local bus, which provides a simple way to connect boards, and it was introduced by Intel in 2004. PCIe (PCI express) is derived from the PCI (Peripheral Component Interconnect) and offers more powerful features. A PCIe driver has been developed in 2012. This feature is now used to access real hardware components on the QUonG board, as the QUonG board is connected to the motherboard using a PCI express bus. For two years, DNA-OS has supported the PCIe.

The driver represents about 10 000 lines of C code specifically written for DNA-OS (based on Linux PCIe driver).

# 3.8 The Virtual EURETILE Platform and Supporting Simulation and Debugging Technologies

Full-system simulation plays an essential role to enable early design exploration, bring up the system software and assess behavioural characteristics, that would be difficult to examine with hardware prototypes. Due to the massively parallel nature of the EURETILE architecture, the requirements for a full-system simulator environment exceed those of state-of-the-art tools, as it should:

- Provide fast and scalable simulation to experiment with a possibly large number of tiles/cores.

- Adapt to different use cases like software development and network scalability tests.

- Provide means to facilitate debugging and profiling of concurrent software.

- Allow fault injection to experiment with fault-awareness mechanisms at other system levels.

In EURETILE, research has been carried out on abstract and parallel simulation as well as on multicore debugging/profiling technologies. The outcome of this research was materialized in the Virtual EURETILE Platform (VEP) and a set of technologies which are described in the following.

#### 3.8.1 VEP characteristics and architecture

The VEP is a SystemC based simulator that models an embedded version of the EURETILE architecture. It allows simulating system configurations composed of several tiles arranged in a complete 3D grid and connected in a 3D toroidal topology. The simulator was created in a flexible way so as to allow runtime user specification of the number of tiles, memory address maps, processor frequencies, among others. VEP tiles contain a small form factor RISC processor tailored for embedded applications, namely the IRISC. The IRISC is created with Synopsys Processor Designer in the LISA language [Synopsys, 2014] and thus allows easy customizations for deriving new specialized ASIPs. A VEP tile also consists of TLM2 (transaction level) models of a memory management unit, memory blocks, a bus, a serial I/O interface, timers, a real-time clock, an interrupt controller and the DNP. A service network interface used for fault monitoring completes a tile. The VEP simulation models are augmented with debugging, tracing, and fault injection capabilities. For the latter, users can specify faults in different components and at precise points in time. Supported faults include processor and DNP breakdowns, severed DNP connections, isolation of tile groups, random bit-flips, among others.

#### 3.8.1.1 Processor model abstractions and optimized variants

The processor model that is in every tile incurs the major cost in terms of simulation speed and memory-footprint. The IRISC instruction-set simulator (ISS) was created at different levels of abstraction to allow trading off speed and accuracy. A cycle-accurate (CA) and an instruction-accurate (IA) IRISC model based on Just-in-time Cache-compiled (JIT-CC) technology [Nohl, 2004] were developed to facilitate two principal use cases: accurate performance analysis and software development. With these models, it is possible to simulate up to 200 tiles. Furthermore, two different optimized variants of the IA ISS were created to satisfy other use cases. The first variant, namely the IRISC IAP, is a simplified model without debug features but compatible with 64-bit compilation, which allows increasing the maximum number of simulated tiles. In a stand-alone simulation, the IRISC IAP executes approx. 24x and 4x faster than the CA and IA models, respectively. Scenarios running applications on 512 tiles have been successfully tested on the IAP but up to a few thousand tiles can be fit in memory. The second variant, namely the IRISC DBT-IA, is based on a dynamic binary translation (DBT) engine [Jones, 2009] that achieves higher speed than the JIT-CC engine. It executes approx. 170x, 30x and 7x faster than the CA, IA and IAP models, respectively, but only 32 tiles can be simulated in a single host due to its stringent memory consumption.

#### 3.8.1.2 Abstract simulation

The VEP can also be executed as an abstract platform (AS) where the ISS is replaced by a host-compiled simulator. In this form, every tile is provided by the Abstract Execution Device (AED), which is a SystemC module that can execute target software compiled for the host machine. The AED communicates with the DNP and other on-tile devices through an interface that is identical to that of the IRISC ISS. It also provides features like software timing annotation and limited visibility of tile-scope global variables. This mechanism was used

to ramp up DNP drivers, test software before the tool-chain for the IRISC was available and evaluate the network scalability. Due to its host-compiled nature, the AED is limited to software without target-specific constructs (e.g., inline assembly). To circumvent this issue, the hybrid simulation technology (HySim) [Kraemer, 2007] that was previously developed by RWTH for the FP6 SHAPES project was revamped. HySim has a virtualization tool-chain that automatically selects and instruments code that can be executed in AS mode, and switches dynamically between AS and ISS when needed. The new HySim can now be used with (i) customizable architectures [Jovic, 2012] and (ii) multi-core systems [Murillo, 2012a].

#### **3.8.1.3 VEP use cases**

The VEP allows targeting different use cases, as shown in the Table. While the CA version is good for accurately assessing the performance of applications, its speed is not enough for regular programming tasks. The IA models are better suited for software development. The IRISC IA is commonly used for software programming and debugging of medium size systems (32 to 200 tiles). The IRISC IAP is used for software testing in large systems and DNP network stress tests (from 200 tiles to approx. 1000 tiles). The IRISC DBT-IA is used for development and debugging of small systems running computational expensive applications. In AS mode, it is possible to simulate very large systems. Thus, the AS is better suited as a DNP-centric simulator to test network scalability and fault awareness features.

Summary of VEP levels of abstraction and use cases

|                  | IRISC CA                | IRISC IA                                                    | IRISC IAP                                           | IRISC DBT-IA                                                    | AED                                   |  |

|------------------|-------------------------|-------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|--|

| Stand-alone MIPS | lone MIPS ~1            |                                                             | ~25                                                 | ~160                                                            | ~3000                                 |  |

| Number of Tiles  | ~200                    | ~200                                                        | ~1000                                               | ~32                                                             | ~20000                                |  |

| Debug Support    | Yes                     | Yes                                                         | No                                                  | Yes                                                             | No                                    |  |

| Use Case         | Performance<br>analysis | SW development,<br>debugging, small<br>to medium<br>systems | DNP stress tests,<br>SW testing in<br>large systems | SW development<br>debugging,<br>complex. apps,<br>small systems | DNP network<br>scalability<br>testing |  |

#### 3.8.1.4 Other speed optimizations

The VEP has various optimizations which are commonplace in full-system simulators. Temporal decoupling (see e.g. [Murillo, 2012a]) and Direct Memory Interface (DMI) access were introduced. Moreover, unnecessary overhead caused by SystemC clock objects was mitigated by, first, adding a custom fast clock implementation and, second, combining multiple clocks with identical timing into single objects. Finally, a processor idle state that is made visible to the simulation kernel was introduced to avoid processing unnecessary core-related SystemC events.

#### 3.8.2 Parallel Simulation Technologies

Although the VEP is compatible with the regular OSCI SystemC kernel, the performance degradation of large system topologies called for the adoption of parallel simulation technologies. This resulted into the creation of two parallel SystemC kernels and a library for distributed SystemC.

#### 3.8.2.1 parSC, SCandal and legaSCi

The parSC simulation kernel [Schumacher, 2010] enables parallel execution by distributing simulation events (such as CPU clock ticks or interrupts) that happen at the same point in time (i.e., the same SystemC delta cycle) among different threads. This strategy is convenient for detailed simulation models (e.g., CA) since they usually have a high number of events occurring concurrently and can as such benefit most from fine-grained parallelism. The parSC approach is, however, prone to concurrency bugs (e.g., data races) because state is usually shared between different SystemC processes in a module. To mitigate this issue, SCandal [Schumacher, 2012a] is a tool designed to analyse non-deterministic traits in SystemC code that might lead to functional anomalies. It was specifically designed to target industry level simulators that use third party binaries where no source code

is available. Additionally, legaSCi [Schumacher, 2013] is an extension to parSC that enables race-free operation by restoring and enforcing sequential process execution, inside the simulation kernel. legaSCi enhances the parSC process scheduler such that all processes marked as part of the same legacy component are scheduled on the same OS thread. parSC with the legaSCi extensions achieves a performance of more than 2x when used with the VEP on a quad-core simulation host. As complementary work in the area of deterministic simulation, a deep analysis of the effects and causes of nondeterministic behaviour in sequential and parallel SystemC simulations was performed [Schumacher, 2012b].

#### 3.8.2.2 SCope

SCope [Weinstock, 2014] is a SystemC kernel that exploits coarse-grained parallelism in simulations. It achieves high speedups when simulating less detailed models, such as those compliant with TLM2. SCope groups several simulation models (e.g., the components of a tile) and then assigns the groups to different host threads. The groups then operate temporally decoupled with regards to the system, i.e., individual groups are allowed to advance in time without frequent synchronization with the other threads. By decreasing the amount of synchronizations, the overall performance is increased. On a quad-core host, SCope gives an speed-up of around 4x compared to OSCI kernel. Dynamic load balancing has also been implemented for SCope that enables moving around components from thread to thread at the SystemC module level. Load balancing has been proven on the VEP with application scenarios that examine different tile workload profiles. For fully unbalanced simulation scenarios, the simulator is 1.35x faster when the load balancing feature is enabled.

#### 3.8.3 Multicore Debugging Technologies

Software debugging for parallel systems is one of the most expensive tasks during the design cycle. The following presents the EURETILE multicore debugging technologies used with the VEP.

#### 3.8.3.1 The Whole-system Debugger – WSDB

Software debuggers for parallel systems should address key issues like abstraction, retargetability, scalability and convergence of information from different data sources. WSDB is a new generic full-system interactive source debugger based on a component-based architecture [Murillo, 2012b] that fulfills these requirements. WSDB offers APIs that facilitate interacting with systems composed of multiple cores. For instance, it allows iterating on groups of tiles, cores and threads for breakpointing, inspection and control. Furthermore, it can be easily extended to perform a multitude of debug tasks by setting user-defined callbacks on internally triggered events (e.g., OS-level events). Other features of WSDB include support for the ELF, DWARF and STABS formats, a flexible stack unwindig API, an API for defining OS-awareness layers, and a debugger plug-in for the Eclipse IDE.

#### 3.8.3.2 SWAT: System-wide Assertions

System-wide Assertions (SWAT) [Murillo, 2015] allow correlating concurrent events from different sources for debugging purposes. SWAT allows inspecting and evaluating software variables and hardware registers/signals as well as defining behavioural patterns with linear temporal logic (LTL), which are then monitored at runtime. Event correlations defined in SWAT are useful for debugging traditional sequential issues and concurrency bugs. Issues at the hardware/software boundary can also be handled efficiently with SWAT, as it provides the capabilities of a source debugger and an assertion-based verification system. SWAT provides a language and a compilation framework. The framework's output is an automatically generated runtime assertion monitor. These monitors are executed externally on a non-intrusive debugger without altering the target system's behaviour. SWAT can also be used as a low level language for finding bugs based on concurrency bug patterns [Murillo, 2011] or other similar specifications.

#### 3.8.3.3 Concurrency analysis and behaviour exploration framework

Dealing with concurrency bugs is a difficult task. Most bugs remain unnoticed and, when they appear, they are hard to reproduce. We developed a concurrency exploration framework for virtual platforms based on dynamic analysis of event ordering constraints [Murillo, 2014]. The approach identifies conflicting concurrent interactions among system components, which are in turn used by the framework to reproduce a previously observed behaviour or intentionally trigger a buggy states. The framework also enables precise control of the

execution of all individual software tasks and components on the target (at the level of monitored events). This is used by bug finding algorithms to manipulate the target's behaviour. An exploration process based on random constraint swapping, which helps to detect actual bugs, completes the debug approach.

#### 3.9 The Distributed Network Processor in VEP

The Distributed Network Processor (DNP) is the INFN intellectual property that implements the 3D torus network connecting the computing nodes in the EURETILE platform. It provides deadlock-free data packets routing and guarantees zero-copy data transfers by supporting the RDMA protocol.

A SystemC TLM model of the DNP is integrated in the VEP platform, one instance per tile. The DNP channels connect the tiles each other in a 3D mesh, and the component simulate the data transfer and routing functionality, with real hardware (APEnet+) latency timings. The DNP model allowed to validate the DNP architecture and to test its scalability. Moreover it has been used to prove the validity of the LO|FA|MO approach to systemic fault awareness (see next section), before of its hardware implementation.

As the model is lightweight and frugal in resource consumption, simulation techniques could be applied aimed at increasing the simulation speed and the possibility to scale the size of the simulated platform. The VEP tile processor (either IRISC or AED) can program the DNP, as a memory mapped device. A higher level API, the DNP RDMA API, allows application level programming, but a more user-friendly interface is the PRESTO library that, on top of the DNP RDMA API, provides MPI-like send/receive primitives for data exchange.

#### 3.10 LO|FA|MO: Fault Detection and systemic Awareness for QUonG and VEP

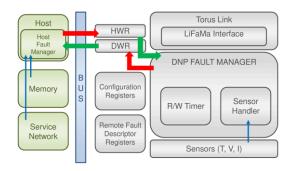

Local Fault Monitor (LO|FA|MO) is a systemic approach to fault detection and awareness for distributed systems. We wanted this approach to guarantee a *no-single-point-of-failure* fault awareness, meaning that the presence of a faulty component should not prevent the system to become aware of it. With these guidelines we designed LO|FA|MO as based on the following principles:

- A LO|FA|MO-enabled 3D toroidal network interface, i.e. the DNP, sporting a dedicated hardware component (DNP Fault Manager-DFM), able to assess the DNP status, and registers containing (encoded) the DNP status, the host status and the status of the first neighbours hosts in the 3D network.

- A dedicated software (Host Fault Manager-HFM) running on each host able to assess the host status and the DNP status as explained in the next point.

- A Mutual Watchdog mechanism between host and DNP on each node, in which the two are peers reading each other status from the watchdog registers and updating their own; periodical read and write timing (with Tread > Twrite) ensure that the peers can determine each other liveness.

- A Service Network for diagnostic messages and accessible by each HFM instance.

- The 3D network implemented by the DNPs as a secondary path for diagnostic messages issued by each DFM.

In the mesh of nodes we also name Supervisors those nodes that monitor the system at higher level in the hierarchy, thus being final target of all diagnostic messages and center of decisions about fault reactivity.

LO/FA/MO mutual watchdog mechanism in which host and 3D Network interface are peers monitoring each other by periodically reading and writing special DNP registers (DNP Watchdog Register and Host Watchdog Register).

An example of a host memory fault detection and systemic awareness. (Left) The fault is detected and reported in the Host Watchdog Register, the DNP Fault Manager reads the register and sends a diagnostic message via 3D network to the first neighbour nodes. (Right) Information about the fault carried by the diagnostic message coming from the 3D network is reported in the other node's DNP Watchdog Register where the Host Fault Manager can read it. Then Host Faul Manager can inform the Supervisor node through the Service Network.

#### 3.10.1 LO|FA|MO implementation on VEP

The DNP model in the VEP contains the DNP Fault Manager block as already mentioned in section 3.9. A Host Faut Manager software implementation runs in the AED processor to complete the mutual watchdog functionality. The entire LO|FA|MO approach has been validated on the VEP by using its fault injection facilities. The validation covered the DNP diagnostic logic in the model, the VEP service network and the AED Fault Manager. VEP configurations with 64 (4x4x4) and 512 (8x8x8) tiles were used for the validation.

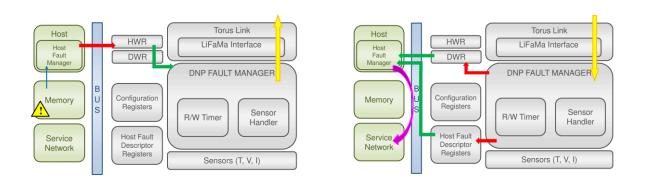

#### 3.10.2 LO|FA|MO implementation on QUonG

LO|FA|MO has been implemented and used efficiently on the QUonG cluster [Ammendola, 2014]. In this implementation the APEnet+ core contains a DFM component, whose resource occupancy (FPGA gates) is very low compared with those of the whole DNP core. The Watchdog Registers are on the FPGA and accessible in target mode on the PCIe bus in ~6 microseconds. Note that at the access rate corresponding to Tread and Twrite (in the range ~10-1000 milliseconds) the bus occupancy is very low.

(left) Time to obtain Supervisor awareness ( $T_{aw}$ ) in case of host breakdown fault, plotted varying the watchdog period  $T_{read}$ . For each  $T_{read}$  value the mean value and the minimum and maximum values are shown for  $T_{aw}$ .

(right) Time to Supervisor awareness ( $T_{aw}$ ) scaling the number of QUonG node running LOFAMO.  $T_{read} = 500$ ms and  $T_{write} = 100$ ms.

The DFM is able to embed diagnostic messages in the physical link protocol of the 3D network, leading to a zero impact of these messages on the NIC performance. Finally the HFM is a Linux multi-thread daemon running on each node CPU, but usage fraction is negligible.

## 3.11 Hardware Experimental Platform (QUonG)

QUonG is a comprehensive initiative aiming at providing a hybrid, GPU-accelerated  $x86\_64$  cluster with a 3D toroidal mesh topology, able to scale up to  $10^4/10^5$  nodes. During 2013, a QUonG cluster was assembled and put into service, with 16 identical tiles (nodes).

They are arranged into a 4x4 network mesh served by one 6-links APEnet+ card per tile. Each tile provides 2 Xeon Westmere-family CPUs, 2 M2075 NVIDIA GPUs and 48GiB of memory; QUonG tiles also partake in two supporting networks, InfiniBand— and GbE-based. Applications can use either the EURETILE software tool-chain (DAL+DNA-OS for QUonG), or standard high-level communication semantics like the Message Passing Interface (OpenMPI and MVAPICH2 implementations are available for InfiniBand and APEnet+ networks) or low-level, interface-specific ones like Verbs or Sockets Direct Protocol (SDP) for InfiniBand and the custom RDMA API for APEnet+. A disparate set of scientific codes has been run on QUonG, in order to stress-test the installation, among which the Distributed Polychronous Spiking Neural Network simulator. In parallel, joint work with TIMA led to a quite stable release of DNAOS on x86\_64 architecture whose highlights are the support of APEnet+ and Intel GbE Ethernet cards as channels for remote communication among DAL processes.

QUonG experimental many-tile hardware platform: 2013 installation

#### 3.12 The APEnet+ interconnection system

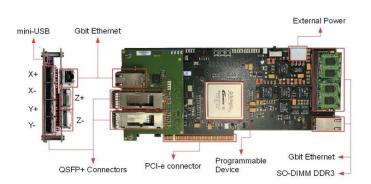

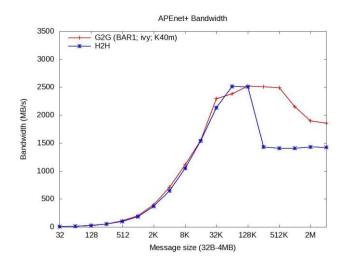

APEnet+ is a point-to-point, low-latency network controller developed by INFN for a 3D-torus topology integrated in a PCIe Gen2 board based on an Altera Stratix IV FPGA. It is the building block for the QUonG hybrid CPU/GPU HPC cluster inside INFN [Ammendola, 2011] and the basis for a GPU-enabling data acquisition interface in the low-level trigger of a High Energy Physics experiment [Ammendola, 2013]. The board provides 6 QSFP+ modules which are directly connected to its embedded transceivers; 4 out of 6 modules are placed onto the main board and 2 more reside on a small piggy back card, thus resulting in a 2-slot wide card. PCI Express mechanical compatibility is preserved with x16 cards. Each Altera Embedded transceiver is capable of a data rate up to 8.5 Gbps in fully bidirectional mode, and a single remote data link is built up by bonding 4 transceivers composing up a link operating at up to 34 Gbps. A complete assembly of the card is shown in figure below.

(Left) APEnet+ interconnect board: 2011 release. (Right) Outline of the main logic blocks of the FPGA architecture.

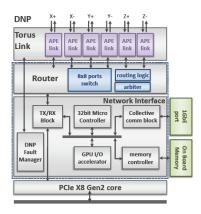

The Distributed Network Processor (DNP) is the core of the APEnet+ architecture; it acts as an offloading engine for the computing node, performing inter-node data transfers. The Torus Link block manages the data flow by encapsulating packets into a light, low-level word stuffing protocol able to detect transmission errors via CRC. The APElink [Ammendola, 2013a] data transmission system sustains a channel bandwidth up to 2.8 GB/s. APElink custom logic [Ammendola, 2013d] enables a global APElink efficiency of 93%. The Router component is responsible for data routing and dispatching, dynamically interconnecting the ports of the crossbar switch; it is able to simultaneously handle 7 flows @3.0 GB/s. The Network Interface is the packet injection/processing logic; it manages data flow to and from either Host or GPU memory. On the receive side, it provides hardware support for the Remote Direct Memory Access (RDMA) protocol, allowing remote data transfer over the network without involvement of the CPU of the remote node. An integrated microcontroller provided by the FPGA platform allows for straightforward implementation of RDMA semantics. The Network Interface is also able to directly access the memory of Fermi- and Kepler-class NVIDIA GPUs implementing GPUDirect V2 (peer-to-peer) and GPUDirect RDMA capabilities [Ammendola, 2013b]. A dedicated component (DNP Fault Manager) provides Fault Awareness capabilities as described in section 3.10.The hardware blocks in the DNP structure are depicted in figure below.

#### 3.12.1 GPUDirect technology on APEnet+

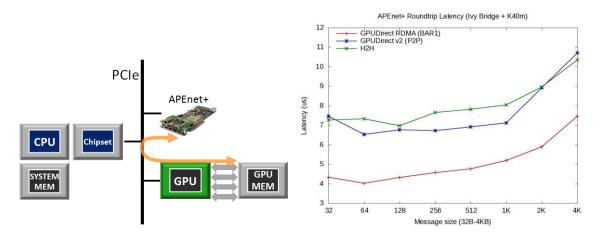

Fermi is the first NVIDIA GPU architecture which externally exposes a proprietary HW-based protocol to exchange data among GPUs directly across the PCI Express bus (PCIe), a technique which is generically referred to GPUDirect v2 or peer-to-peer (NVP2P). The NVIDIA peer-to-peer protocol basically allows one GPU to read and write the memory of another GPU, provided that they are on a compliant platform (suitable PCIe bus topology). This protocol can be exploited by a third-party device to gain direct access to the GPU memory. NVIDIA provides an additional access method for third-party devices, the GPUDirect RDMA (or BAR1), officially introduced a public API to support it on Kepler-based Tesla and Quadro GPUs. APEnet+ is the first third-party device to provide GPUDirect hardware support. The current implementation of the GPU data transmission module is able to generate the read requests towards the GPU with a steady rate of one every 80 ns and implements a pre-fetch logic which attempts to hide the GPU response latency.

(left) APEnet+/GPUDirect RDMA. (right): APEnet+ GPU-to-GPU and Host-to-Host latency

## 3.12.2 RDMA on APENet+

The Network Interface of APEnet+ implements RDMA, a reliable transport protocol in hardware supporting zero-copy networking with kernel bypass. The RDMA request is issued from an application running in user space to the local NIC and then carried over the network to the remote NIC without requiring any kernel involvement. For this to work, RDMA semantics imply three stages:

- a "registration" phase, when sender and receiver 'pin' the relevant areas of their (virtual) memory (making them ineligible for *swapping*) and resolve their physical addresses;

- a "rendezvous" phase, when sender and receiver pass to each other the address of the buffer to be transferred:

- the actual transfer phase, a "one-sided" operation initiated by the sender a PUT semantics or the receiver a GET semantics targeting the addresses registered in the first phase.

On the receive side the NIC needs to directly write the data to the destination buffer (DMA) requiring virtual to physical address translation. Buffer access (read/write) completion acknowledge is pushed into an *event queue* accessible to the application, that can pop it asynchronously.

### 3.12.2.1 RDMA task implementation and acceleration