## **Network of Excellence**

## **NEWCOM#**

Network of Excellence in Wireless Communications#

FP7 Contract Number: 318306

# WP2.1 – Radio interfaces for next generation wireless systems

# D21.1 - Description of EuWIn@CTTC technical facilities and interfaces, and preliminary plan of activities

| Contractual Delivery Date:      | April 30, 2013                                              |

|---------------------------------|-------------------------------------------------------------|

| Actual Delivery Date:           | April 30, 2013                                              |

| Responsible Beneficiary:        | CTTC                                                        |

| Contributing Beneficiaries:     | CTTC, CTTC/UPC, CNIT/UniBo, Bilkent, PUT, UCL, CNRS/Eurecom |

| <b>Estimated Person Months:</b> | 8                                                           |

| Dissemination Level:            | Public                                                      |

| Nature:                         | Report                                                      |

| Version:                        | 1.0                                                         |

This page is left blank intentionally

#### **Document Information**

| Document ID:           | D21.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Version Date:          | May 7, 2013                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Total Number of Pages: | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Abstract:              | The nature of this deliverable of WP2.1 ("Radio interfaces for next-generation wireless systems") is mainly descriptive; it introduces the EuWIn lab at large, providing detailed descriptions about its three sites (CTTC, CNIT/Bologna, CNRS/Eurecom), its goals, and the means to achieve them. It also includes an accurate report on the technical facilities that are available at EuWIn@CTTC and the interfaces through which they can be accessed. Finally, this document also includes the preliminary plan of activities (first JRA proposals, web portal, web meetings, workshops, training schools, industry liaisons, demonstration activities and experimental tours) together with |

| Marine relati          | the lab access policies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Keywords:              | EuWIn, CTTC site, localisation, Wireless systems, radio interfaces, research through experimentation, MIMO, GNSS, low-energy consumption, low emission, localisation, spectrum efficiency, channel measurements, channel modelling, channel database, GEDOMIS, GNSS-SDR, OpenInLocation.                                                                                                                                                                                                                                                                                                                                                                                                          |

#### **Authors**

<u>IMPORTANT</u>: The information in the following two tables will be directly used for the MPA (Monitoring Partner Activity) procedure. Upon finalisation of the deliverable, please, ensure it is accurate. Use multiple pages if needed. Besides, please, adhere to the following rules:

- <u>Beneficiary/Organisation</u>: For multi-party beneficiaries (CNIT) and beneficiaries with Third Parties (CNRS and CTTC), please, indicate beneficiary *and* organisation (e.g., CNIT/Pisa, CNRS/Supelec).

- Role: Please, specify: Overall Editor / Section Editor / Contributor.

| Full Name           | Beneficiary /<br>Organisation | e-mail                      | Role                           |

|---------------------|-------------------------------|-----------------------------|--------------------------------|

| Miquel Payaró       | CTTC                          | miquel.payaro@cttc.es       | Editor, Contributor            |

| Nikolaos Bartzoudis | CTTC                          | nikolaos.bartzoudis@cttc.es | Contributor                    |

| Carles Fernández    | CTTC                          | carles.fernandez@cttc.es    | Contributor                    |

| Pau Closas          | CTTC                          | pau.closas@cttc.es          | Contributor                    |

| Javier Arribas      | CTTC                          | javier.arribas@cttc.es      | Contributor                    |

| Roberto Verdone     | CNIT/Bologna                  | roberto.verdone@unibo.it    | Section Editor,<br>Contributor |

| Sinan Gezici        | Bilkent                       | gezici@ee.bilkent.edu.tr    | Contributor                    |

| Anna Umbert         | CTTC/UPC                      | annau@tsc.upc.edu           | Contributor                    |

| Claude Oestges      | UCL                           | claude.oestges@uclouvain.be | Contributor                    |

| Pawel Kryszkiewicz  | PUT                           | pkrysz@et.put.poznan.pl     | Contributor                    |

Distribution Level: Public Page 3

| Florian Kaltenberger | CNRS/Eurecom | florian.kaltenberger@eurecom.fr | Contributor |

|----------------------|--------------|---------------------------------|-------------|

| Davide Dardari       | CNIT/Bologna | davide.dardari@unibo.it         | Contributor |

## **Reviewers**

| Full Name       | Beneficiary /<br>Organisation | e-mail                   | Date      |

|-----------------|-------------------------------|--------------------------|-----------|

| Roberto Verdone | CNIT/UniBo                    | roberto.verdone@unibo.it | 29/4/2013 |

## **Version history**

| Issue | Date of Issue | Comments                                       |

|-------|---------------|------------------------------------------------|

| 0.1   | 4/4/2013      | First version                                  |

| 0.2   | 10/4/2013     | Integrated with common parts from Track Leader |

| 0.3   | 12/4/2013     | Added input from contributors                  |

| 0.4   | 15/4/2013     | Final version for internal review              |

| 1.0   | 29/4/2013     | Final version after internal revision          |

Distribution Level: Public Page 4

## **Executive Summary**

The nature of this initial deliverable of WP2.1 ("Radio interfaces for next-generation wireless systems") is mainly descriptive and its purpose is three-fold. The first goal is introducing the EuWIn lab at large, providing detailed descriptions about its three sites (CTTC, CNIT/Bologna, CNRS/Eurecom), its goals, and the means to achieve them. The second goal is to provide an accurate report on the technical facilities that are available at EuWIn@CTTC and the interfaces through which they can be accessed. More precisely, the main assets of EuWIn@CTTC are: GEDOMIS®, which offers an experimental environment that enables the prototyping of next generation broadband wireless communication systems, which feature bit-intensive PHY-layer techniques possibly combined, if desired, with multi-antenna schemes; GNSS-SDR, which is an open source GNSS software defined receiver addressing the design and implementation of multi-constellation, multi-band GNSS receivers; and OpenInLocation, which is an open experimental environment for research on indoor location composed of a set of extremely low-cost, programmable nodes (together with their wireless interfaces and their corresponding software repository). Finally, the third goal is to present the preliminary plan of activities (first JRA proposals, web portal, web meetings, workshops, training schools, industry liaisons, demonstration activities and experimental tours) together with the lab access policies that depend on the type of applicant: the access will be essentially free and open for Newcom# partners and associated institutions, and decided on a case-by-case basis for external institutions.

The most important outcome that stems from the contents in this deliverable is that EuWIn@CTTC is now ready to start the experimental activities of WP2.1.

Distribution Level: Public Page 5

## **Table of Contents**

| 1. | Intro | ductionduction                                     | 8    |

|----|-------|----------------------------------------------------|------|

|    | 1.1   | Glossary                                           | 9    |

|    |       | ,                                                  | •    |

| 2. | EuW   | In Scope and Activities                            | .11  |

|    | 2.1 I | ntroduction                                        | 11   |

|    |       | EuWIn Goals and Lines of Action                    |      |

|    | 2.2.1 | Real World Measurements                            |      |

|    | 2.2.2 | Real World Performance Evaluation                  |      |

|    | 2.2.3 | Links with Industries                              |      |

|    | 2.2.4 | Dissemination                                      |      |

|    | 2.2.5 | Durable Integration                                |      |

|    | 2.2.6 | World Contests                                     |      |

|    | _     | EuWIn Activities                                   |      |

|    | 2.3.1 | A Unique Portal                                    |      |

|    | 2.3.2 | Web Meetings                                       |      |

|    | 2.3.3 | Workshops                                          |      |

|    | 2.3.4 | Training Schools                                   |      |

|    | 2.3.5 | Industry Liaisons                                  |      |

|    | 2.3.6 | Demonstration Activities                           |      |

|    | 2.3.7 |                                                    |      |

|    | 2.4   | Γhe Three EuWln Sites                              |      |

|    | 2.4.1 |                                                    |      |

|    |       | EuWIn@UNIBO                                        |      |

|    | 2.4.3 |                                                    |      |

|    | 2.5 I | iaisons with Industries                            | . 17 |

|    | 2.5.1 | EuWIn@CTTC                                         | . 17 |

|    | 2.5.2 | EuWIn@UniBO                                        | . 18 |

|    | 2.5.3 | EuWIn@EURECOM                                      | . 18 |

|    | 2.6   | The EuWin Website                                  | . 18 |

|    |       |                                                    |      |

| 3. | EuW   | In Technical Facilities and Interfaces at CTTC     | . 20 |

|    | 3.1 I | ntroduction                                        | 20   |

|    | 3.2   | GEDOMIS <sup>®</sup>                               | 21   |

|    |       | Description                                        |      |

|    | 3.2.2 | Equipment                                          |      |

|    | 3.2.3 | Interfaces                                         |      |

|    |       | GNSS-SDR                                           |      |

|    | 3.3.1 | Rationale                                          |      |

|    | 3.3.2 | Description                                        |      |

|    | 3.3.3 | Project Ecosystem                                  |      |

|    | 3.3.4 | GNSS-SDR Open Source Software Stack                |      |

|    | 3.3.5 | Software Features                                  |      |

|    | 3.3.6 | Equipment                                          |      |

|    |       | OpenInLocation                                     |      |

|    | 3.4.1 | Rationale                                          |      |

|    | 3.4.2 | Description                                        |      |

|    | 3.4.3 | ·                                                  |      |

|    |       | Facilities and Lab Equipment Outside CTTC Premises | . 48 |

|    |       | Facilities and Lab Equipment at Bilkent University | . 48 |

|    | 3.5.2        | Facilities and Lab Equipment at UPC                                                                                                     | 48 |

|----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 3.5.3        | Facilities and Lab Equipment at UCL                                                                                                     | 50 |

|    | 3.5.4        |                                                                                                                                         |    |

| 4. | Preli        | minary Plans of Activities and Policies                                                                                                 | 55 |

| 4  | <b>1.1</b>   | ntroduction                                                                                                                             | 55 |

| 4  |              | Steps Followed                                                                                                                          |    |

| 4  |              | Research-Specific Plans of Activities                                                                                                   |    |

| 4  |              | Non-Research-Specific Plans of Activities                                                                                               |    |

| 4  |              | Access Policy                                                                                                                           |    |

| 5. | Con          | clusions                                                                                                                                | 63 |

| 6. | App          | endixes                                                                                                                                 | 64 |

| 6  | 6.1 <i>i</i> | Appendix: GEDOMIS <sup>®</sup> Testbed HW & SW Specifications                                                                           | 64 |

|    |              | Hardware                                                                                                                                |    |

|    |              | Software packages and licenses                                                                                                          | 69 |

| •  |              | Appendix: Specifications of the ADP Signal Conversion and Baseband                                                                      |    |

|    |              | sing Platform                                                                                                                           |    |

| -  |              | Appendix: Configuration, Test and Validatation of an Implemented 2x2 Money Money Transmitter and DL Receiver Using the GEDOMIS® Testbed |    |

| ľ  | 6.3.1        |                                                                                                                                         |    |

|    | 6.3.2        | <b>5</b>                                                                                                                                |    |

|    | 6.3.3        |                                                                                                                                         |    |

|    | 6.3.4        |                                                                                                                                         |    |

|    | 6.3.5        |                                                                                                                                         |    |

|    | 6.3.6        | •                                                                                                                                       |    |

| 6  | 6.4          | Appendix: Using GEDOMIS <sup>®</sup> to Develop the PHY-layer of Real-time Syster                                                       |    |

|    |              | 112                                                                                                                                     |    |

## 1. Introduction

EuWIn (the European Laboratory of Wireless Communications for the Future Internet) intends to become one of the durable and most successful outcomes of Newcom#. EuWIn fosters excellence in research in the field of wireless communications, and it aims at training a new generation of scientists prone to do research both from the theoretical and the experimental viewpoint.

The general theme of EuWIn is "Fundamental Research Through Experimentation". This motto emphasizes that the laboratory is not targeted to demonstration activities (though they might be considered sometimes); rather, the laboratory aims at making theoretical and fundamental research closer to the real world, in terms of adherence to the true problems that any new technology has to face at time of implementation, and of realism of model assumptions. As additional scope, EuWIn will represent a sort of gateway among the community of scientists doing fundamental research in the field of wireless communications, and industry.

Despite the intention to become a long-lasting initiative, EuWIn is described in this document only in terms of its plan of activities to be performed within the Newcom# course. EuWIn represents the experimental Track (Track #2) of Newcom#. EuWIn activities are devised as facilitators for the research performed within Track #1. Some of the EuWIn facilities will support the Joint Research Activities (JRAs) conducted within the Track #1 WPs. Inter-Track JRAs will be defined accordingly. On the other hand, EuWIn aims at creating a durable and self-sustainable environment that will survive after the end of Newcom#; therefore, all means to establish a structured integrated laboratory will be pursued and are described in this Deliverable.

EuWIn is composed of three sites, targeting at separate technologies and fields of experimentation: the laboratories of the research center CTTC of Barcelona (Spain), of CNIT/University of Bologna (Italy), and of the EURECOM institute of Sophia-Antipolis (France). The three institutions had developed experimental facilities in the context of other projects in the past years, and have committed to make them available to other Newcom# partners, through an integrated and open framework.

Additional Newcom# institutions, besides the three that committed towards the creation of an open laboratory context, have expressed the intention to contribute through some local experimental facilities to EuWIn: Bilkent, CNRS, PUT, UCL and UPC (third party of CTTC).

The three EuWIn sites cover aspects related to radio interfaces (mainly based on MIMO and PHY-layer algorithms) and localization techniques, at CTTC, flexible radio technologies over MIMO platforms, at CNRS/EURECOM and Internet of Things (IoT) and Smart City applications, at CNIT/UniBO. Overall, accounting for all institutions participating to Track #2, the experimental activities will deal with aspects of modulation, coding, signal processing, localization, radio channel characterization, routing, topology control.

The main scopes of EuWIn, the tools used to achieve integration within the sites, and the facilities available at each of the three sites, are discussed in Section 2 of this Deliverable. The Section also includes a short presentation of the EuWIn website, which is described in more detail in D36.1. In Section 3 the lab equipment made available at CTTC, is presented, and the objectives of the testbeds are clearly identified; two additional parallel Deliverables report on the details related to the CNIT/University of Bologna and EURECOM sites. The general parts of the three Deliverables are common to emphasize the unique scope and the

integrated strategy, while Section 3 is different for each of the three Deliverables. Section 4 shows the plan of EuWIn activities. It is detailed for the next six months, while the plans for the following two years will be described in the Deliverables due at M12. The Section also presents the policy for access to the lab facilities. The conclusions shortly discuss on the potential role of EuWIn within the scientific community and for the European industry context.

#### 1.1 Glossary

ADC Analog-to-digital converter

CIR Channel impulse response

DAC Digital-to-analog converter

DDS Direct digital synthesizer

DL Downlink

DoA Direction of arrival

DoD Direction of departure

DSP Digital signal processor

FBMC Filterbank multicarrier

FPGA Field programmable gate array

GLONASS Global'naya navigatsionnaya sputnikovaya sistema

GNSS Global navigation satellite system

GPL General public licenseGPS Global positioning systemHDL Hardware description languageHTML Hypertext markup language

IC Integrated circuit

JRA Joint research activity

LTE Long term evolution

LAN Local area network

LNA Low noise amplifier

MIMO Multiple input multiple output

OFDM Orthogonal frequency-division multiplexing

PAPR Peak-to-average power ratio

PCB Printed circuit board

PHY Physical layer

RF Radio frequency

RTF Rich text format

RRM Radio resource management

SDR Software defined radio

SFDR Spurious free dynamic range

SPI Serial peripheral interface

TXCO Temperature-compensated crystal oscillator

UL Uplink

USB Universal serial bus

USRP Universal software radio peripheral

VGA Variable gain amplifier VSA Vector signal analyzer

VSG Vector signal generator

WLAN Wireless LAN

XML Extended markup language

## 2. EuWIn Scope and Activities

This Section describes the general goals of EuWIn, the types of activities planned and the policy for accessing its facilities. Short introduction to the EuWIn website structure is also given.

#### 2.1 Introduction

As mentioned in Section 1, the three EuWIn sites deal with separate technical and scientific topics: Radio Interfaces (CTTC), IoT (CNIT/UniBo), and Flexible Communication Terminals (CNRS/EURECOM). However, the scope of EuWIn is to achieve an integrated laboratory able to address under a common environment the various topics of wireless communication technologies for the future Internet. To reach this goal, on the one hand the sites have been identified based on the complementarity of their competencies and facilities; on the other, some technical topics are common to two EuWIn sites, thus facilitating the integration of competencies and procedures: localization techniques are a common topic for CTTC and UniBO; MIMO based platforms for testing purposes are available at both EURECOM and CTTC; heterogeneous architectures and technologies for the IoT are considered both at UniBO and EURECOM sites.

All Newcom# institutions will be allowed to take advantage of this integrated (yet distributed) laboratory, through an open access policy described below. The procedures for the coordinated access to the lab facilities are also introduced in this Deliverable, and implemented through the EuWIn website. Newcom# associate partners will also be allowed to have access under agreed conditions, while institutions external to the Newcom# environment will undergo specific and selective agreements as described below.

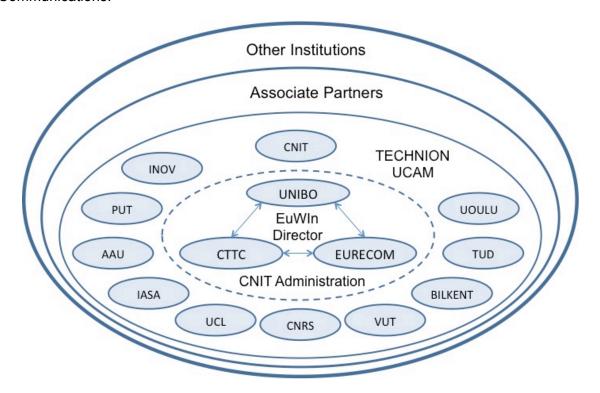

The vision of EuWIn can be represented through the spheres shown in Figure 2-1.

The inner sphere includes the three EuWIn sites. The integration of facilities and coordination of activities is under the responsibility of the EuWIn Director, Roberto Verdone (CNIT/UniBO). The three institutions, as detailed later, have been working during the first semester of Newcom# to extend and integrate their pre-existing facilities, creating the tools for their use by the rest of the Network of Excellence.

The second "internal" sphere includes all Newcom# institutions (the figure emphasizes those who, at time of DoW preparation, expressed commitment towards EuWIn. During the three years of Newcom# the set of these institutions might change). All Newcom# institutions have access to the EuWIn facilities, according to the open access policy defined later, free of charge.

The third "internal" sphere includes the associate partners of Newcom#, both those defined at time of DoW preparation (mainly industries) and those accepted by the consortium after project kick off. These institutions have access free of charge to the EuWIn facilities based on a selective process/policy described later.

Finally, the "external" sphere includes all institutions interested in having access from outside Newcom# to the EuWIn facilities. This sphere is based on a case-by-case consideration of the access conditions, which will depend on the type of activity foreseen, the facility/site of interest, etc.

At time of delivery of this document, the following Newcom# partners are involved in potential JRAs targeted at the exploitation of the EuWIn@CTTC facilities: AAU, Bilkent, CNRS, IASA,

PUT, UCL, and VUT. Moreover, the following additional institutions from outside Newcom# have declared strong interest into the EuWln WP2.1: ACTIX, Agilent, AVEA, U-Blox, NEC Labs, Orange Labs, Renesas Mobile, Samsung, Telecom Italia, Telefonica I+D, and Thales Communications.

Figure 2-1: The Newcom# Spheres.

The EuWIn website will specify and publicize for each sphere the access policy and the procedures for a coordinated exploitation of the laboratory facilities.

#### 2.2 EuWIn Goals and Lines of Action

The uttermost goal of EuWIn is the creation of a new generation of scientists willing to perform fundamental research through experimentation. Additionally, EuWIn, being one of the Tracks of Newcom#, aims at an active role within the Network of Excellence as an instrument for dissemination and link with industries.

These goals can be reached in the long term by developing instruments and activities which will allow the involvement, at different levels, of the largest possible number of researchers, from inside and outside Newcom#. EuWIn will therefore pursue its goals through the implementation of several types of actions:

- 1) Real world measurements helpful for fundamental research activities.

- 2) Real world performance evaluation of fundamental research results.

- 3) Links with industries, either associated to NEWCOM# or not.

- 4) **Dissemination** of NEWCOM# research outcomes.

- 5) **Durable integration** of resources and activities provided by NEWCOM#.

- 6) World contests open to all researchers, within and outside NEWCOM#.

These lines of action are discussed briefly in the following subsections.

#### 2.2.1 Real World Measurements

Real world measurements will be useful in order to extract from them models and parameters to be used in theoretical research. Radio channel characterisation, for instance, is of outmost relevance to scientists studying the link-level performance of wireless systems; human mobility modelling, link-level assessment of the bit error rate against SNR (signal-to-noise-ratio) performance, are examples of research activities which can take advantage of measurement campaigns and are useful to the evaluation of the performance of wireless networks. All the EuWIn sites (and other Newcom# institutions) have facilities which will allow the development of measurement campaigns aimed at the definition of suitable models to be used for the performance of wireless systems, either at link or network level, as specified later. This line of activity indeed will provide *inputs* to the theoretical study of link and network level performance of wireless systems, performed within Track #1, making them more realistic in terms of models used.

#### 2.2.2 Real World Performance Evaluation

Real world performance evaluation is a task performed in research either through mathematical modelling, simulation, emulation or experimentation; when the system under analysis is complex, the latter approach is the only one that is feasible. It requires flexible experimental facilities allowing the implementation of the link-level or network-level techniques/algorithms under evaluation. The EuWIn sites have developed facilities that are flexible enough in order to allow implementation of different techniques/algorithms designed by scientists performing theoretical research. This line of action therefore, will take the *outputs* of the research performed within Track #1, and provide assessment of the performance through experimentation.

#### 2.2.3 Links with Industries

EuWIn will represent the main Newcom# instrument to create links with industries; the lab facilities will be used as proofs-of-concept of the techniques/algorithms designed, studied and evaluated within Track #1. Representatives from industry will be invited at all EuWIn events, and the researchers involved in the JRAs performed within EuWIn will organise visits at the premises of companies. The industry-academia link, which was missing in its predecessor Newcom++, will be established within Newcom# thanks to the availability of the EuWIn facilities and testbeds.

#### 2.2.4 Dissemination

All EuWIn dissemination events, either intended for industry or academia, will have at least one of the EuWIn sites present, showing the facilities, making them available remotely, and reporting on the latest achievements. EuWIn leaflets, posters and video trailers will be generated and made available to all EuWIn researchers with the aim of creating a repository of promotional material to be used for dissemination purposes.

#### 2.2.5 Durable Integration

EuWIn intends to create a framework which will go beyond the duration of the Newcom# project. To this aim, all coordination, promotional and dissemination activities will be geared towards a longer horizon than the three years of expected duration of Newcom#. However, durable integration requires financial sources which should be found outside the Newcom# budget. EuWIn will seek for additional sources of funds through the participation of the

EuWIn institutions to competitive EC calls, and from the private sector (industries willing to access the EuWIn facilities).

#### 2.2.6 World Contests

Some of the EuWIn sites (among them, the one at UniBO) will launch international contests to test over the lab facilities techniques/algorithms designed by institutions willing to participate. This will create further visibility to the laboratory, while representing a potential source of incomes for future activities after the end of Newcom#.

#### 2.3 EuWIn Activities

The lines of action described in the previous subsection take the form of activities performed within Track #2 as it follows:

- 1) A Unique Portal: facilities, activities and repository of measurements;

- 2) Web Meetings, to coordinate and plan visits of researchers;

- 3) Workshops on experimental research;

- 4) Training Schools on experimental research;

- 5) Industry Liaisons;

- 6) **Demonstration activities:** at conferences, fairs, etc;

- 7) **Experimental Tours**: PhD students visiting the three sites in sequence.

Short description of the activities is given in the following subsections.

#### 2.3.1 A Unique Portal

Under the domain euwin.org, a website has been created (properly linked to the Newcom# website). The scope of the portal is to create a unique access to the laboratory, by providing shared documents, description of procedures for getting access to the facilities, and a repository of those measurement data that are shared and can be useful to the researchers involved in EuWIn activities. The website will also provide information on the events generated or participated by EuWIn, the contacts had with industries, etc.

#### 2.3.2 Web Meetings

Besides the usual web meetings held periodically by the three WP Leaders of Track2, EuWIn will organise web meetings open to all EuWIn participants in order to disseminate within the project information regarding the latest development of the lab facilities, to coordinate and schedule the access and the activities of the EuWIn-related JRAs. These web meetings will be called by the EuWIn Director depending on needs and requests, and the dates will be fixed through polls, informing all researchers at least 30 days before the meeting will take place.

#### 2.3.3 Workshops

To foster sensibility towards experimentation, EuWIn will organise workshops, with the contribution of both Newcom# researchers and scientists participating to other projects, which will aim at discussing the benefits of experimental research and compare the approaches toward open access platforms.

#### 2.3.4 Training Schools

One of the most important activities performed within EuWIn, apart from the experimental trials, is the organisation/contribution to training schools. Through the participation of EuWIn key researchers as lecturers and the organisation of experimental sessions at the schools, the attendees will be trained towards experimental research.

## 2.3.5 Industry Liaisons

Each of the EuWIn sites will establish liaisons with specific industrial labs and companies, identified based on the topic of interest of the site. The EuWIn sites will be then responsible for the organisation of periodic meetings with the industry representatives in order to create stable contacts that might bring to forms of support to the EuWIn activities in the long term.

#### 2.3.6 Demonstration Activities

The achievements got within Newcom# and the development of new facilities, will be demonstrated at fairs, exhibitions and other events participated by many industry representatives.

#### 2.3.7 Experimental Tours

The most challenging objective of EuWIn is the creation of a generation of researchers prone to fundamental research trough experimentation, with competencies spanning over different layers of the protocol stack. This goal can be achieved by letting PhD students get involved into activities performed over the experimental facilities of different EuWIn sites, dealing with separate scientific topics. These activities will be denoted as "experimental tours", as the students will visit different sites, performing experiments that will be properly coordinated in order to achieve a unique scientific goal through the integration of measurements achieved over separate testbeds.

#### 2.4 The Three EuWIn Sites

#### 2.4.1 EuWIn@CTTC

The CTTC site (<u>www.cttc.es</u>) features the following three high performance testbeds, which are the core of the EuWIn@CTTC assets:

- a) GEDOMIS® (GEneric hardware DemOnstrator for MIMO Systems): GEDOMIS® is an experimental platform that comprises a complete set of high performance baseband prototyping boards (FPGA and DSP-based), signal generation equipment, high-end RF frontends, signal analysis instruments, specialized software tools and APIs. A key instrument of the testbed is the EB Propsim C8 channel emulator, which can be configured to provide realistic mobility scenarios of both certified and user-designed channel models. The Propsim C8 operates in real-time and facilitates the verification and testing of system designs prior to field-trials. Hence, GEDOMIS® offers a lab environment that enables the prototyping of next generation broadband wireless communication systems, which feature bit-intensive OFDM PHY-layer techniques possibly combined, if desired, with multi-antenna schemes. Moreover, the prototyping boards of GEDOMIS® feature various energy consumption measurement blocks, which can be used to assess the energy-efficiency for a given hardware implementation.

- b) GNSS-SDR (Global Navigation Satellite System Software Defined Radio): GNSS-SDR is an open source GNSS software defined receiver that adresses the design and implementation of multi-constellation, multi-band GNSS receivers. According to its open nature, the source code is published under General Public License (GPL) v3, which secures

practical usability, inspection, peer-review and continuous improvement by the research community, allowing the discussion based on tangible code and the analysis of results obtained with real signals. In addition to the source code, the project offers a development ecosystem (website, code repository, mailing list, bug tracker) that aims to build a community of researchers, developers and users around the project. The ultimate goal is to provide high-accuracy positioning for the masses, and for free. There are many ways for researchers to contribute to the project, e.g., programming new features (algorithms, receiver architectures, etc.), optimizing existing algorithms, reporting bugs or debugging existing features, among many others. This facility's equipment comprises an RF signal generator (Agilent's Vector Signal Generator E4438C equipped with GPS Personality), an assortment of GNSS antennas, RF measurement equipment (oscilloscope, network analyzer, spectrum analyzer), a set of Universal Software Radio Peripherals (V1 and V2) and USB data grabbers.

c) OpenInLocation (an open lab for research on indoor location): The main objectives of this lab is to drive R&D and innovation in indoor location by evaluating state-of-the-art and commercial technologies in challenging environments, improving them in terms of enabling High-Definition Situation-Aware (HDSA) applications and services, and, finally, fostering collaboration to contribute with new ideas for indoor positioning, to disseminate results and outreach to new audiences beyond Newcom#. This lab is composed of a set of extremely low-cost, programmable nodes that can act either as anchor node or as a mobile node, the wireless interfaces for such nodes (WiFi, Bluetooth, ZigBee, etc.), sensors (in IC form), and the corresponding software repository.

The common features to these three labs is that they promote collaborative research by offering an adequate framework and tools and they are all based on the principle of reproducible research, which enables practical discussions on tangible problems.

#### 2.4.2 EuWIn@UNIBO

The EuWin@UNIBO site provides more than 200 wireless nodes implementing different types of radio interfaces, and deployed according to the following platforms:

Flexible Topology Testbed (FLEXTOP) – 100 nodes equipped with IEEE 802.15.4 radios distributed inside the lab over a regular layout creating an open and flexible platform for emulating several types of network topologies, achieved through proper software setting of the inter-node losses. This platform is based on over-the-air (OTA) implementation of software, meaning that NEWCOM# partners will be given remote access to implement the software;

Data Sensing and Processing Testbed (DATASENS) – An infrastructure of approximately 100 nodes using IEEE 802.15.4 radios deployed inside one of the University buildings, in rooms and corridors, implementing sensors able to monitor/emulate physical instances like light intensity, temperature, current drain, equipped with small LCD screens that will ease the management and control of application tasks. In addition to the nodes composing the fixed infrastructure, approximately 50 battery-supplied mobile nodes (with 802.15.4 devices) carried by people moving around, are part of the testbeds (Roaming Nodes);

Localization Testbed (LOCTEST) - Approximately 50 additional nodes with high-accuracy localization capabilities, using IEEE 802.15.4a or IEEE 802.15.4f Ultra-Wide Bandwidth (UWB) radios, will be deployed in the same building depending on the future commercial availability of low-cost UWB-based devices;

The infrastructure also includes some network coordination nodes equipped with mini-PC boards and different types of gateways (WLAN, LAN) for proper interconnection to the Internet.

### 2.4.3 EuWIn@EURECOM

EURECOM (www.eurecom.fr) is a research and teaching institute located in the Sophia Antipolis Technopole in the South of France. EURECOM's research activity traditionally focuses on 3 domains which have led to the creation of three research departments: Networking & Security, Multimedia Communications, and Mobile Communications. The Mobile Communications Department has its focus on digital signal processing for mobile communications, information theory, 4th generation and clean-slate cellular radio systems, wireless protocols, mobile ad hoc networks, software radios, and SW and HW prototyping. In addition to fundamental research, the department has strong expertise in open-architecture multi-way real-time radio platforms (www.openairinterface.org) for use in publicly-funded research projects aiming at demonstrating innovations at all protocols layers (RF to applications). The latter is provided to EuWIN for use within the network and afterwards. The OpenAirInterface.org (OAI) development and facilities primarily target cellular technologies (LTE/LTE-Advanced and beyond) and rapidly-deployable mesh/ad-hoc networks. The platform comprises both hardware and software components and can be used for simulation/emulation as well as real-time experimentation. It comprises the entire protocol stack from the physical to the networking layer. The objective of this platform is to provide methods for protocol validation, performance evaluation and pre-deployment system test.

#### 2.5 Liaisons with Industries

## 2.5.1 EuWIn@CTTC

Currently, the CTTC team involved in WP2.1 ("Radio interfaces for next-generation wireless systems") has links with many industry players, among which the most relevant follow:

AT4 Wireless (recently acquired by Agilent Technologies): This collaboration started in 2009, when the CTTC team started to develop, together with the AT4 Wireless team, the test platform E2010, which is designed to perform compatibility tests to LTE terminals. The experience gained through this collaboration has contributed to a knowledge transfer, which is foreseen to be very useful in Task 2.1.4 ("High spectrally-efficient radio interfaces").

AVIAT Networks: This collaboration started in 2012. CTTC is carrying out a series of projects for the Silicon Valley-based company AVIAT Networks. Among these projects, the most relevant for Newcom# is the project where CTTC is providing a baseband processing solution for the improvement of energy efficiency in new generation transmitters for wireless backhauling equipments. This collaboration can have a positive impact on CTTC's participation in Task 2.1.2 ("Low-energy-consumption and low-emission radio interfaces"). Moreover, within this same topic, CTTC has submitted a proposal in the Seventh Framework Programme together with the Slovenian branch of AVIAT Networks.

Nutaq (before Lyrtech RD): This collaboration started in 2012. Nutaq is currently commercializing a software IP that contains the physical layer of the WiMAX standard developed by CTTC, which is named BeMImoMAX (http://nutaq.com/public/files/products/bemimomax/bemimomax.pdf). The CTTC team is now adapting this IP to make it compatible with the LTE standard. If other IPs are obtained as a result of the experimental research performed within Newcom#, CTTC can study together

with Nutaq and the other partners involved in the research the possibility of commercializing them.

#### 2.5.2 EuWIn@UniBO

The EuWIn site in Bologna has links with many industries, owing to the participation to many EC projects and industrial contracts. The main industry links, related to the scopes of EuWIn, are mentioned here:

the FLEXTOP testbed developed within EuWIn is of interest to the research labs of Telecom Italia, with particular reference to IoT applications;

EuWIn@UniBo has a peculiar link with Embit srl, a small Italian company which is design centre for Texas Instruments and Freescale and the provider of all wireless devices implemented within the laboratory;

the EuWIn site in Bologna has a preferred link with Intel labs of Ireland, which also investigate smart city applications of wireless communications.

#### 2.5.3 EuWIn@EURECOM

OAI has explicit links with industrial partners who contribute to its development both within the context of publicly-funded projects and out of mutual interest on specific research subjects. Currently, the main industrial collaborators, which are, incidentally, affiliate members of the NoE, include:

Alcatel Lucent Bell-Labs (Villarceaux, France) contribute to optimized real-time signal processing for SDR, innovative protocol extensions to LTE, emulation tools based on OAI, interfacing of OAI to industrial-grade RF platforms (remote radio-heads - RRH).

Orange Labs (Beijing, China, subdivision of Orange France) contribute to optimized real-time signal processing for SDR, interfacing of OAI to other hardware platforms (custom and USRP).

Agilent (Beijing, China) contribute to optimized real-time signal processing for SDR.

Thales Communications (Gennevilliers, France) contribute to development of multi-hop protocols and resource allocation strategies for rapidly-deployable mesh networks and innovative signal processing for improving RF amplifier efficiency in terminals.

#### 2.6 The EuWIn Website

The EuWIn website has been designed using the same platform chosen for the Newcom# portal, i.e., Joomla. This makes their maintenance easier. It has been devised both as an instrument for facilitating cooperation among the institutions involved (through a private part used as repository of shared documents and measurement databases), and as a dissemination tool providing all the information needed to join the laboratory activities.

However, it is important to emphasise that the EuWIn website does not represent a duplication of the information reported in the Newcom# portal, and all official documents related to the project will be found only on the Newcom# portal. Therefore, deliverables and meeting minutes will be posted on the latter, whereas promotional material (leaflets, video

trailers, etc.) and documents describing in detail the lab facilities, will be found on the EuWIn website.

Moreover, the EuWIn website is integrated in the Newcom# portal, as all user credentials made available to Newcom# researchers to access the project portal will be imported on the EuWIn site, so that all Newcom# researchers will be given access to the private area of the EuWIn website under the same credentials.

The structure devised for the EuWIn website is as follows.

HOME it contains a short welcome message and describes the goals of EuWIn

STRUCTURE description of the lab structure is given, using contents of this Deliverable

→ Sites map, link to three institution websites

→ Director short descript of role, personal welcome message

→ WP Leaders short descript of roles, personal welcome messages

→ Partners mention of Newcom# partners active within EuWIn

→ Liaisons mention of the industries/labs/projects linked to EuWIn activities

FACILITIES general description of the various platforms

→ Platform#1 (eg GEDOMIS) description

→ Platform#2 (eg FLEXTOP) → Platform#3 (eg DATASENS)

→ Platform#4 (eg LOCTEST)

→ ...

ACCESS the general access policy is described

→ Documents link to public documents

→ Join forms to be filled for requesting access

→ Visit forms to be filled for proposing a visit to the laboratory sites

DEMOS inaugural video and images

→ one per demo realised, with some info (where, who, picture, what facility)

WORKSHOPS description of the philosophy behind the organisation of workshops

→ one per workshop organised, contributed (where, programme, what facility)

SCHOOLS description of the philosophy behind the organisation of schools

→ one page per school organised, contributed (where, programme, what facility)

REPOSITORY a username/password form to be filled for restricted access

#### CONTACTS

Concerning the repository, whose access will be restricted to Newcom# partners and affiliate institutions, it was agreed by the WP Leaders that it will contain the outcome of the measurement campaigns performed within the Newcom# JRAs, and the documents needed to coordinate/facilitate access to the lab facilities.

The first version of the website, released at M6, will replace the three pages DEMOS, WORKSHOPS, SCHOOLS, with one single page EVENTS. More details regarding the first version of the EuWIn website are found in D3.6.1.

## 3. EuWIn Technical Facilities and Interfaces at CTTC

This Section provides a description of the technical facilities that are available at EuWIn@CTTC together with the necessary interfaces to interact with them. Moreover, some additional facilities and equipments, which other partners intend to use and which are available outside the CTTC premises, are also described, as they are included in WP2.1.

#### 3.1 Introduction

The experimental activities performed at the EuWin@CTTC site will address aspects related to low-energy and low-emission radio interfaces (e.g., PAPR reduction algorithms). Moreover, applied research will also focus on novel high spectral efficiency radio interfaces where advanced coding strategies, e.g., polar codes, will be implemented and tested. In parallel to these experimental research activities, channel measurements, models, and databases will also be created and maintained to be able to validate the obtained results with practical channels that exist in real life; this activity will be partly carried out in cooperation with the COST Action IC1004 in which several partners involved in this lab (AAU, UCL, CNIT) participate. Finally, localization techniques will be addressed through the implementation of positioning algorithms in platforms based on inertial sensors, commercial GNSS ICs, etc. This latter activity will be tightly connected to the one performed at the EuWIn@CNIT/Bologna site.

In order to satisfactorily carry out the above mentioned activities, CTTC makes available the three high performance testbeds that have been briefly described in Section 2.4.1: **GEDOMIS®**, **GNSS-SDR**, and **OpenInLocation**. Their detailed description follows:

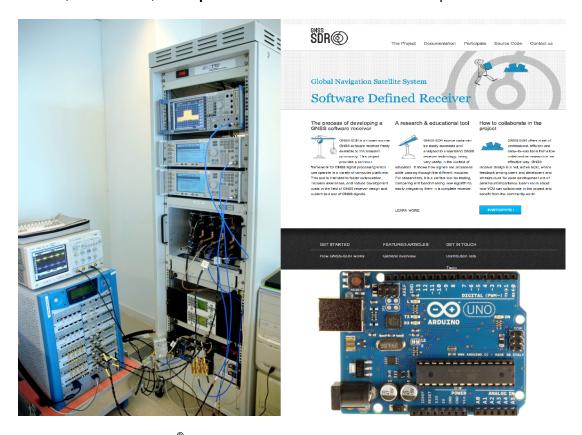

Figure 3-1: The GEDOMIS<sup>®</sup> testbed (left), the GNSS-SDR project webpage (top right), and one Arduino board from the OpenInLocation lab (bottom right).

## 3.2 GEDOMIS®

#### 3.2.1 Description

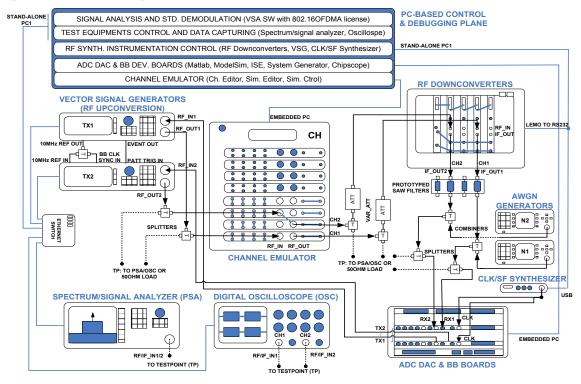

The GEDOMIS® testbed is an ideal platform to develop, test and validate the PHY-layer of modern wireless communication systems covering the prototyping and verification requirements of advanced solutions that target base stations, smart antennas, MIMO systems, Software-Defined Radio (SDR), geolocation, cognitive radio and high-speed test and measurement campaigns. In the past it has been used to develop and test real-time systems based on the IEEE 802.11, IEEE 802.16 and 3GPP rel. 9 standards. GEDOMIS® is able to host PHY-layer prototypes of multi BSs and multi User Equipments (UEs). A nonexhaustive list of supported PHY-layer development scenarios is given in table 1 (e.g., according to the number of transmitters-receivers, the number of antennas at each end, the transmission scheme and the signal bandwidth). Please note that wherever the signal bandwidth is mentioned to reach up to 10 MHz, it is an approximate calculation which needs to be thoroughly investigated in case the mentioned system is planned to be developed. At the same time, wherever a signal bandwidth of 20 MHz is mentioned, it refers to systems that have already been developed at GEDOMIS®. A schematic representation of GEDOMIS® is given in Figure 3-2, which includes the majority of the hardware equipment and boards used in the default set-up of the testbed. A brief description of its high-end instruments and boards is given in the following section. Detailed specifications are quoted in Appendix 6.1.

Figure 3-2: Schematic diagram of the default set-up of the GEDOMIS® testbed.

| Number of<br>Tx - Rx | Number of<br>antennas Tx- Rx | Antenna Scheme | DL with emulated<br>UL | DL and UL | Bandwidth (MHz) |

|----------------------|------------------------------|----------------|------------------------|-----------|-----------------|

| 1-1                  | 4x4 <sup>1</sup>             | MIMO           | yes                    | no        | up to 10        |

| 1-1                  | 2x2                          | MIMO           | yes                    | no        | 20              |

Using to 2 extra E4438C Vector Signal Generators from Agilent which are not available at GEDOMIS but could be made available (authorization is required since they belong to other research areas at CTTC).

| 1-1              | 1x2              | SIMO | yes | no               | 20       |

|------------------|------------------|------|-----|------------------|----------|

| 1-1              | 2x1              | MISO | yes | no               | 20       |

| 1-1              | 2x2 <sup>1</sup> | MIMO | -   | yes              | up to 10 |

| 1-1              | 1x2              | SIMO | -   | yes              | up to 10 |

| 1-1              | 2x1 <sup>1</sup> | MISO | -   | yes              | up to 10 |

| 4-41             | 1x1              | SISO | yes | no               | up to 10 |

| 2-4              | 1x1              | SISO | yes | no               | up to 10 |

| 1-3              | 1x1              | SISO | -   | yes (for the Tx) | up to 10 |

| 2-2              | 1x1              | SISO | yes | no               | 20       |

| 2-2 <sup>1</sup> | 1x1              | SISO | -   | yes (for the Tx) | up to 10 |

| 2-2 <sup>1</sup> | 2x2              | MIMO | yes | no               | up to 10 |

| 1-2              | 1x2              | MISO | yes | no               | up to 10 |

Table 3-1: Indicative PHY-layer development scenarios supported by GEDOMIS<sup>®</sup>.

#### 3.2.2 Equipment

## Signal generation HW:

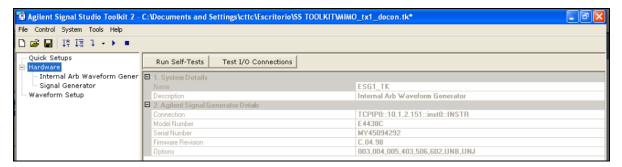

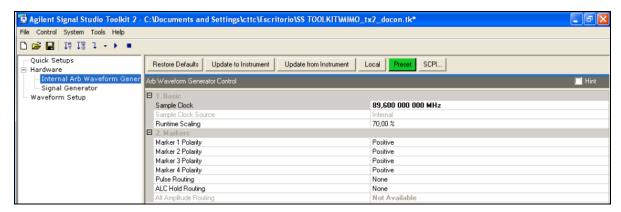

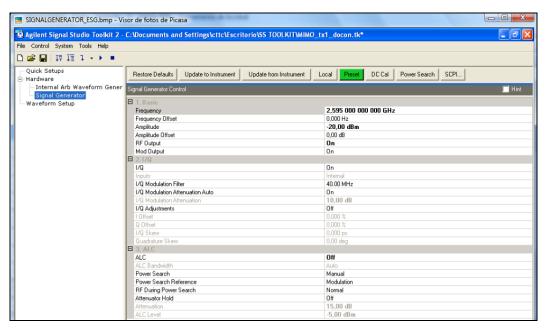

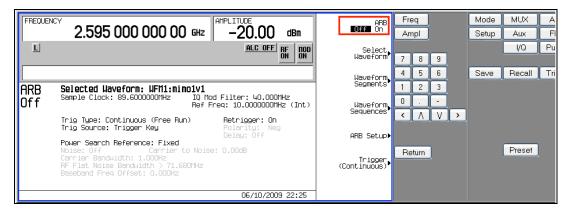

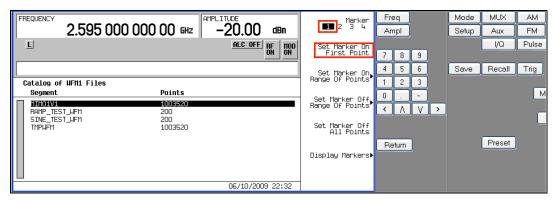

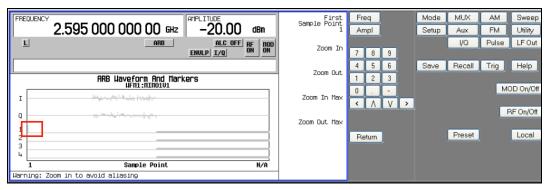

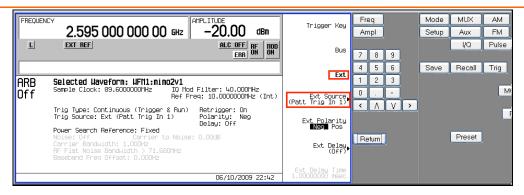

- Agilent Vector Signal Generators up to 6GHz: The E4438C ESG vector signal generator (VSG) combines outstanding RF performance and sophisticated baseband generation to deliver calibrated test signals at baseband, IF, and RF frequencies up to 6 GHz. It offers an internal baseband generator with arbitrary waveform and real-time in-phase/quadrature (I/Q) capabilities, ample waveform playback and storage memory, and a wide RF modulation bandwidth. By using more than two of these signal generators MIMO transmission is enabled.

- Agilent Baseband Studio digital signal interface module: The N5102A Baseband Studio digital signal interface module provides fast and flexible digital inputs or outputs for the E4438C ESG vector signal generator. In output mode, you can deliver realistic complex-modulated signals directly to digital devices and subsystems. In the input mode, the interface module ports custom digital inputs to the signal generator's baseband system, providing a quick and easy way of upconverting to calibrated analog IF, RF or microwave (μW) frequencies. In both operating modes, the interface module adapts to the specific device with the logic type, data format, clock features, and signalling being required.

- Applied Instruments NS-3 RF Noise sources up to 2.15 GHz: This broadband RF Noise Generator generates an extremely flat AWGN signal from 5 to 2150 MHz. The output level adjusts in 0.1 dB steps over a 30 dB range (-90 dBm/Hz max. output power, ± 2.0 dB flatness over full operating range) and can be ON/OFF pulse modulated. Typical applications: signal/carrier to noise generation (i.e. typically for BER vs SNR system testing), active device loading, interference, RF leakage, frequency response, intermodulation and insertion loss testing.

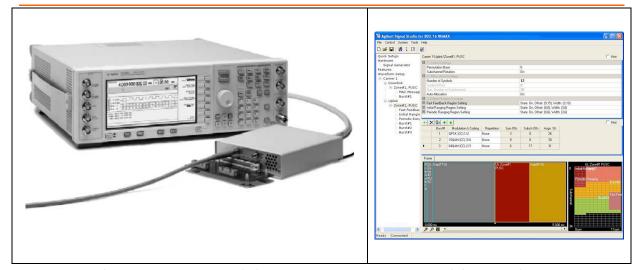

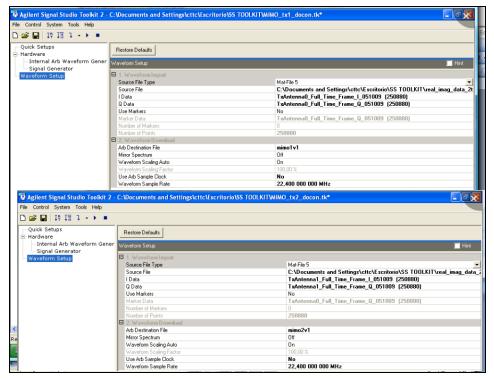

Figure 3-3: Signal creation HW & SW: Agilent Technologies ESG E4438C Vector signal generator and N5101A Baseband Studio PCI card (left) and Signal Studio SW (right).

#### Signal generation SW:

- <u>Agilent Signal Studio</u>: Agilent Signal Studio is a suite of flexible, standards-based signal creation software that allows cutting the time spent on signal simulation and provides a validated and performance optimized reference signal to better characterize, evaluate and fine tune designs. The CTTC licensed standard signals are Wireless Local Area Networks (WLAN) IEEE 802.11 a/b/g/j/p, WiMAX (IEEE 802.16-2004, IEEE 802.16e-2005 Wave2), and Digital Video Broadcasting DVB-T/H/C. The software enables the generation of a wide range of application-specific test signals, at baseband, RF, and microwave frequencies using the Agilent ESG vector signal generators available at GEDOMIS<sup>®</sup>. For downloading custom I/Q waveforms (e.g. MATLAB files) into the signal generators the application Signal Studio Toolkit is used.

- <u>Agilent Baseband Studio</u>: This SW is a suite of digital baseband hardware, software application tools, and accessories that enable digital baseband and RF designers to generate, capture, impair, playback, and emulate real world signal conditions. Baseband Studio applications can be used with the E4438C ESG vector signal generators, and PCs equipped with the N5101A Baseband Studio PCI card (not available in GEDOMIS<sup>®</sup>).

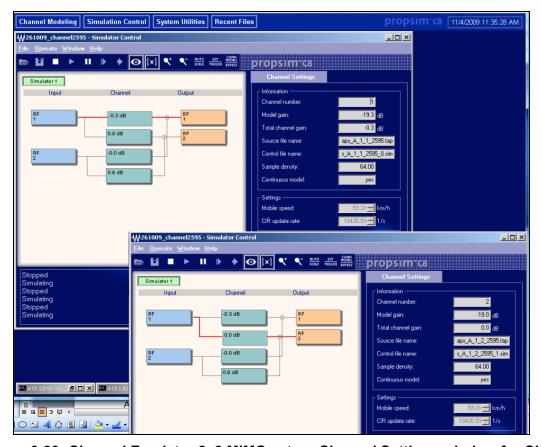

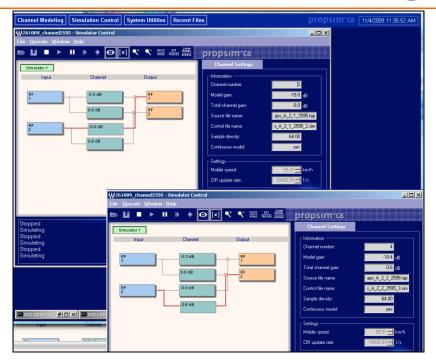

#### **Channel Emulation hardware & software:**

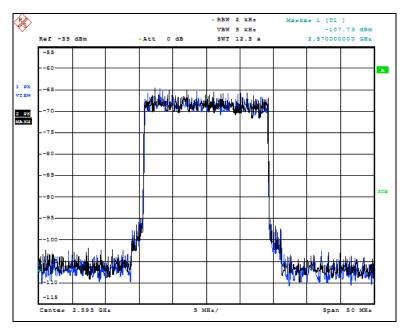

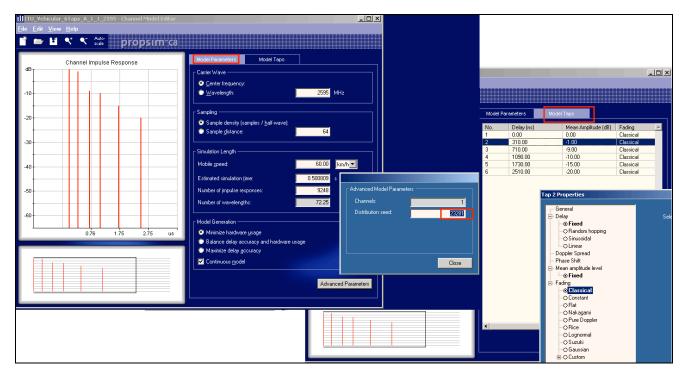

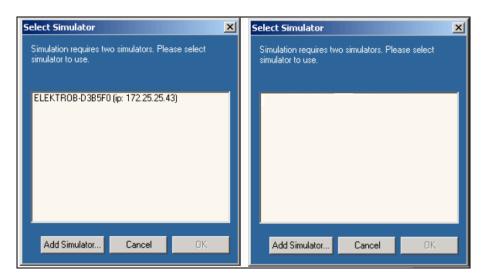

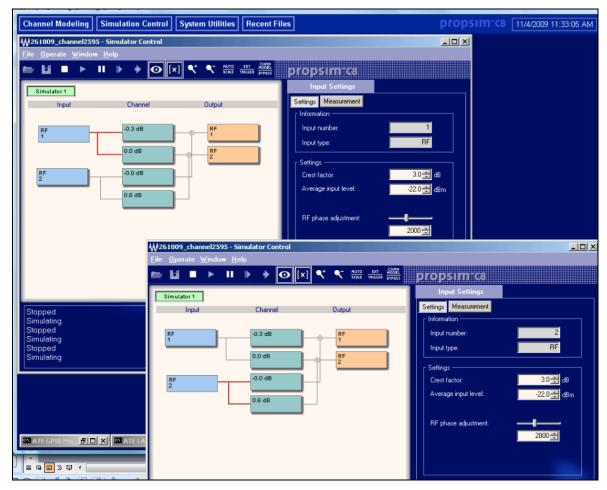

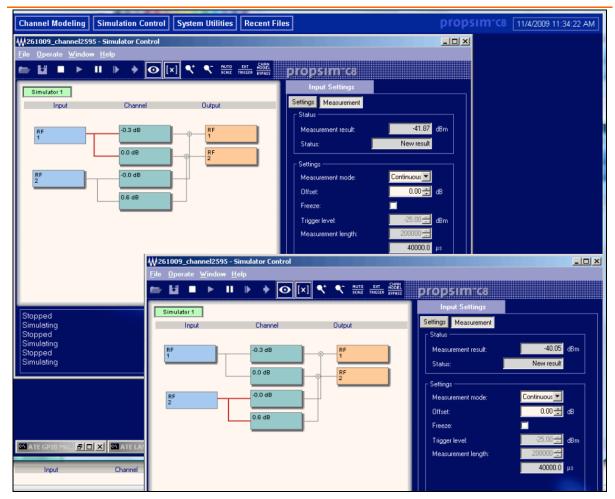

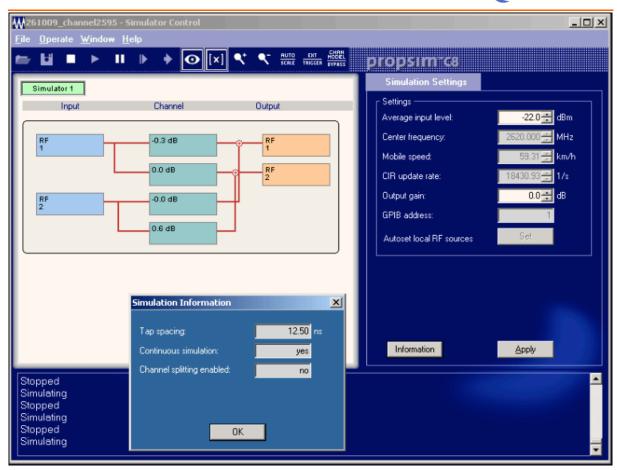

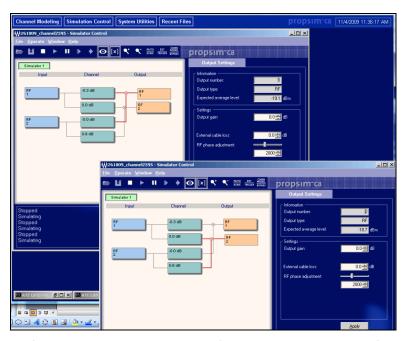

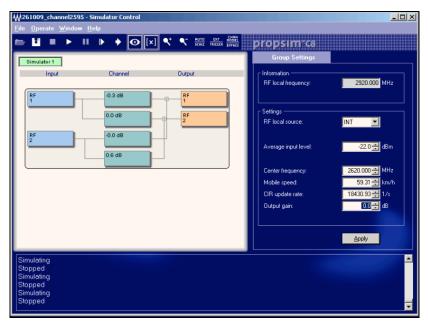

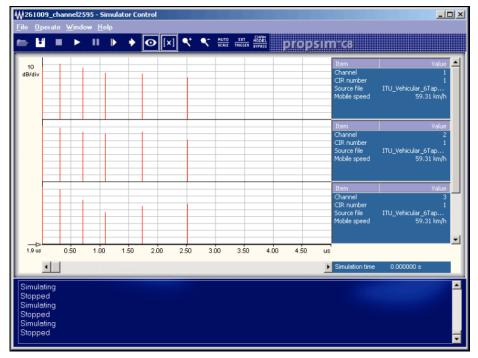

- <u>Elektrobit (EB) C8 Channel Emulator</u>: The EB Propsim C8 is a technology-independent radio channel emulator supporting all major wireless standards and signal types in a broad frequency range (350MHz to 6GHz, 70 MHz bandwidth with default option) covering established and future technologies. It allows users to perform realistic and accurate radio channel emulation supporting the development of most demanding wireless applications such as beam forming, 4×4 MIMO, network level testing, software defined radio and aerospace satellite communications.

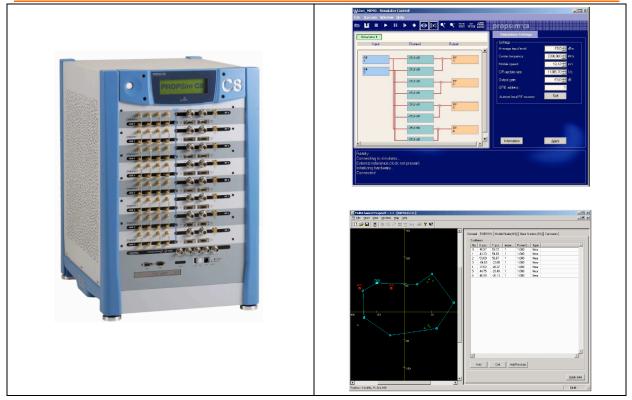

Figure 3-4: EB Propsim C8 channel emulator (left), Simulator Editor & Propsoft+ GUIs (right).

The physical radio channel characteristics, such as frequency, multipath propagation, fast fading, dynamic delays, attenuation, noise, interference and shadowing, can be emulated independently on each channel. The user can utilize all major standardized channel models or create its own radio channel models with a set of available versatile channel modelling tools. These tools provide means for modelling MIMO complex correlation or DoA/Direction of Departure (DoD), DoA/DoD spread and antenna geometry based beam forming for smart antenna applications. In addition to statistical and spatial channel models, the user can utilize measured channel data or data collected with various measurement tools (e.g. scanners and drive test tools) supported by EB Wireless Environment Solution. EB Propsim C8 is delivered with Windows 2000 and application software pre-installed including channel model, correlation and simulation editors. The channel emulator is also equipped with Propsoft+, a Channel Impulse Response (CIR) generator software that generates a set of time variant complex channel impulse responses from a user specified propagation environment.

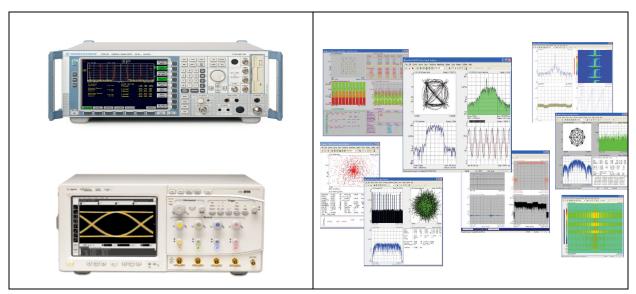

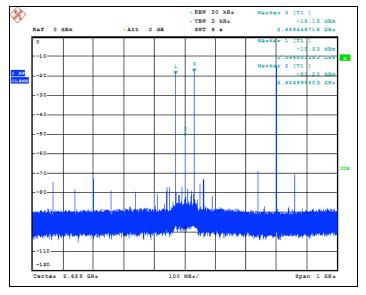

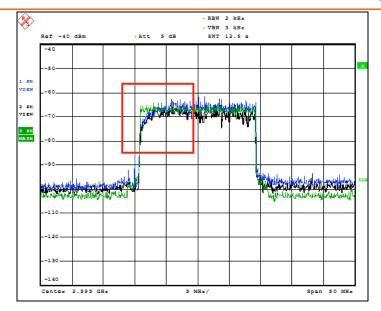

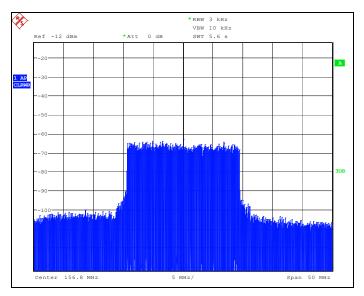

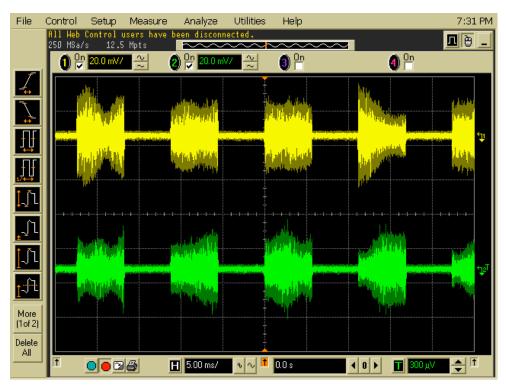

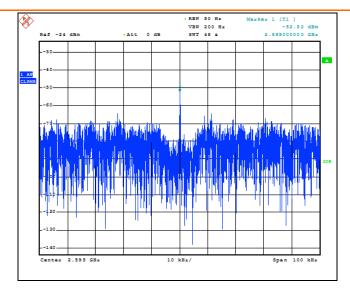

## Signal Analysis HW:

- Rohde & Schwarz FSQ Signal Analyzer up to 26.5GHz: It offers signal analysis at a demodulation bandwidth of up to 120 MHz with the dynamic range of a high-end spectrum analyzer. The equipment has application firmware for digital demodulation measurements for WLAN (IEEE 802.11 a/b/g/j and IEEE 802.11 turbo mode) and WiMAX (IEEE 802.16-2004, IEEE 802.16e-2005), and for noise figure and gain analysis.

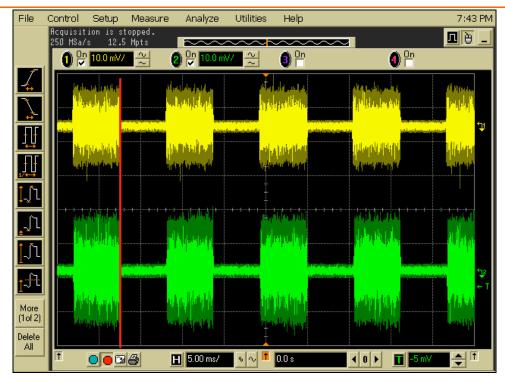

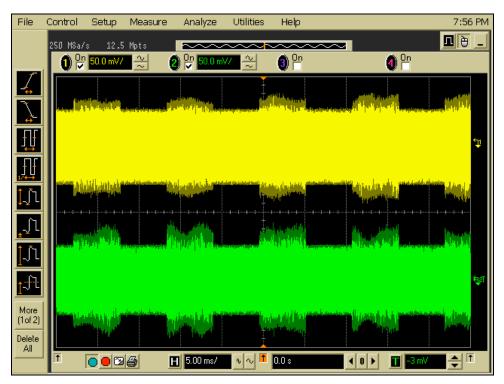

- <u>Agilent Infiniium Oscilloscope</u>: The Agilent 8000B Series Infiniium real-time ultra-high performance oscilloscope is required to meet the needs of engineers designing state of the art high-speed serial communication links and other ultra-high-speed electronic systems. The available scopes support 4 analog channels with up to 10GHz Bandwidth with up to 40

GSa/s sample rate. This instrument can be used as multiple-channel analog front-end to extract data for further processing with the Agilent 89600 VSA software (and thus enabling MIMO reception).

Figure 3-5: R&S FSQ26 Signal analyzer and Agilent Technologies DSO80804B Infiniium Oscilloscope (left) and 89600 VSA software GUI captures (right).

#### Signal Analysis SW:

- <u>Agilent 89600 Vector Signal Analysis (VSA)</u>: The software provides superior general-purpose and standards-specific signal evaluation and troubleshooting tools. These tools can be used to dig into the signal and gather the data needed to successfully troubleshoot PHY layer signal problems. GEDOMIS® disposes the full set of libraries through the educational license of VSA.

Real-world signals acquired by the 89600 software can be linked to the Agilent Advanced Design System (ADS) simulation environment (which can also load waveforms into the signal generators and thus close the loop) for further processing or mixed-domain and multiplatform verification.

#### Synthetic instrumentation:

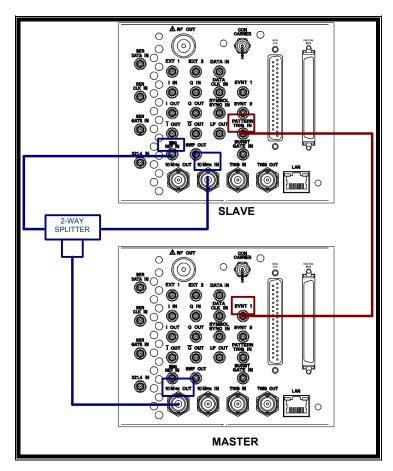

- Mercury Computer Systems (MCS) High Performance 4-channel RF Downconverter: The MCS Echotek Series RF 3000 Tuners is a reconfigurable multi-channel platform to downconvert general wireless standard signals from RF to IF. The equipment must be placed within the frame of a complete RF, data acquisition and signal processing platform and performs high dynamic range, wide bandwidth, excellent phase noise, single or multi-channel phase-coherent operation and ultra fast tuning speed. The basic 3000T tuner is comprised of two single-slot VME modules: the 3000RF receiver module and the 3000S synthesizer module (using Direct Digital Synthesizer (DDS) technology). This 2-board 6U VME set functions as an ultra high-performance 20 MHz to 3000 MHz RF-to-IF. The tuner provides both an intermediate frequency at 140 MHz (65MHz bandwidth) and a baseband output suitable for direct input into an external A/D converter. The 3000RF module has a dual RF input, which can be switched for systems that may have high and low antenna array inputs. Alternatively, one RF input can be utilized as a dedicated calibration port. For multi-channel applications, additional 3000RF modules can be integrated with the 3000S synthesizer

module to form a multi-channel fast-tuning radio solution. The system can run in a master/slave configuration, such that the system can be dynamically changed to run in either independently tunable or phase-coherent operation. This allows the system to be cabled up once and reconfigured on the fly via the control software that can be configured for a standard RS-232 or a serial peripheral interface (SPI) port, thereby allowing the unit to be controlled via the front panel in addition to the VME bus. GEDOMIS® features a [4RF+1synthesizer] module-configuration enclosed in a Vector Series 400 6U 21slot VME chassis allowing future expansions and integration of upconverters (for TX) or other 6U ADC/DAC or DSP/FPGA VME boards. The high-performance characteristics are enabling factors for applications such as MIMO wireless communication systems (commercial mobile phone base stations, wireless LAN networks) or diverse multiple-purpose software radio allowing cognitive radio, direction finding and beamforming.

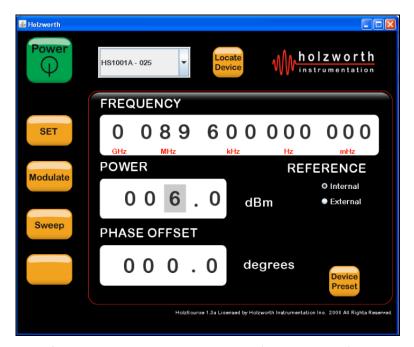

Figure 3-6: MCS Echotek Series 3000T downconverters (left) and Holzworth Instrumentation HS1001A synthesizer.

- Holzworth Microwave Source: The Holzworth HS1001C RF Synthesizer is an ultra low phase noise, single channel CW source. Capable of tuning frequencies from 8MHz to 1GHz in 0.001Hz step resolution, this "small form" versatile synthesizer can be controlled directly by the proprietary application software Labview or a preloaded lookup table which enables such functionality as rapid frequency hopping. The device can be either DC powered by using an external AC/DC power supply or by using a custom made dual USB cable (and thus enhancing its portability). The source can be used as (below IEEE L-band) RF synthesizer, or as baseband system clock or ADC sampling frequency generator: CTTC is currently working in many wireless demonstrators for some wireless standards/systems (WiFi, WiMAX, UWB, DVB, GPS/Galileo...) and for certain applications it is required both low jitter and low phase noise (e.g. high-density multi-carrier OFDM systems).

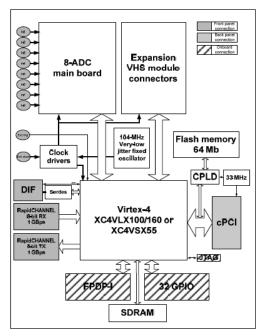

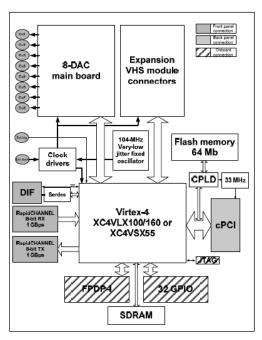

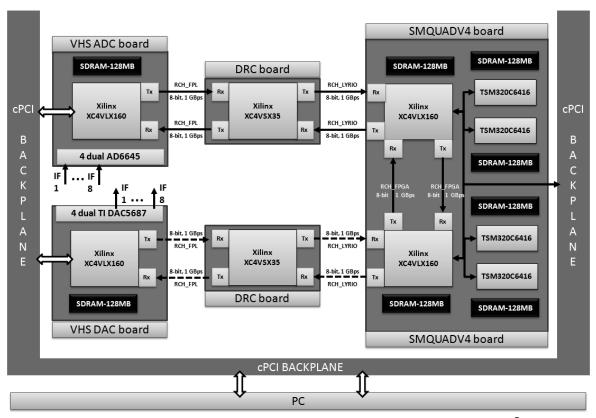

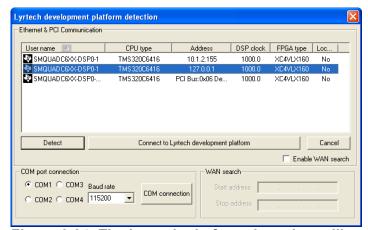

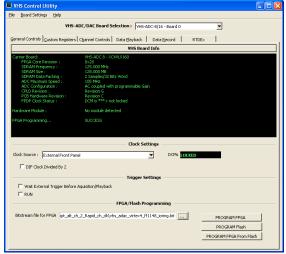

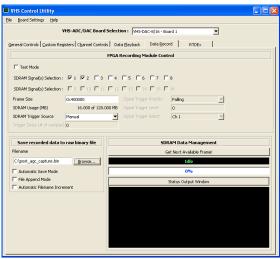

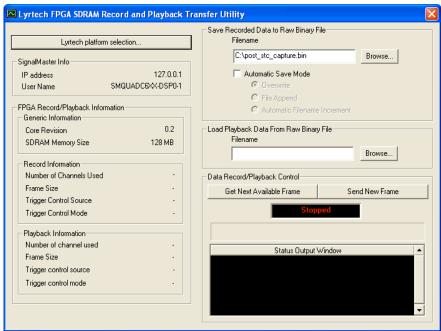

#### Lyrtech ADP, signal conversion and baseband processing platform:

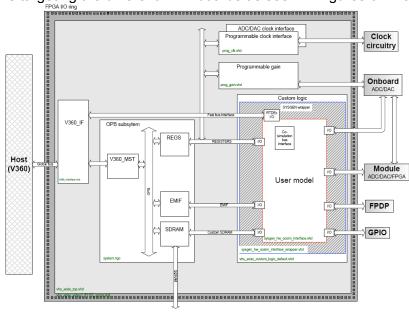

The Lyrtech's Advanced Development Platform (ADP) comprises a full set of signal conversion and baseband processing boards. Full specifications are given in Appendix 6.2. The VHS-DAC and VHS-ADC (Figure 3-7) signal conversion boards of the ADP are fitted respectively with 4 dual TI DAC5687 Digital to Analogue Converters (DAC) providing up to 8 transmitting channels and 4 dual AD6645 Analogue to Digital Converters (ADC) providing up to 8 receiving channels. These two boards allow the implementation of MIMO systems and other antenna array configurations used in radar or terrestrial-to-satellite communications. Each of the eight phase-coherent channels of the DAC and ADC boards shares a common clock source and includes a digitally controlled Variable Gain Amplifier (VGA). There is also an on-board 104 MHz crystal and external clock and trigger inputs in both boards. The DAC

and ADC boards include a single Xilinx Virtex-4 FPGA device (i.e., XC4VLX160), 128 MB of on-board SDRAM and they are connected to a cPCI chassis through a dedicated backplane connection. Finally, a proprietary full-duplex 1GBps bus (i.e., Rapid Channel) allows the VHS-ADC and VHS-DAC boards to connect with the main baseband processing board.

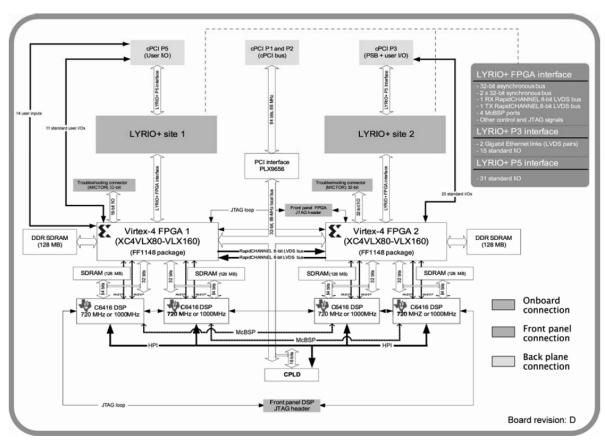

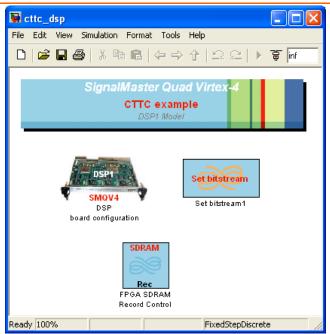

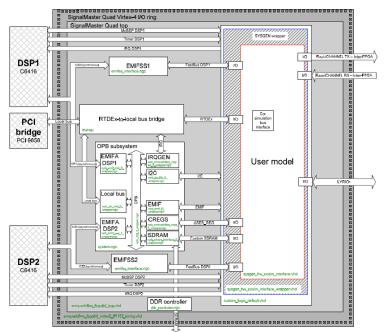

Figure 3-7: The block diagram of the VHS-ADC (left) and the VHS-DAC (right) boards.

In order to compare the challenges of wideband bit-intensive baseband operations, the ADP includes another baseband signal processing board, namely the Signal Master Quad (SMQUAD), able to address demanding data loads and DSP operations. As seen in Figure 3-8, this board includes two Xilinx Virtex-4 FPGA devices (i.e., XC4VLX160 in our case) and 4 fixed-point DSP processors from TI (i.e., TMS320C6416 running up to 1GHz in our case). The SMQUAD features 128 MB of SDRAM per FPGA and DSP processor. The inter-FPGA communication is accomplished via a full-duplex 1GBps bus and the FPGA-to-DSP communication is accomplished via a 32-bit wide bus. As in the case of the VHS-DAC and VHS-ADC boards the SMQUAD board is similarly connected to the chassis via the cPCI backplane. The SMQUAD features two additional daughter-boards (DRC), which are connected to the LYRIO+ sites. The DRC boards are connected to the LYRIO+ sites of the SMQUAD board and help the latter to establish full-duplex 1GBps connections with the VHS-ADC and VHS-DAC boards thanks to the on-board Rapid Channel connector. The FPDP and GPIO-32 I/O interfaces are not included. Each DRC boards is fitted with a Xilinx Virtex-4 FPGA device (i.e., XC4VSX35).

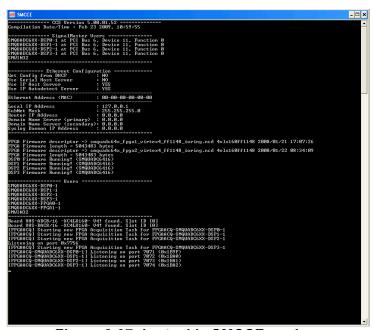

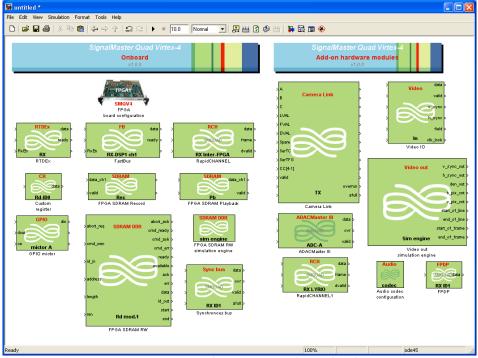

Finally, the chassis is fitted with a PC which runs Windows XP 32-bit (i.e., ADP software compatibility prerequisite). The PC is also connected to the cPCI backplane and runs the ADP software and drivers (ADP version 3.0 or 3.2²), including dedicated Graphical User Interfaces (GUIs) for controlling and interacting with each board that is connected to the cPCI chassis. Considering that all described boards fitted in the ADP are making use of the same the cPCI bus, the role of the PC is not limited to off-line control functions, but it is also thought to be used for various real-time operations such as waveform record and play-back, programming registers on the FPGA and use of the Real-Time Data Exchange (RTDEx) bus. Figure 3-9 shows a joint representation of the different boards comprising the GEDOMIS® testbed. Note that one of the DRC boards is currently not operating.

<sup>&</sup>lt;sup>2</sup> These versions of ADP are compatible with the Xilinx ISE 9.2, TI Code Composer 3.3 and Mathwork's Matlab 2007b versions.

Figure 3-8: The block diagram of the SMQUAD board.

Figure 3-9: Overview of the ADP solution available at GEDOMIS<sup>®</sup>.

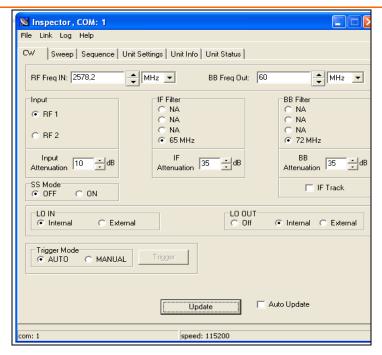

#### 3.2.3 Interfaces

The testbed does not offer a unified Graphical User Interface (GUI) to program, control and configure all of its hardware equipment and software. The different equipment, boards and software can be accessed with the means specified hereafter:

- Different web-based GUIs running on a browser of the ADP PC provide access to the:

- o Agilent E4438C VSGs,

- o Rohde & Schwarz FSQ Signal Analyzer and the

- o Agilent 8000B Series Infiniium Oscilloscope

- GUIs running at the ADP PC provide APIs for the:

- o MCS Echotek Series RF 3000 4-channel Downconverters

- o Holzworth HS1001C RF Synthesizer

- o Lyrtech VHS-ADC, VHS-DAC and SMQUAD boards of the ADP

- Instrument programmed exclusively in-situ (no GUI is available):

- o Applied Instruments NS-3 RF Noise sources

- A separate PC (embedded in the instrument) runs a software that provides access to the:

- Elektrobit C8 Channel Emulator

- A separate PC hosts the (the ADP PC does not meet the performance specs):

- o Agilent VSA

In theory, all the instruments (apart from one), APIs and software of GEDOMIS® that run on a PC can be accessed with different remote desktop sessions (i.e., considering that all PCs run different MS Windows versions). However, configuring and programming GEDOMIS® via remote access is practically impossible, since there has always to be present an engineer with previous exposure in use and manipulation of the instruments and software of GEDOMIS®. Many configuration options will have to be tested and validated in-situ together with the visiting researcher³. Also, the large number of User's Manuals and technical documentation makes it anyway practically impossible for someone to rapidly use the testbed without the help of qualified and experienced researchers who have already used GEDOMIS® before; apparently this can be facilitated only with in-situ use. It is also important to note that GEDOMIS® comprises a set of heterogeneous instrumentation and boards; it is thus vital for the instrument-safety to be always supervised in-situ any research and development activity. The same applies when the instruments or components of the testbed must be appropriately configured, connected or tuned to meet specific performance prerequisites or test-scenarios.

## GEDOMIS® can be used to develop:

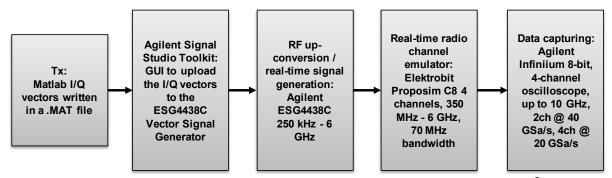

i. Offline testbeds which typically combine Matlab simulations at the two baseband ends transmitter and receiver- with instrumentation for the signal conversion (DACs, RF upconversion, channel emulator or antennas, RF downconversion, ADCs). Offline testbeds are typically used to evaluate quasi-static channels.

<sup>&</sup>lt;sup>3</sup> Setting up and configuring a real-time wireless communication testbed that focuses on PHY-layer algorithm prototyping implies the separate and joint testing of the diverse type of instruments and signal processing boards that form part of it. This allows researchers to achieve the desirable operating conditions and performance, according to the specifications of a certain standard. In order to accomplish this task, certain performance features of the equipment comprising the testbed need to be characterized and analysed, a fact that helps to identify performance bottlenecks at the beginning of the development. Real-time testbeds are commonly having performance stability issues due to the interdependencies among instruments in the signal processing path (baseband, ADC/DAC, RF conversion and channel); it is quite common for example that the power-level of the signal between cabled instruments or hardware boards may unexpectedly variate out of the defined range due to some sort of failure, mismatch or loose connection of cables, adapters, attenuators, on-board connectors or other components. This may significantly change the overall expected performance of the developed baseband transmitter and receiver, making also hard the traceability of the problem during system-debugging.

ii. Real-time testbeds which features an end-to-end full real-time operation able to validate realistic mobility and fast fading channel conditions.

A brief guide that describes the two modes of development and operation of GEDOMIS<sup>®</sup> is given hereafter:

## Configuring and using GEDOMIS® as an offline testbed:

- Build in Matlab the Tx baseband output I/Q vectors (stored in a .MAT)

- Use Agilent's Signal Studio Toolkit

- Upload I/Q vectors to the Agilent's ESG4438C Vector Signal Generators (VSGs)

- Use the two ESG4438C VSGs to produce real RF signals

- o The ESG4438C has a baseband BW of up to 40 MHz for this operation mode

- The ESG4438C embeds an arbitrary waveform generator and RF signal upconverter circuitry able to provide at real-time signals from 250 kHz to 6 GHz

- The VSGs can realize 2 independent Tx or a 2-antenna MIMO Tx

- Use the Elektrobit Proposim C8 channel emulator to apply a static channel

- The emulator supports up to 4 channels, 350 MHz 6 GHz, 70 MHz bandwidth.

- Load a standard channel from an existing library

- Build channels in Matlab and upload them to the emulator (up to 48 taps each)

- OPTION 1: Use the Agilent Infiniium 80000B 4-channel oscilloscope to capture data

- o Up to 10 GHz, sample rates: 2ch @ 40 GSa/s, 4ch @ 20 GSa/s

- Memory depth per channel: 1M (4ch), 2M (2 ch))

- The Oscilloscope offers 6.2 effective bits resolution to the captured data

- Optional step: Use Agilent's VSA to demodulate the signal

- The channel emulator is by-passed

- The signal has to be compliant with a standard supported by VSA

- VSA runs at a PC and takes samples from the Oscilloscope via Ethernet

- o Post-process the captured data in Matlab

- Develop the Rx in Matlab

- · OPTION 2 Achieve a better resolution in the captured data

- Use the RF donwcoverters (20MHz to 3GHz, Phase-Coherent 4 channel)

- Use the 8-channel ADC board (105MSPS, 14 bit) featuring an FPGA device

- Tune the RF down-converters to provide the IF frequency that satisfies the analogue bandwidth and sampling specifications of the ADC devices

- Apply an empirical back-off margin (e.g., 12 dBs) by modifying the gain of the on-board VGAs (i.e., using a GUI) to avoid the saturation of the ADCs

- Capture and retrieve the data at the FPGA device of the ADC board using a preconfigured FPGA application and a dedicated GUI

Figure 3-10: The offline PHY-layer realization flow using GEDOMIS<sup>®</sup>.

## Using GEDOMIS® to develop a real time testbed:

- Develop the Tx in Matlab and capture data that can be used for developing the Matlab model of the Rx following the procedure for offline realizations

- Manually translate the Matlab model of both Tx and Rx to HDL code

- Debug the HDL functional code using proprietary HDL simulation EDA tools

- Implement the RTL code to target the FPGA devices of GEDOMIS®

- o Integrate both Tx and Rx with the firmware of the boards

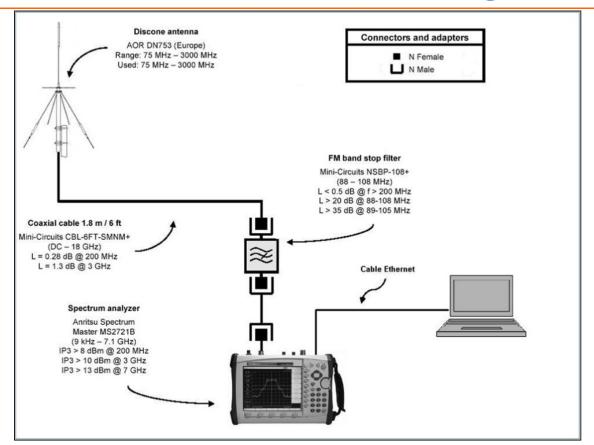

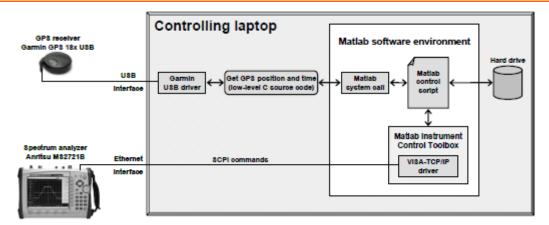

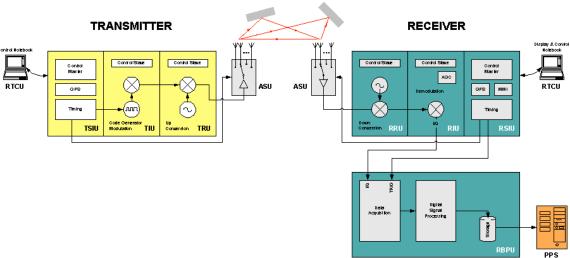

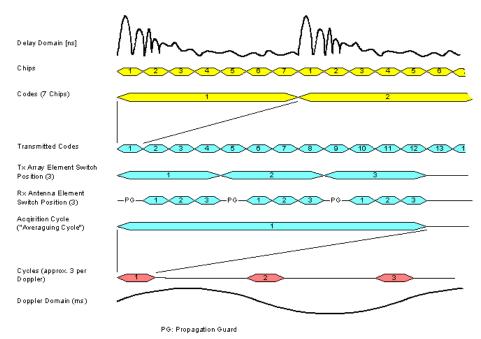

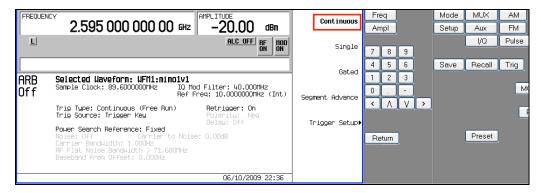

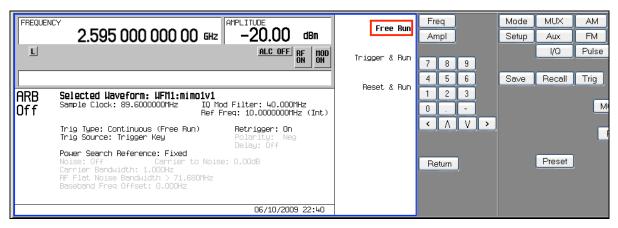

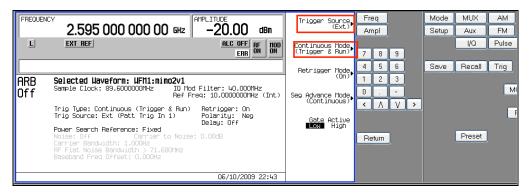

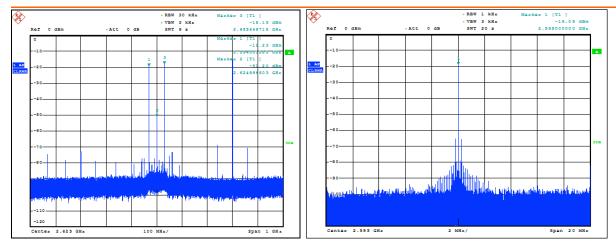

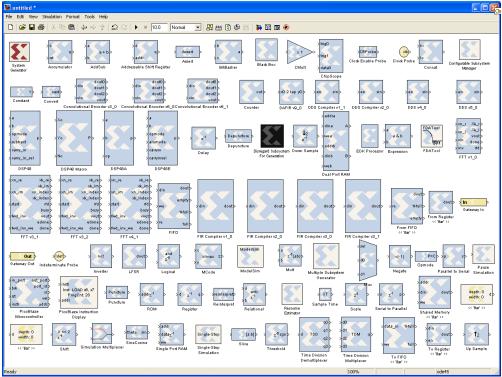

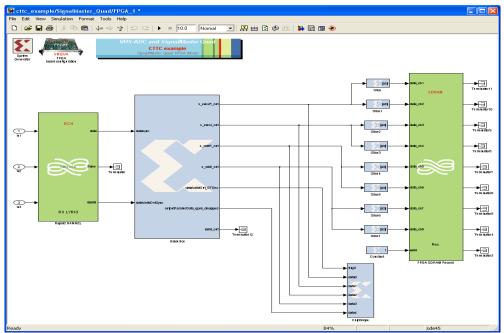

- o Configure for the DAC devices e.g., filters, interpolation factor, IF signal