# Low latency and high throughput dynamic network infrastructures for high performance datacentre interconnects

Small or medium-scale focused research project (STREP)

Co-funded by the European Commission within the Seventh Framework Programme

Project no. 318606

Strategic objective: Future Networks (ICT-2011.1.1)

Start date of project: November 1st, 2012 (36 months duration)

#### **Deliverable D3.3**

# Evaluation of OPS, OCS and TOR switches' prototypes and programmable optical NICs including electronics control and interfaces

**Due date:** 28/02/2015 **Submission date:** 08/04/2015

Deliverable leader: TUE

Author list: Wang Miao (TUE), Nicola Calabretta (TUE), Harm Dorren (TUE), Yi Shu (UNIVBRIS),

Yan Yan (UNIVBRIS), Bingli Guo (UNIVBRIS), Chris Jackson (UNIVBRIS), Georgios Zervas (UNIVBRIS), Shuping Peng (UNIVBRIS), Reza Nejabati (UNIVBRIS), Dimitra Simeonidou (UNIVBRIS), Salvatore Spadaro (UPC), Fernando Agraz (UPC), Jose Carlos

Sancho (BSC), Hugo Meyer (BSC), Montse Farreras (BSC)

#### **Dissemination Level**

| $\boxtimes$ | PU: | Public                                                                                |

|-------------|-----|---------------------------------------------------------------------------------------|

|             | PP: | Restricted to other programme participants (including the Commission Services)        |

|             | RE: | Restricted to a group specified by the consortium (including the Commission Services) |

|             | CO: | Confidential, only for members of the consortium (including the Commission Services)  |

#### **Abstract**

This document presents the implementation and experimental evaluation of the hybrid data plane prototypes developed in LIGHTNESS.

LIGHTNESS data plane integrates innovative optical switching technologies including programmable optical Network Interface Card (NIC), optical Top of Rack (ToR) switch, optical packet switching (OPS) and optical circuit switching (OCS)to provide scalable, high bandwidth and low latency optical interconnectivity within the data centre network (DCN) infrastructure. The architecture-on-demand (AoD) switch nodes bound all the switching elements and enable the flexible configuration of the intra- and inter-cluster communication for the flat DCN.

The results of the prototypes implementation for OPS, OCS and TOR nodes as well as programmable optical NICs are presented in this deliverable. It also provides a final report about the overall data plane architecture for LIGHTNESS. Experimental assessments of the prototypes, interfaces between switching nodes and interfaces with control plane are reported in detail. The benefits of synthetic hybrid data plane have been analyzed and evaluated with scientific applications. An all-optical solution for intra- DCN to inter-DCN interface is also introduced. As a comprehensive summary of the achievements in WP3, the results descript in this document will be employed as guideline for the experimental evaluation of the DCN integration in the WP5.

# **Table of Contents**

| Та | ble of | Contents                                                       | 3  |

|----|--------|----------------------------------------------------------------|----|

| 0. | Execu  | utive Summary                                                  | 8  |

| 1. | Intro  | duction                                                        | 9  |

|    | 1.1.   | Motivation and scope                                           | 9  |

|    | 1.2.   | Structure of the document                                      | 9  |

| 2. | LIGHT  | TNESS data plane implementation and evaluation                 | 11 |

|    | 2.1.   | Implementation of the hybrid OCS/OPS data plane testbed        | 11 |

|    | 2.2.   | Implementation of the interface to control plane               | 15 |

| 3. | Optic  | al ToR and programmable NIC evaluation                         | 17 |

|    | 3.1.   | Implementation                                                 | 17 |

|    |        | 3.1.1. Optical ToR implementation                              | 17 |

|    |        | 3.1.2. Programmable NIC Implementation                         | 18 |

|    | 3.2.   | System evaluation                                              | 22 |

|    |        | 3.2.1. WSS-based optical ToR evaluation                        | 22 |

|    |        | 3.2.2. FPGA-based programmable NIC evaluation                  | 23 |

|    | 3.3.   | Interface with control plane                                   | 30 |

|    |        | 3.3.1. Interface with control plane for optical ToR            | 30 |

|    |        | 3.3.2. Interface with control plane for hybrid NIC             | 30 |

| 4. | OCS s  | witch evaluation                                               | 31 |

|    | 4.1.   | Implementation and System Evaluation                           | 31 |

|    | 4.2.   | Interface with control plane                                   | 35 |

| 5. | OPS s  | witch evaluation                                               | 36 |

|    | 5.1.   | Implementation                                                 | 36 |

|    | 5.2.   | System evaluation                                              | 39 |

|    |        | 5.2.1. Performance assessment with burst-mode receiver         | 39 |

|    |        | 5.2.2. Performance evaluation in a 1.3 μm system               | 42 |

|    |        | 5.2.3. Evaluation of OPS-based virtual network reconfiguration | 43 |

|    | 5.3.   | Interface with control plane                                   | 45 |

| <ul> <li>6.1. Synthetic hybrid DCN configuration <ul> <li>6.1.1. Implementation of hybrid DCN communication</li> </ul> </li> <li>6.2. Multi-tenant synthetic hybrid DCN composition <ul> <li>6.2.1. Scenario description</li> <li>6.2.2. Synthetic DCN composition algorithm</li> <li>6.2.3. Algorithm evaluation</li> </ul> </li> <li>6.3. Performance evaluation on scientific applications <ul> <li>6.3.1. Simulator modules</li> <li>6.3.2. Simulation scenario and results</li> </ul> </li> <li>7. Design, implementation of intra- DCN to inter-DCN interface</li> <li>8. Conclusions</li> <li>9. References</li> </ul> |    |         |          |                                                 | Lightness | 5 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|----------|-------------------------------------------------|-----------|---|

| <ul> <li>6.1.1. Implementation of hybrid DCN communication</li> <li>6.2. Multi-tenant synthetic hybrid DCN composition</li> <li>6.2.1. Scenario description</li> <li>6.2.2. Synthetic DCN composition algorithm</li> <li>6.2.3. Algorithm evaluation</li> <li>6.3. Performance evaluation on scientific applications</li> <li>6.3.1. Simulator modules</li> <li>6.3.2. Simulation scenario and results</li> <li>7. Design, implementation of intra- DCN to inter-DCN interface</li> <li>8. Conclusions</li> <li>9. References</li> </ul>                                                                                      | 6. | Synth   | etic hyl | brid DCN architecture                           | 47        |   |

| <ul> <li>6.2. Multi-tenant synthetic hybrid DCN composition</li> <li>6.2.1. Scenario description</li> <li>6.2.2. Synthetic DCN composition algorithm</li> <li>6.2.3. Algorithm evaluation</li> <li>6.3. Performance evaluation on scientific applications</li> <li>6.3.1. Simulator modules</li> <li>6.3.2. Simulation scenario and results</li> <li>7. Design, implementation of intra- DCN to inter-DCN interface</li> <li>8. Conclusions</li> <li>9. References</li> </ul>                                                                                                                                                 |    | 6.1.    | Synthe   | etic hybrid DCN configuration                   | 47        |   |

| <ul> <li>6.2.1. Scenario description</li> <li>6.2.2. Synthetic DCN composition algorithm</li> <li>6.2.3. Algorithm evaluation</li> <li>6.3. Performance evaluation on scientific applications</li> <li>6.3.1. Simulator modules</li> <li>6.3.2. Simulation scenario and results</li> <li>7. Design, implementation of intra- DCN to inter-DCN interface</li> <li>8. Conclusions</li> <li>9. References</li> </ul>                                                                                                                                                                                                             |    |         | 6.1.1.   | Implementation of hybrid DCN communication      | 49        |   |

| <ul> <li>6.2.2. Synthetic DCN composition algorithm</li> <li>6.2.3. Algorithm evaluation</li> <li>6.3. Performance evaluation on scientific applications</li> <li>6.3.1. Simulator modules</li> <li>6.3.2. Simulation scenario and results</li> <li>7. Design, implementation of intra- DCN to inter-DCN interface</li> <li>8. Conclusions</li> <li>9. References</li> </ul>                                                                                                                                                                                                                                                  |    | 6.2.    | Multi-t  | tenant synthetic hybrid DCN composition         | 51        |   |

| <ul> <li>6.2.3. Algorithm evaluation</li> <li>6.3. Performance evaluation on scientific applications <ul> <li>6.3.1. Simulator modules</li> <li>6.3.2. Simulation scenario and results</li> </ul> </li> <li>7. Design, implementation of intra- DCN to inter-DCN interface</li> <li>8. Conclusions</li> <li>9. References</li> </ul>                                                                                                                                                                                                                                                                                          |    |         | 6.2.1.   | Scenario description                            | 51        |   |

| <ul> <li>6.3. Performance evaluation on scientific applications <ul> <li>6.3.1. Simulator modules</li> <li>6.3.2. Simulation scenario and results</li> </ul> </li> <li>7. Design, implementation of intra- DCN to inter-DCN interface</li> <li>8. Conclusions</li> <li>9. References</li> </ul>                                                                                                                                                                                                                                                                                                                               |    |         | 6.2.2.   | Synthetic DCN composition algorithm             | 53        |   |

| <ul> <li>6.3.1. Simulator modules</li> <li>6.3.2. Simulation scenario and results</li> <li>7. Design, implementation of intra- DCN to inter-DCN interface</li> <li>8. Conclusions</li> <li>9. References</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                           |    |         | 6.2.3.   | Algorithm evaluation                            | 54        |   |

| <ul> <li>6.3.2. Simulation scenario and results</li> <li>7. Design, implementation of intra- DCN to inter-DCN interface</li> <li>8. Conclusions</li> <li>9. References</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 6.3.    | Perfor   | mance evaluation on scientific applications     | 57        |   |

| <ul><li>7. Design, implementation of intra- DCN to inter-DCN interface</li><li>8. Conclusions</li><li>9. References</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |         | 6.3.1.   | Simulator modules                               | 59        |   |

| 8. Conclusions 9. References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |         | 6.3.2.   | Simulation scenario and results                 | 64        |   |

| 9. References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7. | Desig   | n, imple | ementation of intra- DCN to inter-DCN interface | 69        |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8. | Concl   | lusions  |                                                 | 72        |   |

| 10. Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9. | Refer   | ences    |                                                 | 73        |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 | . Acror | nyms     |                                                 | 75        |   |

# **Figure Summary**

| Figure 2.1: LIGHTNESS data plane architecture with (a) FPGA-based electrical ToR and (b) hybrid NIC and \   | WSS-    |

|-------------------------------------------------------------------------------------------------------------|---------|

| based optical ToR                                                                                           |         |

| Figure 2.2: LIGHTNESS intra-cluster DCN architecture                                                        | 13      |

| Figure 2.3: LIGHTNESS inter-cluster DCN architecture                                                        | 14      |

| Figure 2.4: Implementation of the hybrid OCS/OPS data plane test bed                                        | 15      |

| Figure 2.5: Interface between control plane and data plane                                                  | 16      |

| Figure 3.1: WSS-based Optical ToR implementation                                                            | 18      |

| Figure 3.2: FPGA-based NIC Block Diagram                                                                    | 18      |

| Figure 3.3: FPGA-based controller agent interface block diagram                                             | 19      |

| Figure 3.4: NIC LUT address MAP in the FPGA                                                                 |         |

| Figure 3.5: FPGA-based PCIe and DMA engine block diagram                                                    | 20      |

| Figure 3.6: FPGA-based traffic classification block diagram                                                 | 21      |

| Figure 3.7: Packet size switchover when receives the request                                                | 22      |

| Figure 3.8: HiTech Global Xilinx Virtex 6 PCIE board                                                        |         |

| Figure 3.9: PCIe/DMA-only test setup and FPGA-based implementation                                          |         |

| Figure 3.10: DMA engine driver script                                                                       |         |

| Figure 3.11: Basic NIC, PCIe/DMA with MC and FIFO setup and FPGA-based implementation                       |         |

| Figure 3.12: Basic NIC throughput by RAM block                                                              |         |

| Figure 3.13: Basic NIC latency result                                                                       | 26      |

| Figure 3.14: FPGA-based programmable NIC experiment setup                                                   | 27      |

| Figure 3.15: FPGA-based programmable NIC maximum throughput measurement result                              |         |

| Figure 3.16: FPGA-based programmable NIC maximum throughput measurement result (1500B)                      |         |

| Figure 3.17: FPGA-based programmable NIC maximum throughput measurement result (1500B)                      | 28      |

| Figure 3.18: Programmable parameters test results                                                           |         |

| Figure 3.19: WSS-based Optical ToR's interface with control plane                                           |         |

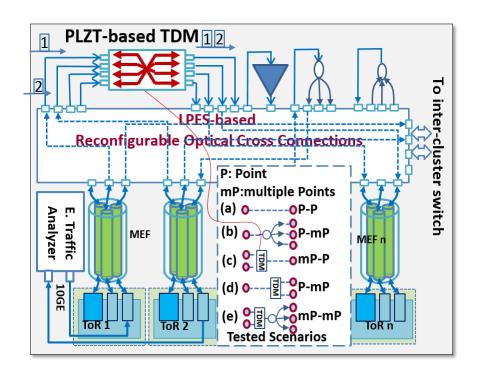

| Figure 4.1: Experimental Setup of intra-cluster OCS network                                                 |         |

| Figure 4.2: Experimental setup of the FPGA-based ToR                                                        |         |

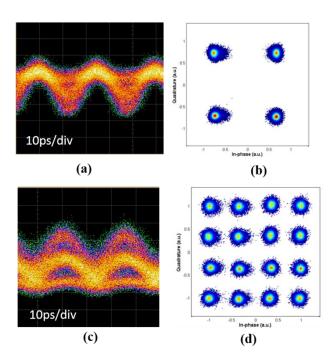

| Figure 4.3: Eye diagrams of the generated 40Gbaud QPSK signal (a) and 40 Gbaud 16QAM signal (c). The        |         |

| corresponding recovered constellations are shown in (b) and (d)                                             | 33      |

| Figure 4.4: Experimental results of intra-cluster network: (a) Ethernet-based OCS network; (b) TDM network  | ork.    |

|                                                                                                             | 34      |

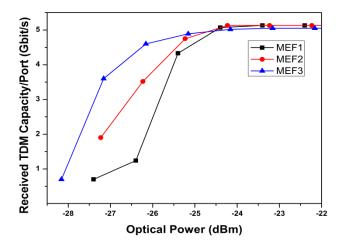

| Figure 4.5: Received TDM capacity for different received optical powers after broadcasting for scenario (e  | :) . 34 |

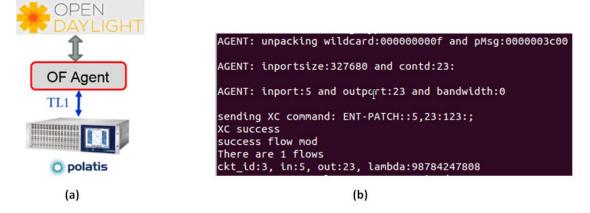

| Figure 4.6: Port switch based OCS switch's interface with control plane: (a) system architecture (b) OF age | nt      |

| capture                                                                                                     | 35      |

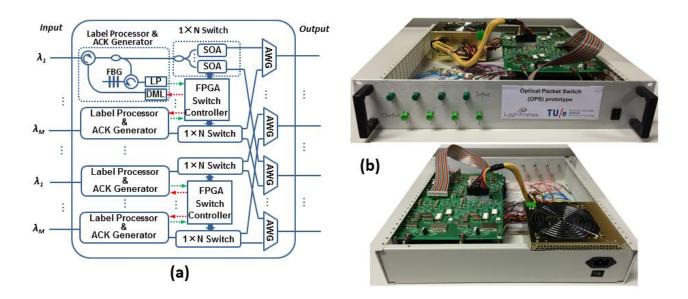

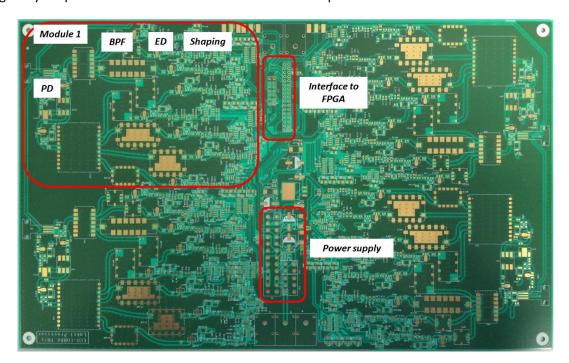

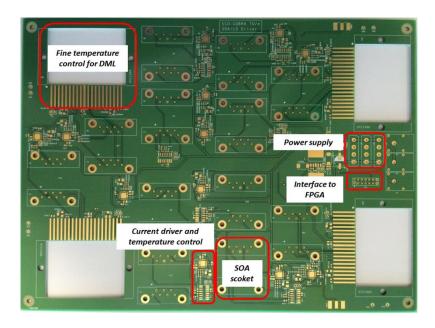

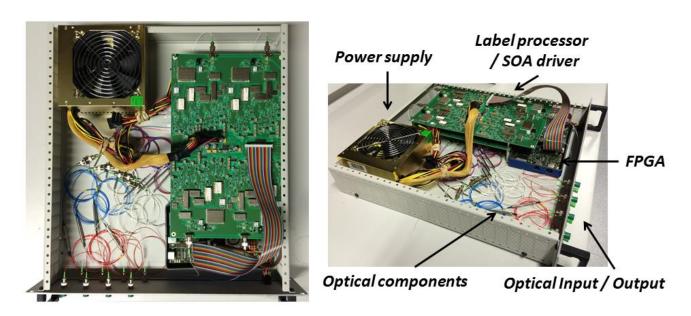

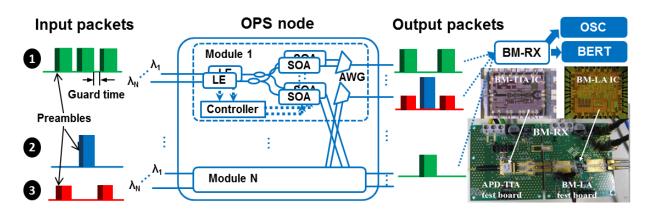

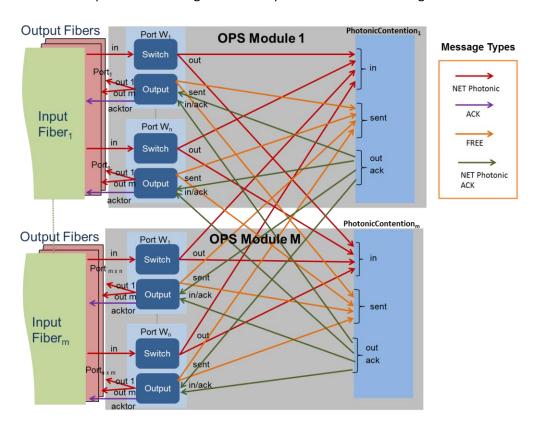

| Figure 5.1: (a) Modular OPS architecture with distributed control. (b) OPS prototype                        | 36      |

| Figure 5.2: PCB board of the label processor                                                                |         |

| Figure 5.3: PCB board of the SOA driver                                                                     |         |

| Figure 5.4: Detailed implementation schematic for OPS prototype                                             | 38      |

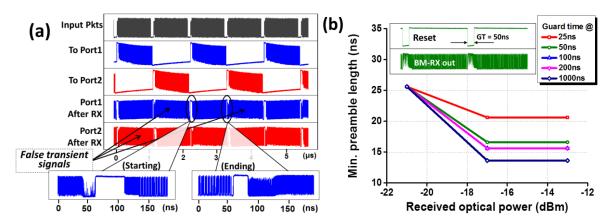

| Figure 5.5: Experimental set-up to evaluate the OPS system with burst-mode receiver                         | 39      |

| Figure 5.6: (a) waveforms detected by two separate BM-RXs; (b) minimum preamble length vs. input pow        | er at   |

| different guard-time                                                                                        | 40      |

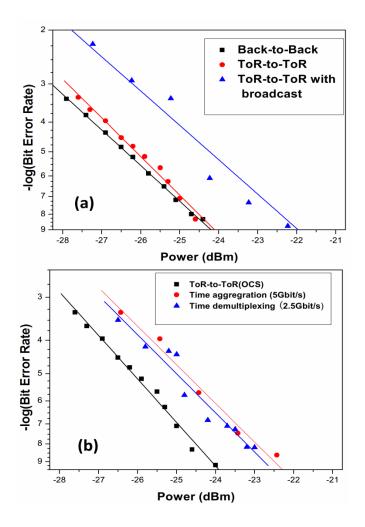

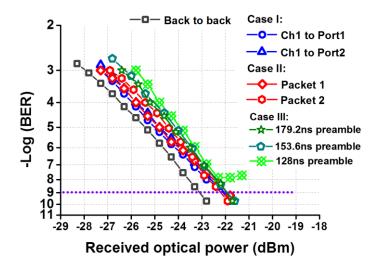

| Figure 5.7: BER curves for B2b and 3 cases                                                                  | 41      |

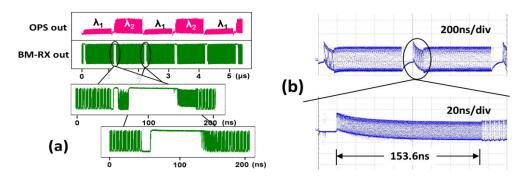

| Figure 5.8: waveforms of asynchronous packets equalized by the BM-RX; (b) waveform of BM-CDR output         |         |

| Figure 5.9: Architecture of the 1.3 μm optical packet switch                                                |         |

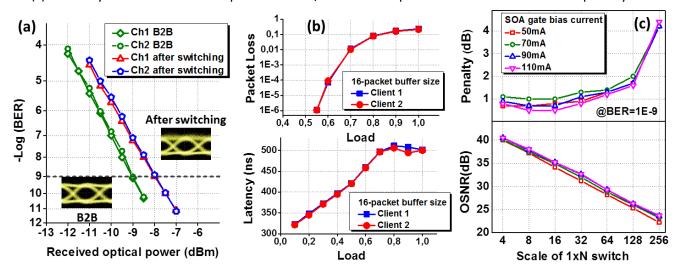

| Figure 5.10: (a) BER curves and eye diagrams; (b) packet loss and latency; (c) penalty and OSNR for scaling |         |

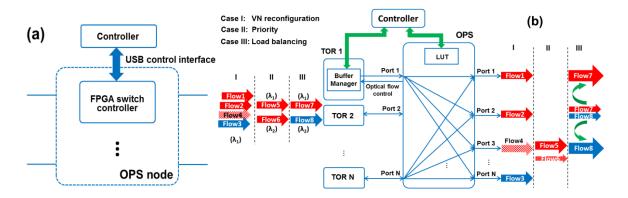

| Figure 5.11: (a) Schematic of the control interface; (b) experimental set-up for the reconfigurable VN      | 43      |

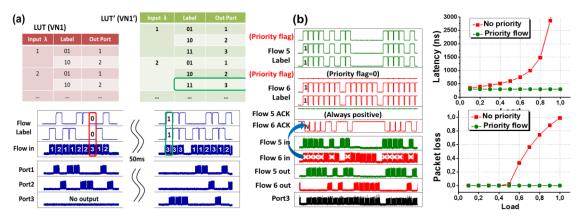

| Figure 5.12: (a) VN1 reconfiguration; (b) Time traces of Flow5 & Flow6 and packet loss & latency            | 44      |

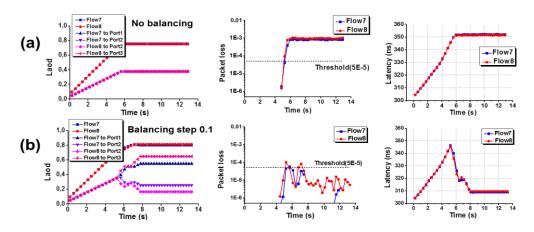

| Figure 5.13: Load, packet loss and latency changes without adjusting (a) and with load balancing with step | of c |

|------------------------------------------------------------------------------------------------------------|------|

| 0.1 (b)                                                                                                    | 45   |

| Figure 5.14: (a) OF-Agent architecture (b) OF-Agent implementation scheme [17]                             | 46   |

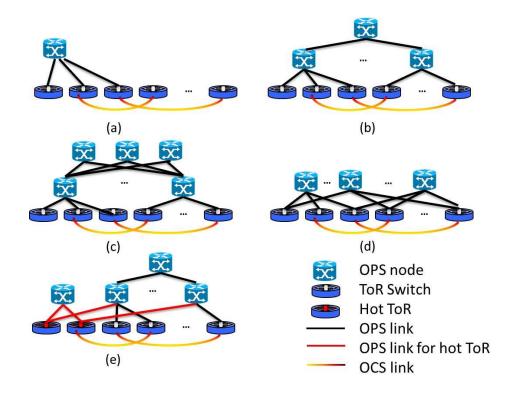

| Figure 6.1: Different network topologies supported by LIGHTNESS DCN approach                               | 48   |

| Figure 6.2: DCN reconfiguration with traffic load management strategy                                      | 49   |

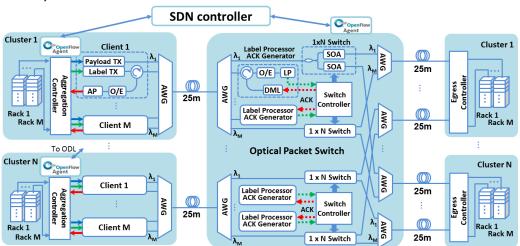

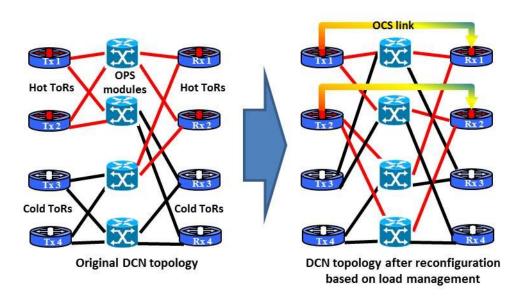

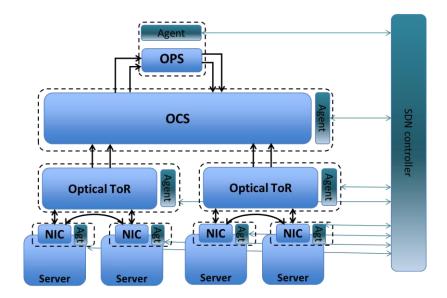

| Figure 6.3: SDN enabled Hybrid OPS/OCS DCN Architecture                                                    | 50   |

| Figure 6.4: Port switch based OCS switch's interface with control plane                                    | 51   |

| Figure 6.5: Multi-tenant synthetic DCN scenario.                                                           | 52   |

| Figure 6.6: Example of synthetic DCN composition.                                                          | 53   |

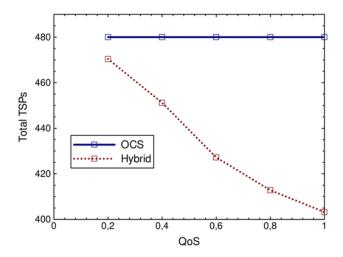

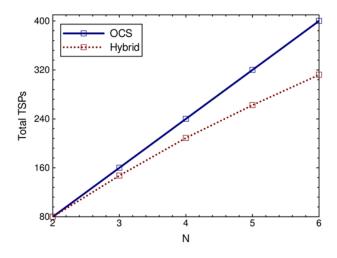

| Figure 6.7: TSPs as a function of the number of requests per tenant                                        | 55   |

| Figure 6.8: TSPs as a function of the QoS per virtual link                                                 | 56   |

| Figure 6.9: TSPs as a function of the QoS per virtual link                                                 | 56   |

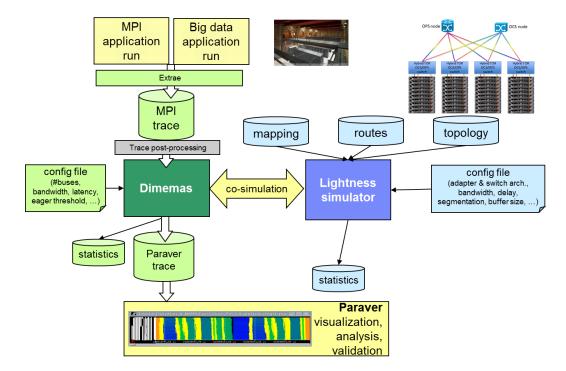

| Figure 6.10: Simulation framework                                                                          |      |

| Figure 6.11: Architecture on Demand overview                                                               | 59   |

| Figure 6.12: SDN controller design in the LIGHTNESS simulator                                              | 60   |

| Figure 6.13: Hybrid NIC design in the LIGHTNESS simulator                                                  |      |

| Figure 6.14: OPS design in the LIGHTNESS simulator                                                         |      |

| Figure 6.15: Required connections in the AoD in order to connect the OPS                                   | 64   |

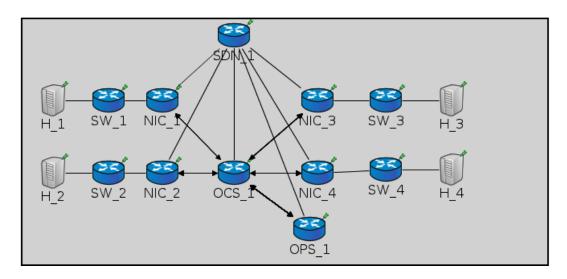

| Figure 6.16: Network representation in the Omnest simulator. One host per NIC is being used as well as o   | ne   |

| OPS, one OCS and an SDN controller                                                                         | 66   |

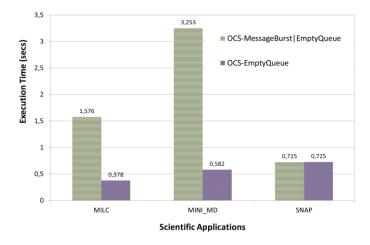

| Figure 6.17: Comparison of two different disconnection mechanisms when using the OCS                       | 66   |

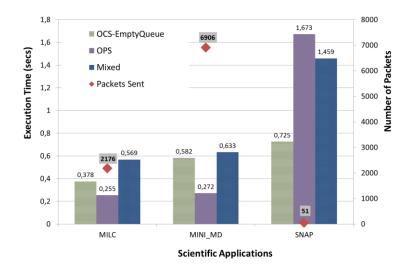

| Figure 6.18: Comparison of performance when applications use the OCS, the OPS and a combination of the     | ıem  |

|                                                                                                            | 67   |

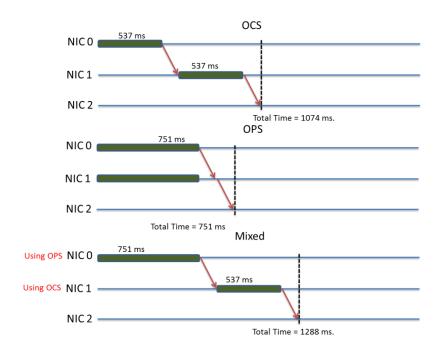

| Figure 6.19: Analysis of delays that are added because of reconnections                                    | 68   |

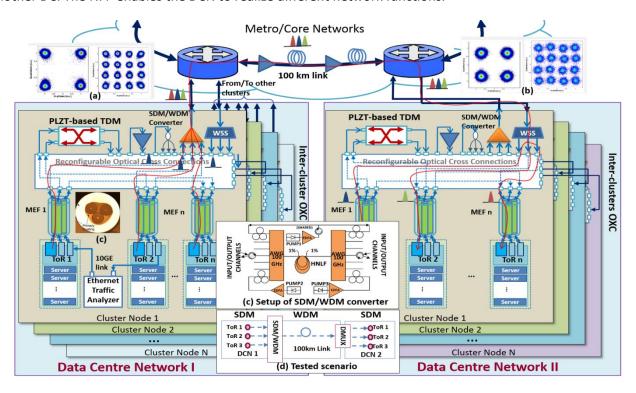

| Figure 7.1: Proposed solution for intra-DCN communication (SDM+TDM) and inter-DCN communication            |      |

| (SDM+WDM)                                                                                                  | 69   |

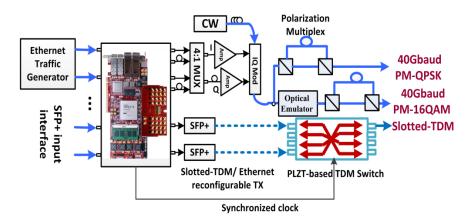

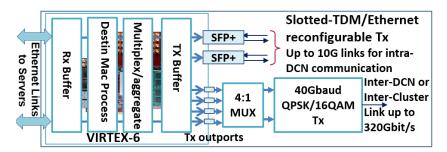

| Figure 7.2: FPGA-based ToR providing slotted-TDM/Ethernet signals for intra-DCN and BVT for inter-DCN.     | 70   |

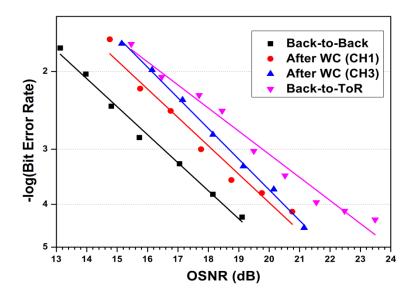

| Figure 7.3: OSNR vs. BER for 40Gbaud PM-QPSK signals for inter-DCN communication                           | 71   |

# **Table Summary**

| Table 2.1: Summary of the interface between control plane and devices | 16 |

|-----------------------------------------------------------------------|----|

| Table 3.1: Characteristics of the WSS-based ToR                       |    |

| Table 6.1: Simulation parameters                                      | 65 |

# **O.Executive Summary**

The exponential growth of the Internet traffic is boosting the requirements of DCN for higher capacity, lower latency and more flexible interconnectivities. To overcome the hardware limitations of multi-tier electrical DCNs, optical switching technologies exploiting space, time, and wavelength multiplexing have been investigated in several projects for effectively accommodating data centre (DC) applications [1]. A novel flat and scalable data plane architecture which supports high-bandwidth and agile network connectivity has been defined in LIGHTNESS. In cooperation with a unified network control plane, the data plane elements can be dynamically configured to adapt to the on-demand requirements.

The objectives of WP3 are the design and implementation of the switching technologies involved in the data plane. The high-end NIC implemented with Field-Programmable Gate Array (FPGA)-based platform aggregates the traffic from the dedicated server and transmits the data to the pure optical ToR for intra- and inter-rack communication. The AoD-based OCS backplane and the OPS interconnect all the ToRs and specified to handle long-lived and short-lived inter-rack traffic, respectively. This deliverable mainly focuses on the evaluations of the prototypes including optical ToR, OCS, OPS and programmable NIC. Based on the design scheme reported in D3.1 [2] and the preliminary evaluation results descript in D3.2 [3], the prototypes of the switching nodes are implemented and experimentally assessed.

As the final deliverable of the WP3, not only the system evaluation of each switching element, but also the evaluation of the overall data plane architecture is reported. The performances of the programmable OCS/OPS DCN architecture allowing for dynamic inter- and intra- cluster network topology and technology synthesis are analysed. The performance of the synthetic hybrid data plane is analysed and evaluated with scientific applications. The results of the data plane integration in this document will serve as a complementary content for experimental validation in WP5.

To enable the dynamic control and operation from the Software Defined Networking (SDN)-based control plane, the hardware and software control interfaces have been developed for the different switching nodes (ToR, AoD and OPS). As OpenFlow (OF) has been chosen as the communication protocol for the southbound interface, dedicated OF-agents are implemented to facilitate the messages delivering between the SDN controller and switching elements. The implementation schemes of the OF-agents are explained in detail and the performances of the control interfaces are experimentally evaluated. The investigation results will be further utilized and finalized in WP5 during the integration of the data plane and the control plane developed in WP4.

# 1.Introduction

## 1.1. Motivation and scope

The bandwidth of the data centre networks (DCNs) scales with roughly a factor of 1000 every 10 years [4]. Nowadays the DC traffic is handled by the multi-tier electronic switches. Limited by the scaling issues including latency and bandwidth bottleneck of the electronic switches, the high capacity and flexibility required by next generation DCN applications justifies the investigation of high-end optical switching technologies. Besides the switching nodes, a more efficient topology is also required to improve the performance in terms of bandwidth and latency. To this end, the LIGHTNESS proposes a flat data plane architecture integrating both OCS and the OPS switching technologies to deal with the inconsistent application requirements. Programmable NIC is directly plugged into each server and is given the intelligence to diverge the traffic to OCS/OPS according to the specific requirements. Benefiting from this, the ToR could be implemented optically eliminating the extra processing efforts. Control interfaces are developed for the switching elements which enables the control plane to flexibly and dynamically provision of the data plane resources.

The switching nodes have been properly designed and experimentally implemented [3,4]. The final implementation and assessments of the prototypes are presented in this document. This includes the optoelectronic interfaces and the controlling interfaces to SDN controller which have been tested and evaluated in detail. To enable the overall operation of the data plane, different switching technologies are integrated and the synthesized hybrid OCS/OPS data plane has been assessed. The switching performance of the individual sub-systems and as a whole system has been examined which makes this deliverable a summary of the results achieved in WP3 along its whole duration. The prototypes will be employed in the data plane integration and data plane/control plane integration defined in WP5.

#### 1.2. Structure of the document

This document is structured as follows.

Chapter 2 provides the detailed implementation schemes of the LIGHTNESS data plane including both intracluster and inter-cluster scenarios. Two different design schemes for ToR switching node are investigated. The OCS/OPS test bed used for evaluating the overall data plane performance is introduced. A summary of the interfaces exposed towards the control plane is also provided.

Chapter 3 describes the implementations of the novel optical ToR and the programmable NIC. The advantages over the traditional solutions are also presented. The characteristics of the optical ToR and the capabilities of the optical NIC are reported. It also presents the evaluation results of the NIC in terms of throughput and latency and the interfaces with control plane for both nodes.

Chapter 4 presents the implementation and system evaluation of the OCS node. In particular, the intra-cluster network is investigated and the opto-electronic interface used to provide bandwidth adjustable transmission is explained.

Chapter 5 focuses on the modular OPS node and reports the related implementation and assessment results. The preparation of the compact printed circuit board (PCB) designs for the prototype is described and the performance evaluation of the burst mode operation is given. Capabilities of network reconfiguration benefited from SDN have been evaluated. The interface with the control plane is also discussed at the end of this chapter.

Chapter 6 presents the benefits of synthetic hybrid DCN architectures. It introduces the performance evaluation of programmable synthetic hybrid OCS/OPS DCN. The case of multi-tenant scenario where each tenant requests several virtual slices according to their needs is investigated. The benefits of the hybrid DCN are analyzed considering dynamic on-demand DCN configuration. An experimental implementation of the synthetic data plane is also evaluated. Finally, the evaluation of the performance with real world scientific applications for the LIGHTNESS solution is reported.

Chapter 7 provides an all-optical multi-dimensional and programmable solution for inter-DCN communications. High speed interface for inter-DCN communication is described and the experimental evaluation results are given.

# 2.LIGHTNESS data plane implementation and evaluation

# 2.1. Implementation of the hybrid OCS/OPS data plane testbed

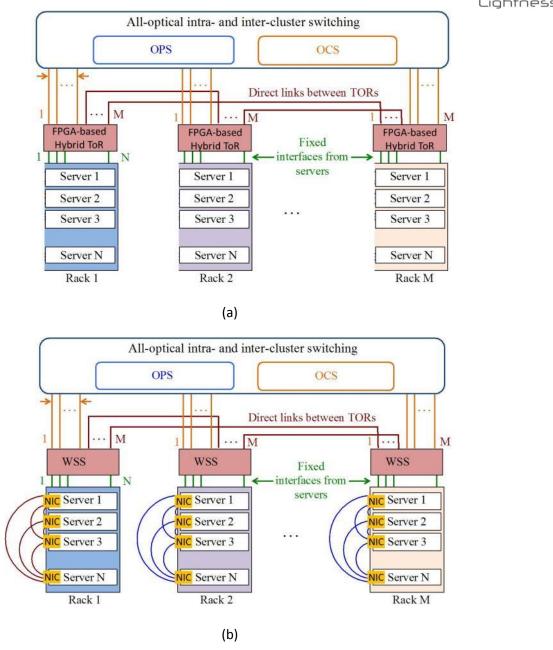

As presented in D3.1 [2], the intra-DC network architecture is displayed in Figure 2.1. Two different schemes for ToR switch design are investigated.

In Figure 2.1(a), a hybrid ToR switch is designed and implemented based on high-speed FPGA platforms. It can interface the servers to the hybrid OPS/OCS interconnects network by efficient aggregation and mapping of the traffic in long-lived data flows (to be transported by OCS network) and in short-lived packet flows (to be transported by OPS network). It includes several interfaces:

- The interface with control plane communicates with the controller by 10Gbps link, and makes the FPGA-based hybrid ToR switch controllable from control plane;

- The interface with server is 10Gbps enhanced small form-factor pluggable (SFP+), through that the hybrid ToR switch receives/sends Ethernet frames from/to the server

- To realize OPS transmission, a label interface is employed to send/receive labels and ACK signals to/from Switch Module FPGA

- The inter-rack communication is through 10x10Gbps Dense Wavelength Division Multiplexing (DWDM) C Form-factor Pluggable (CFP) links.

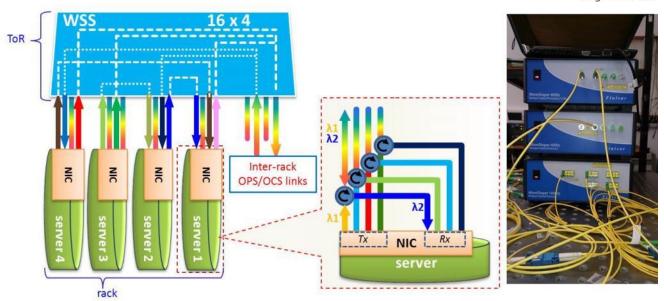

In Figure 2.1(b), the Hybrid NIC is deployed directly on the server in place of the commercial NIC. Thus, the hybrid OPS/OCS switchover functions can be implemented in the Hybrid NIC on the server. The ToR switch does not need to employ any electronic platform but contains only pure optic components such as wavelength selective switches (WSS) or spectrum selective switches (SSS). Furthermore, the servers in the rack can directly communicate with each other. More discussion about optical ToR and hybrid NIC can be found in Chapter 3.

**Figure 2.1:** LIGHTNESS data plane architecture with (a) FPGA-based electrical ToR and (b) hybrid NIC and WSS-based optical ToR

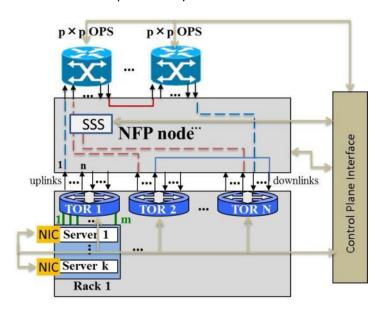

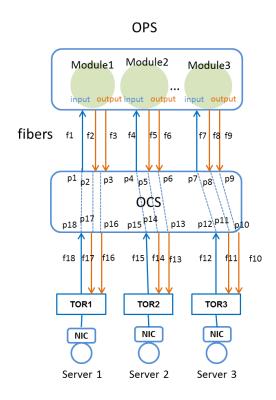

The OPS and OCS schemes are accommodated seamlessly by network function programmable (NFP) node deploying Architecture-on-Demand (AoD) concept [5]. The AoD configuration utilizes a large-port-count fibre switch (LPFS)[6] as the optical backplane. The group of optical modules, acting as the plug-in function pool in the AoD architecture, include Wavelength Division Multiplexing (WDM) modules (e.g. Arrayed Waveguide Grating (AWG), SSS, etc.), Time Division Multiplexing (TDM) modules (e.g. fast switch, OPS system, etc.), and other modules such as splitters, Erbium doped fibre amplifiers (EDFAs) or optical delay lines. With this architecture, different arrangements of inputs, modules and outputs can be constructed by setting up appropriate cross-connections in the optical backplane. Thus, synthetic node architectures can be dynamically created involving only the required transmission and functionality. Utilizing the programmability provided by AoD, the NFP node is capable to deliver various network functions on demand. The implemented functions in

the node can operate in aggregation as well as in isolated groups, which enables the node to fully support hardware virtualization: creating slices of the node and associating them with arbitrary traffic types.

Figure 2.2 illustrates an example for synthetic OPS/OCS intra-cluster connection. OPS/OCS programmable channels provided by hybrid NIC on each server are connected to the NFP node. Then, if OPS function is required, the corresponding link can be connected to an OPS module directly (blue dash line) or connected to SSS, where link capacity can be readjusted or reassembled with other OPS channels from other ToRs (e.g. for multicasting), before the OPS module (red dash line). Likewise, OCS links can be established by connecting OCS-enable channels, after reassembling or directly, between two ToRs through the NFP node (blue solid line). In addition, different OPS modules can be cascaded on demand by setting OCS links between them (red solid line). All ToRs and NICs are connected with control plane with Ethernet raw sockets, and so does the NFP node. Thus, the control layer can configure and enable OPS/OCS function for each intra-cluster connection.

Such intra-cluster architecture design can be easily extended to the inter-cluster DCN architecture, as shown in Figure 2.3. With all clusters utilizing the same intra-cluster infrastructure, another NFP node is used as the inter-cluster NFP node for the interconnection between clusters. Each cluster is connected to the inter-cluster NFP node with a bunch of fibre from the intra-cluster NFP node. A group of Inter-cluster OPS modules are connected to the inter-cluster NFP node as well. ToRs in different clusters can communicate with each other through relayed OCS links or OPS modules provided by inter- and intra-cluster NFP nodes.

Figure 2.2: LIGHTNESS intra-cluster DCN architecture

Figure 2.3: LIGHTNESS inter-cluster DCN architecture

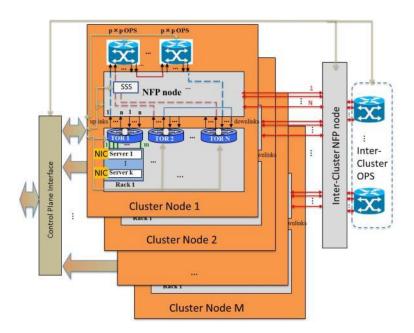

The implementation of the hybrid OCS/OPS data plane test bed is illustrated in Figure 2.4. All the transmitters and receivers from hybrid NICs are connected to a 192×192 fibre switch (Polatis) through 4X16 WSS (FinisarWaveShaper) [7]. The OPS node, additional WSSs (1X4 or 4X16), EDFAs, couplers and splitters are already connected to the fibre switch for network function programmability. At the transmitter side, the FPGA-based NIC parses the input traffic from servers. The inter-function switch sends the traffic either to 10Gbps SFP+links or the optical bandwidth variable transmitters (BVT) according to its destination and capacity. For the SFP+ link, the traffic is aggregated and then encapsulated to OPS or OCS signals. Programmable OPS/OCS over Space Division Multiplexing (SDM) signals are provided through two SFP+ transceivers for intra-cluster communication. The OPS signals are synchronized with the OPS node in the same cluster. For the optical BVT link, the traffic is also aggregated and sent to the optical BVT to generate optical signals with variable capacities for inter-DCN or inter-cluster communication. In the setup of the optical BVT, an electrical multiplexer multiplexes the four 10 Gbaud input signals to a 40 Gbaud electrical signal, which is used to drive an IQ modulator to achieve 40 Gbaud QPSK signals. An optical emulator is followed to generate 40 Gbaud 16QAM signals. A bank of tunable external cavity lasers (ECLs) is feeding the modulators.

Figure 2.4: Implementation of the hybrid OCS/OPS data plane test bed

# 2.2. Implementation of the interface to control plane

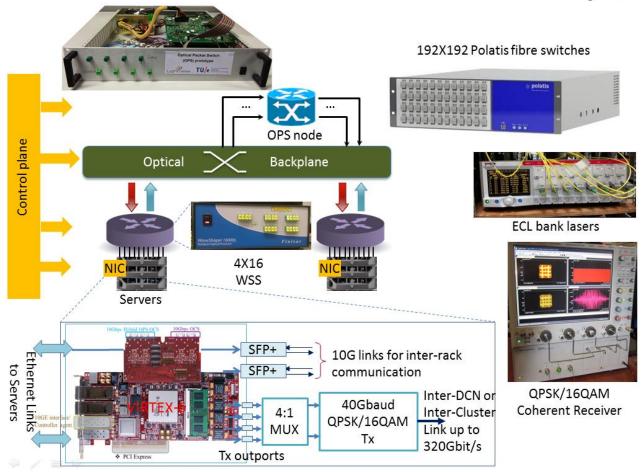

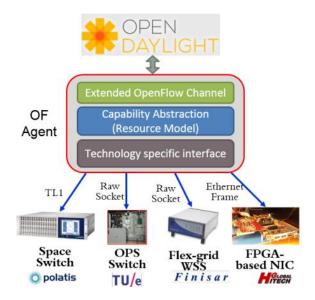

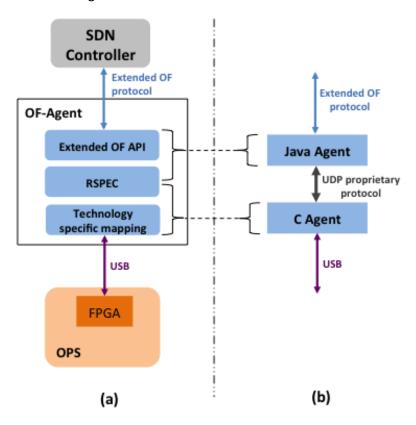

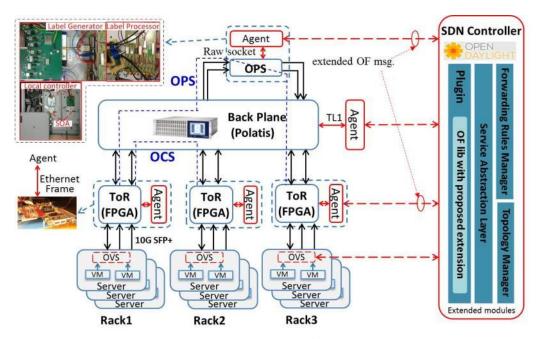

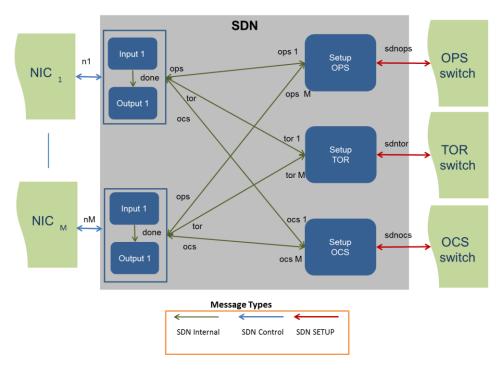

The interface between the control plane and the data plane, i.e. the SDN southbound interface, is the responsible for enabling the SDN-based control and operation of the DCN. In LIGHTNESS, the southbound interface has been implemented by means of the OpenFlow (OF) protocol, which was extended to support the particular features of the hybrid all-optical data plane proposed in the project [8]. Furthermore, to enable the OF-based configuration in the network elements (NEs) of the data plane, a set of OF-Agents was developed. These OF-Agents reside on top of each NE (i.e. OCS, OPS, ToR and NIC) and their role is two-fold. On the one hand, the agents translate the extended OF protocol messages coming from the SDN-controller into a set of operations that perform the actual configuration of the device. On the other hand, the agents collect monitoring information from the devices and send it to the SDN controller formatted as extended OF protocol messages.

Figure 2.5: Interface between control plane and data plane

Figure 2.5 provides the general view of the communication interface between the SDN controller and optical devices developed/employed in LIGHTNESS. The architecture of the OF agents that have been developed for each data plane element is depicted as well (more details can be found in D4.3). In brief, agents utilize the NE's specific management interface (like Simple Network Management Protocol (SNMP), Transaction Language 1 (TL1), Vendor Application Programming Interface (API), etc.) to communicate with the data plane. A generic resource model is used to maintain NE's configuration (i.e., port capabilities and switching constraints). The resource model and specification deals with the complexity of the NEs capabilities and represents them to the controller in a generic way. Finally, the OF agent includes an OF API, which is responsible for the communication with the SDN controller through an extended version of the OF protocol.

Table 2.1 summarizes the control plane interface developed for each LIGHTNESS device and more details will be elaborated in the following section.

|             | Devices                   | Agent development |                     |                         |  |  |  |  |  |  |  |

|-------------|---------------------------|-------------------|---------------------|-------------------------|--|--|--|--|--|--|--|

|             |                           | Language          | Running environment | Device interface        |  |  |  |  |  |  |  |

| OCS switch  | Polatis N-VST-16x16       | С                 | Linux               | Ethernet port           |  |  |  |  |  |  |  |

| Optical ToR | FinisarWaveshaper<br>4000 | С                 | Linux and windows   | USB                     |  |  |  |  |  |  |  |

| OPS         | 4x4 OPS                   | Java and C        | windows             | USB                     |  |  |  |  |  |  |  |

| NIC         | FPGA                      | С                 | Linux               | Ethernet port<br>(SFP+) |  |  |  |  |  |  |  |

Table 2.1: Summary of the interface between control plane and devices

# 3. Optical ToR and programmable NIC evaluation

# 3.1. Implementation

#### 3.1.1. Optical ToR implementation

The proposed optical ToR based on NxM WSS is shown in Figure 3.1. While most of the DCN architectures in the state-of-the-art propose electronic ToRs, our DCN design introduces all-optical links from server-to-server without any O/E/O conversion in the middle stages, thus offering lower latency, higher energy and cost efficiency. In addition, another considerable advantage of having NxM WSS as switching elements instead of static AWGs, router-AWG or fibre switches, is the dynamicity and the flexibility in routing a range of frequency channels on any physical output port, combining both frequency and fibre switching. One more benefit of this WSS-based DCN design stems from the ability of the WSS to operate in Flex-grid, fine filtering desired spectrum slices. Then considering also that links inside DCs are shorter compared to metro/core networks and can tolerate lower Bit Error Rate (BER)-Optical Signal Noise Ratio (OSNR), the channels, i.e. 10Gb/s OOK, can be spaced much closer (20GHz instead of 50GHz that AWGs support). That results in increasing the spectral efficiency of the system by at least 150% while using low-cost technology. Furthermore, the WSS employed in our test bed supports bidirectional communication and can be reconfigured arbitrary (e.g. the 4X16 WSS can be used as 8X12 or 10X10 WSS as well). Thus, the proposed NxM WSS-based ToR design provides intra-rack communication between servers, as well as low-latency inter-rack connectivity with on-demand flexible bandwidth. Grand-bandwidth data exchanges can be served by the high-capacity DP-QPSK channels and/or a combination of the 10G channels.

Figure 3.1: WSS-based Optical ToR implementation

#### 3.1.2. Programmable NIC Implementation

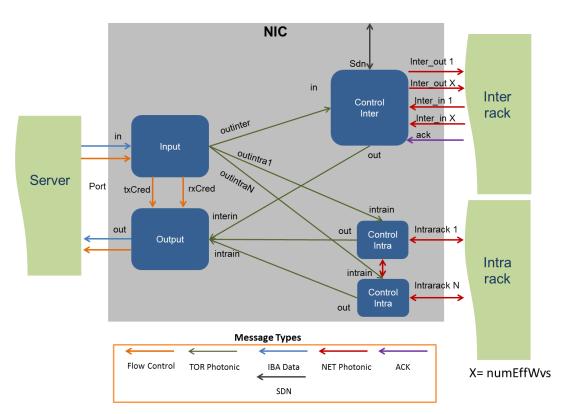

The programmable NIC is proposed to replace the traditional NIC and plugged into each server directly. This flattens the DC infrastructure, enables all intra-rack optical server-to-server communications and eliminates the electronics in the ToR. The infrastructure with programmable NICs and pure optical ToR switch enables achieving high performance intra-rack evolving to inter-rack communication.

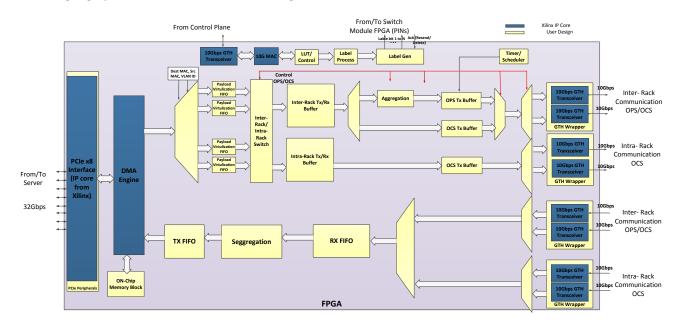

Figure 3.2: FPGA-based NIC Block Diagram

The programmable optical NIC is FPGA-based, designed and implemented in Hitech Global's HTG-V6HXT-X16PCIE-380. It features with Xilinx HX380T FPGA, SFP+ interfaces and Gen2 PCIe interface. The FPGA-based programmable NIC design and implementation block diagram is shown in Figure 3.2.

In Figure 3.2, the blocks represent variable functions. The blue ones are IP cores from Xilinx or third party and the yellow ones are designed and implemented by ourselves. The data flow follows the arrow in the block diagram. The FPGA-based programmable NIC fetches the data from the server RAM and can support 2 hybrid OPS/OCS ports for inter-rack communication and 2 OCS ports for intra-rack communication.

The functions of the programmable NIC are as below:

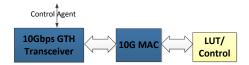

a) 10GE interface with OF agent for communication with SDN control plane

The OF-agent, which acts as a mediation entity with the SDN control plane, talks with the FPGA-based programmable NIC through 10GE interface. The FPGA-based programmable NIC receives the pre-defined Ethernet frame, parses the frame, get the useful information and stores the commands in the Look-Up Table(LUT). The FPGA-based block diagram is shown in Figure 3.3.

Figure 3.3: FPGA-based controller agent interface block diagram

The size of pre-defined Ethernet frame (with VLAN ID) is 1504 Byte, the node ID is defined as the first byte of destination MAC address. The programmable NIC supports push, pull, add, delete and modify functions. These functions are defined in the last byte of destination MAC address of the Ethernet frame. The details of the mapping information of the LUT and the Ethernet frame are shown in Figure 3.4.

|      |                                  |                                            |      |     |      |      |       |     |    |     |       | Ethernet Frame<br>lines (Captured<br>by Wireshark) | LUT RAM     |       |       |             |             |      |      |     |     |                           |                       |      |  |   |   |    |      |               |      |     |         |             |

|------|----------------------------------|--------------------------------------------|------|-----|------|------|-------|-----|----|-----|-------|----------------------------------------------------|-------------|-------|-------|-------------|-------------|------|------|-----|-----|---------------------------|-----------------------|------|--|---|---|----|------|---------------|------|-----|---------|-------------|

| AD   | 31                               | 30                                         | 29   | 28  | 27   | 26   | 25    | 24  | 23 | 22  | 21    | 20                                                 | 19          | 18    | 17    | 7 16        | 15          | 14   | 13   | 12  | , 1 | 11 10 9 8 7 6 5 4 3 2 1 0 |                       |      |  |   |   |    |      | hv Wiresharki |      |     |         |             |

| ,,,, | 31                               | 30                                         | 23   | 20  |      |      | 23    |     | 23 |     |       |                                                    | 13          | 10    |       | , 10        | 13          | 17   | 13   |     | +   |                           |                       |      |  | - | - | -1 | -    |               |      |     | 0       | 04.00       |

|      |                                  | Source MAC Address Destination MAC Address |      |     |      |      |       |     |    |     |       |                                                    |             | ess   |       | 01,02       |             |      |      |     |     |                           |                       |      |  |   |   |    |      |               |      |     |         |             |

| 00   | RESERVED                         |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       | 10,20 | 03,04,05,06 |             |      |      |     |     |                           |                       |      |  |   |   |    |      |               |      |     |         |             |

|      |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     | f   | rame                      | Time-slice<br>numbers |      |  |   |   |    |      |               |      |     |         |             |

| 01   | K                                | еер а                                      | live | mes | sage | leng | th (1 | .0) |    | Tin | ne-sl | ice c                                              | urati       | on (0 | 09)   |             |             |      |      |     |     | size                      | (08)                  |      |  |   |   | Et | hern | et/OF         | PS M | ODE | 30,40   | 07,08,09,10 |

| 02   | OPS switch information channel 1 |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       | 50,60       | 11,12,13,14 |      |      |     |     |                           |                       |      |  |   |   |    |      |               |      |     |         |             |

| 03   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       | 70,80 | 15,16,17,18 |             |      |      |     |     |                           |                       |      |  |   |   |    |      |               |      |     |         |             |

| 04   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el1 |     |                           |                       |      |  |   |   |    |      |               |      |     | 90,a0   | 19,20,21,22 |

| 05   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el1 |     |                           |                       |      |  |   |   |    |      |               |      |     | b0,c0   | 23,24,25,26 |

| 06   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el1 |     |                           |                       |      |  |   |   |    |      |               |      |     | d0,e0   | 27,28,29,30 |

| 07   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el1 |     |                           |                       |      |  |   |   |    |      |               |      |     | f0,100  | 31,32,33,34 |

| 08   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     |     |                           |                       |      |  |   |   |    |      |               |      |     | 110,120 | 35,36,37,38 |

| 09   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el2 |     |                           |                       |      |  |   |   |    |      |               |      |     | 130,140 | 39,40,41,42 |

| 10   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el2 |     |                           |                       |      |  |   |   |    |      |               |      |     | 150,160 | 43,44,45,46 |

| 11   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el2 |     |                           |                       |      |  |   |   |    |      |               |      |     | 170,180 | 47,48,49,50 |

| 12   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el2 |     |                           |                       |      |  |   |   |    |      |               |      |     | 190,1a0 | 51,52,53,54 |

| 13   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el2 |     |                           |                       |      |  |   |   |    |      |               |      |     | 1b0,1c0 | 55,56,57,58 |

| 14   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    | OP          | S sw  | itch  | n infor     | mati        | on c | nann | el2 |     |                           |                       |      |  |   |   |    |      |               |      |     | 1d0,1e0 | 59,60,61,62 |

| 15   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     |     |                           |                       |      |  |   |   |    |      |               |      |     | 1f0,200 | 63,64,65,66 |

| 16   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     |     | Heade                     | er (Buffe             | r 1) |  |   |   |    |      |               |      |     | 210,220 | 67,68,69,70 |

| 17   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     |     | Heade                     | er (Buffe             | r 2) |  |   |   |    |      |               |      |     |         | 71,72,73,74 |

| 18   |                                  |                                            |      |     |      |      |       |     |    |     |       | 250260                                             | 75,76,77,78 |       |       |             |             |      |      |     |     |                           |                       |      |  |   |   |    |      |               |      |     |         |             |

| 19   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     |     | Heade                     | er (Buffe             | r 4) |  |   |   |    |      |               |      |     | 270,280 | 79,80,81,82 |

| 20   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     |     | Heade                     | er (Buffe             | r 1) |  |   |   |    |      |               |      |     | 290,2a0 | 83,84,85,86 |

| 21   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     |     | Heade                     | er (Buffe             | r 2) |  |   |   |    |      |               |      |     | 2b0,2c0 | 87,88,89,90 |

| 22   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     |     | Heade                     | er (Buffe             | r 3) |  |   |   |    |      |               |      |     | 2d0,2e0 | 91,92,93,94 |

| 23   |                                  |                                            |      |     |      |      |       |     |    |     |       |                                                    |             |       |       |             |             |      |      |     |     | Heade                     | er (Buffe             | r 4) |  |   |   |    |      |               |      |     | 2f0,300 | 95,96,97,98 |

Figure 3.4: NIC LUT address MAP in the FPGA

The LUT contains every single function that FPGA-based programmable NIC can support. The functions include fetching/storing data from/to the server RAM, OCS/OPS hitless switchover and the hitless switchover of the programmable parameters, such as time-slice duration and keep-alive message duration. These functions will be described later in this section.

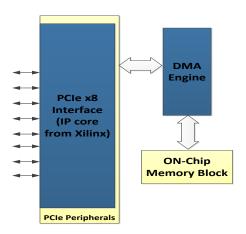

#### b) PCIe Gen2 fetching/storing data from/to the server RAM

The PCI Express is based on point-to-point topology, with separate serial links connecting every device to the host. To get the maximum throughput, we used a Direct Memory Access (DMA) for copying large amounts of data efficiently between two devices with minimal host processor involvement. The advantage of using the DMA with PCIe is DMA Engine can issue large burst transactions and a repetitive task required only simple decisions, well suited for hardware acceleration. The FPGA-based block diagram of the PCIe with DMA is shown in Figure 3.5.

Figure 3.5: FPGA-based PCIe and DMA engine block diagram

Here the PCIe core is a hard IP core directly embedded in the FPGA board. The underlying communications mechanism consists of three layers: the Transaction Layer, the Data Link Layer, and the Physical Layer. The transmission of the packet which is interested for us is defined as a Transaction Layer Packet (TLP), which relates to the PCIe's uppermost layer. A flow control mechanism makes sure that a packet is sent only when the link partner is ready to receive it.

The DMA engine is the EZDMA2 IP core from PLDA. The PLDA EZDMA2 core can support up to 8 built-in DMA channels and up to 4GB DMA data transfer. With the 8 independent DMA channels that may be used simultaneously, it could manage up to 8 separate data flows.

The main module in the EZDMA2 core is the master request module and the master completion module. The master request module receives and transmits transfer requests to the transmit module. When one or more channel requests are detected, the Master Request Module masks requests for which there are no completion resources or not enough credits. It then selects the requests according to a round-robin priority scheme. Data is read from the local interface without any DMA channel interaction. Master Completion module receives Completions from the Receive module. It identifies the appropriate completion resource, DMA channel, and local address for the Completion and informs the requesting channel. Data is transmitted

to the local interface without any DMA channel interaction. The Master Completion Module receives Completions from the Receive module and informs the requesting channel.

#### c) Destination MAC address, source MAC address and VLAN ID based traffic classification

The programmable FPGA-based NIC is capable of classify the traffic based on the destination MAC address, source MAC address and VLAN ID. The income traffic is filtered and stored in separate isolated FIFO, and will be aggregated or processed based on each FIFO. The FPGA-based traffic classification block diagram is shown in Figure 3.6.

Figure 3.6: FPGA-based traffic classification block diagram

The implementation includes 4 FIFOs. The matching of the header includes destination MAC address (6 bytes), source MAC address (6 bytes) and VLAN ID (4 bytes). There is a separate mask for each bit of the header. The mask works on bit-based map, select the bits of header to match with the traffic. In the FPGA implementation, we defined the bit-based '1' means select, '0' means not. All the matching information is sent through the controller agent and the LUT updates the matching information accordingly. Therefore, the FPGA-based programmable NIC is capable of classify the traffic based on one single, or a set of header information, i.e., the last byte of destination MAC address 01 can be picked up and stored in FIFO1, the last byte of destination MAC address 02-07 can be groomed in FIFO2 and so on. This function supplies the most flexibility and availability for classifying the traffic.

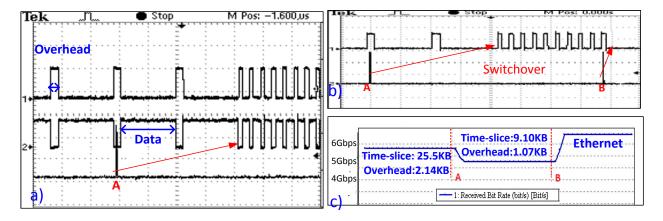

#### d) OPS/OCS hitless switchover

A very important function of the FPGA-based programmable NIC is the OPS/OCS hitless switchover. There are two ports in the implementation supporting the hybrid OPS/OCS switchover. To get the hitless feature, when the FPGA-based programmable NIC receives the OPS/OCS switchover command from the controller agent, the OPS/OCS switchover functional block does not switch immediately; instead, it carries on with the current mode and clears the data in the transmitter buffer. After the transmitter buffer is empty, the mode is switched, and the NIC starts to transmit the traffic in the new mode.

#### e) Configurable parameters

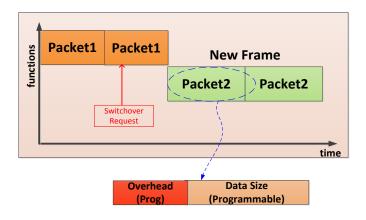

For the OPS, the packet size and overhead is an important consideration in the experiment. These two parameters can be programmed on-the-fly in the FPGA-based programmable NIC by the controller agent.

When the data goes through the OPS switches, the packets are cut and forwarded to the path according to the label which causes the FPGA-based programmable NIC receives the traffic in burst mode. When there is

no traffic received or the receiver receives the adjacent packets from different sources, the FPGA-based receiver lost the clock. Then, in the start of the packet, the FPGA-based receiver has to recover the clock based on the incoming traffic. Therefore, the overhead before the data is vital to avoid any data loss for the FPGA receiver recovering the clock. The duration of the overhead needed, just enough for recovering the clock, depends on the transmission environment, i.e. the number of the switches used, the loss of the optical devices and so on. When setting up the optical network with the FPGA-based programmable NIC, we can configure the overhead parameter on-demand.

After fixed the minimum overhead, the maximum bandwidth and the latency are relevant to the real data size in the packet. Based on the requirements of the different scenario, such as latency sensitive or bandwidth crucial, we can program the data size accordingly.

Figure 3.7: Packet size switchover when receives the request

Figure 3.7 shows that when the request of changing the overhead size or data size is received, the FPGA-based programmable NIC finishes the current packet and starts to transmit the packet with the new size parameters.

# 3.2. System evaluation

#### 3.2.1. WSS-based optical ToR evaluation

The characteristics of WSS-based optical ToR by deploying Finisar Waveshaper 16000 are listed in Table 3.1. Furthermore, we measured the pass-through latency of the WSS (24ns) with the traffic analyzer.

| Insertion Loss (incl. connectors) | 6.5 dB (typ. 4.5 dB) |

|-----------------------------------|----------------------|

| Polarization Dependent Loss (PDL) | 0.7 dB (typ. 0.2 dB) |

| Filter Shape                      | Arbitrary            |

| Filter Bandwidth                  | 10 GHz to 5 THz      |

| Center Frequency Setting Accuracy | ± 2.5 GHz            |

| Bandwidth Setting Accuracy        | ± 5 GHz              |

| Settling Time                        | 500 ms   |

|--------------------------------------|----------|

| Maximum Total Input Optical Power    | + 27 dBm |

| Max Optical Power per 50 GHz channel | + 13 dBm |

| Latency pass-through (measured)      | 24ns     |

Table 3.1: Characteristics of the WSS-based ToR

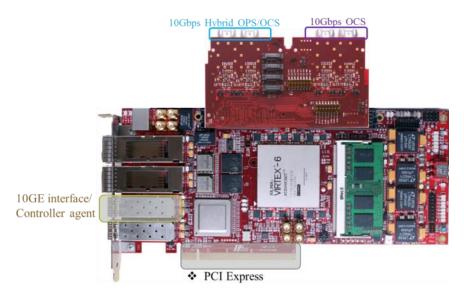

#### 3.2.2. FPGA-based programmable NIC evaluation

The FPGA-based programmable NIC is fully tested and evaluated based on the functions described in the previous section. The board we used for testing is Hitech Global Xilinx Virtex 6 PCle board. The picture of the board is shown in Figure 3.8.

Figure 3.8: HiTech Global Xilinx Virtex 6 PCIE board

The PCIe interface on the board is Gen2 x16 lanes, we used x8 lanes for the implementation and testing because the DMA core we currently used only supports x8 lanes. We used 2 ports on the FPGA Mezzanine Card (FMC)-SFP+ daughter card as the hybrid OPS/OCS transceivers (inter-rack communication), and 2 ports on the FMC-SFP+ daughter card for the OCS only transceivers (intra-rack communication). Furthermore, we used one port on the board for communicating with the controller agent.

We did several experiments based on the PCIe/DMA only, PCIe/DMA with MAC and FIFO, and the programmable NIC. The experiment setup and test results are shown as below:

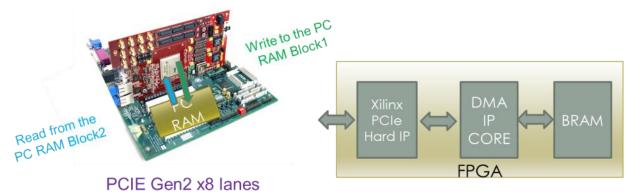

#### a) PCIe/DMA-only test

The first experiment is only based on the PCle/DMA. The test setup is shown in the left side of Figure 3.9. The FPGA-based board is plugged into the server PCle socket. In the FPGA, the design and implementation is shown in the right side of Figure 3.9. In this experiment, only dummy data are used for transmitting and

receiving.

Figure 3.9: PCIe/DMA-only test setup and FPGA-based implementation

When write, the dummy data is sent through the DMA, PCIe and stored in the server RAM block 1.

When read, the dummy data is read from the server RAM block2, through the PCIe, DMA and stored in the BRAM of the FPGA.

The screen of the 8 functions the driver support is shown in Figure 3.10. The driver of the DMA engine allows to preset the size of the block data that to be transferred in one go.

```

Ø. Exit

1. Read Config

2. Read Config to file

3. Read Bar

4. Read Bar to file

5. Write Bar

6. DMA Test

7. SG DMA Test

8. Throughput measurement

Enter your choice :_

```

Figure 3.10: DMA engine driver script

We did the experiment based on 128KB block data.

The Maximum Throughput Measurement (128KB block data):

Read only (PC to NIC): Read Rate 12.8Gbps

Write only (NIC to PC): Write Rate 23.36Gbps

Read and Write: Read Rate 10.46Gbps Write Rate 21.36Gbps

When read/write through PCIe, the protocol is set to wait for the host (server) to reply. Therefore, the DMA performance is dependent on the latency of the platform, which is the time that the host takes to reply. For writing to the PC RAM, it only needs to wait the response and completion from the host once before writing the block of RAM. For reading from the PC RAM, it needs to wait the response from the host every TLP. So the read rate is lower than write rate.

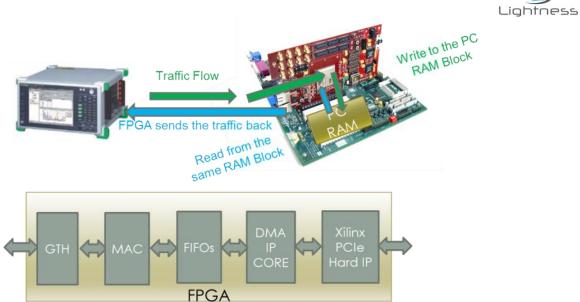

#### b) Basic NIC, PCIe/DMA with MAC and FIFO, real Ethernet traffic

The second experiment setup is shown in the top of Figure 3.11. The FPGA-based implementation is shown in the bottom of Figure 3.11, which includes GTH (transceiver in the FPGA), 10GE MAC, FIFOs, DMA and PCIe.

Figure 3.11: Basic NIC, PCIe/DMA with MC and FIFO setup and FPGA-based implementation

The traffic is generated by the traffic generator and sent to the FPGA through 10Gbps link, the 10GE MAC processed the data, buffered them, and stored in the server RAM through DMA/PCIe. Then these data are read back from the same RAM block and moved back to the FPGA FIFO by DMA/PCIe. After processed by MAC, these data are sent out as Ethernet frames and received by traffic analyzer.

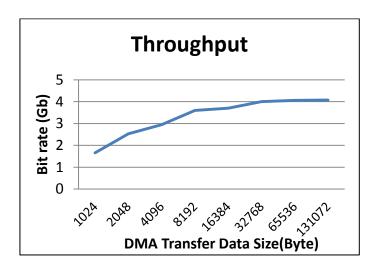

By configuring the DMA transferring data size (assigned RAM block size), we can measure the maximum throughput (1500B Ethernet Frame) that the basic NIC can deliver without any data loss. The result chart is shown in Figure 3.12Error! Reference source not found..

Figure 3.12: Basic NIC throughput by RAM block

When the RAM block size goes larger, the more data is transferred in one-go. The maximum throughput in this experiment is around 4Gbps. There are two factors that affect the limited throughput here. One is the Read and Write process works on the same RAM block in the PC, the read only happens after write, not simultaneously, so the throughput is limited. The other one is because the implementation in the FPGA caused around 30% data overhead when moving the traffic to the server RAM.

Figure 3.13: Basic NIC latency result

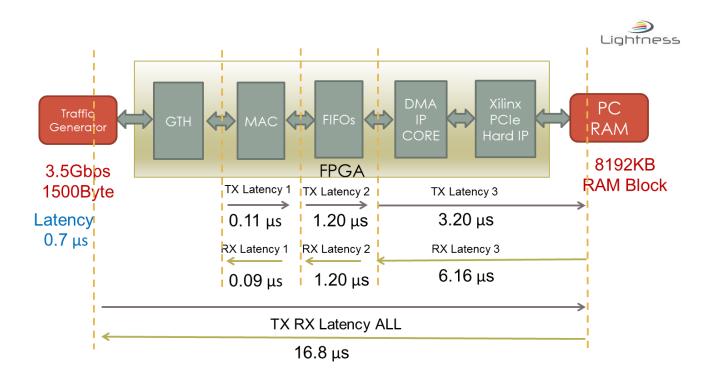

To get the latency result, we compromise the traffic and RAM block size by configuring 8192KB RAM block size, and set the traffic as 3.5Gbps. The detailed latency is shown in Figure 3.13.

From Figure 3.13, we can see the latency is mainly caused by the DMA/PCIe moving data between FPGA and PC RAM. The TX latency is  $3.2\mu s$  and the RX latency is  $6.16\mu s$ . The FIFO latency is because the implementation of the basic NIC needs to wait for a complete Ethernet frame then send out. The total latency for the basic NIC to receive a 1500B Ethernet Frame, put it in the PC RAM, read it out, processed in the FPGA, and then sent back to the traffic analyzer is  $16.8\mu s$ .

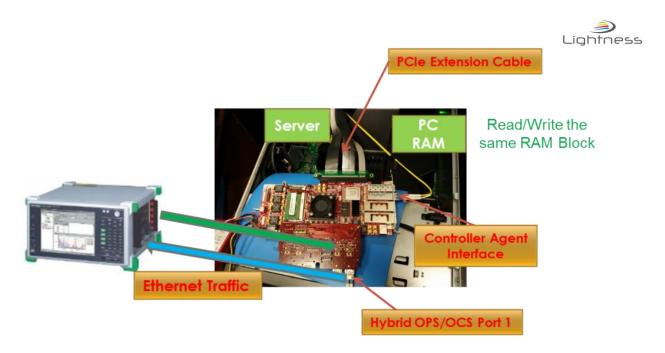

#### c) FPGA-based programmable NIC test

The FPGA-based programmable NIC is experimentally tested. The experiment setup is shown in Figure 3.14. The FPGA-based programmable NIC is connected to the server socket through PCIe extension cable. The controller agent interface of the FPGA-based programmable NIC is connected with the server through SFP+ and fibre. For testing, the traffic generator generates the Ethernet traffic and feeds directly to the hybrid OPS/OCS port. The hybrid port 1 is set to OCS mode. Therefore, after receiving the Ethernet traffic, the FPGA-based NIC processed the data, and sent them through DMA/PCIe to the server RAM. After the transmission, the DMA engine initiates the transmission from the server RAM back to the FPGA. The FPGA-based NIC then do the processing in the OCS mode and sends the traffic out to the traffic analyzer which measures the latency.

Figure 3.14: FPGA-based programmable NIC experiment setup

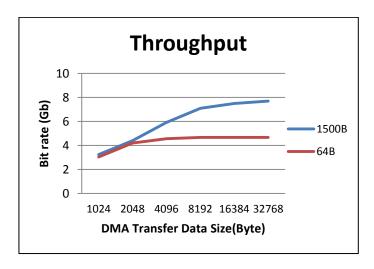

In the experiment we measured the maximum throughput and the latency. The maximum throughput measurement result is shown in Figure 3.15. For the throughput measurement, the data is written to the RAM, and after the block of RAM is filled, the data is read back. The maximum throughput is limited because of this non-duplex transmission.

Figure 3.15: FPGA-based programmable NIC maximum throughput measurement result

The maximum throughput for 1500B Ethernet frame is around 8Gbps and for 64B Ethernet frame is around 4.7Gbps. The difference of the maximum throughput that the FPGA-based programmable NIC can achieve between 1500B and 64B is because the header and tailor of the frames need to be written into the RAM to get the correct data out, and for 64B, the ratio of the real data and the whole frame with header and tailor is much lower than 1500B. Therefore, the throughput performance for 64B Ethernet frame is worse than 1500B Ethernet frame. This throughput could be improved by sending the data directly from the server.

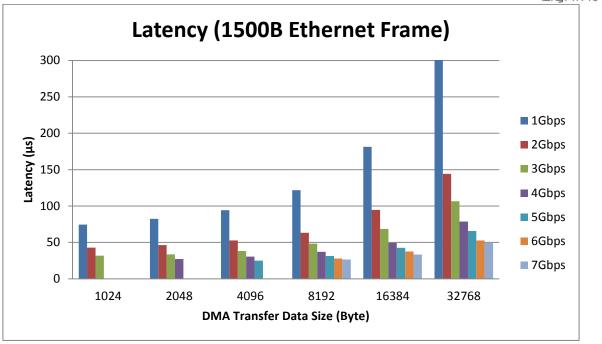

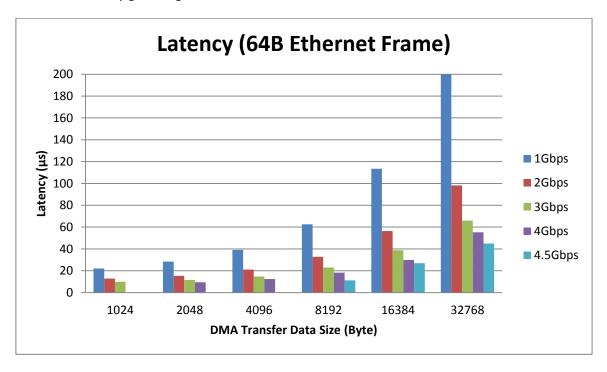

We also measured the latency with different DMA transfer data size and Ethernet frame size. The measurement results are shown in Figure 3.16 and Figure 3.17.

Figure 3.16: FPGA-based programmable NIC maximum throughput measurement result (1500B)

Figure 3.16 shows the measured latency result of the traffic of 1500B Ethernet frame. The latency increases when the DMA transfer data size increases. The minimum latency we can get is when transmitting 3Gbps traffic with 1024Byte DMA transfer data size. By increasing the DMA transfer data size, the throughput increases but the latency gets longer.

Figure 3.17: FPGA-based programmable NIC maximum throughput measurement result (1500B)

Figure 3.17 shows the measured latency result of the traffic of 64B Ethernet frame. Similar to the measured results of 1500B Ethernet frame, the measured result shows the latency increases when the DMA transfer

data size increases. The minimum latency measured is  $9.417\mu s$  when DMA transfer data size is 2048 Bytes, and the bit rate of the traffic is 4Gbps.

Comparing Figure 3.16 and Figure 3.17, the traffic of 64B Ethernet frame has better latency performance than the traffic of 1500B Ethernet frame. In the FPGA-based traffic processing, 1500B Ethernet frame takes longer time than 64B Ethernet frame.

Lastly, we measured the FPGA-based programmable NIC performance when switchover among the programmable parameters and OCS/OPS switchover.

Figure 3.18: Programmable parameters test results

Figure 3.18(a) shows the hitless transmission after switchover, when switch from OPS to OCS, the interfunction switch blocks wait for the current aggregated time-slice finished, then starts to transmit the Ethernet. In opposite, while switching from OCS to OPS, the FPGA waits finishing processing current Ethernet Frame, and then starts to transmit as packet-based. The programmable parameters switchovers are demonstrated in Figure 3.18 (b) and (c), such as overhead (programmable from 0 to 39KB) and packet data size (programmable from 80B to 31.25KB) parameters changed from one to the other which shows in Figure 3.18(c) that the maximum bandwidth changed correspondingly.

## 3.3. Interface with control plane

#### 3.3.1. Interface with control plane for optical ToR

Figure 3.19: WSS-based Optical ToR's interface with control plane

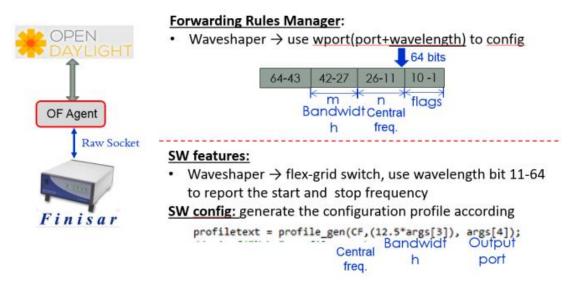

The OF agent sits between the SDN controller and WSS-based optical ToR and includes two software tools: one is running on a Linux server which directly communicates with the SDN controller in the northbound and with a windows proxy (where WSS driver are installed) in the southbound. The interaction between these two parts is implemented through socket.

The OF agent (windows proxy) communicates with WSS through Ethernet interface (management interface) and messages are transmitted in raw socket. For the feature advertisement, except the flex-grid switch capability, the agent also reports the supported frequency range (with start and stop frequency) and port count, fetched from device (using the management API command). For configuration purpose, after the agent receives the configuration message (OF cflow\_mod as shown in Figure 3.19) from the controller, it uses the central frequency/bandwidth and the output port to generate a configuration profile according to the specification defined by the WSS. This profile will be loaded by WSS to implement the channel configuration. The channel release follows the same approach.

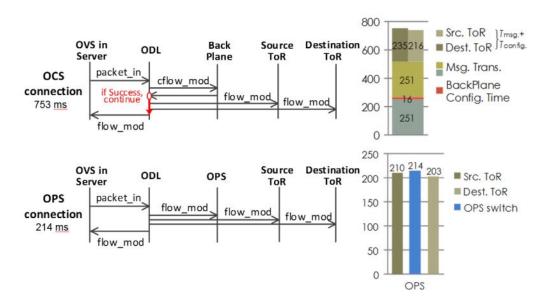

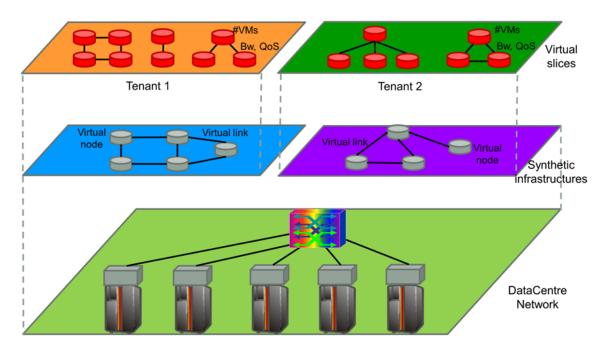

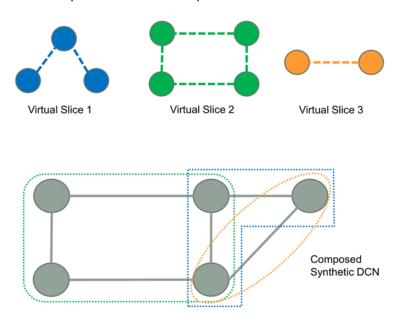

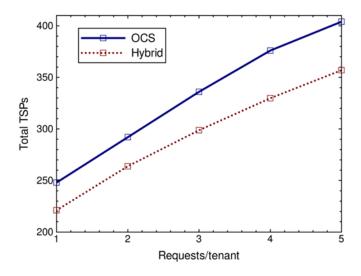

#### 3.3.2. Interface with control plane for hybrid NIC