# **REALITY**

# Reliable and Variability tolerant System-on-a-chip Design in More-Moore Technologies

### Contract No 216537

### Deliverable D8.5

### **Dissemination and Use Plan**

# (second issue, at the end of project)

Editor: Miguel Miranda, Yves Laplanche, Giuseppe Desoli

Status - Version: V1.0

Date: 4/10/2010

Confidentiality Level: Public

ID number: IST-216537-WP8-D8.5.doc

### © Copyright by the REALITY Consortium

### The REALITY Consortium consists of:

| Interuniversity Microelectronics Centre (IMEC vzw) | Prime Contractor | Belgium        |

|----------------------------------------------------|------------------|----------------|

| STMicroelectronics S.R.L. (STM)                    | Contractor       | Italy          |

| Universita Di Bologna (UNIBO)                      | Contractor       | Italy          |

| Katholieke Universiteit Leuven (KUL)               | Contractor       | Belgium        |

| ARM Limited (ARM)                                  | Contractor       | United Kingdom |

| University Of Glasgow (UoG)                        | Contractor       | United Kingdom |

# **Table of contents:**

| 1. DISCLAIMER                                                                | 4  |

|------------------------------------------------------------------------------|----|

| 2. ACKNOWLEDGEMENTS                                                          | 4  |

| 3. DOCUMENT REVISION HISTORY                                                 | 4  |

| 4. PREFACE                                                                   | 5  |

| 5. ABSTRACT                                                                  | 6  |

| 6. INTRODUCTION                                                              | 7  |

| 7. DISSEMINATION ACTIVITIES                                                  | 8  |

| 7.1. DISSEMINATION STRATEGY                                                  | 8  |

| 7.2. INTERNAL PROJECT COMMUNICATION / DISSEMINATION                          | 9  |

| 7.2.1. INTERNAL WEBSITE AND WIKI                                             | 9  |

| 7.2.2. PROJECT MEETINGS1                                                     | 0  |

| 7.2.3. COMMUNICATION LIST                                                    | 1  |

| 7.3. EXTERNAL COMMUNICATION / DISSEMINATION1                                 | .1 |

| 7.3.1. PUBLIC WEB SITE                                                       | .1 |

| 7.3.1.1. STATISTICAL INFORMATION1                                            | 2  |

| 7.3.1.2. EXTRA STATISTICAL INFORMATION1                                      | 3  |

| 7.3.2. PROMOTION AT EXHIBITIONS AND CONFERENCES                              | 4  |

| 7.3.3. ORGANIZATION OF TRAINING - WORKSHOPS1                                 | 5  |

| 7.3.3.1. DATE 2010 WORKSHOP: THE FRUITS OF VARIABILITY RESEARCH IN EUROPE 15 |    |

| 7.3.4. PROMOTIONAL FLYER AND BULLETIN1                                       | 9  |

| 7.3.5. PRESS RELEASES                                                        | 0  |

| 7.3.6. CROSS REFERENCE PROMOTION2                                            | 0  |

| 7.4. SCIENTIFIC DISSEMINATION                                                | 2  |

| 7.4.1. PUBLICATIONS IN CONFERENCES                                           | 2  |

| 7.4.2. WORKSHOPS, SEMINARS, TUTORIALS AND KEYNOTES2                          | 4  |

| 7.4.3. EDUCATION                                                             | 5  |

| 8. FINAL USE PLAN (EXPLOITATION STRATEGY)2                                   | 6  |

| 8. | 1.   | USE BY INDUSTRIAL PARTNERS IN PROPRIETARY PRODUCTS                                                                   | 26 |

|----|------|----------------------------------------------------------------------------------------------------------------------|----|

| 8. | 1.1. | ST MICROELECTRONICS                                                                                                  | 26 |

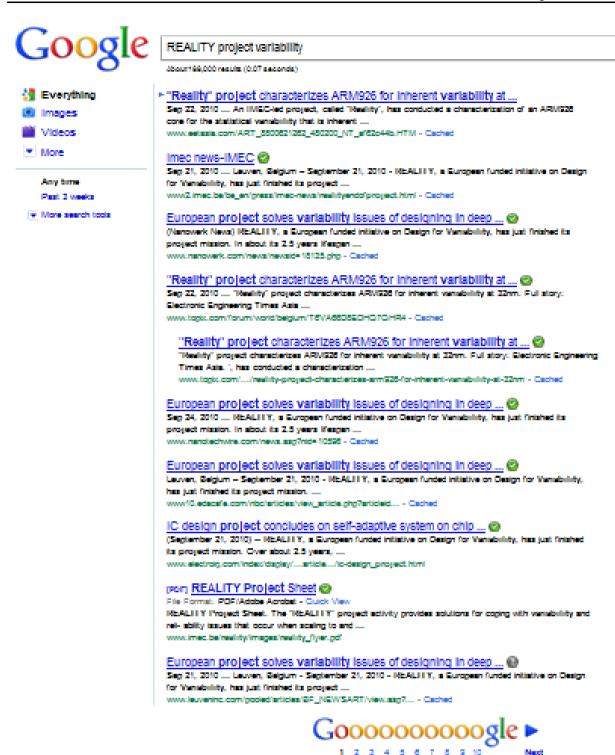

|    |      | RID (CORNER/STATISTICAL) STATISTICAL TIMING ANALYSIS FLOW FOR DIGITAL BLOCKS. ALITY: NOT ONLY TECHNICAL ACHIEVEMENTS |    |

| 8. | 1.2. | ARM                                                                                                                  | 30 |

|    | IMPO | RIABILITY CHARACTERIZATION:                                                                                          | 32 |

| 8. | 2.   | USE BY ACADEMIC PARTNERS TO ADVANCE RELEVANT RESEARCH                                                                | 33 |

| 8. | 2.1. | UNIVERSITY OF GLASGOW                                                                                                | 33 |

| 8. | 2.2. | KULEUVEN                                                                                                             | 33 |

| 8. | 3.   | USE BY RESEARCH INSTITUTION IMEC                                                                                     | 33 |

| 9. | LI   | IST OF ABBREVIATIONS                                                                                                 | 35 |

### 1. Disclaimer

The information in this document is provided as is and no guarantee or warranty is given that the information is fit for any particular purpose. The user thereof uses the information at its sole risk and liability.

### 2. Acknowledgements

The author acknowledges contributions by all work-package leaders of the REALITY consortium.

## 3. Document revision history

| Date       | Version | Editor/Contributor | Comments      |

|------------|---------|--------------------|---------------|

| 30/09/2010 | V0.1    | Miguel Miranda     | First draft   |

| 6/10/2010  | V1.0    | Miguel Miranda     | Final version |

#### 4. Preface

The scope and objectives of the REALITY project are:

Development of design techniques, methodologies and methods for real-time guaranteed, energy-efficient, robust and adaptive SoCs, including both digital and analogue macro-blocks

### The Technical Challenges are:

- To deal with increased static variability and static fault rates of devices and interconnects.

- To overcome increased time-dependent dynamic variability and dynamic fault rates.

- To build reliable systems out of unreliable technology while maintaining design productivity.

- To deploy design techniques that allow technology scalable energy efficient SoC systems while guaranteeing real-time performance constraints.

### Focus Areas of this project are:

- "Analysis techniques" for exploring the design space, and analysis of the system in terms of performance, power and reliability of manufactured instances across a wide spectrum of operating conditions.

- "Solution techniques" which are design time and/or runtime techniques to mitigate impact of reliability issues of integrated circuits, at component, circuit, architecture and system (application software) design.

The REALITY project has started its activities in January 2008 and is planned to be completed after 30 months. It is led by Dr. Miguel Miranda of IMEC. Five contractors (STM, ARM, KUL, UoG, UNIBO) participate in the project. The total budget is 2.899 k€.

#### 5. Abstract

The goal of this document is to provide the details regarding the deliverable "D8.5 Dissemination and Use Plan (DUP)" for the REALITY Project (IST-216537) at the end of last reporting period.

The DUP aims at describing the planned strategy for the internal and external dissemination of the project's objectives and also at stating a preliminary approach to the market analysis and exploitation of the REALITY project's results and outputs.

The DUP is conceived in conjunction with all the Consortium partners in order to give way to the most effective strategy and to obtain the highest return in terms of mass-knowledge on the project's topics and of economic gain. This deliverable in particular, addresses specific dissemination actions and proposes an approach to the future exploitation of the REALITY project results and outputs.

This document is issued in the third year (M32) close to the project end date and it summarizes the dissemination and use strategy. It also provides a more in depth analysis of the valorisation and use case scenarios.

After an introduction to the general aims of the dissemination and preliminary exploitation planning, D8.5 is subdivided into two main sections. The first chapter offers a detailed description of the dissemination activities performed and planned for promoting and spreading the REALITY results among and to the international academic and industrial organizations. The second chapter provides an overview of the exploitation possibilities from the viewpoint of our industrial parents.

Within the REALITY consortium all partners contribute to a large extend equally to the dissemination of the project results.

IPR, Access rights and licensing have been made explicit and described in an elaborate way in the Consortium Agreement which was signed by all consortium partners.

#### 6. Introduction

The REALITY project has started its activities in January 2008 and has completed after 32 months. It is led by Dr. Miguel Miranda of IMEC. The Project Coordinator is also Dr. Miguel Miranda from IMEC. Five contractors (STM, ARM, KUL, UoG, UNIBO) participate in the project. The total budget is 2.899 k€.

This FP7 funded project is the base for collaboration between major industrial players in this field, research institutes and academic partners: ST, ARM, University of Glasgow, University of Bologna, KU Leuven and IMEC.

The selected target test vehicles for REALITY project comes from the two industrial partners: ST and ARM.

The "REALITY" project activity provides solutions for coping with variability and reliability issues that occur when scaling to and beyond the 32 nm technology node. A system-level solution is provided by focusing on two main axes: Analysis Techniques and Solution Techniques.

Deliverable D8.5

### 7. Dissemination Activities

### 7.1. Dissemination Strategy

The dissemination ensures the spreading of the project's outcome among other industrial and academic organizations so that the methodologies and tools developed can be used in these sectors.

This objective has been achieved by using multiple different strategies.

In general terms, the dissemination of the REALITY project adopted the following principles:

- <u>Dissemination of project results to the international research and design community,</u> which is a crucial aspect for the effective exploitation of the project results in the community and outside the consortium. This objective has been achieved through tge many scientific publications, participation to conferences, and the maintenance of the project website.

- The organizations of training actions/workshops has complemented and strengthen the

dissemination. The mobilization of resources of REALITY (most of which invested in R&D

activities) coupled with the expertise of the partners involved, have guaranteed that

innovative technologies in the area of reliability and variability have been created during

the execution of the project.

- The dissemination of project results by the consortium partners as well as by the broader community of designers vary depending on the specific technological results obtained in REALITY and the specific business segments addressed by the partners. Dissemination opportunities have been created though by advertising to the right audience and communities.

Deliverable D8.5

#### 7.2.1. Internal website and wiki

7.2. Internal Project communication / dissemination

At the start of the REALITY project, IMEC has created and hosts an internet website (<a href="www.fp7-reality.eu">www.fp7-reality.eu</a>) which is up and running since April 2008. The goal of this site has been to share research results among the general public and enhance the visibility of the research activity. A wiki (<a href="http://www-micrel.deis.unibo.it/~reality/wiki/index.php/Main Page">http://www-micrel.deis.unibo.it/~reality/wiki/index.php/Main Page</a>) has been setup by the University of Bologna. The primary goal of the wiki is to stimulate the effective communication within the project consortium. It is also intended as a way to limit the circulation of files and paper as much as possible.

The REALITY consortium registered and acquired the right to use an ".eu" domain name for the project website: www.fp7-reality.eu

During the course of the project, the REALITY website contents will be progressively enriched in order to provide an up-to-date view of the research progress.

Access to the wiki is password protected and meant for keeping internal project data like:

action trackers

Deliverable D8.5

- confidential presentation material

- risk management plan and updates

- document templates

- deliverables (non public), and related draft work documents

- scientific reports, in case they are for restricted use

- communication lists

Figure 1: Screenshot of the wiki page for internal communication purposes

The contents and objectives of the public website can be found below.

### 7.2.2. Project meetings

Face to face project meetings with having all consortium partners to join, have been held each six months approximately. A fixed item on the meeting agenda has been a brief status review by each of the individual consortium partners on their realized and planned dissemination activities. Also the inventory and outlook for new scientific publications in the past and next half year was shared. Finally, tactics and approach towards dissemination of the potential project results to industrial companies outside the consortium were discussed. In this way a close monitoring of the joint dissemination activities were realized as well as the possibility to anticipate to the definition and fine-tuning of near term actions.

Besides the regular consortium meetings, another path that the consortium followed was the internal scientific dissemination. This action aimed at exploiting the REALITY results towards the academic consortium partners in order to advance relevant research in the

Deliverable D8.5 Page 11 of 35

corresponding laboratories of these academic partners and to support their teaching activity through enrichment of the relevant courses or the introduction of new ones.

#### 7.2.3. Communication list

An integral part of the project management has been team organization and communication. The REALITY project team has setup a simple but effective communication list which features all the team member names, their role in the project or function, and their coordinates.

This communication list has been updated and reviewed on a regular base, typically each month

The use of this list obviously enables proper communication among the consortium and to the relevant stakeholders. More importantly it makes sure no valuable information gets lost, stakeholders are informed about project events and the persons responsible for dissemination are clearly identified.

The communication list is available to all the partners via the project wiki page.

#### 7.3. External communication / dissemination

#### 7.3.1. Public Web site

The <u>www.fp7-reality.eu</u> website contains also a Public area that is the official homepage of the project and that serves as a public repository for all project related information.

Figure 2: Recent screenshot of the REALITY web homepage

The web site gives interested users access to a number of public pages providing a description of the project objectives, news, announcement of upcoming events, links to exhibitions where the REALITY project will be represented, contact information and reports or specifications.

Figure 2 provides a recent screenshot of the REALITY web site. In the public area (upper corner at the right hand side) it is clearly visible the announcement of the REALITY workshop held during June 2010 was participants could get access to the latest results of the project. In the same area we make accessible the material presented at the workshop to the public.

The <a href="www.fp7-reality.eu">www.fp7-reality.eu</a> website contains a statistical monitoring function which allows the host to analyse the website traffic. In the course of the project it will help the project team to gain a better view of the interested audience and fine-tune the available information and contents of the website.

Relevant information which is monitored:

- traffic tracking

- amount of page views

- visitors and their geographical location (country of origin)

- the way visitors came to the site

- comparison of traffic per month and intensity

#### 7.3.1.1. Statistical information

This statistical information can be accessed at all times via the following link: http://webstats.motigo.com/stats?AETKZALB7G6GmCZQTm2KB0i8F7cQ

Access statistics of the web site are as follows: The statistics demonstrating the total accesses of the REALITY website have been marked since the 22<sup>nd</sup> of April 2008, and especially after the first ten days of the website's settlement and functionality. The statistics are based on *Motigo Webstats* (<a href="http://webstats.motigo.com">http://webstats.motigo.com</a>). The Motigo Webstats engine is employed to let the external visitors of the Website have access on the visits and the access rates of the website and has been chosen, because, it does not require that the visitor has any username and password in order to demonstrate the web statistics.

In this report, the statistics of the REALITY website accesses are obtained from *Motigo Webstats* engine and they are demonstrated below, in the following figures. The reporting period relates to January 1<sup>st</sup> 2009 till August 30<sup>th</sup> 2010. Records previous to June 2008 have been provided in the first issue of this report (deliverable D8.3).

Deliverable D8.5 Page 13 of 35

### 7.3.1.2. Extra statistical information

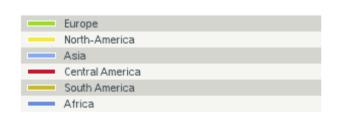

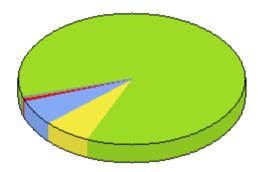

In the two following figures, the screenshots of Motigo Web pages for the REALITY website are shown, for the duration of the reporting period. These figures are given to demonstrate the format of these Web tracking engines and the way of showing the information about the web accesses of a certain website.

### Country of origin

Figure 3: Overview of worldwide website traffic

Figure 4: Table pie of website traffic per continents

Deliverable D8.5 Page 14 of 35

Table 1: Overview of traffic in specific countries worldwide

Figure 5: Table pie of website traffic worldwide

The statistics information given in this paragraph includes the most prevalent metrics, which could let someone have a clear enough picture of the total visit rate during the years 2009 and 2010. The Web tracking engine installed on the website derives several other metrics and features.

On request, this information can be delivered to the REALITY Consortium partners via the common communication channels (via email, wiki or website)

#### 7.3.2. Promotion at exhibitions and conferences

During the first reporting period a multitude of occasions were exploited with the aim to make the start of the REALITY project public and to explain the target objectives to the general public. These actions are a part of a broader dissemination strategy.

The path which was rolled out by the consortium is a mix of dedicated promotion activities combined with key note lectures and presentations at renowned conferences.

The result is clear: the presence of the REALITY project team was observed by a broad audience both general public and specialists. This yields a number of contacts showing interest in the REALITY research topic. On top of this, the start of the REALITY project has been picked up by the press resulting in a variety of press articles.

Exhibitions and conferences fulfil a complementary role as a fast medium for diffusion of results. All the REALITY consortium partners have definitely continued during the reporting period joining exhibitions and with technical presentation as much as possible in order to show the benefits of the developed methodologies and tools with presence at key European Conferences such as DATE.

<u>The Design, Automation, and Test in Europe (DATE)</u> conference is one of the worlds premier conferences dedicated to electronic and embedded systems. It was held at the Acropolis Centre in Nice, France during 20-24 April 2009 and at the International Congress Centre in Dresden, Germany during 8-12 March 2010.

DATE is sponsored by the European Design and Automation Association, the EDA Consortium, the IEEE Computer Society: (TTTC), (CEDA), ECSI, RAS and ACM SIGDA.

### 7.3.3. Organization of training - workshops

The organization of training - workshop actions complements and strengthens the dissemination. The mobilization of resources of REALITY (most of which will be invested in R&D activities) coupled with the expertise of the partners involved, guarantees that innovative technologies in the area of the REALITY project will be created during the execution of the project.

### 7.3.3.1. DATE 2010 Workshop: The Fruits of Variability Research in Europe

With respect to the REALITY FP7 project, a workshop was organized at DATE conference 2010. The conference is sponsored by an impressive list of industrial companies and was an excellent opportunity to disseminate results from the REALITY project to the public and in specific to the representatives of the industrial companies active in this domain.

### Overview of this workshop

This workshop is prompted by the confluence of a recent upsurge in academic interest in the area (for instance, after a special session flagging variability at the 2007 VLSI Technology Symposium, the coverage of variability and associated reliability jumped from a single session in 2008, to three sessions in 2009), significant political backing (Dr Georg Kelm, EU Head of Sector Information Society and Media, is quoted as saying "this is an area of great success for Europe where national and EU funding complement each other"), and because of the presence of a number of EU and UK consortia involved in grants in the area, either starting or presently producing results:

- 2007-10 The UK EPSRC (gow.epsrc.ac.uk/ViewGrant.aspx?GrantRef=EP/E003125/1) design for variability project (Glasgow, Manchester, Southampton, York, Edinburgh Universities)

- 2008-10 REALITY FP7 STREP (www.fp7-reality.eu) on the impact of variability on design (IMEC, KU Leuven, Bologna, ARM, ST)

- 2009-11 EU ENIAC MOdeling and DEsign of Reliable, process variation-aware nanoelectronic devices, circuits and systems (29 EU partners)

Specifically the Workshop covered recent significant results from EU projects and pointed to future research directions. I featured a keynote talk from one of the recognised experts in the field from Asia, and then sessions on: the measurement, simulation and modelling of device variability in today's and end-of-roadmap devices; progress in simulation tools to analyse the effects of device variability on circuit and systems level manufacturability, design, reliability and circuit performance; techniques for creating variability-resilient solutions in circuit and systems design. Also a Poster session, running during coffee and lunch breaks, that gave attendees a focal point for sharing new developments in the field, and future aspects of variability and reliability research and knowledge transfer were discussed in a concluding think-tank session.

Figure 6 shows a snapshot of the DATE 2010 web site announcing its workshop on "The Fruits of variability Research in Europe".

Figure 7 shows the program of the workshop featuring five out of nine speakers who are active team members of the REALITY project, covering different topics of our project: from statistical variability and reliability aware device modelling to system level variability aware design and analysis.

Figure 6 Snapshot of the DATE 2010 web site announcing its workshop on "The Fruits of variability Research in Europe"

### Workshop structure:

| Session 1 – Perspective  09:00 Keynote: Toshiro Hiramoto (University of Tokyo) Variability research: accomplishments and future directions – a Japanese perspective  10:00 Asen Asenov (Glasgow University) Device variability and reliability: towal end of the roadmap.  10:30 Coffee & Poster Session  Session 2 – Simulation strategies and tools  11:00 Scott Roy (Glasgow University) Statistical compact model strategies: efficit bridging the gap between devices and circuits.  11:30 Miguel Miranda (IMEC) Hierarchical, variability aware circuit and system simulation.  12:00 Lunch  Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to synin the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradations resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view  14:30 Coffee & Poster Session |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| accomplishments and future directions – a Japanese perspective  10:00 Asen Asenov (Glasgow University) Device variability and reliability: towal end of the roadmap.  10:30 Coffee & Poster Session  Session 2 – Simulation strategies and tools  11:00 Scott Roy (Glasgow University) Statistical compact model strategies: efficit bridging the gap between devices and circuits.  11:30 Miguel Miranda (IMEC) Hierarchical, variability aware circuit and system simulation.  12:00 Lunch  Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to synin the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                      |        |

| 10:00 Asen Asenov (Glasgow University) Device variability and reliability: towal end of the roadmap.  10:30 Coffee & Poster Session  Session 2 – Simulation strategies and tools  11:00 Scott Roy (Glasgow University) Statistical compact model strategies: efficit bridging the gap between devices and circuits.  11:30 Miguel Miranda (IMEC) Hierarchical, variability aware circuit and system simulation.  12:00 Lunch  Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to synin the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradati resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                        |        |

| end of the roadmap.  10:30 Coffee & Poster Session  Session 2 – Simulation strategies and tools  11:00 Scott Roy (Glasgow University) Statistical compact model strategies: efficient bridging the gap between devices and circuits.  11:30 Miguel Miranda (IMEC) Hierarchical, variability aware circuit and system simulation.  12:00 Lunch  Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to syntin the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                    | ds the |

| Session 2 – Simulation strategies and tools  11:00 Scott Roy (Glasgow University) Statistical compact model strategies: efficient bridging the gap between devices and circuits.  11:30 Miguel Miranda (IMEC) Hierarchical, variability aware circuit and system simulation.  12:00 Lunch  Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to synin the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradations resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                        | us me  |

| Session 2 – Simulation strategies and tools  11:00 Scott Roy (Glasgow University) Statistical compact model strategies: efficient bridging the gap between devices and circuits.  11:30 Miguel Miranda (IMEC) Hierarchical, variability aware circuit and system simulation.  12:00 Lunch  Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to synin the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradations resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                        |        |

| 11:00 Scott Roy (Glasgow University) Statistical compact model strategies: efficient bridging the gap between devices and circuits.  11:30 Miguel Miranda (IMEC) Hierarchical, variability aware circuit and system simulation.  12:00 Lunch  Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to synin the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                      |        |

| bridging the gap between devices and circuits.  11:30 Miguel Miranda (IMEC) Hierarchical, variability aware circuit and system simulation.  12:00 Lunch  Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to syn in the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

| <ul> <li>Miguel Miranda (IMEC) Hierarchical, variability aware circuit and system simulation.</li> <li>Lunch</li> <li>Session 3 – Solutions</li> <li>Andy Tyrrell (University of York) Evolutionary algorithms as an aid to syn in the presence of variability.</li> <li>Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions</li> <li>Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ently  |

| Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to syn in the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| <ul> <li>12:00 Lunch</li> <li>Session 3 – Solutions</li> <li>13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to synin the presence of variability.</li> <li>13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions</li> <li>14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| Session 3 – Solutions  13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to syn in the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradate resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| <ul> <li>Andy Tyrrell (University of York) Evolutionary algorithms as an aid to synin the presence of variability.</li> <li>Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions</li> <li>Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| <ul> <li>13:00 Andy Tyrrell (University of York) Evolutionary algorithms as an aid to synin the presence of variability.</li> <li>13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions</li> <li>14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| in the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| in the presence of variability.  13:30 Georges Gielen (Katholieke Universiteit Leuven) Variability and degradation resilient analogue and digital circuit design: techniques and solutions  14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | thesis |

| resilient analogue and digital circuit design: techniques and solutions 14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| resilient analogue and digital circuit design: techniques and solutions 14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | on     |

| 14:00 Luca Benini (DEIS Università di Bologna) System-level variability countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| countermeasures in many-core computing - a vertically integrated view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| Session 4 – The Future                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| 15:00 Steve Furber (Manchester University) SpiNNaker: a large scale SoC design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | as a   |

| test vehicle for variability modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| 15:30 Enrico Macii (Politecnico di Torino) MODERN, a European flagship proje                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t in   |

| variability and it's impact on design –overview and goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 16:00 Panel Discussion Variability research: Our place in the world? Where next                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •      |

| 17:00 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

Figure 7 Description of the program of the 2010 DATE workshop on "The Fruits of Variability Research in Europe" featuring five out of nine speakers who are active team members of the REALITY project, covering different topics of our project.

A complete overview of this workshop can be found at <a href="http://www.date-conference.com/date10/conference/date10-workshop-W2">http://www.date-conference.com/date10/conference/date10-workshop-W2</a>

Deliverable D8.5 Page 19 of 35

### 7.3.4. Promotional Flyer and Bulletin

A brochure (leaflet) was compiled during the first reporting period containing the key information about the REALITY project: funding, start-end date, consortium partners, objectives, methodologies, benefits and target achievements.

The brochure has been printed and distributed in the different events in which the consortium partners have participated. During the first reporting period the REALITY flyers were distributed at DATE '08 (March 2008, Munich - Germany). During the second and third reporting periods flyers were distributed during the subsequent organizations of such event at Nice in 2009 and Dresden in 2010. In 2010 flyers were also distributed during the

The below figure shows a selected page from the brochure as an example.

### Reliable and Variability tolereant System-on-a-chip Design in More-Moore Technologies

The "REALITY" project activity provides solutions for coping with variability and reliability issues that occur when scaling to and beyond the 32 nm technology node. A system-level solution is provided by focusing on two main axes: Analysis Techniques and Solution Techniques.

This European Community FP7 funded project is the base for a collaboration between major industrial and academic players in this field: ST, ARM, IMEC, Katholieke Universiteit Leuven, Universita di Bologna and University of Glasgow.

#### Scope

- As ministurization of the CMOS technology advances, designers will have to deal with increased variability and character performance of devices, intrinsic variability of devices, which begins to be visible in 65nm devices, already will become much more startificant in smaller technologies. Soon it will not be occurred to dealer systems using current methods and sechniques. Scaline berond the 32 nm technology node brings a number of problems whose impact on dealer has not been evaluated yet. Random intra-discretization problems whose impact on the smaller problems and their combined impact on the system level coarametric quality metrics are becoming prominent issues. Dealing with these new challeness will require an adaptation of the current dealer process: a combination of dealer time and number scholouse and methods will be needed to currents the convect function of Systems on Chio (SoC) over the product's lifetime, despite the fabrication in unreliable nano-scale technologies.

- The objective of this project is to develop design techniques and methods for real-time sugranteed, energy-efficient, polyuet and subfactors and of the control of the contro

### Technological challenges

- Build reliable systems out of unreliable technology while maintaining design productivity.

- How to cope with increased static variability and static fault rates of devices and interconnects during the circuit

and system design phase.

- How to cope with increased time-dependent dynamic variability and dynamic fault rates during the circuit and avation dependence.

- Decloy deaten technology state allow technology scalable energy efficient SoC systems while guaranteeins real-time performance constraints.

REALITY Project Sheet

#### Solutions

- <u>Analysis sechniques</u>: for exploring the design space, and analysing of the system in terms of performance, power

and reliability of manufactured instances across a wide spectrum of operating conditions (thermal, noise, ase).

- <u>Solution techniques</u>: which are design time and/or runtime techniques to mitigate the impact of reliability issues (seen as time-dependent variability aspects) of integrated circuits at component, circuit, architecture and system

www.fp7-reality.eu

Figure 8: The REALITY Brochure

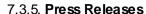

The start of the REALITY project has been noticed and picked-up by the press. Multiple contacts led to several articles. A the end of the project a second press release was lunched reporting the main outcome of the project and this has been widely picked-up by the specialized press. A total number of 19 press release clips echoing the end of project REALITY press release have been identified by October 1<sup>st</sup> 2010, distributed along the three main continents: Europe, America and Asia. With the large majority of them in them concentrated in the US. This reflects the tremendous impact that the project results of REALITY has had in the electronic industry.

One example of such a press announcement can be found http://www.eetasia.com/ART 8800621262 480200 NT af62c44b.HTM

| DATE       | MEDIUM                             | TITLE                                                                                   | K PLACE       |

|------------|------------------------------------|-----------------------------------------------------------------------------------------|---------------|

| 21/09/2010 | EETimes Europe                     | REALITY European project concludes after 2.5 years                                      | Belgium       |

| 23/09/2010 | Industrial Sourcing News           | Project maps ARM core variability at 32-nm                                              | Belgium       |

| 24/09/2010 | EETimes India                      | IMEC-led project characterizes ARM926 core                                              | India         |

| 21/09/2010 | Bits & Chips Online                | Europees consortium rondt project Soc-variabiliteit af                                  | The Netherlan |

| 21/09/2010 | Electronic Specifier               | European project solves variability issues of designing in deep submicron IC technology | UK            |

| 21/09/2010 | New Electronics                    | Project finds way to avoid variability in 32nm cmos designs                             | UK            |

| 21/09/2010 | EETimes News & Analyses            | Project maps ARM core variability at 32-nm                                              | US            |

| 21/09/2010 | Chip design Magazine               | REALITY Consortium Solves Deep Submicron Variability                                    | US            |

| 21/09/2010 | EDA Café                           | European project solves variability issues of designing in deep submicron IC technology | US            |

| 21/09/2010 | Newswire Today                     | European Project Solves Variability Issues of Designing in Deep Submicron IC Technology | US            |

| 21/09/2010 | Global SMT & Packaging             | European project solves variability issues of designing in deep submicron IC technology | US            |

| 21/09/2010 | Semiconductor Packaging News       | Project solves variability issues of designing in deep submicron IC technology          | US            |

| 21/09/2010 | Nanotechnology Now                 | European project solves variability issues of designing in deep submicron IC technology | US            |

| 21/09/2010 | IC Market Place                    | Project maps ARM core variability at 32-nm                                              | US            |

| 22/09/2010 | Electro IQ (Solid State Technology | IC design project concludes on self-adaptive system on chip: Discoveries summarized     | US            |

| 24/09/2010 | Nanotech Wire                      | European project solves variability issues of designing in deep submicron IC technology | US            |

| 21/09/2010 | PR ZOOM                            | European Project Solves Variability Issues of Designing in Deep Submicron IC Technology | US            |

| 21/09/2010 | Nanowerk                           | European project solves variability issues of designing in deep submicron IC technology | US            |

| 22/09/2010 | EETimes Asia                       | "Reality" project characterizes ARM926 for inherent variability at 32nm                 | Asia          |

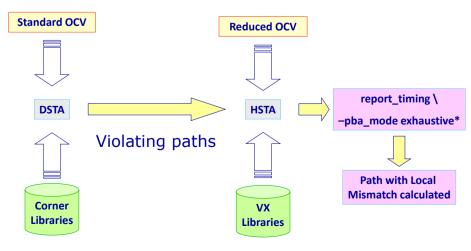

### 7.3.6. Cross reference promotion

### • Cross reference promotion within the REALITY consortium

In order to increase the visibility on the ongoing project research work as well as to increase the traffic to the REALITY website, consortium partners have setup a link from their own website to the project website. In addition to these references, links from other project websites where the REALITY consortium partners participate in have been made to the REALITY URL (e.g. <a href="http://www.nanocmos.ac.uk/essderc/">http://www.nanocmos.ac.uk/essderc/</a>). Where ever possible the REALITY project URL is mentioned in publications, reports and conference presentations.

A search at Google yields:

Figure 9: Cross reference promotion inside & outside the REALITY consortium

The acronym REALITY is a common English word. To maximize the search results, the term "variability project" has to be added. The use of non-existing words as acronym would raise the number of relevant search results. This is an interesting fact for future European projects.

Cross reference promotion outside the REALITY consortium

Search

ådvanced sean

Clear signs of interest for the REALITY research progress have been shown by other project teams (this was very clear during the setup of new projects in this area, e.g. ENIAC initiatives). The REALITY consortium actively pursues to keep a good relation with these other project teams as it may be a potential channel for dissemination and future exploitation. Running activities in this area will be elaborated further in the next reporting periods.

### 7.4. Scientific dissemination

Deliverable D8.5

One of the main vehicles for diffusion of research results is, obviously, to publish in outstanding journals and conferences in the field of interest, appropriate presentations and publications will be encouraged to ensure wide visibility of the project results.

The partners promised to publish papers in conferences and journals of the related field. This promise has been kept. In addition several team members have been invited for keynote speeches and presentations on the topics covered by REALITY. The following summarizes the publications obtained

#### 7.4.1. Publications in conferences

Conferences fulfil a complementary role as a fast medium for diffusion of results. A list of the most relevant conferences in the fields of interest for the project includes: DATE, ESSDERC/ESSCIRC, IEDM and IEEE International Symposium on Quality Electronics Design. All these conferences are targeted by all partners in order to show the benefits of the developed methodologies and tools.

- C. Forzan and D. Pandini, "Statistical Static Timing Analysis: A Survey," Integration, the VLSI Journal, vol. 42, pp. 409-435, Jun. 2009.

- D. Pandini, "Statistical Static Timing Analysis: A New Approach to Deal with Increased Process Variability in Advanced Nanometer Technologies."

- Intl. Conf. on CMOS Variability (ICCV), May 2009.

- Paul Zuber, Petr Dobrovolny, Vladimir Matvejev, Philippe Roussel and Miguel Miranda, "Using Exponent Monte Carlo for Quick Parametric Yield Prediction of CMOS Circuits under Process Fluctuations", 19th International Workshop on Power And Timing Modeling, Optimization and Simulation (PATMOS), Springer, 2009

- Miranda Corbalan, M.; Dierickx, B.; Zuber, P.; Dobrovolny, P.; Kutscherauer, F.; Roussel, P. and Poliakov, P., Variability aware modeling of SoCs: from device variations to manufactured system yield, International Symp. On Quality Electronic Design, San Jose, USA, 2009.

- Zuber, P.; Miranda Corbalan, M. and Dobrovolny, P., "Statistical Memory Analysis for SRAM Design", 2<sup>nd</sup> IEEE Design for Reliability and Variability Workshop, Austin, TX, USA, 2009

- Francesco Paterna, Luca Benini, Andrea Acquaviva, Francesco Papariello, Giuseppe Desoli, Mauro Olivieri: Adaptive idleness distribution for non-uniform aging tolerance in MultiProcessor Systems-on-Chip. DATE 2009: 906-909

- Francesco Paterna, Luca Benini, Andrea Acquaviva, Francesco Papariello, Giuseppe Desoli: Variability-tolerant workload allocation for MPSoC energy minimization under real-time constraints. ESTImedia 2009: 134-142

- Root Causes and Impact of Random Variability in Advanced Technologies Yves Laplanche - ARM Global Engineering Conference - 5-8 May 2009 - Loughborough -UK

- Analyze of Temporal and Random Variability of a 45nm SOI SRAM Cell Y. Laplanche - International SOI Conference - 5-8 October 2009 - Crowne Plaza Hotel, Foster City, California, USA

- E.Maricau and G.Gielen, "Efficient Reliability Simulation of Analog ICs Including Variability and Time-varying Stress", DATE proceeding 2009.

- E.Maricau and G.Gielen, "A Methodology for Measuring Transistor Ageing Effects Towards Accurate Reliability Simulation", IOLTS proceedings 2009.

- G. Paci, D. Bertozzi, L. Benini, Effectiveness of adaptive supply voltage and body bias as post-silicon variability compensation techniques for full-swing and low-swing on-chip communication channels, in Design, Automation & Test in Europe Conference & Exhibition, DATE 2009.

- Sathanur, A. Pullini, L. Benini, G. De Micheli, E. Macii, Physically clustered Forward Body Biasing for variability compensation in nano-meter CMOS design, in Design, Automation & Test in Europe, DATE 2009.

- Asenov, Variability Headaches in Sub-32 nm CMOS, ECS Trans. Vol. 25, p. 131 (2009)

- B. Cheng, S. Roy, A.R. Brown, C. Millar, A. Asenov, Evaluation of statistical variability in 32 and 22nm technology generation LSTP MOSFETs, Solid-State Electronics, Volume 53, Issue 7, pp.767-772 (2009)

- M. F. Bukhori, A. R. Brown, S. Roy and A. Asenov, Simulation of Statistical Aspects of Reliability in Nano CMOS Transistors, IEEE Trans. Reliability (Accepted)

- E. Maricau and G. Gielen, "Variability-aware reliability simulation of mixed-signal ICs with quasi-linear complexity", DATE, pp.1530-1591, 2010.

- E. Maricau and G. Gielen, "Efficient variability-aware NBTI and hot carrier circuit reliability analysis", IEEE Transactions on Computer Aided Design, vol.29, no.12, 2010.

- A. R. Brown, V. Huard and A. Asenov, "Statistical simulation of progressive NBTI degradation in a 45nm technology pMOSFET", IEEE Trans. on Electron Devices, Vol.57, No.9 pp.2320-2323 (2010)

- A. R. Brown, N. M. Idris, J. R. Watling and A. Asenov, "Impact of Metal Gate Granularity on Threshold Voltage Variability: A Full-Scale 3D Statistical Simulation Study", IEEE Electron Device Letters, (in press)

- F. Paterna, A. Acquaviva, A. Caprara, F. Papariello, G. Desoli, L. Benini, "Variability-tolerant run-time workload allocation for MPSoC energy minimization under real-time constraints", ACM Conf. Computing Frontiers, pp. 109-110 (2010)

- Francesco Paterna, Andrea Acquaviva, Alberto Caprara, Francesco Papariello, Giuseppe Desoli, Luca Benini: Variability-tolerant run-time workload allocation for MPSoC energy minimization under real-time constraints. Conf. Computing Frontiers 2010: 109-110

- Selma Laabidi, Advanced Variability Analysis from devices to systems ARM Global Engineering Conference - 4th-7th May 2010 - Loughborough – UK

Deliverable D8.5 Page 24 of 35

### 7.4.2. Workshops, seminars, tutorials and Keynotes

Regarding section 7.3.3, academic project members have made efforts to advance the research in the area in the laboratories of the academic partners (as promised) and beyond. Toward this end, the partners have actively held tutorials and presented keynotes. The following is a list of keynotes and tutorials for the first reporting period:

- Concerning invited presentations, Miguel Miranda, project coordinator gave an overview of the project status of REALITY on his talk: *Design for Variability Efforts in Europe REALITY project* at the 2<sup>nd</sup> NMI International Conference on CMOS Variability: ICCV 2009, Wednesday, 13<sup>th</sup> May 2009 in London-UK (<a href="http://www.nmi.org.uk/conference/index.html">http://www.nmi.org.uk/conference/index.html</a>)

- A. Asenov, Statistical variability and reliability in next generation CMOS technologies and the ITRS response. 2<sup>nd</sup> NMI International Conference on CMOS Variability: ICCV 2009, Wednesday, 13<sup>th</sup> May 2009 in London-UK (<a href="http://www.nmi.org.uk/conference/index.html">http://www.nmi.org.uk/conference/index.html</a>)

- A. Asenov, Statistical variability: a roadblock to future scaling (How the statistical variability is shaping the ITRS) Proc. INSIGHT 2009, pp 309-316 (2009) Invited

- A. R. Brown, "TCAD simulation of statistical variability" at Workshop on Simulation and Characterization of Statistical CMOS Variability and Reliability, Bologna (September 2010)

- A. Asenov, Modelling and Simulation of Transistor and Circuit Variability and Reliability, IEEE CICC, San Jose (September 2010).

- A. Asenov, Interaction between TCAD, compact models and circuit simulation to support statistical and robust design " at Workshop on Simulation and Characterization of Statistical CMOS Variability and Reliability, Bologna, (September 2010)

- A. Asenov, Advanced Monte Carlo Techniques in the Simulation of CMOS Devices and Circuits, 7th Int. Conf. Numerical Methods and Algorithms, Borovetz, Bulgaria (August 2010)

- A. Asenov, SINANO Summer School, Bertionoro, Italy (July 2010)

- A. Asenov, Statistical variability in conventional and modern CMOS devices 1, UPC, Barcelona (July 2010)

- A. Asenov, Statistical reliability in conventional and modern CMOS devices 2, UPC, Barcelona (July 2010)

- A. Asenov, Statistical Variability and Corresponding Compact Model Strategies, COMON Compact Model Training Course, Taragona (June 2010)

- A. Asenov, Statistical variability and reliability, TSMC (April 2010)

- A. Asenov, Variability Prediction via TCAD Tools, VLSI-DAT Workshop, Taiwan (April 2010)

- A. Asenov, Modelling and simulation of statistical variability in nanometer CMOS technology, AACD'10, Graz (March 2010)

- A. Asenov, Forever CMOS, UKDF, Manchester (March 2010).

- A. Asenov, Statistical variability and reliability: Physical device simulation, statistical compact model strategy, statistical circuit simulation, GLOBALFOUNDRIES, Dresden (March 2010).

- A. Asenov, Modelling perspective of future n-channel high-mobility transistors, ULIS, Glasgow (March 2010)

- A. Asenov, Device variability and reliability: towards the end of the roadmap, DATE, Dresden (March 2010)

- Davide Pandini, Statistical Static Timing Analysis: A New Approach to Deal with Increased Process Variability in *Europe – REALITY project* at the Advanced

Nanometer Technologies, 2<sup>nd</sup> NMI International Conference on CMOS Variability: ICCV 2009, Wednesday, 12<sup>th</sup>-13<sup>th</sup> May 2009 in , London-UK (<a href="http://www.nmi.org.uk/conference/index.html">http://www.nmi.org.uk/conference/index.html</a>) (invited)

- D. Pandini, "Variability in Advanced Nanometer Technologies: Challenges and Solutions," (Keynote Speech) PATMOS, Sep. 2009.

- D. Pandini, "Computing and Design for Silicon Manufacturing," *HIPEAC Cluster Meeting*, Jan. 2009.

- D. Pandini, "Statistical Static Timing Analysis: A New Approach to Deal with Increased Process Variability in Advanced Nanometer Technologies," *Intl. Conf. on CMOS Variability (ICCV)*, May 2009.

- D. Pandini, "Variability in Advanced Nanometer Technologies: Challenges and Solutions," (Keynote Speech) *PATMOS*, Sep. 2009.

- D. Pandini, "Variability in Advanced Nanometer Technologies: Challenges and Solutions," (Keynote Speech) *VARI*, May 2010.

- D. Pandini, "Variability in Advanced Nanometer Technologies: Challenges and Solutions," SINANO, Jul. 2010.

- G. Gielen, Elie Maricau, Pieter De Wit, Design for Reliability of Analog Circuits in Nanometer CMOS Technology, Reliability and Design Conf., Stuttgart, 2009 (invited)

#### 7.4.3. Education

Again relating to training activities R&D team members have actively been involved in courses related to the topic of the project. The following courses were held by the partners:

### IM EC:

P.Zuber, P.Dobrovolny, M.Miranda IDESA lecture on Statistical SRAM Analysis, May 3<sup>rd</sup> 2010, IMEC

### 8. Final Use Plan (exploitation strategy)

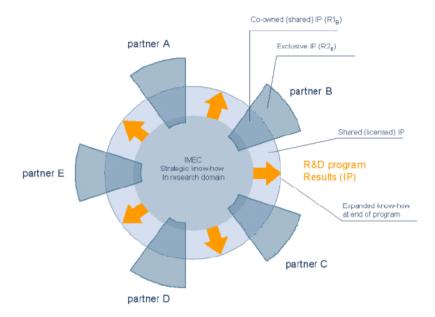

The objective of defining the exploitation strategy is to identify the results from the project that can be used or exploited by partners. Therefore, an initial analysis has been assessed on the exploitable results. Based on these results, possible exploitation strategies have been defined. Both the academic and industrial partners have been instrumental in using the methodologies and tools developed during the project course.