## REALITY

# Reliable and Variability tolerant System-on-a-chip Design in More-Moore Technologies

### Contract No 216537

## **Deliverable D7.6**

## **Annual project progress report (Year 2)**

Editor: Miguel Miranda

Co-author: Andrea Acquaviva, Asen Asenov,, Luca Benini, Andrew

Brown, Binjie Cheng, Wim Dehaene, Giuseppe Desoli, Georges Gielen, Virgile Javerliac, Selma, Laabi, Yves

Laplanche, Davide Pandini, Scott Roy, Paul Zuber

Status - Version: V1.2

Date: 22/03/2010 Confidentiality Level: Public

ID number: IST-216537-WP7-D7.6

#### © Copyright by the REALITY Consortium

#### The REALITY Consortium consists of:

| Interuniversity Microelectronics Centre (IMEC vzw) | Prime Contractor | Belgium        |

|----------------------------------------------------|------------------|----------------|

| STMicroelectronics S.R.L. (STM)                    | Contractor       | Italy          |

| Universita Di Bologna (UNIBO)                      | Contractor       | Italy          |

| Katholieke Universiteit Leuven (KUL)               | Contractor       | Belgium        |

| ARM Limited (ARM)                                  | Contractor       | United Kingdom |

| University Of Glasgow (UoG)                        | Contractor       | United Kingdom |

Deliverable D7.6 Page 2 of 69

### 1. Disclaimer

The information in this document is provided as is and no guarantee or warranty is given that the information is fit for any particular purpose. The user thereof uses the information at its sole risk and liability.

## 2. Acknowledgements

## 3. Document revision history

| Date       | Version | Editor/Contributor                                                                                                                                                                                              | Comments                                                                                                                           |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 26/0/2010  | V0.1    | Miguel Miranda                                                                                                                                                                                                  | First draft                                                                                                                        |

| 11/02/2010 | V0.2    | Andrea Acquaviva, Asen Asenov,, Luca Benini, Andrew Brown, Binjie Cheng, Wim Dehaene, Giuseppe Desoli, Georges Gielen, Virgile Javerliac, Yves Laplanche, Miguel Miranda, Davide Pandini, Scott Roy, Paul Zuber | partners for the different<br>technical WPs (WP1, WP2,<br>WP3, WP4, WP5, WP6,<br>WP8). WP7 and financial                           |

| 25/02/2010 | V0.3    | Andrea Acquaviva, Asen Asenov,, Luca Benini, Andrew Brown, Binjie Cheng, Wim Dehaene, Giuseppe Desoli, Georges Gielen, Virgile Javerliac, Yves Laplanche, Miguel Miranda, Davide Pandini, Scott Roy, Paul Zuber | information in Sections 15 and                                                                                                     |

| 4/03/2010  | V1.0    | Miguel Miranda                                                                                                                                                                                                  | Full version including project management sections                                                                                 |

| 22/3/2010  | V1.1    | Miguel Miranda                                                                                                                                                                                                  | Update of Section 15 with the list of the people involved in the project and their function (those who claim for personnel costs). |

| 24/3/2010  | V1.2    | Miguel Miranda                                                                                                                                                                                                  | Corrected inconsistencies found in Tables 7, 8 and 10 (marked in yellow to highlight the changes made)                             |

Deliverable D7.6 Page 3 of 69

#### 4. Preface

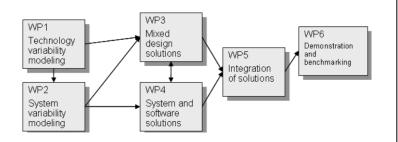

The scope and objectives of the REALITY project are :

• Development of design techniques, methodologies and methods for real-time guaranteed, energy-efficient, robust and adaptive SoCs, including both digital and analogue macro-blocks"

#### The Technical Challenges are:

- To deal with increased static variability and static fault rates of devices and interconnects.

- To overcome increased time-dependent dynamic variability and dynamic fault rates.

- To build reliable systems out of unreliable technology while maintaining design productivity.

- To deploy design techniques that allow technology scalable energy efficient SoC systems while guaranteeing real-time performance constraints.

#### Focus Areas of this project are:

- "Analysis techniques" for exploring the design space, and analysis of the system in terms of performance, power and reliability of manufactured instances across a wide spectrum of operating conditions.

- "Solution techniques" which are design time and/or runtime techniques to mitigate impact of reliability issues of integrated circuits, at component, circuit, architecture and system (application software) design.

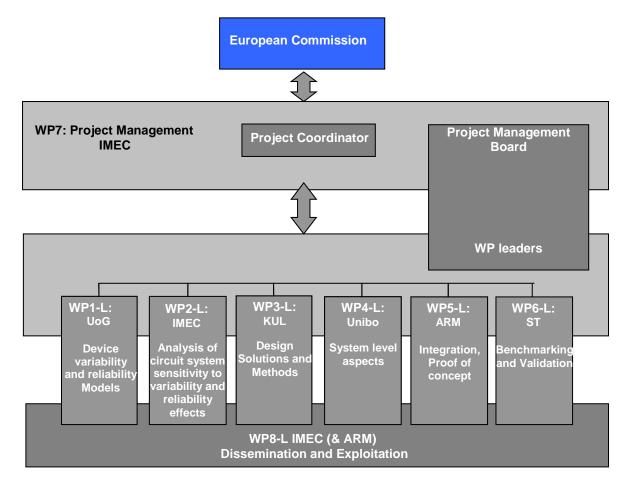

The REALITY project has started its activities in January 2008 and is planned to be completed after 30 months. It is led by Dr. Miguel Miranda of IMEC. The Project Coordinator is Dr. Miguel Miranda from IMEC. Five contractors (STM, ARM, KUL, UoG, UNIBO) participate in the project. The total budget is 2.899 k€

Deliverable D7.6 Page 4 of 69

## 5. Abstract

This report is deliverable 7.6: "Annual project progress report". The reporting period is from M13 until M19. Hence it covers roughly the first semester of project execution after the first review meeting.

Deliverable D7.6 Page 5 of 69

## 6. List of Abbreviations

| REALITY | Reliable and Variability tolerant System-on-a-chip Design in More-Moore |  |  |  |  |

|---------|-------------------------------------------------------------------------|--|--|--|--|

|         | Technologies                                                            |  |  |  |  |

| CAD     | computer aided design                                                   |  |  |  |  |

| DSP     | digital signal processing                                               |  |  |  |  |

| HW      | Hardware                                                                |  |  |  |  |

| IC      | integrated circuit                                                      |  |  |  |  |

| SoC     | system on chip                                                          |  |  |  |  |

| SW      | Software                                                                |  |  |  |  |

|         |                                                                         |  |  |  |  |

|         |                                                                         |  |  |  |  |

|         |                                                                         |  |  |  |  |

Deliverable D7.6 Page 6 of 69

| 7. List of Tables                                                                                                                                                            |                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Table 1. Standard deviation values for DVth and Db parameters                                                                                                                | 20                                |

| Table 2 Execution time of the optimized LP version and BP algorithms for an increasing nu                                                                                    |                                   |

| processors and tasks                                                                                                                                                         | 37                                |

| Table 3 List of planned Deliverables for Year 2                                                                                                                              |                                   |

| Table 4 List of planned Milestones for Year 2                                                                                                                                |                                   |

| Table 5: Update of the DoW version 2.5 (May 2009)                                                                                                                            |                                   |

| Table 6: Update of the DoW version 3.4 (December 2009)                                                                                                                       |                                   |

| Table 7: Summary of changes with respect to the original project plan for period 2                                                                                           |                                   |

| Table 8: Overview of project meetings                                                                                                                                        |                                   |

| Table 9: List of deliverables submitted to the EC                                                                                                                            |                                   |

| Table 10 List of Deliverables with actual modifications with respect to the DoW existing at the beginning 2                                                                  | _                                 |

| period 2                                                                                                                                                                     | 63                                |

| 8. List of Figures                                                                                                                                                           |                                   |

|                                                                                                                                                                              |                                   |

| Figure 1. A normal probability plot of the threshold voltages, VT of 200 microscopically different                                                                           | 45nm p-                           |

| channel devices. Plots for devices with no traps, and with trap sheet densities of 1×10 <sup>11</sup> cm <sup>-2</sup> , 5×                                                  | 10 <sup>11</sup> cm <sup>-2</sup> |

| and 1×10 <sup>12</sup> cm <sup>-2</sup> , are shown. The inset shows experimental results for a similar device from STM.                                                     | 17                                |

| Figure 2. A normal probability plot of the increase in threshold voltages, $\Delta VT$ , of 200 microscopically                                                              | different                         |

| 45nm p-channel devices when trapped charge is introduced at the Si/SiO2 interface. Plots for                                                                                 |                                   |

| with trap sheet densities of 1×10 <sup>11</sup> cm <sup>-2</sup> , 5×10 <sup>11</sup> cm <sup>-2</sup> and 1×10 <sup>12</sup> cm <sup>-2</sup> are shown. The inse           |                                   |

| experimental results for a similar device from STM.                                                                                                                          |                                   |

| Figure 3. Hole concentration in one particular microscopically different p-channel device that                                                                               |                                   |

| random dopants and LER (a) with and (b) without additional trapped charges with a sheet de                                                                                   |                                   |

| 5×10 <sup>11</sup> cm <sup>-2</sup> . Acceptors are shown in blue and donors in red, while trapped charges are green.                                                        |                                   |

| concentration surface is included, and the surface plot above shows the hole concentration in                                                                                |                                   |

| through the channel                                                                                                                                                          |                                   |

| Figure 4 Distribution of threshold voltages for 200 devices (a) each with a different gate grain par                                                                         |                                   |

| different average grain diameters, and (b) with each of the three individual sources of v                                                                                    |                                   |

| considered here (MGG, RDD and LER) and also with all three sources combined. For the final                                                                                   |                                   |

| all sources combined, 10,000 devices have been simulated                                                                                                                     |                                   |

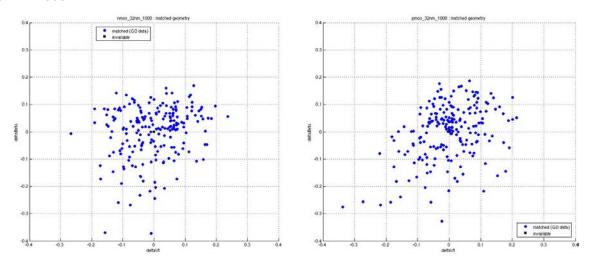

| Figure 5: The random variations (D V <sub>th</sub> , Db) of <i>nfet</i> and <i>pfet</i> type transistors (extracted from the family curves coming from atomistic simulation) |                                   |

| Figure 6 SSTA (GOLDTIME) vs. Monte Carlo (ELDO MC\)                                                                                                                          |                                   |

| Figure 7. Timing path in CMOS065LP technology                                                                                                                                |                                   |

| Figure 8 Device mismatch impact on path delay                                                                                                                                |                                   |

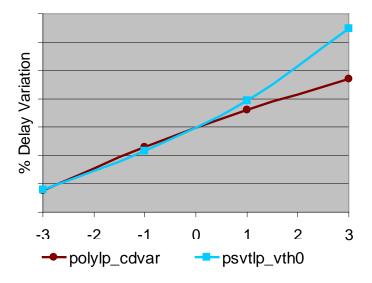

| Figure 9 Poly CD and threshold voltage non-linearity                                                                                                                         |                                   |

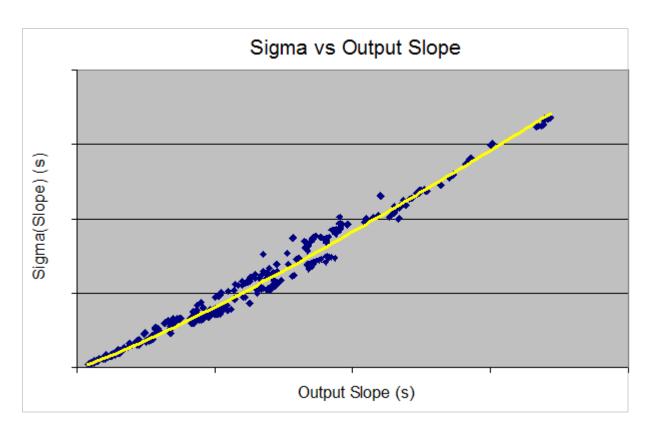

| Figure 10. Output slope variation trend                                                                                                                                      |                                   |

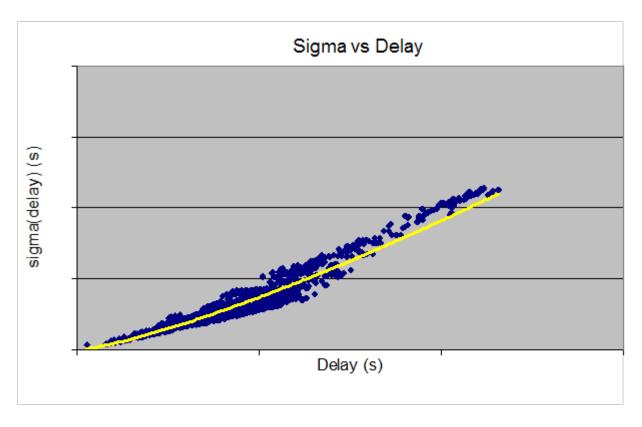

| Figure 11. Propagation delay variation trends                                                                                                                                |                                   |

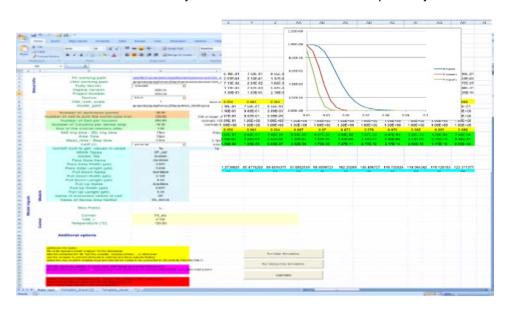

| Figure 12: Snapshots of the "push button" margining                                                                                                                          |                                   |

| Figure 13 Hybrid statistical analysis flow                                                                                                                                   | 27                                |

| Figure 14: The islands definition for the KUL 32kbit SRAM memory                                                                                                             |                                   |

| Figure 15 Ddistribution of energy consumption for different memory parts of the designed memory                                                                              |                                   |

| Figure 16 Execution time vs energy consumption per cycle.                                                                                                                    | 37                                |

| Figure 17 Task allocation policy applied to the MPEG2 benchmark                                                                                                              | 38                                |

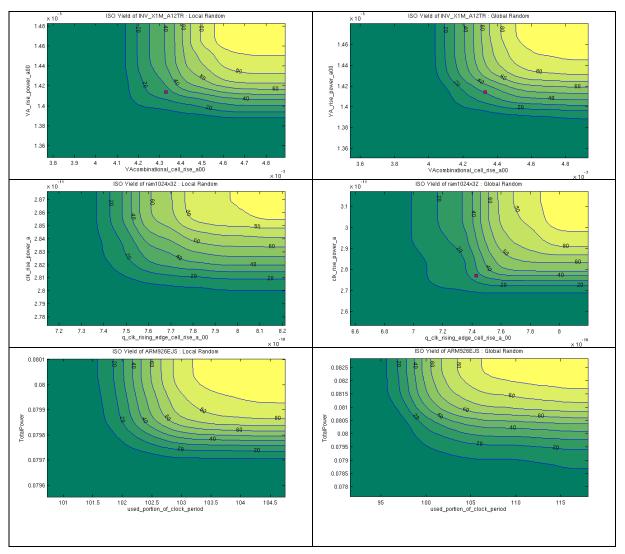

| Figure 18: Variability as ISO-Yield MAP for: small gate (TOP), memory (MIDDLE), Processor (BOTTO                                                                             | OM) 43                            |

| Figure 19 REALITY project team and coordination                                                                                                                              |                                   |

## 9. Table of contents

| 1.          | DISCLAIMER                                                                                                                                                                                                                                                                                    | 2                    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2.          | ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                              | 2                    |

| 3.          | DOCUMENT REVISION HISTORY                                                                                                                                                                                                                                                                     | 2                    |

| 4.          | PREFACE                                                                                                                                                                                                                                                                                       | 3                    |

| 5.          | ABSTRACT                                                                                                                                                                                                                                                                                      |                      |

| 6.          | LIST OF ABBREVIATIONS                                                                                                                                                                                                                                                                         |                      |

| 7.          | LIST OF TABLES                                                                                                                                                                                                                                                                                |                      |

| 8.          | LIST OF FIGURES                                                                                                                                                                                                                                                                               |                      |

| 9.          | TABLE OF CONTENTS                                                                                                                                                                                                                                                                             |                      |

| ə.<br>10.   |                                                                                                                                                                                                                                                                                               |                      |

|             |                                                                                                                                                                                                                                                                                               |                      |

| 11.<br>DE   | SIGN IN MORE-MOORE TECHNOLOGIES"                                                                                                                                                                                                                                                              |                      |

| 12.         | WORK PROGRESS AND ACHIEVEMENTS DURING THE PERIOD                                                                                                                                                                                                                                              | 17                   |

| 1           | 12.1. WP1: Device variability and Reliability Models (WP leader: UoG)                                                                                                                                                                                                                         | 21<br>29<br>34       |

|             | 12.6. WP6: VALIDATION AND ASSESSMENT OF RESULTS (WP LEADER: ST)                                                                                                                                                                                                                               | 42                   |

| 13.         | ,                                                                                                                                                                                                                                                                                             |                      |

| 14.         | PROJECT MANAGEMENT                                                                                                                                                                                                                                                                            | 52                   |

|             | 14.1. CONSORTIUM MANAGEMENT TASKS AND ACHIEVEMENTS;                                                                                                                                                                                                                                           | 53                   |

| 1           | 14.2.2. Status of the 32nm data set – history of developments                                                                                                                                                                                                                                 | 56                   |

| 1<br>1<br>1 | 14.4. LIST OF PROJECT MEETINGS, DATES AND VENUES IN PERIOD 2:         14.5. IMPACT OF DEVIATIONS MATERIALIZED FROM THE PLANNED MILESTONES AND DELIVERABLES         14.6. DEVELOPMENT OF THE PROJECT WEBSITE:         14.7. USE OF FOREGROUND AND DISSEMINATION ACTIVITIES DURING THIS PERIOD: | 60<br>62<br>64<br>64 |

| 1<br>15.    | 14.8. COORDINATION ACTIVITIES COMMENT – KEY MESSAGE :                                                                                                                                                                                                                                         |                      |

| 1<br>1      | 15.1. ST MICROELECTRONICS                                                                                                                                                                                                                                                                     | 64<br>65<br>66       |

|             | 15.4. Katholieke Universiteit Leuven                                                                                                                                                                                                                                                          |                      |

Deliverable D7.6 Page 8 of 69

| 15.6 | 6. ARM                                                     | . 68 |

|------|------------------------------------------------------------|------|

| 16.  | FINANCIAL STATEMENTS – FORM C AND SUMMARY FINANCIAL REPORT | . 68 |

| 17   | CERTIFICATES                                               | 69   |

Deliverable D7.6 Page 9 of 69

#### PROJECT PERIODIC REPORT

Grant Agreement number: 216537

Project acronym: REALITY

Project title: "Reliable and Variability tolerant System-on-a-chip Design in More-Moore Technologies"

Funding Scheme: Collaborative project (STREP)

Date of latest version of Annex I against which the assessment will be made:

Periodic report:  $1^{st} \square 2^{nd} X 3^{rd} \square 4^{th} \square$

Period covered: from 01/01/2009 to 31/12/2009

Name, title and organisation of the scientific representative of the project's coordinator:

Dr. Miguel Miranda

Tel: +32 16 281 524

Fax: +32 16 28 1515

E-mail: Miguel.Miranda@imec.be

Project website address: http://www.fp7-reality.eu/

Deliverable D7.6 Page 10 of 69

#### 10. Declaration by the scientific representative of the project coordinator

I, as scientific representative of the coordinator of this project and in line with the obligations as stated in Article II.2.3 of the Grant Agreement declare that:

- The attached periodic report represents an accurate description of the work carried out in this project for this reporting period;

- The project has fully achieved its objectives and technical goals for the period;

- The public website is up to date, if applicable.

- To my best knowledge, the financial statements which are being submitted as part of this report are in line with the actual work carried out and are consistent with the report on the resources used for the project and if applicable with the certificate on financial statement.

- All beneficiaries, in particular non-profit public bodies, secondary and higher education establishments, research organisations and SMEs, have declared to have verified their legal status. Any changes have been reported under section 15 (Project Management) in accordance with Article II.3.f of the Grant Agreement.

Name of scientific representative of the Coordinator: Miguel Miranda Corbalan

Date: 15/02/2010

Signature of scientific representative of the Coordinator

#### Miguel Miranda

Senior Scientist TU-SSET-DC - Group

Phone: +32 16 28 15 24 / Fax: +32 16 28 15 15

E-mail:Miguel.Miranda@imec.be / Skpye: miguel.miranda.imec

Deliverable D7.6 Page 11 of 69

## 11. Publishable summary: "Reliable and Variability tolerant System-on-a-chip Design in More-Moore Technologies"

## **Project Facts:**

• FP7 Project : European Community funded

Coordination : IMEC

Website: www.fp7-reality.eu

• Duration : 30 Months

• Effort: 382 person-months

Industry: ARM (UK), ST Microelectronics (Italy)

• Start date: 1st January 2008

University: Glasgow (UK), Bologna (Italy), Leuven (Belgium)

Research Centre : IMEC (Belgium)

## Scope:

Scaling beyond the 32 nm technology

Tackle the increased variability and changing performance of devices from device unto system level.

Random discrete dopants in a 35 nm MOSFET from the present 90 nm technology node.

## **Challenges:**

- Increased static variability and static fault rates of devices and interconnects.

- Increased time-dependent dynamic variability and dynamic fault rates.

- Build reliable systems out of unreliable technology while maintaining design productivity.

- Deploy design techniques that allow technology scalable energy efficient SoC systems while guaranteeing real-time performance constraints.

## Proposed solution:

- System analysis of performance, power, yield and reliability of manufactured instances across a wide spectrum of operating conditions.

- Generally applicable solution techniques to mitigate the impact of reliability issues of integrated circuits, at component, circuit, and architecture and system design.

Deliverable D7.6 Page 12 of 69

#### WP1: Device variability and Reliability Models (WP leader: UoG)

Task T1.1.1 (Validation and calibration against 45 nm technology generation devices) was completed and reported in 2008. This year's efforts have been focused on tasks T1.1.2 (started in 2009) and tasks T1.2.1, T1.2.2, T1.3.1, T1.3.2 and T1.3.3 already started in 2008.

#### T1.1.2 Simulation of variability in 32 nm technology generation devices.

An NDA was signed on 9/4/2009 to allow transfer of 32nm TCAD data from ST to UoG with the 4-way agreement being signed on 15/5/2009. The TCAD data was transferred to UoG on 28/04/2009. UoG has introduced the provided doping profiles into their simulator and calibrated the simulations against the provided I-V curves. UoG has performed simulations to investigate the variability in threshold voltage due to random discrete dopants and line edge roughness. A new source of variability (workfunction variation due to metal gate granularity) has also been included in the simulator for the first time. Full  $I_{D^-}V_G$  characteristics for both n- and p-channel devices, at high and low drain voltage, have been simulated. Ensembles of 200 devices that differ due to random discrete dopants, line edge roughness and metal gate granularity have been used.

#### T1.2.1 Statistical simulation of the impact of fixed/trapped charges.

Simulation of the impact of fixed/trapped charges in 45nm devices was completed and reported in 2008. Further analysis of the simulation results was performed in early 2009 and the results have been submitted for publication in IEEE Transactions on Electron Devices. The equivalent work for 32nm devices will be performed at the start of 2010.

#### T1.2.2 Modelling of time dependent variation:

Simulation models for NBTI, HCD and SDB: this was completed and reported in 2008.

Variability aware method to incorporate reliability effects (NBTI, HCD and/or SBD) in transistor level netlists: This task goal is a modelling technique to include reliability effects in a variability aware transistor level model of any given circuit with the goal of simulating the combined impact of static variability and reliability. The inputs are the extracted variability injectors from 3.3 and the simulation models for reliability defined the previous year in 2.2

#### T1.3.1 Statistical compact model parameter sets.

45nm statistical compact models were delivered by UoG and reported in 2008. Due to differences in release number between the 32nm compact model supplied by STM and the TCAD simulation data to which the UoG simulator was calibrated, a different approach has been adopted for the 32nm devices. UoG have provided the  $I_D$ - $V_G$  characteristics from T1.1.2 to IMEC who have extracted variability injectors that can be used in the provided STM compact models. This allows other partners to use compact models with variability without violating the NDA between STM and UoG on the supply of device information.

#### T1.3.2 Extraction of key statistical parameters.

More physically based compact models, such as PSP, will allow the extraction of key parameters which could have geometry dependent statistical distributions: UoG has developed a statistical extraction strategy for PSP.

#### T1.3.3 Extraction of variability injectors

Method and tool flow to extract Vt and beta variations from I-V curves (device DC transfer characteristics): Application of extraction flow to ST 45nm data was completed and reported in 2008. Application of extraction flow to ST 32nm data to extract Vt and beta variations from I-V curves provided by UoG (based on the low-level technological information received from ST) has been done in 2009 and variability injectors have been provided to project partners.

Deliverable D7.6 Page 13 of 69

#### WP2: System and circuit characterization and sensitivity analysis (WP leader: IMEC)

Although it might be considered a straightforward task, statistical library characterization is a critical showstopper to the adoption of statistical analysis and optimization techniques in industrial digital flows. ARM has kept on developing with his EDA partner the characterization tool capable of generating a CCSA-VA liberty file with a high accuracy. A good correlation between analysed variability and Monte Carlo simulation was finally achieved. A 80 cell library has been characterized and will be evaluated on a system level design. In parallel, ST developed and validated a practical, yet accurate technique to reduce the mismatch characterization time during the reporting period. It is based on the simultaneous identification of the transistors impacting the cell performances, on the reduction of the characterization grid size, and on the identification of a restricted set of transistor parameters that largely impact on the device performances, since it would not be feasible to consider all the parameters present in typical transistor compact models.

While industry support exists for library characterization of standard cells, entirely new ways have to be gone for non-standard cells. ARM developed a push button tool for the designers to easily apply the read current characterization, based on spreadsheet tables and SPICE. In parallel, implications of Silicon-on-Insulator (SOI) technology on variability are investigated. KUL has prepared a memory for use in imec's MemoryVAM characterization tool.

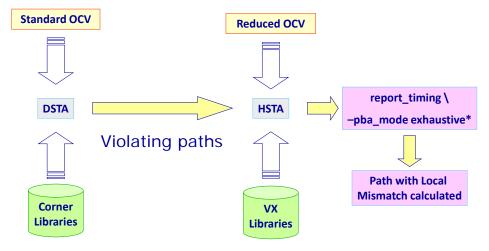

On digital block level, ST introduced its new hybrid approach. A traditional DSTA based on corners is carried out using the tools currently available in the digital sign-off flow. After DSTA, ST considers the critical paths violating the timing constraints and also those paths that are "potentially" critical, i.e., whose timing slack are very small and subject to the detrimental impact of process variability. During this analysis, OCVs are taken into account by means of derating factors (which can be overly pessimistic as it was demonstrated during the previous WP2 activities). After selecting the critical/violating paths, on one side ST reduces the OCV margins (based on process variability data) and also carries out a path-based SSTA (HSTA) based on the statistical libraries described earlier. Following this approach it is possible to remove timing violations without taking unnecessary margins.

Imec has continued to implement and verify the technique to translate IP-level variability to System-level variability. The electronic Information Format (IF) that imec develops to exist parallel to the classical top-down and bottom-up design flow is continuously extended in order to cope with advanced information like block-level-sensitivity data.

#### WP3: Mixed mode countermeasures (WP leader: KUL)

The work of KUL between M13 and M24 has focused on task T3.2.

Task T3.2 has been divided into two sections: a first section extends the work done in T3.1 to include variability awareness to the reliability simulation of electronic circuits. In a second section, this knowledge is used to design a variability/reliability-resilient memory IP block.

A. Variability and degradation phenomena demand the use of novel design techniques, e.g. Knobs & Monitors, to guarantee optimal performance over a specified lifespan. A nominal reliability simulation methodology is used in combination with a variability-aware framework to maintain simulation accuracy while taking process variations into account. The methodology has been demonstrated effectively, but efficiency can still be improved in the coming months.

B. The design of a memory IP-block has been carried out as a case study to develop and validate variability-aware and low-power design methodologies for a state-of-the-art memory. To be able to cope with variability, statistical behavioural models are required. In this way the number of design loop iterations between the architectural and the circuit level can be reduced. The techniques that have been studied in this work are: (fully) divided word and bit lines, charge recycling, asymmetric sense amplifier redundancy, low swing techniques, etc. This work has temporarily been halted due to the lack of 32nm device models, which has caused serious delays and personeffort underspending. Part of this task has also been done collaboratively by IMEC, who set up the VAM environment and ran the statistical characterization flow on the KUL SRAM memory.

Deliverable D7.6 Page 14 of 69

Since the work in this task has not yet been completed due to the delay and personeffort underspending as discussed above, KUL will continue and finalize this work by extension of Task T3.2 into June 2010. The completion of this work is also essential to support the activities in WP6. KUL will report this extended work in an updated version D3.2b of the Deliverable D3.2.

The work of UNIBO between M13 and M24 has focused on T3.4, and more specifically analyzing variability effects on on-chip communication and developing techniques for compensating for them and supporting runtime adaptation and variability management. The analysis has identified on-chip communication links (and more specifically Network-on-chip links) as critical components to be analyzed and protected by adequate countermeasures, based on Adaptive body bias (ABB) and adaptive supply voltage (ASV), which have been identified in T3.3 as effective methods for post-silicon tuning to reduce variability on generic combinational circuits or microprocessor circuit sub-blocks. The results have been reported in D3.3 (delivered on time at M12).

#### WP4: System level countermeasures (WP leader: UNIBO)

The work performed by UNIBO until M18 was focused on Task 4.1, 4.2, 4.3 and 4.4 (in collaboration with ST). The first two tasks (results are reported in D4.1 – delivered on time at M9) allowed to build the software infrastructure for the development of variability countermeasures developed in Task4.3 (results are reported in D4.2 – delivered on time at M18).

Main activities related to Task4.3 have been:

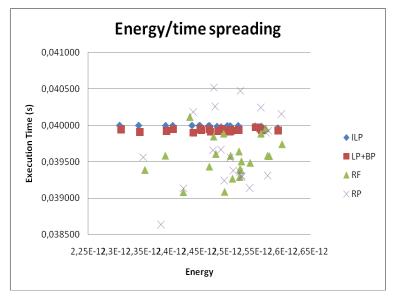

- 1. Definition of the problem of task allocation under variability effects to minimize energy under time constraints. We devised an Optimal solution with Integer Linear Programming. It is very slow and suitable for off-line validation. We then developed a sub-optimal solution based on Linear Programming and BinPacking, which is suitable for implementing task allocation at startup time. Finally, we developed an approximate solution based on a Look-up Table, which is much faster and allows online implementation.

- 2. Development of a theoretical solution and its implementation on the simulation platform that has been enhanced with power and variability models as part of WP5

- 3. Refinement of the task model (independently, barrier synchronized tasks representative of embarrassingly parallel computation like as done in video processing algorithm)

- 4. Comparison against state-of-the-art policies: Rank Power/Rank Freq

- 5. Analysis of compensation capabilities using VAM-generated variability affected platforms.

The activity about Task 4.4 started in collaboration with ST. In particular, UNIBO is currently working on the optimization of the policies on the target multicore platform, provided by ST and on the target validation benchmarks defined in WP6, for which UNIBO is also performing the porting to the simulation platform as part of WP6.

The activity performed by UNIBO during the period M19-M24 in WP4 was focused on the completion of Task 4.4, concerning the optimization of the system level countermeasures for the specific hardware platform defined in WP5 and the benchmarks to be used for evaluation in WP6. More specifically, the activities have been:

- The development of an optimized online version of the variability-aware task allocation policy exploiting a new formulation of Linear Programming problem that can be solved during application execution. This optimization is needed for the implementation of the task allocation policy on multimedia applications on a frame-by-frame basis.

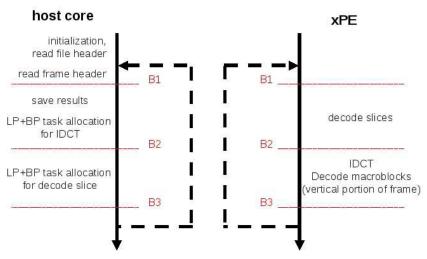

- 2. The analysis of the impact of variability on the performance and energy consumption of multimedia applications, namely on the MPEG2 video decoder benchmark from ST (WP6). The application is parallelized so that some functions (i.e. IDCT and Decode Slice) are performed by various cores at the same time. This analysis provided information about the impact of speed and power consumption variations among the different cores on the energy and deadline miss rate.

- 3. The implementation of the optimized variability-aware allocation policy on the target platform running the MPEG2 video decoding benchmark.

Deliverable D7.6 Page 15 of 69

More details and results related to this activities will be reported in D4.3 due on M27.

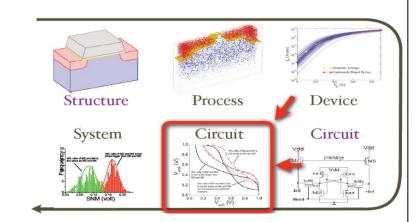

#### WP5: Design flow, integration, proof of concept (WP leader: ARM)

This Work Package coordinates and carries out the evaluation of the different project components. It is the place where the components of the project come together and will involve developing methodologies and test platforms to enable the evaluation to take place. It is responsible for assessing the severity of the uncompensated situation, and quantifying the improvements that result from the application of techniques identified in other Work Packages. It is also responsible for identifying the techniques that prove to be unsuccessful (and why), as well as to point to other techniques that might be worth investigation (beyond this project).

In a first phase we defined the system platforms and the IP blocks in which we will evaluate the developed techniques. Some initial developments on the xSTream and the ARM system platforms have already started in the first period.

The second period has seen a ramping up of the integration activity. The flow integration started on the first period on several cells has been extended to a full library. The work has been focused on the VAM flow from IMEC. A 32nm library composed of 80 cells is used as bases of the validation work. A full variability analysis has been performed on this library. Thanks to the deployment of a Research Island inside ARM a strong cooperation on the variability analysis of the VAM flow was undertaken. IMEC could hereby get access to the ARM926 design and the 32nm library.

In the scope of the variability characterization a ARM memory critical path has been characterized for different memory cut sizes. One size was chosen to perform a benchmarking of memory design coming out from the WP3 developments. Memory VAM was also applied to the memory developed by KUL.

The ALU of the ARM926 was chosen as the test vehicle for the Active Body Biasing scheme evaluation. UniBO started the adaptation of its methodology using a 45nm library provided by ST. The 32nm library, including back biasing information, became available at the end of the period allowing testing this technique on the 32nm node as well.

On the xSTream platform an important effort has been spent in the development of the simulation infrastructure of the system level design. An adaptation of an in house flexible model has been done in order to be able to simulate the xSTream processor and the xPE IP blocks including variability information. The variability impact seen on the system will be modelled by the "back of the envelop" approach proposed by UniBo. This approach is based on equation providing the relationship between corner variations and the system performances. A calibration of the variability information will be done using the VAM information on the ARM926. In order to account for the variability information at the system level during the simulation, specific adaptations of the software infrastructure had to be made.

Finally a monitoring system has been integrated to the xSTream platform. The system is based on a library component: Monitoring Micro IP. The information coming out from the IP can be accessed either by a Process Monitoring block which controls the knobs on the system or directly read out during the testing of the system.

This second period has seen a lot of activity in this work package. Most of the integration work has been done and is described in the delivery D5.3 which paves the path to the assessments done in WP6.

#### WP6: Validation and assessment of results (WP leader: ST)

This work package is the place were most of the results, methodologies, flows, IPs developed and/or leveraged in the other work packages come together for validating the project's goal of "build reliable systems with unreliable components".

The WP tasks are designed to validate and assess the project results through the benchmarking of individual IP blocks along with the identification and porting of a set of industrially relevant applications. The general focus is the leverage of IPs and applications along with their integration and mapping onto the integrated application platform developed with contributions from WP3,4,5. The output of the work package is the evaluation both in terms of NRE, final product cost, and in general advantages over the uncompensated case, of the benefit stemming from the methodologies, techniques and components developed by the project.

During the last six months of the second year of execution of WP6 activities, the work has progressed mainly for tasks T6.4, T6.5.1 and T6.5.2, allocation of resources to task has been aligned to expected levels from

Deliverable D7.6 Page 16 of 69

the DoW. Tasks T6.2 and T6.3 have been completed during the first six months of this year and reported in the previous Periodic Activity Report.

In the context of WP6 validation tasks, as reported in the last Periodic Activity Reports, the partners of REALITY have agreed to validate the technologies and methodologies developed with two separated flows for the multimedia (STM) and general purpose (ARM) platform components.

The ARM926 test case has been applied towards the validation and benchmarking of both variability aware circuits and design and analysis flows; the process was driven by the availability of 32nm silicon technology data complemented by advanced variability analysis techniques at the atomistic level and up to devices, standard cell libraries, circuits and memories and whole netlists.

The major output of the period is the release of the report associated to D5.3; in this report are detailed many of the validation and benchmarking activities and results carried out by the partners on the different IPs and analysis flows deployed in the project.

For the multimedia scenario, a suitably defined simulation platform based on the REALITY platform definition tasks of WP5 has been made available. Such simulation platform provides a set of parallel media acceleration engines from STM (called xPEs) and an STM proprietary host processor, ST231, supporting Linux and a suitable run-time environment for the accelerators.

#### Objectives for the period 2, Project M13 until M24

The reporting Period 2 covers the project time-schedule M13 until M24, i.e. starting from 1<sup>st</sup> January 2009 until 31<sup>st</sup> December 2009. This report is a mid year progress report for such period.

Description of the performance / research indicators (all targets for Y2 have been met!)

| Description of the           | he performance / research ind                                                                                                                                                                  | icators (all targets for Y2 have                                                                                                                                                                        | e been met!)                                                                                                              |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| WP                           | After year 1                                                                                                                                                                                   | After year 2                                                                                                                                                                                            | At end of project                                                                                                         |

| WP1<br>Device<br>variability | Physical modeling and understanding of the variability at 45/32 nm technology nodes (TN). First statistical compact models.                                                                    | Compact models that accurately capture the variability and the reliability issues at 32 nm.                                                                                                             | Models fine tuned. Feedback from device measurements incorporated.                                                        |

|                              | Preliminary version of a RDR std. cell library [32nm]. Flow definition and framework set up for variability characterization. Correlated variability energy timing flow definition and set up. | Variability characterization of a [32nm] RDR std cell library. Exploitation of the variability aware modelling flow on the driver application vehicle, including a solution for IP blocks and memories. | Methodology fine tuned. Feedback from benchmarking acknowledged.                                                          |

| WP3<br>Mixed design          | Description of the variability and reliability analysis methods at circuit level                                                                                                               | Demonstration of the developed method on SRAM and analog circuits                                                                                                                                       | Validation of the developed method                                                                                        |

| WP4<br>Algorithm             | Software techniques for flexible data and workload allocation for migration (the base flexible RTSM support)                                                                                   | Control algorithms for system level reliability and variability management (exploiting of the base RTSM support)                                                                                        | Porting, optimization and tuning for the target evaluation platform of: (a) the flexible RTSM, (b) the control algorithms |

| WP5<br>Integration           | Definition of characterization blocks, macrocells, and system level architecture                                                                                                               | Validation and application of methods to macrocells and integration into system                                                                                                                         | Final system integration, validation feeding into WP6 benchmarking                                                        |

| WP6<br>Benchmarking          | Identification of relevant industrial applications and associated requirements and evaluation metrics                                                                                          | Definition of the validation plan Benchmarking of block level IPs                                                                                                                                       | Benchmarking of system level platform Evaluation of results and impact according to validation plan criteria              |

Deliverable D7.6 Page 17 of 69

#### 12. Work progress and achievements during the period

#### 12.1. WP1: Device variability and Reliability Models (WP leader: UoG)

Note: In this work package there is data that has been provided by STM to UoG and covered under the NDA between these two parties, e.g. device structures and TCAD I-V characteristics which will not be shown hereby.

Due to the initial unavailability of the 32nm structure information and TCAD simulation results, further investigation of reliability in the 45nm devices was done. Most device reliability problems are associated with generation of fixed charges or the trapping of electrons and/or holes in defect states in the gate stack during circuit operation. Using experimental data for the stress dependence of the average density of the stress generated charge and defect states, and their spatial positions, we had carried out a detailed 3D simulation of the statistical distribution of the corresponding changes in device characteristics due to microscopic manifestations of particular device defect configurations.

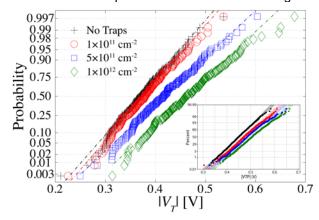

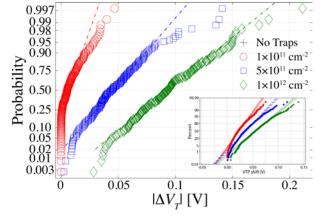

Figure 1. A normal probability plot of the threshold voltages, VT of 200 microscopically different 45nm p-channel devices. Plots for devices with no traps, and with trap sheet densities of 1×10<sup>11</sup>cm<sup>-2</sup>, 5×10<sup>11</sup>cm<sup>-2</sup> and 1×10<sup>12</sup>cm<sup>-2</sup>, are shown. The inset shows experimental results for a similar device from STM.

Figure 2. A normal probability plot of the increase in threshold voltages,  $\Delta VT$ , of 200 microscopically different 45nm p-channel devices when trapped charge is introduced at the Si/SiO2 interface. Plots for devices with trap sheet densities of  $1\times10^{11} \text{cm}^{-2}$ ,  $5\times10^{11} \text{cm}^{-2}$  and  $1\times10^{12} \text{cm}^{-2}$  are shown. The inset shows experimental results for a similar device from STM.

The fresh devices include random discrete dopants (RDD) and line edge roughness (LER). The threshold voltages are extracted, based on a current criterion, and their distribution for the fresh devices is plotted with black crosses in Figure 1. Three different levels of NBTI degradation are investigated corresponding to positive interface charge densities of  $1\times10^{11}$  cm<sup>-2</sup>,  $5\times10^{11}$  cm<sup>-2</sup> and  $1\times10^{12}$  cm<sup>-2</sup>, and Figure 1. also shows the threshold voltage distributions corresponding to these three different charge densities. Apart from the average increase in the threshold voltage associated with NBTI degradation in large transistors, a marked change in the slope of the distribution is observed in Figure1, indicating an increase in the spread with the increase in trap density. Figure 1 also clearly indicates that the threshold voltage distributions are not strictly Normal (which would present as a straight line on the plot), and the departure from normality is larger in the tails. For each of the 200 devices simulated, the change in  $V_T$  as a result of the NBTI degradation is shown on a normal probability plot in Figure 2 for the same three levels of degradation. For low trap sheet density ( $1\times10^{11}$  cm<sup>-2</sup>) there are many devices that show no increase in threshold voltage at all. In these cases the traps (if there are any) are not occurring at locations within the channel where there is significant current flow, as dictated by the distribution of discrete impurities.

Deliverable D7.6 Page 18 of 69

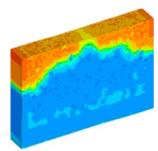

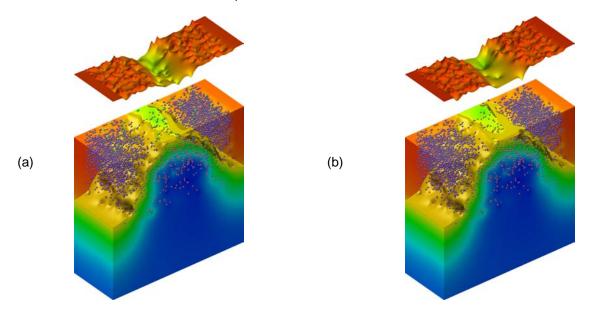

Figure 3 illustrates results of the simulation of one particular microscopically unique pMOSFET that includes random dopants and LER (a) without and (b) with additional trapped charges. Both the colour mapped hole concentration and the positions of the random dopants are shown (acceptors in blue, donors in red). One iso-concentration surface is included providing a clear visual impression of the non-uniform channel formation due to the discrete random dopants and LER.

Figure 3. Hole concentration in one particular microscopically different p-channel device that includes random dopants and LER (a) with and (b) without additional trapped charges with a sheet density of 5×10<sup>11</sup>cm<sup>-2</sup>. Acceptors are shown in blue and donors in red, while trapped charges are green. One iso-concentration surface is included, and the surface plot above shows the hole concentration in a sheet through the channel.

On  $28^{th}$  April 2009, STM provided UoG with the Technology Computer-Aided Design (TCAD) data for the IBM 32nm low power devices. This consisted of device structure files (compatible with the Synopsys Sentaurus simulation package), which provided device geometry and doping profiles, and also  $I_D$ - $V_G$  characteristics. Further clarification of specific material parameters was also provided when requested.

UoG has introduced the provided device structures into the UoG 'atomistic' device simulator. The profiles of each dopant species are mapped onto the simulation mesh used by the simulator, and saved as doping files to be read in upon execution of the simulator. The next step was to run the simulator to produce  $I_D$ - $V_G$  characteristics at low and high drain voltage and calibrate the simulations to match the TCAD simulation results provided by STM. This is done by adjusting parameters in the mobility models (such as the saturation velocity) to obtain the correct current levels, and the metal gate workfunction can be adjusted to match the threshold voltage. The mobility models used are a doping concentration dependent model to account for ionised impurity scattering, a perpendicular electric field model to account for surface roughness scattering and a longitudinal electric field model to account for velocity saturation. Good agreement between the UoG simulator and the provided current-voltage characteristics has been obtained for both n- and p-channel devices.

Deliverable D7.6 Page 19 of 69

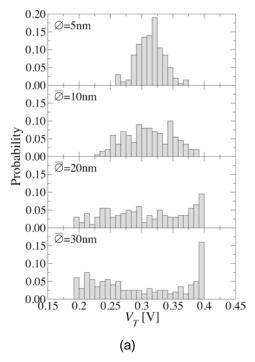

Once the simulator has been calibrated to match the provided data, the different sources of variability that are important for this particular bulk MOSFET technology can be introduced. For both the n- and p-channel devices the sources included are random discrete dopants (RDD), line edge roughness (LER) and workfunction variation due to metal gate granularity (MGG). As a preliminary investigation, simulations to calculate the variability in the threshold voltage were performed including different sources of variability, alone and in combination. The UoG 'atomistic' simulator has been modified as part of this project to include MGG for the first time. This allowed the impact of MGG to be estimated, as this source of variability had not previously been examined. The effect of the average diameter,  $\overline{\varnothing}_{\underline{\centerdot}}$  of the grains in the gate was investigated, looking at the change in  $V_T$  distribution and  $V_T$  variability. It was observed that  $\sigma V_T$  increases with increasing grain size and starts to saturate as the average grain diameter approaches the dimensions of the channel. Figure 4a presents the  $V_T$  distributions for different  $\overline{\varnothing}$  showing that the distributions are bounded by the threshold voltages corresponding to the two different workfunctions that can occur in the TiN gate. Figure4b presents the distributions for different sources of variability showing that the spread in  $V_T$  due to MGG is as large as that due to random dopants. It is also clear that the  $V_T$  distribution with all sources is not Gaussian, and making the assumption that it is could affect the validity of, for example, statistical circuit and timing simulations.

Figure 4 Distribution of threshold voltages for 200 devices (a) each with a different gate grain pattern, for different average grain diameters, and (b) with each of the three individual sources of variability considered here (MGG, RDD and LER) and also with all three sources combined. For the final case of all sources combined, 10,000 devices have been simulated.

Following discussions with STM it was decided to use an average grain diameter for the gate material taken from literature (22nm). This produced very close to the same  $\sigma V_T$  as published data for IBM 32nm technology giving confidence in the results of the simulator. Then full  $I_D$ - $V_G$  characteristics for ensembles of 200 'atomistically' different devices were simulated, for both n- and p-channel devices at high ( $V_D$ =1.0V) and low ( $V_D$ =0.05V) drain voltage.

Deliverable D7.6 Page 20 of 69

On obtaining the 32nm process design kit (PDK) from STM it was found that the I-V characteristics obtained from Spice simulations with the PDK did not closely match those supplied from the TCAD simulations to which the UoG simulator had been calibrated due to the difference in release number between the PDK SPICE models and the TCAD data that has been transfer to UoG. If UoG were to extract compact models directly from the variability simulations these would not be consistent with the compact models in the PDK being used by the other project partners. An alternative method for the propagation of variability information from the device models to the circuit level was proposed and agreed upon. STM agreed that UoG may provide the I-V characteristics from their device simulations to IMEC who would extract *variability injectors* which can be incorporated into any compact modelling strategy. In this way the variability obtained from the UoG simulations can be included within statistical circuit simulations based on the STM 32nm PDK while at the same time providing a level of abstraction from the original information provide by STM to UoG under the NDA.

IMEC extracted variability injectors from two sets of  $I_{\rm d}$ - $V_{\rm gs}$  curves (atomistic simulations) provide by UoG. UoG built atomistic transistor models based on the low-level technological information provided by ST and performed 200 atomistic simulations for nmos and pmos-type transistors each. IMEC applied the s2v (statspice to VAM) tool implementing extraction methodology and derived statistical populations (D $V_{\rm th}$ , Db) for random variations. Figure 5 shows the results for *nfet* - n-type MOSFET model – and *pfet* - p-type MOSFET model.

Figure 5: The random variations (D $V_{th}$ , Db) of *nfet* and *pfet* type transistors (extracted from the family of  $I_{cl}/V_{cs}$  curves coming from atomistic simulation)

IMEC analysed variability clouds extracted from UoG atomistic simulation data. Table 1 summarise the results for random process variations. It shows the standard deviation values of  $DV_{th}$  and Db for two basic transistor models - *pfet* and *nfet* – having minimal size (w=32nm, t=32nm).

|                  | sigma DV <sub>th</sub> | <b>sigma</b> Db |

|------------------|------------------------|-----------------|

| nfet (nmos type) | 9.04382E-02            | 9.65812E-02     |

| pfet (pmos type) | 9.05554E-02            | 1.00704E-01     |

Table 1. Standard deviation values for DVth and Db parameters

Because the UoG atomistic model and simulations take care of process variation sources at the atomistic level and also add some additional variation sources not included in the statistical compact spice model of ST, the standard deviation values are expected and reasonable.

IMEC has made the variability injectors available to project partners so they can be used in statistical circuit simulations.

#### Use of resources

Deliverable D7.6 Page 21 of 69

| Partner | Planned effort (MM) | Actual effort (MM) |

|---------|---------------------|--------------------|

| UOG     | 12                  | 39.6(*)            |

| IMEC    | 4.4                 | 4.4                |

| UNIBO   | 0                   | 0                  |

| ST      | 2                   | 2.35               |

| KUL     | 0                   | 0                  |

| ARM     | 0.2                 | 0.2                |

| TOTAL   | 18.6                | <i>46.55(*)</i>    |

(\*) The actual number of PMs for UoG is much higher than planned because UoG had to develop the methodology for simulation of metal grain variability which was not envisaged at the beginning of the project. Therefore we had to deploy significant additional manpower. This became possible due to the favorable exchange rate for the Euro and by deploying PhD students at lower rate than a normal research associate. The additional man power was also used to explorer in details the accuracy of different compact model strategies that will be reported in the next deliverable.

### 12.2. WP2: System and circuit characterization and sensitivity analysis (WP leader: IMEC)

This section describes the status of all WP2-related activities.

#### Task 2.1: Development and characterization of a standard cell library under variability impact

- <u>Objective</u>: To develop analysis and simulation techniques for statistical characterization of standard cell libraries;

- Input: Transistor-level netlist of each standard cell to be characterized;

- Output: Techniques for statistical characterization of a standard cell library.

Deliverable D7.6 Page 22 of 69

ARM has kept on developing with his EDA partner the characterization tool capable of generating a CCSA-VA liberty file with a high enough accuracy. A good correlation between analysed variability and Monte Carlo simulation was finally achieved. A 80 cell library has been characterized and will be evaluated on a system level design. The main remaining issue in the field is the validation of the characteristics of a complex cell, especially flip-flops which characterization is incompatible with the traditional Monte-Carlo methodology applied in HSPICE.

For ST, in the reporting period the statistical characterization of device random mismatch for industrial standard cell libraries in ST's CMOS065LP (65nm low-power) technology has progressed in line with the plans. For device mismatch characterization, ideally every single transistor should be exposed to characterization, thus introducing a larger characterization time that given the typical size of industrial standard cell libraries has rapidly become unaffordable. Therefore, speed-up techniques are mandatory to reduce the characterization runtime.

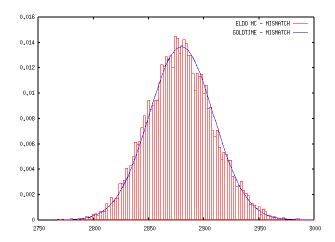

Figure 6 SSTA (GOLDTIME) vs. Monte Carlo (ELDO MC\)

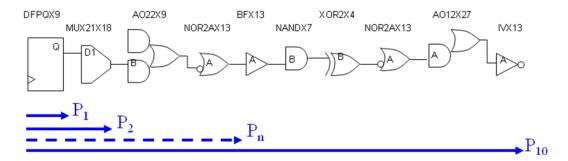

Figure 7. Timing path in CMOS065LP technology

A practical, yet accurate, technique to reduce the mismatch characterization time that was developed and validated during the reporting period, is based on the simultaneous identification of the transistors impacting the cell performances, on the reduction of the characterization grid size, and on the identification of a restricted set of transistor parameters that largely impact on the device performances, since it would not be feasible to consider all the parameters present in typical transistor compact models. The parameters that confirmed the most significant impact on cell delay were the threshold voltage and mobility.

Deliverable D7.6 Page 23 of 69

The approach developed for random mismatch characterization was validated by comparing statistical static timing analysis (SSTA) against transistor-level Monte Carlo analysis on several path delays extracted from industrial digital blocks in CMOS065LP technology designed at ST. The experimental results reported in Figure 6 demonstrate an excellent agreement between SSTA and Monte Carlo analysis, thus validating the proposed technique for mismatch statistical characterization.

Furthermore, a design-level analysis on the extracted timing paths was performed. The statistical timing analysis carried out on the timing path depicted in Figure 7 are reported in Figure 8, and demonstrate that mismatch is impacting only short paths, since for longer paths the random nature of device mismatch cancels out.

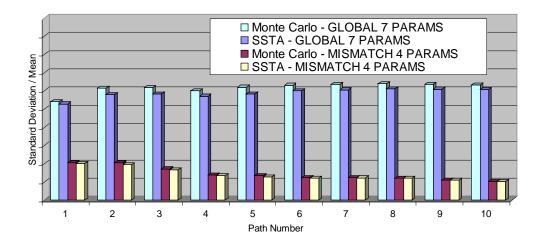

Figure 8 Device mismatch impact on path delay

Again, the statistical analysis performed both on global parameters and on mismatch parameters shows an excellent correlation with respect to Monte Carlo analysis, thus validating our approach.

The statistical characterization performed in CMOS065LP was also extended to CMOS045LP (45nm low-power) technology, which is today the most advanced CMOS nanometer technology in production, and the same characterization methodology and flow were used. An important factor to be considered is the non-linear dependence of cell delay on process variations, which was characterized in CMOS045LP. Poly CD, as well as threshold voltage, exhibits a non-linearity (more significant in PMOS devices) as shown in Figure 9. Poly CD non-linearity was known in CMOS065LP, but threshold voltage was observed in CMOS045LP, likely due to large deviations coupled with low voltage and temperature.

Other cell timing characteristics were analyzed. In particular, we considered the propagation delay and output slope, whose behavior against process variability are reported in Figure 10 and Figure 11 respectively, where both propagation delay and output slope variations for different timing arcs (~2900) of various standard cells with different driving strengths follow a well-defined trend vs. delay and slope values, for a given voltage and temperature condition.

Deliverable D7.6 Page 24 of 69

Figure 9 Poly CD and threshold voltage non-linearity

We also analyzed the impact of device mismatch in CMOS045LP, with the same approach validated for CMOS065LP. With the increase in the number of stages along the delay path, the sigma/mean ratio follows a similar relationship to what was observed in CMOS065LP.

Finally, statistical characterization was also performed on standard cell libraries in CMOS045, exploiting commercial tools currently available in the ST design flow. In particular, local mismatch libraries were generated around the corners:

- "Slow-Slow" min VDD;

- "Fast-Fast" max VDD.

Liberty-NCX tool was used to perform this characterization. The tool contains smart algorithms to avoid running a full Monte Carlo analysis, since as it was demonstrated from the activity in CMOS065LP, that many simulations for a single slew/load pair are needed, and consequently the characterization runtime is too large. As a result, the statistical characterization runtime was drastically reduced and with respect to deterministic library characterization, the overall overhead was significantly less than 4X.

Deliverable D7.6 Page 25 of 69

Figure 10. Output slope variation trend

Figure 11. Propagation delay variation trends

Deliverable D7.6 Page 26 of 69

The statistical libraries thus obtained are currently under exploitation for the statistical timing analysis of digital blocks and SoCs.

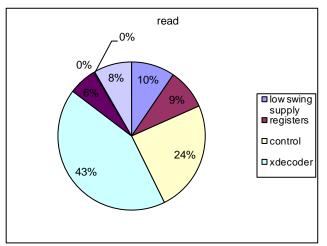

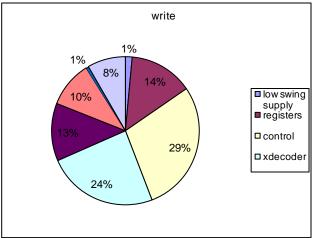

#### Task 2.2: Statistical Characterization of Macro-Blocks

The memory created for D3.2 was adapted and prepared to be tested by the MVAM tool. Test benches were created to test energy use, memory delay and setup and hold time for the data input. The work necessary to prepare the memory was larger then it should be. A few reasons for this can be given. 1) The memory had to be shrunk to 1/8 of its original size (from 8KB to 1KB) making it suboptimal. This had to be done to make a more fair comparison with the ARM memory. 2) More fundamental, the MVAM tool uses sliced netlists (netlists in which idle components are cut to reduce computational overhead). Making a correct sliced netlist for a complex memory is far from trivial. 3) To increase simulation speed, memory access cycles used to set bit data, precharge voltages etc. and replaced by complex initial conditions, which have to be added manually. 4) Energy calculations on sliced netlist are particularly difficult to implement as energy multiplication factors differ from subcircuit to subcircuit and are different for active and leakage power. KUL will continue this work in 2010 to make the comparison with the current ARM solution possible.

The characterization of memory blocks using the Extreme Value Statistics has first been adapted to the write margin issue. A methodology has been defined to evaluate the worst case of the traditional static write margin scheme. Since our office is also focusing on SOI technology, we developed new dynamic techniques to find the real worst case write margin taking into account SOI effects. To achieve this goal a monitoring of the body potential is done and re-injected in the simulations after then. The technique has been applied for first test on a 45nm bitcell. In the meantime transient simulations schemes have also been investigated to accurately imitate the behaviour of the cells during the actual usage in read and write mode.

In the read mode, for example a simple worst case cell has been modelled using the previously extracted Extreme Values distribution. The accuracy of this simulation has not been proven yet.

Figure 12: Snapshots of the "push button" margining

In parallel a push button tool has been developed for the designers to easily apply the read current characterization. The tool is based on an XL file which contains all the necessary simulation information for the simulation. Once the spice simulation is completed the output data are loaded and the Extreme Value distribution is automatically fit.

From these data a Yield curve with different scenarios are shown to the designer. Despite this interface effort designers are reluctant to use this methodology since the mathematical background appears too heavy and they find the traditional sigma parameters they were using for ages.

Deliverable D7.6 Page 27 of 69

#### Task 2.3: Hybrid (corner/statistical) Statistical Analysis flow of for Digital Blocks

- Objective: To develop an innovative yet practical solution for statistical analysis and process variability

evaluation of large SoC designs in advanced nanometer technologies and targeted towards industrial

exploitation;

- <u>Input</u>: Statistical standard cell library, gate-level netlist of digital blocks. Industrial standard cell corner libraries; industrial STA tools, derating factors (for on-chip variations, i.e., OCV), device compact models and process parameter variations;

- Output: Statistical timing information of the digital block, critical path, and statistical information for average/worst-case timing. Statistical libraries with local device mismatch, reduced OCVs, hybrid statistical analysis flow.

Statistical analysis solutions for random within-die (WID) variations available today are quite complex for an effective industrial exploitation. Most approaches for WID variations are focused on systematic mismatch, which can be ameliorated by means of manufacturing-driven improvements (regularity, restricted design rules, resolution enhancement techniques). In REALITY we demonstrated that Statistical Static Timing Analysis (SSTA) is a good estimator of random WID variations, but in general, it lacks ease of deployment in an industrial environment, and requires a lot of efforts to characterize the statistical libraries, as it was demonstrated with the work previously carried out in WP2. Moreover, it also true that chip designers in an industrial environment, who have to satisfy tough turn-around-time requirements, and have to meet strict time-to-market windows dictated by an increasingly fierce competition, do not want to change the traditional sign-off methodology for timing verification based on deterministic static timing analysis.

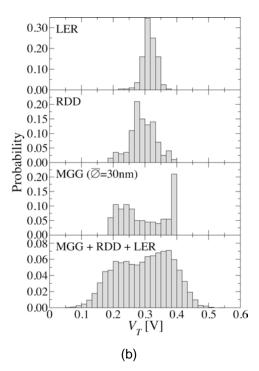

Figure 13 Hybrid statistical analysis flow