# Model-based Analysis & Engineering of Novel Architectures for Dependable Electric Vehicles

Report type Deliverable D3.2.1

Report name Analysis and Synthesis Concepts

**Supporting Engineering Scenarios**

Dissemination level PU

Status Intermediate (2nd iteration)

Version number 2.0

Date of preparation 2012-10-04

## **Authors**

Editor E-mail

Martin Walker @hull.ac.uk

**Authors** E-mail

Martin Walker Martin.Walker@hull.ac.uk Sandra Torchiaro Sandra.Torchiaro@crf.it

DeJiu Chen chen@md.kth.se

Tahir Naseer tnqu@md.kth.se

Mark-Oliver Reiser Mark-Oliver.Reiser@tu-berlin.de

David Parker

D.J.Parker@hull.ac.uk

Henrik Lönn

David Servat

David.Servat@cea.fr

Nidhal Mahmud

N.Mahmud@hull.ac.uk

Reviewer E-mail

Andreas Abele Andreas.Abele@continental-corporation.com

## **The Consortium**

Volvo Technology Corporation (S) Centro Ricerche Fiat (I)

Continental Automotive (D) Delphi/Mecel (S) 4S Group (I)

MetaCase (Fi) Pulse-AR (Fr) Systemite (SE) CEA LIST (F)

Kungliga Tekniska Högskolan (S) Technische Universität Berlin (D) University of Hull (GB)

# Revision chart and history log

| Version | Date       | Reason                                                   |

|---------|------------|----------------------------------------------------------|

| 0.1     | 2010-12-01 | Initial outline.                                         |

| 0.9     | 2011-05-09 | Final draft                                              |

| 1.0     | 2011-05-27 | Final review                                             |

| 1.0.1   | 2011-07-1  | Optimisation discussion                                  |

| 1.0.2   | 2011-07-6  | Timing analysis update                                   |

| 1.0.3   | 2011-07-12 | Added details on the optimisation architecture elements. |

| 1.0.4   | 2011-08-31 | Period 1 refinements                                     |

| 1.1.0   | 2012-03-30 | Second iteration                                         |

| 1.1.1   | 2012-09-15 | Draft version for review release of second iteration     |

| 2.0.0   | 2012-10-04 | Release version of second iteration                      |

#### **List of Abbreviations**

AADL Architecture and Analysis Design Language

ARS Assigned Requirement for Safety

ASIL Automotive Safety Integrity Level

ASR Assigned Safety Requirement

CCF Common cause failure

COF Constrained Output Failure

DRS Driver Reaction System

DSR Derived Safety Requirement

ETA Event Tree Analysis

FEV Fully Electric Vehicle(s)

FMEA Failure Modes and Effects Analysis

FTA Fault Tree Analysis

GSPN Generalised Stochastic Petri Net

HAZOP Hazard & Operability Analysis

HiP-HOPS Hierarchically-Performed Hazard Origin & Propagation Studies

HRC Heteorogenous Rich Components

MC Markov Chain

MoC Model of Computation

M(A) Model (Airfix)

PROMELA Process Meta-Language

RBD Reliability Block Diagram

RAS Replenishment-at-Sea

RSA Required Safety Assignment

SAFORA State Automata to Fault-trees extended with temporal information (ORA in Greek)

SAR Search-and-Rescue

SM State Machine

SPEEDS Speculative and Exploratory Design in Systems Engineering

SPIN Simple PROMELA Intepreter

SRA Safety Requirement Allocation

SRD Safety Requirement Derivation

TFT Temporal Fault Tree

UML Unified Modelling Language

## Table of contents

| Au  | ıthors     |                                                                                    | 2  |

|-----|------------|------------------------------------------------------------------------------------|----|

| Re  | evision ch | art and history log                                                                | 3  |

| Lis | st of Abb  | eviations                                                                          | 4  |

| Ta  | ble of co  | ntents                                                                             | 5  |

|     |            |                                                                                    |    |

| 1   | Introd     | uction                                                                             | 7  |

|     | 1.1        | Goals                                                                              | 7  |

|     | 1.2        | tructure                                                                           | 8  |

| 2   | Analys     | sis and synthesis concepts to support ISO 26262                                    | 10 |

|     | 2.1        | ummary of the ISO 26262 safety design workflow                                     | 10 |

|     | 2.2 F      | lazard analysis in ISO 26262                                                       | 12 |

|     | 2.3 F      | lisk assessment in ISO 26262                                                       | 13 |

|     | 2.3.1      | Evaluation Criteria                                                                | 14 |

|     | 2.3.2      | ASIL (Automotive Safety Integrity Levels)                                          | 15 |

|     | 2.4 A      | SIL decomposition and allocation in ISO 26262                                      | 17 |

|     | 2.4.1      | ASILs in ISO 26262                                                                 | 17 |

|     | 2.4.2      | ASIL Decomposition & Allocation Algorithm                                          | 22 |

|     | 2.4.3      | HiP-HOPS and Tool Support for ASILs                                                | 34 |

|     | 2.5        | viscussion & Further Work                                                          | 36 |

|     | 2.5.1      | Support for ASILs                                                                  | 36 |

|     | 2.6        | Optimisation algorithm for ASIL Decomposition                                      | 38 |

|     | 2.6.1      | The ASIL Optimisation Process                                                      | 38 |

|     | 2.6.2      | Encoding                                                                           | 39 |

|     | 2.6.3      | Evaluation Heuristics                                                              | 39 |

|     | 2.6.4      | Optimisation algorithms                                                            | 40 |

|     | 2.6.5      | Implementation & Performance                                                       | 40 |

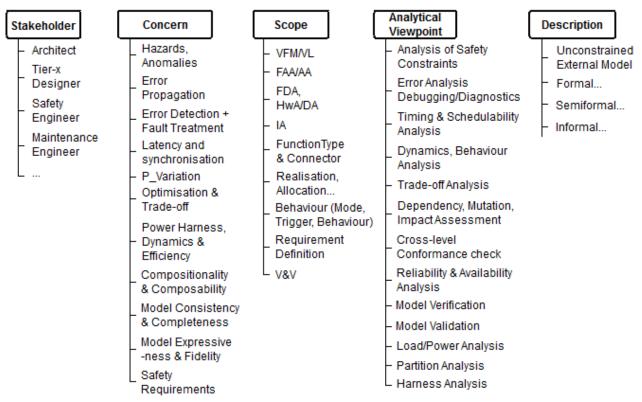

| 3   | Model      | -based system analysis techniques                                                  | 42 |

|     | 3.1 T      | he Scope of Analysis support by EAST-ADL                                           | 42 |

|     |            | nhanced language support for behaviour-centric analysis                            |    |

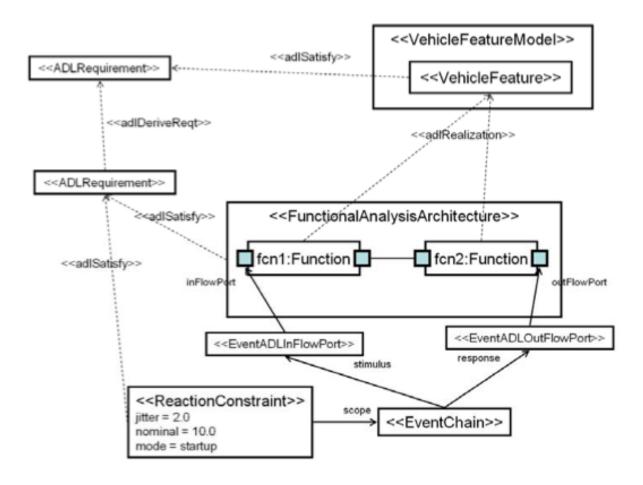

|     | 3.2.1      | The roles of EAST-ADL native behaviour constraint specification                    | 43 |

|     | 3.2.2      | Key content of EAST-ADL native behaviour constraint specification                  | 44 |

|     | 3.2.3      | Relating EAST-ADL native behaviour constraint specification to external formalisms | 44 |

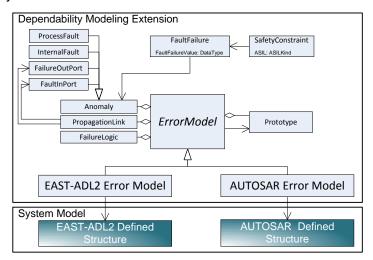

|     | 3.3 N      | lodelling support for dependability analysis                                       | 47 |

|     | 3.3.1      | Dependability and error modelling in EAST-ADL                                      | 47 |

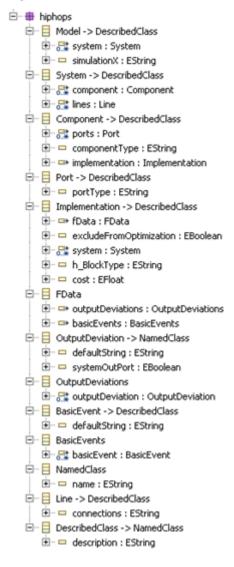

|     | 3.3.2      | Safety Analysis with HiP-HOPS Technology                                           | 48 |

|     | 3.3.3      | Multi-perspective analysis of EAST-ADL models                                      | 54 |

|     | 3.3.4      | Dynamic SM-based Safety Analysis                                                   | 58 |

|   | 3.3.5      | Tool specification and exchange formats                     | 60 |

|---|------------|-------------------------------------------------------------|----|

|   | 3.3.6      | Tool Integration                                            | 60 |

|   | 3.3.7      | Semantic Mapping Transformation                             | 62 |

|   | 3.3.8      | Representation Transformation                               | 62 |

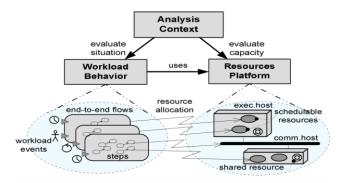

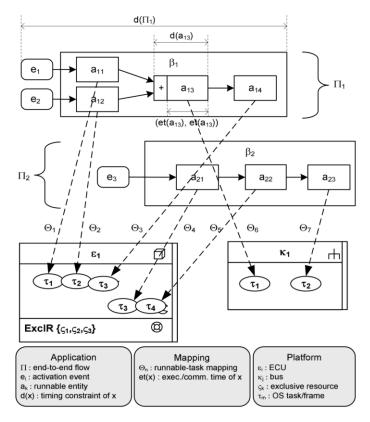

| 3 | .4 Timi    | ng Analysis                                                 | 64 |

|   | 3.4.1      | EAST-ADL/TADL                                               | 64 |

|   | 3.4.2      | MARTE                                                       | 66 |

|   | 3.4.3      | Summary                                                     | 68 |

|   | 3.4.4      | Timing analysis tooling                                     | 69 |

| 3 | .5 Anal    | lysis and Synthesis concepts to support Electrical Vehicles | 70 |

|   | 3.5.1      | Identified Needs                                            | 70 |

|   | 3.5.2      | Component count and cost analysis                           | 70 |

|   | 3.5.3      | Cable Length                                                | 74 |

|   | 3.5.4      | Power Consumption                                           | 74 |

|   | 3.5.5      | Current analysis                                            | 74 |

|   | 3.5.6      | Power Distribution Analysis                                 | 75 |

| 4 | Automation | c multi-objective optimisation of system models             | 76 |

| 4 | .1 Brief   | f description of optimisation definitions and concepts      | 76 |

|   |            | nparison of optimisation algorithms                         |    |

| 7 | 4.2.1      | Genetic Algorithms (GAs)                                    |    |

|   | 4.2.2      | Tabu Search                                                 |    |

|   | 4.2.3      | Ant Colony                                                  |    |

|   | 4.2.4      | Simulated Annealing                                         |    |

| 4 |            | support for automatic optimisation                          |    |

|   | 4.3.1      | Variability in HiP-HOPS                                     |    |

|   | 4.3.2      | HIP-HOPS Optimisation Algorithm                             |    |

|   | 4.3.3      | Achieving full multi-objective optimisation in MAENAD       |    |

|   | 4.3.4      | Optimisation Architecture Elements                          |    |

|   | 4.3.5      | Product Line Optimisation                                   |    |

|   | 4.3.6      | The Plan                                                    |    |

| 5 |            | ntation support for variability management                  |    |

| J | -          |                                                             |    |

| 6 | Summary    | and conclusions                                             | 95 |

| 7 | Referenc   | es e                    | 97 |

#### Introduction

#### 1.1 Goals

The primary challenge of the MAENAD project is to develop methods and techniques to support the engineering and design of FEV (Fully Electric Vehicles). To achieve this, it is necessary to define language support in EAST-ADL for the required modelling, analysis, and optimisation concepts, and furthermore to develop algorithms and specify tools that can be implemented and used to analyse and optimise those models. The extensions to EAST-ADL to support the additional modelling concepts are covered in D3.1.1, while the specification of analysis and optimisation algorithms is described in this document, D3.2.1.

In particular, the D.3.x.1 deliverables are intended to support the following project objectives:

• O1-1: Support in EAST-ADL for the safety process of ISO 26262 and representation of safety requirements.

The ISO 26262 standard contains a number of different procedures and design techniques to ensure the safety of an automotive system. To achieve the project goals, EAST-ADL must be extended to support the different modelling approaches present in ISO 26262 and algorithms or tools should be developed to support the analyses required by ISO 26262. The additional analysis concepts and tool support required for ISO 26262 are described in this document.

O1-2: Automatic allocation of safety requirements (ASILs).

One of the features of ISO 26262 is the concept of ASILs (Automotive Safety Integrity Levels) and the way they can be allocated to different system elements to meet safety requirements. The automatic allocation of safety requirements also has potential applications beyond simply supporting ISO 26262 and could be applied to similar types of qualitative requirements in other domains. While the language concepts necessary to support ASILs and safety requirements are described by D3.1.1, the algorithms for the analysis and allocation of ASILs are specified in this document.

• O2-1: Dependability analysis of EAST-ADL models (with capabilities for multi-mode and temporal analysis of failures, together with integrated assessment of HW-SW design perspectives).

To fully support ISO 26262, it must also be possible to perform various dependability analyses at different stages of the design process, ranging from more simple conceptual analysis to more detailed architectural analysis. Such analyses include hazard analyses, risk analyses, criticality analyses, Failure Modes and Effects Analysis (FMEA), and Fault Tree Analysis (FTA).

O2-2: Behavioural Simulation of EAST-ADL models.

As well as dependability analysis, another goal of MAENAD is to introduce execution and compositional behaviour semantics into EAST-ADL to allow for behavioural simulation and analysis of EAST-ADL models. The modelling concepts necessary for behavioural simulation are described in D3.1.1 while the analysis and tool support necessary is specified in this document.

O2-3: Timing Analysis of EAST-ADL models.

The third type of model-based analysis included MAENAD is timing and performance analysis. As with the other forms of analysis, the necessary language concepts are described in D3.1.1 while the algorithm and tool support is specified here in D3.2.1. In the case of timing analysis, this will mean developing ways of linking EAST-ADL models to external timing analysis tools like MAST or RT-DRUID.

O3-1: Extension of EAST-ADL with semantics to support multi-objective optimisation for product lines.

In addition to analysis of EAST-ADL models of FEVs, another goal of MAENAD is to support model-based optimisation. This involves both extending existing or developing new concepts in EAST-ADL to allow for substitution of one design element for another to create a design space that can be explored by optimisation algorithms such as genetic algorithms. The notion of substitutability and the definition of alternative model elements that can be explored by the optimisation algorithm are achieved via extension of the variability capabilities of EAST-ADL.

The modelling concepts necessary for optimisation, including variability, are described in D3.1.1, while the algorithmic support is specified here in D3.2.1.

O3-2: Definition of a library of standard architectural patterns that can be automatically applied on an un-optimised EAST-ADL model in order to improve dependability and performance.

Finally, one technique for supporting model-based optimisation is to allow different architectural patterns to be applied to a design model. Such patterns exhibit different dependability and performance characteristics, and the automatic selection and substitution of such patterns can allow different design candidates to be rapidly conceived and evaluated. The types of patterns and the methods with which they may be included in the optimisation process will be included in later versions of this document.

#### 1.2 Structure

The above objectives are developed in MAENAD by several different working groups that each focus on different aspects of the project goals: ISO 26262 support (XG-I), system analyses (XG-A), optimisation (XG-O), and variability (XG-V). Both D3.x.1 deliverables are therefore organised along these lines, and therefore the overall structure of D3.2.1 is as follows:

**Section 2** describes the requirement for additional analysis techniques and tools necessary to fully support the ISO 26262 design process, including a brief summary of the ISO 26262 workflow itself. ASIL decomposition is covered in this section.

**Section 3** describes the concepts and algorithms behind the various system analyses and tools developed in MAENAD, including subsections for both dependability analysis to support ISO 26262 and each of the other types of analysis of EAST-ADL models, namely behavioural simulation and timing analysis. There is also a section on support for FEV analysis concepts. The specifications of the analysis concepts and algorithms in D3.2.1 is a valuable input to the tool implementation activities of WP5, as well as feeding back into development of EAST-ADL itself.

**Section 4** covers the development of concepts and algorithms for the automatic optimisation of EAST-ADL models, particularly with respect to dependability and timing/performance objectives. Later in the project, it will also describe the development of different substitutable architectural patterns that can be used in the optimisation process, although these will be fully specified in an appendix instead.

**Section 5** briefly covers the analysis and tool support developed in MAENAD for the modelling of variability. Some of the variability concepts are also inevitably discussed as part of the optimisation section.

**Section 6** summarises the different analysis and synthesis concepts described in D3.2.1 and relates them to the objectives set out in this introduction, describing how each is fulfilled (or not) by the algorithms and tools developed in MAENAD.

## 2 Analysis and synthesis concepts to support ISO 26262

This section describes the requirements of the ISO 26262 standard and how we aim to support those requirements in MAENAD.

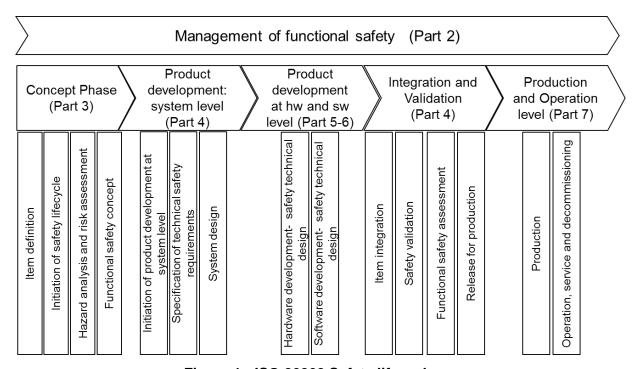

## 2.1 Summary of the ISO 26262 safety design workflow

The ISO/FDIS 26262 requires the application of a "functional safety approach", starting from the preliminary vehicle development phases and continuing throughout the whole product life-cycle. This approach allows for the design of a safe automotive system. Furthermore, it provides an automotive specific risk-based approach for determining risk classes named ASILs (Automotive Safety Integrity Levels). The new standard uses ASILs for specifying the item's necessary safety requirements for achieving an acceptable residual risk, and provides requirements for validation and confirmation measures to ensure a sufficient and acceptable level of safety being achieved [1].

The main phases of ISO 26262 are:

- Concept phase (ISO 26262 Part 3):

- Item definition: during this phase the Item has to be identified and described. To have a satisfactory understanding of the item, it is necessary to know about its functionality, interfaces, and any relevant environmental conditions. Moreover the boundary of the item has to be defined.

- Initiation of safety lifecycle: the safety lifecycle is initiated based on Item definition and by determining the development category (e.g. current production, new, modified, etc). In the case of modification, an impact analysis shall be performed.

- Hazard analysis and risk assessment: to evaluate the risk associated with the item under safety analysis, a risk assessment is carried out. A risk assessment considers the functionality of the item and a relevant set of scenarios (operating conditions & environmental conditions). For each identified hazardous event the ASIL level has to be determined. Moreover, after the assessment of the risk, the safety goal (top level safety requirements) shall be defined.

- Functional Safety Concept: based on the safety goals, the functional safety requirements have to be specified. The functional safety concept shall include:

- Functional safety requirements → to define in a complete way the functional safety requirements, the following attributes have to be defined for each hazardous event: safety goals, operating modes, fault tolerant time interval, possible safe state, transitions to and from the safe state, emergency operation interval, functional redundancies, driver warning, degraded operation and driver's actions;

- Item functional description and requirement allocation;

- Interaction description with vehicle systems;

- Functional specifications to achieve the safety goals;

- Description of external measures to avoid or mitigate the effects of hazards.

- System level development specification, (ISO 26262 Part 4)

- Initiation of product development at system level: the functional safety activities during the individual sub-phases of system development have to be determined and

- planned. The safety plan shall include the Item integration and testing plan, the validation plan and the functional safety assessment plan.

- Specification of technical safety requirements: the technical safety requirements shall be specified by refining the functional safety concept, considering both the functional concept and the preliminary architectural assumptions. Moreover the consistency and traceability between functional safety requirements and technical safety requirements shall be verified.

- System design: the system design and the technical safety concept that comply with the functional requirements, and the technical safety requirements specification of the item shall be defined. Methods and measures to avoid systematic failures have to be applied during system design. Furthermore, methods to avoid random hardware failures during system operation shall be applied in this phase.

- Comply with the technical safety requirements specification: it is necessary to verify that the system design and the technical safety concept comply with the technical safety requirements specification.

- Hardware and Software level development, (ISO 26262 Part 5 and Part 6)

- Hardware and Software development safety technical design: based on the system design specification, the item is developed from the hardware and software level perspective.

- System level development integration and validation (ISO 26262 Part 4)

- o Item integration: the compliance with each safety requirement in accordance with its specification and ASIL classification shall be tested. Moreover it is necessary, during this phase, to verify that the "System design" covering the safety requirements is correctly implemented by the entire item. The item integration starts with the integration of the hardware and software of each element that the item comprises. After the integration of the elements into a full system, the final step is the integration of the item with other systems within a vehicle and with the vehicle itself.

- Safety validation: the evidence of compliance with the safety goals and evidence that the functional safety concepts are appropriate for the functional safety of the item shall be provided. Moreover the evidence that the safety goals are correct, complete and fully achieved at the vehicle level shall be provided.

- Functional safety assessment: it is necessary to assess that the functional safety is achieved by the item.

- Release for production: the release for production criteria at the completion of the item development shall be specified. The release for production confirms that the item complies with the requirements for functional safety at the vehicle level.

- Production and Operation Level (ISO 26262 Part 7)

- Production: a production process for safety-related elements or items that are intended to be installed in road vehicles has to be developed and maintained. Functional safety during the production process by the relevant manufacturer or the person or organisation responsible for the process shall be achieved.

- Operation, service and decommissioning: in order to maintain the functional safety after the item's release for production, the customer information, maintenance and repair instructions, and disassembly instructions regarding the item, system or element shall be specified.

- Management of functional safety (ISO 26262 Part 2): in this phase the requirements for management of functional safety are specified. These requirements cover all the phases of the safety lifecycle, and are specified for:

- Overall safety lifecycle management;

- Safety management during the concept phase and the product development;

- Safety management after the item's release for production.

Figure 1 - ISO 26262 Safety lifecycle

#### 2.2 Hazard analysis in ISO 26262

To identify the hazards, it is essential to define the malfunctions and eventual maintenance condition(s) related to the item.

All possible functional anomalies derivable from each foreseeable source shall be defined.

In general, for each *target function* (the function description in terms of output(s) behaviour) it is always possible to define, in an exhaustive manner, the malfunctions in terms of anomalies of function activation:

- Unwanted activation

- Missed activation

- Degraded activation (vs. value or timing)

- Incoherent activation (in presence of more than one function's output)

- Unwanted deactivation

- Missed deactivation

- Degraded deactivation (vs. value or timing)

- Incoherent deactivation (in presence of more than one function's output)

#### 2.3 Risk assessment in ISO 26262

In order to perform a correct and complete risk assessment, a proper set of realistic scenarios (all variables and/or states that characterise the functions or affect them) must be defined.

A complete description of a scenario includes:

<u>Operative conditions</u> → selection of the factors related to vehicle usage scenarios to be considered for situation analysis and hazard identification. Examples in the vehicle dynamic control field are:

- Dynamic driving state

- ✓ Speed

- ✓ Longitudinal acceleration

- ✓ Lateral acceleration

- **√** ...

- Manoeuvres

- ✓ Curve

- ✓ Overtaking

- ✓ Braking

- ✓ Lane change

- **√** ..

- Driver condition

- ✓ Attention level

- ✓ Hands on steering

- **√** ..

- <u>Environmental conditions</u> → selection of the factors related to environmental variables to be considered for situation analysis and hazard identification. Typical environmental conditions include:

- Location

- ✓ Urban road

- ✓ Suburban road

- ✓ Motorway or highway (with lateral barriers)

- ✓ ..

- Street condition

- ✓ Adherence

- ✓ Road surface type (smooth, rough, etc.)

- ✓ Slope

- ✓

- Traffic situation

- Presence of other vehicle(s) (lateral, oncoming, following, etc.)

- ✓ Presence of cycles, pedestrians, etc.

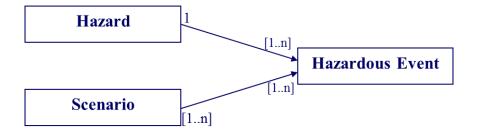

The hazard under safety analysis, when applied to the operational situations (operative & environmental conditions), triggers the so called "hazardous event".

Figure 2 - Hazardous Events

For each identified hazardous event, the severity, controllability and exposure values should be ranked to determine the associated Automotive Safety Integrity Level (ASIL), representing the level of risk.

Parameters for risk determination according to ISO 26262:

- Controllability [C]:

- Avoidance of a specified harm or damage through timely reactions of the persons involved.

- Severity [S]:

- Measure of the expected degree of harm to an endangered individual in a specific situation.

- Exposure time [E]:

- State of being in an operational situation that may be hazardous if coincident with the malfunction under consideration

## 2.3.1 Evaluation Criteria

## Controllability

The controllability shall be assigned to one of the controllability classes C0, C1, C2 and C3 in accordance with the table below:

| Class | Description                               |  |

|-------|-------------------------------------------|--|

| C0    | Controllable in general                   |  |

| C1    | Simply controllable                       |  |

| C2    | Normally controllable                     |  |

| C3    | C3 Difficult to control or uncontrollable |  |

Table 1 - Controllability

It is important to note that the controllability levels assigned to the various situations should be assessed through specific testing on the road, fault injection, etc.

## Severity

The severity shall be assigned to one of the severity classes S0, S1, S2 or S3 in accordance with the table below.

| Class | Description                                              |  |  |  |

|-------|----------------------------------------------------------|--|--|--|

| S0    | No injuries                                              |  |  |  |

| S1    | Light and moderate injuries                              |  |  |  |

| S2    | Severe and life-threatening injuries (survival probable) |  |  |  |

| S3    | <u> </u>                                                 |  |  |  |

Table 2 - Severity

## **Exposure time**

The probability of exposure shall be assigned to one of the probability classes E1, E2, E3 and E4 in accordance with the table below.

| Class | Description         |  |

|-------|---------------------|--|

| E1    | ery low probability |  |

| E2    | _ow probability     |  |

| E3    | Medium probability  |  |

| E4    | High probability    |  |

Table 3 - Exposure

## 2.3.2 ASIL (Automotive Safety Integrity Levels)

Safety Integrity Levels (SILs) are abstract classification levels that can be used to indicate the level of safety required of safety-critical systems (or elements thereof). SILs have been adopted as part of safety standards such as IEC 61508 and - in the automotive domain - ISO/FDIS 26262. In the context of the upcoming ISO 26262, SILs are known as ASILs - Automotive Safety Integrity Levels - and form a major part of the standard: ASILs are used to specify the necessary safety requirements for achieving an acceptable residual risk, as well as providing requirements for validation and confirmation to ensure the required levels of safety are being achieved.

Safety requirements in these standards are intended to ensure the system being designed is free from unacceptable risk (assuming the requirements are met) and are derived through a process of analysis and risk assessment. The aim of the process is to determine the critical system functions - those which have the potential to be hazardous in the instance of failure - and the requirements necessary to mitigate the effects or reduce the likelihood of those hazards. These safety requirements are often associated with integrity requirements that apply to those critical functions to indicate, in essence, what level of contribution they have towards the overall system safety and thus what level of safety they should implement to avoid system failures. A low ASIL therefore indicates that the element is not a major contributor to severe system failures, while a high ASIL indicates that it is potentially is a major contributor, and this allows a means of verifying that system safety requirements are being achieved by ensuring that the ASILs allocated to system elements are also being met.

Therefore ASILs play a dual role in the development of safety-critical systems: they allow for top-down allocation of safety requirements to different elements of the system according to their contribution to risk, and they allow for bottom-up verification to show that the safety requirements are being met by the developed system.

ASILs are divided into one of four classes to specify the item's necessary safety requirement for achieving an acceptable residual risk, with D representing the highest and A the lowest class. The ASIL-Level shall be determined for each hazardous event using the estimation parameters severity (S), probability of exposure (E) and controllability (C) in accordance with the table below. QM (Quality Management) can be applied to non-safety critical elements to indicate that there are no specific safety requirements in place.

|            |    | C1 | C2 | С3 |

|------------|----|----|----|----|

|            | E1 | QM | QM | QM |

| <b>S</b> 1 | E2 | QM | QM | QM |

| 31         | E3 | QM | QM | А  |

|            | E4 | QM | А  | В  |

|            | E1 | QM | QM | QM |

| S2         | E2 | QM | QM | А  |

| 52         | E3 | QM | А  | В  |

|            | E4 | А  | В  | С  |

|            | E1 | QM | QM | А  |

| <b>S</b> 3 | E2 | QM | А  | В  |

| 33         | E3 | А  | В  | С  |

|            | E4 | В  | С  | D  |

**Table 4 - Determining ASILs**

ASIL = QM (Quality Management) → the function has no impact on safety - it is not necessary to define any safety requirement

$ASIL = A \rightarrow$  the function has a minimal impact on safety

$ASIL = B \rightarrow$  the function has an impact on safety – considerable damage

ASIL = C → the function has impact on safety – relatively high damage associated with medium-high probability of being in a situation of risk

ASIL = D → the function is critical - very significant damage associated with a high probability of being in a situation of risk

## **Top-level safety requirements**

During the concept phase a *safety goal* shall be defined for each hazardous event. This is a fundamental task, since the safety goal is the top level safety requirement, and it will be the base on which the functional and technical safety requirements are defined. The safety goal leads to item characteristics needed to avert the hazard or to reduce risk associated with the hazard to an acceptable level. Each safety goal is assigned an ASIL value to indicate the required integrity level according to which the goal shall be fulfilled. For every safety goal a *Safe state*, if applicable, shall be identified in order to declare a system state to be maintained or to be reached when the failure is detected, so to allow a failure mitigation action without any violation of the associated safety goal. For each safety goal and safe state (if applicable) that are the results of the risk assessment, at least one safety requirement shall be specified.

## 2.4 ASIL decomposition and allocation in ISO 26262

One of the benefits of ASILs is that they can be decomposed across different elements and subsystems of the system architecture so that the highest constituent ASIL need not apply equally to the entire system; instead, those parts of the system that are most critical and that contribute most to potential failures are allocated higher ASILs and are thus subject to the strictest safety requirements, while less important parts that have little or no bearing on potential failures are allocated lower ASILs and are subject to lower safety requirements. This is important as high levels of safety are much more expensive to implement than lower levels of safety, and if the required level of safety can be achieved for a lower cost, then it is normally desirable to do so.

However, although ISO 26262 defines guidelines and procedures to be followed during ASIL decomposition and allocation, the process is generally a manual and unaided one. This can be problematic in situations where multiple safety-critical functions are delivered by complex, networked architectures. As part of the MAENAD project, we aim to provide both language and tool support for a more systematic approach to ASILs, including the potential for automatic decomposition of ASILs. Specifically, objective O1-1 states that EAST-ADL should be extended to support the safety process of ISO 26262 and provide representation of safety requirements, while objective O1-2 explicitly states a goal of developing support for the automatic allocation of ASILs. The intention is to ensure that the use of ASILs as described in ISO 26262 can be carried out more easily and efficiently even in larger and more complex systems.

## 2.4.1 ASILs in ISO 26262

ISO 26262 sets out a comprehensive methodological framework for the design and development of electronic engineering (EE) systems in the automotive domain. ASILs - and the associated acts of determining and upholding safety requirements - form a major part of this process as they are the mechanism by which the required levels of safety are represented and maintained throughout the design of the system. As such, ISO 26262 contains a considerable amount of information on ASILs and how they should be used. For detailed information, the reader should refer to ISO 26262 itself, but a general overview of the more relevant parts will be given here.

## 2.4.1.1 Hazard Analysis and definition of ASILs

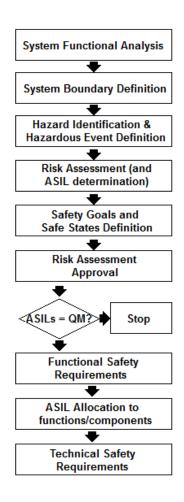

ASILs are initially derived during the process of defining the safety requirements, i.e., what must be done to ensure a reasonable freedom from unacceptable risk. They are obtained through a combination of functional hazard analysis and risk assessment techniques, starting at an abstract, high-level concept stage (corresponding to EAST-ADL's Vehicle level). These are then developed further and verified at subsequent stages of the design, as represented in increasingly lower, more concrete design views (corresponding to EAST-ADL's Analysis and Design levels).

Figure 3 - Overview of the ISO 26262 safety workflow

The first step is the identification of hazards and the definition of hazardous events. This initially consists of assessing the 'target feature' of the item under safety analysis and determining its possible malfunctions, i.e., possible anomalies in its output (also known as *feature flaws*). All possible functional anomalies - whether internal, external (e.g. due to misuse), or as a result of maintenance (or the lack thereof) - are considered. These malfunctions form the basis of the hazards - the potential sources of harm that the item can cause. In addition, the various possible operating and environmental scenarios are also considered in which these hazards may occur; taken together, they form the definition of the *hazardous events*, i.e., the occurrence of a given hazard in a particular scenario.

Hazardous Events are then classified in terms of its risk by assigning it an ASIL. This is arrived at by considering the hazardous event from three perspectives: controllability, severity, and exposure, each of which is graded into four categories. The level of risk is determined as a function of the frequency and severity of the hazardous event, and the frequency in turn is determined by the controllability and exposure, so the ASIL can be derived from these factors, as shown in Table 4.

The ASIL itself is captured as part of the *safety goal* corresponding to the hazardous event. For all elements not classified as QM (and it is important to note that QM can only be assigned to elements that are not considered to be safety relevant), a safety goal should be defined. These can result in top-level (i.e., system-level) safety requirements that describe the characteristics the item needs to avert or otherwise mitigate the effects of the hazard in order to achieve an acceptable level of safety. In addition, for every safety goal, a safe state should be defined,

indicating what state the system should maintain or transition to when the hazardous event is detected in order to mitigate that event and achieve the safety goal.

It should also be noted that for a Safety Element out of Context (SEooC), much of this hazard analysis is not possible (due to the lack of contextual information), and so an assumed ASIL is typically assigned instead.

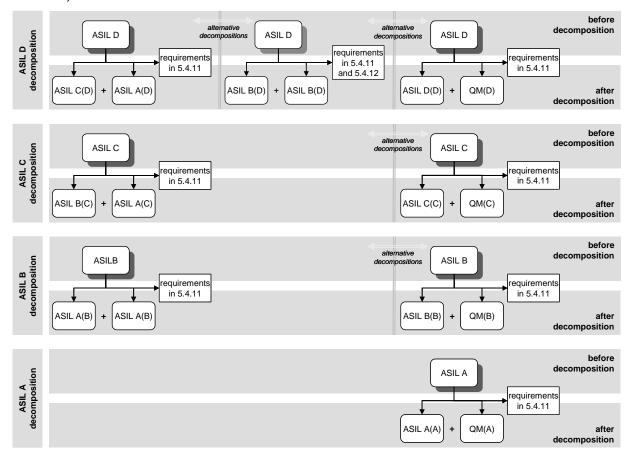

#### 2.4.1.2 ASIL Decomposition

Once defined, the ASILs of the top-level safety goals are propagated throughout the development process as the safety requirements are refined. Each derived safety requirement inherits the ASIL from the safety goal or requirement it was derived from, and so the functional and technical safety requirements that are ultimately allocated to architectural elements all possess a corresponding ASIL.

It is also possible for ASILs to be defined independently of the safety goals when looking at Safety Elements out of Context (SEooC). A SEooC can be a system, subsystem, software or hardware component, or any other part of a system that is safety-critical and designed to be generic and used within more than one system. In this case it is possible to analyse the SEooC with regard to safety, without knowing the context in which the element may operate, by assuming ASIL values and using those values in later decomposition.

These ASILs can be tailored to fit the architecture of the design through the process of *ASIL decomposition*, in which different ASILs are allocated to different elements while ensuring that the overall ASILs as defined by the system-level safety requirements are still being achieved. This process takes advantage of architectural decisions - such as the inclusion of independent or redundant architectural elements - to implement the safety requirements across these elements and thus (potentially) assigning a lower ASIL to the decomposed safety requirements that apply to each individual element without affecting the ASIL that applies to those elements taken together. It is important to note that this can only be achieved where there is a sufficient degree of independence between elements and no critical dependencies (and thus dependent failures) to influence them; this can exclude instances of homogenous redundancy (situations where the same element is duplicated to achieve some measure of redundancy) where elements may suffer from common flaws even if no explicit dependencies exist between elements. ISO 26262 suggests that when deciding the matter of independence, the following should be considered:

- Similar or dissimilar redundant elements:

- Different functions implemented with identical software or hardware elements;

- Functions and their respective safety mechanisms;

- Partitions of functions or software elements;

- Physical distance between hardware elements, with or without a barrier;

- Common external resources.

ISO 26262 also distinguishes between independence (which requires freedom from both cascading/propagating failures as well as common cause failures, and which affects the viability of decomposition) and interference (which requires only freedom from cascading failures and which affects the allocation of QM to sub-elements).

Figure 4 shows how the ASILs can be decomposed such that two (or more) lower ASILs can be equivalent to a higher ASIL. Note that the original ASIL is retained in brackets afterwards. Decomposition can also be applied to elements that are not safety-critical, assuming there is no link between those elements and safety-relevant elements such that failures can cascade from one to the other; in these cases, the non-critical elements can be allocated QM while the safety-related element gains a true ASIL. Decomposition can be applied during multiple stages of the design process, including the concept phase (corresponding to EAST-ADL analysis level and

FAA), system phase (corresponding to the EAST-ADL design level, with FDA for functions and HDA for platform), and software and hardware phases (corresponding to Implementation level and AUTOSAR).

Figure 4 - Decomposition Algebra

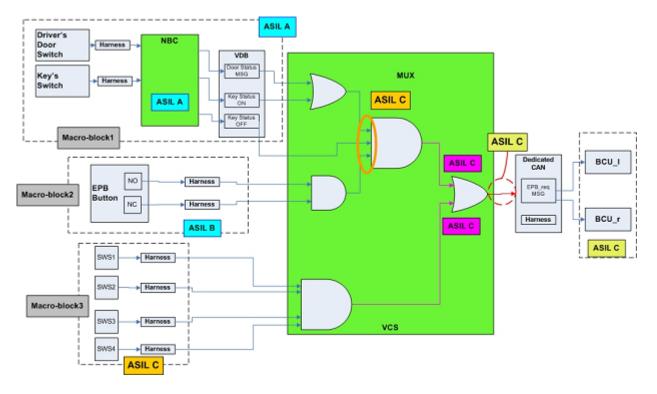

Figure 5 shows how ASILs can be decomposed across independent channels in an architecture. The modelled system as a whole has ASIL C, indicating there is a relatively severe hazard that must be avoided. Parts of the system that contribute directly to the system failure (such as the Dedicated CAN and the outputs) receive the ASIL directly too. When there is a disjunction, e.g. two or more components can all cause the system failure individually, they all receive the full ASIL. Only when components must fail together in conjunction to cause the system failure is the ASIL diluted. This can be seen in the simple case for Macro-block3 in the diagram, which collectively receives an ASIL C; the subcomponents within (ultimately SWS1-4) may not have the full ASIL C, however, and there are a number of different possible combinations of ASILs that would fulfil the ASIL C for the subsystem as a whole (e.g. A + A + A + A).

A more complex case arises with Macro-block1 and Macro-block2. Both must fail in conjunction to cause system failure, thus both together receive a share of the ASIL C. Because of the AND failure logic (caused by multiplexers) in the "VCS" component, the received ASIL C can be decomposed over Macro-block 1 and Macro-block 2 such that Macro-block 1 receives ASIL A and Macro-block 2 receives ASIL B (which together meet ASIL C), since both are required to cause the VCS to fail. By contrast, Macro-block 3 inherits ASIL C directly since it is single-handedly capable of causing the VCS to fail. It is also worth noting that the ASILs of each of these three Macro-blocks could be decomposed further within those blocks too. For example, in Macro-block1, a failure of either output is all that is necessary, whereas in Macro-block2, a failure of both outputs is needed, so in Macro-block1, all components would require ASIL A (i.e., the ASIL of Macro-block1) since any individual failure is sufficient, but in Macro-block2, both originating contributors (NO and

NC in the EPB Button subsystem) could receive ASIL A (rather than ASIL B, the ASIL of Macro-block2) as both need to fail for Macro-block2 to fail.

Figure 5 - ASIL Decomposition example

## 2.4.1.3 Safety Analysis in support of ASILs

An assessment of the failure logic of the system and thus a verification of whether elements of the system are indeed independent (without any dependent or common cause failures) can be carried out by a variety of safety analysis techniques. ISO 26262 suggests that qualitative methods should be applied during the abstract system phase and software phase, while quantitative methods can be applied during the hardware phase to allow for the quantification of random hardware failures (although it also suggests common cause failures should still be estimated on a qualitative basis due to the difficulty in accurately quantifying them). Any analysis should take into account:

- Random hardware failures (which may be quantified)

- Development/design faults (e.g. due to errors in design or requirements)

- Installation faults

- Repair/maintenance faults

- Environmental factors (e.g. temperature, pressure, corrosion, electromagnetism)

- Failures of common external resources (e.g. power, communication buses)

- Stress due to specific situations (e.g. wear & tear)

The objective of the safety analyses in these cases is to examine the consequences of the failures on the elements of the system, providing information on whether the safety goals & requirements are being met and also determining whether or not ASIL decomposition will be possible. Analysis may also discover new hazards. ISO 26262 suggests the following analysis techniques:

- Qualitative & quantitative FMEA

- Qualitative & quantitative FTA

- Qualitative & quantitative ETA

- HAZOP (qualitative)

- Markov models (quantitative)

- RBDs (quantitative)

FTA in particular is well suited to performing analysis for the purposes of ASIL decomposition since it can take into account the effects of multiple failures, which e.g. FMEA cannot. Thus it can determine whether or not two or more input failures must occur to cause an output failure (which may suggest the possibility for ASIL decomposition in that case).

In the case of random hardware failures, it is possible to apply quantitative analysis if the appropriate failure data is available. In these cases, quantitative target values for the maximum probability of the violation of each safety goal can be used; ISO 26262 provides a table with one such possible set of values:

| ASIL | PROBABILITY                        |

|------|------------------------------------|

| D    | < 10 <sup>-8</sup> h <sup>-1</sup> |

| С    | < 10 <sup>-7</sup> h <sup>-1</sup> |

| В    | < 10 <sup>-7</sup> h <sup>-1</sup> |

Table 5 - Possible target probabilities for different ASILs

However, it should be noted that these are only suggestions and can be tailored to fit the circumstances, particularly if e.g. trusted field data is available.

#### 2.4.2 ASIL Decomposition & Allocation Algorithm

## 2.4.2.1 ASIL Decomposition with multiple hazards

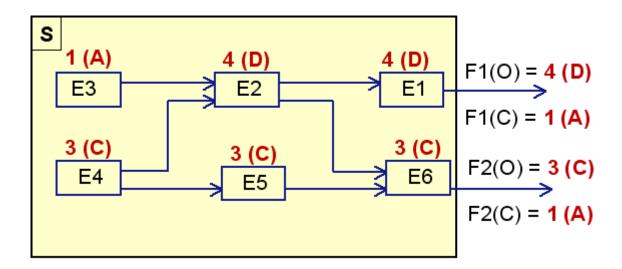

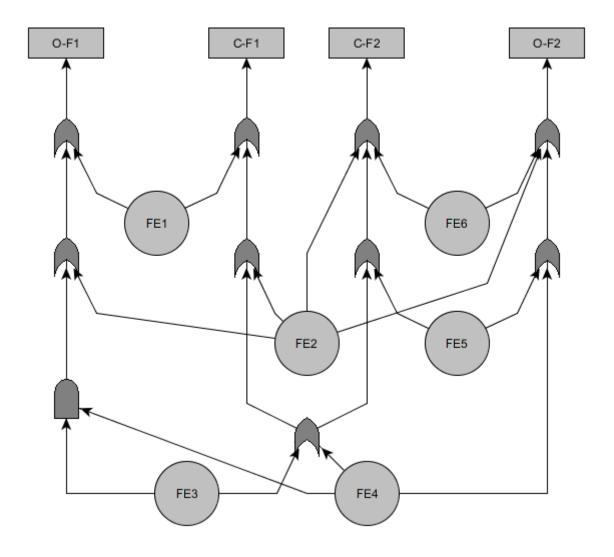

As stated in the previous section, one of the primary objectives of MAENAD is not merely to provide support for the ISO 26262 safety design process but also to support the automatic decomposition of ASILs. Because of the large role ASILs play in ISO 26262, having tool support and particularly a degree of automation - may be very important. While simple examples that deal with only a single hazard - like that in Figure 5 - can be decomposed manually as they do not have too many elements or too complex logic, when multiple hazards are in play, this becomes significantly more difficult, even for small, seemingly simple systems like that in Figure 6. In this example, there is a system (S) that provides two separate outputs, F1 and F2. The six subelements of the system (e.g. functions, components etc.), E1 to E6, are the components necessary to provide these two outputs. Each output can fail in one of two ways - omission (lack of provision of output) and commission (unexpected or unwanted provision of output), and thus there are four hazards (omission of F1, commission of F1, omission of F2, and commission of F2) which interact at multiple points.

Figure 6 - Dealing with multiple hazard constraints

In most examples, there are many alternative ASIL assignment strategies that could be used (as in the case of Figure 5, for example). However, when there is more than one hazard and thus more than one system safety requirement, the competing demands of these multiple requirements can be used to reduce the number of possible assignments. In the more abstract example above, there is in fact only one possible assignment (there are other valid ones, but they are redundant), though this is definitely not apparent at first sight.

Firstly, each of the four hazards has its own assigned ASIL:

- F1(O) Omission of output from F1, with ASIL D

- F1(C) Commission of output from F1, with ASIL A

- F2(O) Omission of output from F2, with ASIL C

- F2(C) Commission of output from F2, with ASIL A

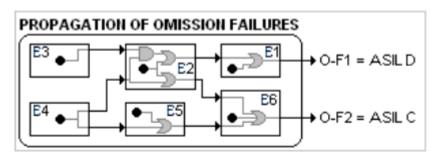

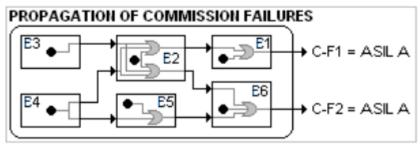

As stated above, due to the connecting failure logic amongst the six sub-elements in the system, it transpires that there is only one real possible ASIL assignment. To see why, it is necessary to go into more detail. First, the causes of each hazard must be explored. The failure logic of the system is better shown below in Figure 7. In this figure, the propagation of failure causes for the omission failures and propagation of failure causes for the commission failures are shown separately. The black dots represent internal failures of the components they are in and are numbered according to the element they are in, thus failure event FE3 is a failure of element E3. Furthermore, for the sake of simplicity, we assume that omission failures only cause other omission failures and commission failures only cause other commission failures, though in the general case this is not always true, and failures of one type can cause failures of another type.

Figure 7 - Failure logic in the example system

As an example, take F1(O). Its initial cause is an omission from component E1, which uses OR logic - it can be caused either by an internal failure mode FE1 (the black circle) or by an omission of input. Since FE1 is directly capable of causing the output failure F1(O), it receives ASIL D. Omission of input to E1 is caused solely by an omission from E2, which in turn is caused either by an internal failure mode (FE2) or by an omission of input at *both* inputs. FE2 therefore receives ASIL D as well. However, omission of input to E2 is caused by a conjunction of omissions from both E3 and E4, so they each contribute some share of the ASIL D. There are five possible assignments for these two components:

| • | FE3 = QM (0), FE4 = D (4) | Total = 4 (D) |

|---|---------------------------|---------------|

| • | FE3 = A (1), FE4 = C (3)  | Total = 4 (D) |

| • | FE3 = B (2), FE4 = B (2)  | Total = 4 (D) |

| • | FE3 = C (3), FE4 = A (1)  | Total = 4 (D) |

Assignments where ASILs for both FE3 and FE4 are *more* than sufficient to meet the safety requirement, e.g. FE3 = ASIL C and FE4 = ASIL C, are also possible, but not considered unless necessary (i.e. unless both FE3 and FE4 directly contribute to an ASIL C hazard somewhere). Furthermore, since both FE3 and FE4 can contribute to the system failure, neither should really be allocated QM according to ISO 26262. However, by assigning each ASIL an appropriate value (e.g. D = 4, A = 1), it can be seen that all of these alternatives are equivalent to ASIL D when summed and so all are at least theoretically valid.

Total = 4 (D)

To reduce the number of combinations, it is necessary to look at the other hazards and their ASILs. It is determined through decomposition that commission of F1 (i.e., F1 (C)), with ASIL A, is caused by any internal failure mode of E1, E2, E3, and E4; thus each of those failure modes (FE1-FE4) must be at least ASIL A. That firmly eliminates two possibilities for FE3 and FE4 (namely, where one is ASIL D and the other is QM). Next, decomposition of F2(O) – with ASIL C – shows that there are four possible causes: FE2, FE4, FE5, or FE6. Each therefore requires a minimum of ASIL C. This removes two more possibilities from the list, leaving only one possible allocation: FE3 = ASIL A, FE4 = ASIL C.

In this way, ASIL decomposition using multiple hazards allows us to determine which failure modes contribute to which hazards, and by process of elimination, determine what ASIL each

FE3 = D (4), FE4 = QM (0)

failure mode should have (or, more frequently, determine a set of many possible ASIL allocations for those failure modes). The new algorithm developed in MAENAD (and originated in ATESST2) supports this kind of multi-hazard ASIL decomposition process.

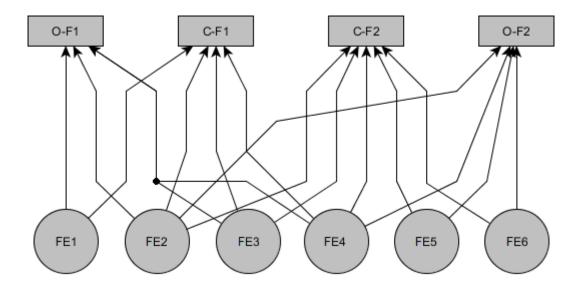

#### 2.4.2.2 Using FTA as the basis of ASIL decomposition

Before ASILs can be decomposed, it is necessary to understand which parts of the system are independent and whether or not failures can cascade from one element to another. FTA - particularly component-based FTA like that performed by the HiP-HOPS tool (see Section 3.3.2) - is ideal for this, as a fault tree naturally analyses the propagation and combinations of failures throughout a system. The failure logic in the previous example, as shown in Figure 7, is effectively a set of interconnected fault trees: there are four top events (one for each hazard), but only six basic events (the internal failures of the six components). Each failure can therefore contribute to more than one top event, and it is this fact that is the basis of the multiple-hazard ASIL decomposition. The actual fault trees used are presented (in a rather unconventional interconnected form) in Figure 8.

Looking at the figure, it is possible to see how FE2 for example contributes to all four top events; in this case it would have to receive the highest of the top event ASILs (in this case, ASIL D). FE4 contributes to all four events, but one of them (O-F1) is via an AND gate, meaning that it is now subject to multiple constraints:

- It must have at least the same ASIL as C-F1 (A)

- It must have at least the same ASIL as C-F2 (A)

- It must have at least the same ASIL as O-F2 (C)

- Together with FE3, it must add up to the same ASIL as O-F1 (D)

Taken together, the most likely assignment here is to give FE4 ASIL C and then FE3 can have ASIL A, assuming it is not subject to any higher ASIL from different branches.

This system of overlapping ASIL constraints both adds complexity to the process and also adds value to it, since it allows us to reduce the total number of possible ASIL assignments (and in general, there are a lot). Furthermore, fault trees are one of the best ways of being able to model these overlapping constraints. Other techniques that deal only with single failures, like FMEAs, would be unsuitable for this as they cannot show the effects of conjunctions of failures, which is what makes decomposition possible.

In particular, compositional FTA (the HiP-HOPS approach) - in which the system fault trees (e.g. O-F1, C-F2 etc.) are synthesised by connecting the individual fault trees of the separate components (E1, E2 etc.) - is ideally suited for this and can readily create such fault trees.

Figure 8 - Interconnected FTs

In fact, FTA has an even bigger advantage in that what really matters are the minimal cut sets of the fault trees, i.e., the set of smallest possible combinations of basic events capable of causing the system failures (or hazards in this case). Since these are calculated directly by FTA, it is much easier to see the relationships between the basic events and the hazards they cause. For example (where the black dot represents a conjunction):

Figure 9 - Direct connections from basic events to hazards

On the basis of these minimal cut sets, we can allocate the hazards' ASILs directly to the cut sets, and then (if applicable) decompose them across the basic events that comprise those minimal cut sets.

#### 2.4.2.3 Decomposition Algorithm

The first step in the algorithm is to ensure that a set of *safety constraints* (i.e., ASILs applying to one or more output failures in the system) have been defined. These safety constraints, and their assigned ASILs, may have been produced as a result of a prior hazard analysis of the system (in which case the ASILs are derived from the hazardous events and safety goals) or may simply be assumed in the case of a SEooC. These safety constraints (and their ASILs) constitute one input to the algorithm; the other is a logical representation of the failure behaviour of the system, e.g. as described by the results of a fault tree analysis. Typically, one fault tree must be generated for each safety constraint, modelling the causes of the *constrained output failure* (COF).

Thus:

#### Inputs:

- Set of safety constraints, each of which should have an ASIL and a fault tree generated for its constrained output failure.

- Set of minimal cut sets (from the fault trees modelling the logical failure behaviour of the system) that cause the constrained output failures.

## **Outputs:**

• Set of possible ASIL assignments for all basic events in the form of *Safety Requirement Assignments*; there will typically be many of these.

The important entities in the algorithm are as follows:

## • Safety Constraint (SC)

Represents an ASIL applied to an output failure (malfunction) of an element of the system (or of the system itself). The output failure becomes the top event of a fault tree and its assigned ASIL serves as the basis of the decomposition.

#### Cut Set (CS)

Cut sets are the results of the FTA. They contain sets of basic events (BEs) and are responsible for causing the COFs.

## • Basic Event (BE)

A basic event (or BE) is an individual component or function failure in the system. Individually it may or may not have any effect on the system, but if it is a member of a cut set, it will contribute to at least one COF. Basic events are the primary targets for assignment of ASILs from the safety constraints they affect (whether directly or indirectly). When allocated an ASIL from a Derived Safety Requirement (or DSR - see next), the DSR also 'locks' them at that ASIL so that only DSRs with higher ASILs can change them until the original DSR releases the lock. This prevents BEs being incorrectly allocated lower ASILs, so a BE can always be allocated a higher ASIL, but never a lower one.

#### Derived Safety Requirement (DSR)

In the context of the algorithm, a Derived Safety Requirement describes an ASIL value that a set of basic events (i.e., a minimal cut set) must implement to achieve required system risk levels. DSRs are produced by the ASIL decomposition and allocation process. More than one DSR may apply to the same basic event, in which case the highest ASIL from all the DSRs that apply to that BE is used.

#### Safety Requirement Allocation (SRA)

A Safety Requirement Allocation is the output of the algorithm and represents a set of possible ASIL assignments to the basic events of the system that will meet the initial safety requirements as defined by the Safety Constraints. Typically many SRAs will be generated.

The algorithm itself is described in pseudo code below.

## **ASIL Decomposition Algorithm**

```

for each safety constraint (SC):

for each cut set (CS) in SC:

Generate new 'Derived Safety Requirement' or DSR (contains events and ASIL from SC)

Sort the DSRs - least basic events first, then highest ASIL first.

Recurse for every derived safety requirement (DSR):

while there remain unallocated DSRs:

if this DSR applies to only one basic event:

Assign DSR's ASIL to the only BE

If the assignment succeeded and BE's ASIL is >= DSR's ASIL:

BE is locked at that ASIL by this DSR {*1*}

Recurse for next DSR

}

else

Recurse for next DSR

Unlock BE

else (DSR applies to more than one BE)

Iterate through all possible assignments of DSR's ASIL for these BEs {*2*}

If this assignment meets the DSR's ASIL:

Attempt to assign ASILs to BEs {*1*}

If it worked and the DSR is achieved, recurse for next DSR

}

}

Unlock all BEs

}

}

```

```

else (there are no remaining DSRs)

{

Store the current configuration of BEs & ASILs as one possible assignment (SRA) {*3*}

Backtrack up recursion stack to try new combinations

}

```

The above algorithm describes the overall process, but it is worth describing certain aspects (numbered) in more detail:

## 1) Allocating ASILs to Basic Events

The key to the algorithm is the priority locking mechanism used by the Basic Events. When a Derived Safety Requirement attempts to allocate an ASIL to a Basic Event, this operation only succeeds if one of the following is true:

- The Basic Event is not locked

- The BE is locked, but the DSR is the one who holds the most recent lock

- The DSR's ASIL is higher than the ASIL of the current lock holder

When the assignment succeeds, the DSR that allocated it locks the Basic Event and registers itself with the Basic Event as the current lock holder (the BE retains a stack of lock holders). This ensures that a Basic Event can only be given an equal or higher ASIL than the one it currently holds, never a lower one (for this purpose, an ASIL is equated to a numeric value, e.g. A = 1, B = 2, C = 3 etc.). If the DSR's ASIL is lower, then the new assignment fails and the algorithm will potentially backtrack to try a new combination of assignments.

## 2) Iterating through possible combinations of assignments for a set of BEs

There can be many possible combinations of assignments for any given set of BEs. The theoretical maximum number of permutations is given by the formula:

$$p = (m + 1)^n$$

where p is the number of permutations, m is the maximum ASIL value (4 in this case, but then we add 1 because we include 0/QM), and n is the number of basic events constrained by the SR. So for a 2 event cut set, there is a maximum of 25 possible assignments; for 3 events, there are 125.

Each assignment is determined mechanically, so it will start with e.g. 0/0/0, then 0/0/1, then 0/0/2 etc., and assign each of these values to the targets. However, not all of these permutations are used. Firstly, those that do not meet the current DSR are immediately discarded; for example, if the required ASIL value is 3 and the current permutation is 0/0/1 (sum = 1, which is less than 3), this would not even be tested. Secondly, it is possible for one or more of the BEs to already have been locked by earlier DSRs; in these cases, permutations in which those BEs have lower ASIL values are not even enumerated and are thus skipped. This helps to improve the efficiency of the process. Note however that assignments that *more* than meet the DSR are kept at this stage, so 1/2/3 (total = 6) would be kept even if the required total was only 3.

#### 3) Storing possible assignments

Once all safety requirements have been examined and all of their ASILs assigned to basic events in such a way that all of the DSRs are still being achieved (i.e., no combination of basic event ASILs add up to less than the ASILs of any of the hazards they cause), that assignment of ASILs

and corresponding basic events is stored as a Safety Requirement Allocation (SRA). Safety Requirement Allocations are nothing more than dictionaries using basic events as keys and allocated ASILs as their corresponding values.

However, there can be a great many Safety Requirement Allocations and it is important to cut down the number wherever possible. Therefore, we can do some redundancy checking at this stage. The main form of checking is to see whether one allocation renders another redundant. For example, if basic event BE1 is assigned ASIL C and BE2 is assigned ASIL B, and that is a valid allocation (i.e., all DSRs are met), then an allocation in which BE1 is assigned ASIL D and BE2 is assigned ASIL C would be redundant. To borrow an optimisation term, it is *dominated* by the first allocation. It is important to note that this is only the case if *all* of the ASILs are higher than (or equal to) another allocation; if BE1 was ASIL B and BE2 was C, then it would not be redundant.

To extend the example, assuming two BEs in total, BE1 and BE2, and four allocations added in the following order:

|    | BE1   | BE2   | TOTAL |                                         |

|----|-------|-------|-------|-----------------------------------------|

| 1) | C (3) | B (2) | D (5) |                                         |

| 2) | C (3) | A (1) | D (4) | - Makes #1 redundant, so #1 is removed  |

| 3) | D (4) | A (1) | D (5) | - Is made redundant by #2, so not added |

| 4) | B (2) | B (2) | D (4) | - Is <i>not</i> redundant               |

In this case there are two non-redundant allocations (#2 and #4) and two redundant ones (#1 and #3). By keeping the number of allocations to a minimum throughout the process, we reduce the amount of checking we need to do when we add later SRAs. Even so, this can still be an expensive process, as every new SRA needs checking against every existing SRA. There are potential optimisations possible here, however.

#### 2.4.2.4 Example

To see how the algorithm works when applied to the previous 6-component example in Figure 6, we can work through the algorithm manually (albeit skipping the sorting for illustrative purposes).

First, we need a list of minimal cut sets, together with the hazards they cause and associated ASILs:

```

O-F1 - ASIL D (4)

{FE1} {FE2} {FE3.FE4}

C-F1 - ASIL A (1)

{FE1} {FE2} {FE3} {FE4}

O-F2 - ASIL C (3)

{FE2} {FE4} {FE5} {FE6}

C-F2 - ASIL A (1)

{FE2} {FE3} {FE4} {FE5} {FE6}

```

We can now generate a set of Derived Safety Requirements, one for each cut set. This tells us what different ASILs apply to each cut set. We can represent these in the form of equations, for clarity:

| {FE1=4} | {FE2=4} | $\{FE3 + E4=4\}$ |         |         |

|---------|---------|------------------|---------|---------|

| {FE1=1} | {FE2=1} | {FE3=1}          | {FE4=1} |         |

| {FE2=3} | {FE4=3} | {FE5=3}          | {FE6=3} |         |

| {FE2=1} | {FE3=1} | {FE4=1}          | {FE5=1} | {FE6=1} |

Next we have to recurse through all of these DSRs, attempting to lock the Basic Events at each point. To make it clear what's happening, the status of the BEs (and their locks) is shown at each point. Bold event values indicate a successful lock; italic values indicate failure. We shall only examine the first full recursion.

|          | FE1    | FE2    | FE3 | FE4 | FE5 | FE6 |

|----------|--------|--------|-----|-----|-----|-----|

| 1. FE1=4 | 4 (#1) | -      | -   | -   | -   | -   |

| 2. FE2=4 | 4 (#1) | 4 (#2) | -   | -   | -   | -   |

3. For 3, we have two events, so we need to iterate through all permutations that add up to at least 4. We shall consider these separately.

| 3a: | FE3=0, | FE4=4: |

|-----|--------|--------|

|-----|--------|--------|

|           | 4 (#1) | 4 (#2) | 0 (#3a) | 4 (#3a) | -       | -       |

|-----------|--------|--------|---------|---------|---------|---------|

| 4. FE1=1  | 4 (#1) | 4 (#2) | 0 (#3a) | 4 (#3a) | -       | -       |

| 5. FE2=1  | 4 (#1) | 4 (#2) | 0 (#3a) | 4 (#3a) | -       | -       |

| 6. FE3=1  | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | -       | -       |

| 7. FE4=1  | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | -       | -       |

| 8. FE2=3  | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | -       | -       |

| 9. FE4=3  | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | -       | -       |

| 10. FE5=3 | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | 3 (#10) | -       |

| 11. FE6=3 | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | 3 (#10) | 3 (#11) |

| 12. FE2=1 | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | 3 (#10) | 3 (#11) |

| 13. FE3=1 | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | 3 (#10) | 3 (#11) |

| 14. FE4=1 | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | 3 (#10) | 3 (#11) |

| 15. FE5=1 | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | 3 (#10) | 3 (#11) |

| 16. FE6=1 | 4 (#1) | 4 (#2) | 1 (#6)  | 4 (#3a) | 3 (#10) | 3 (#11) |

|           |        |        |         |         |         |         |

We have now run out of DSRs and so can store this as one possible SRA for the system:

As it turns out, the next recursion gives us a better solution. When we backtrack, we go back to the last time we have more than one basic event in a SR and were iterating through possible permutations. In this case, that SR was #3, so we can skip back to there and continue with #3b instead:

| 2h· | : FE3= | 1 🗆   | ⊏∥ニつ・ |

|-----|--------|-------|-------|

| OU. |        | I. FI | C4=0. |

| 4 (#1) | 4 (#2)                                                                                            | 1 (#3b)                                                                                                                                                                                                                                                                                                                                                             | 3 (#3b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

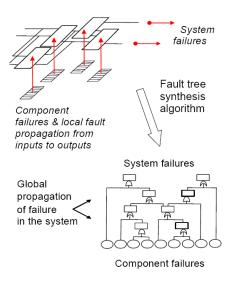

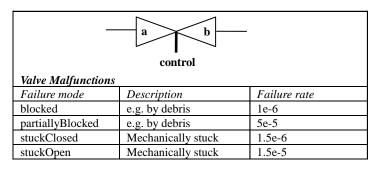

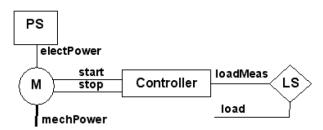

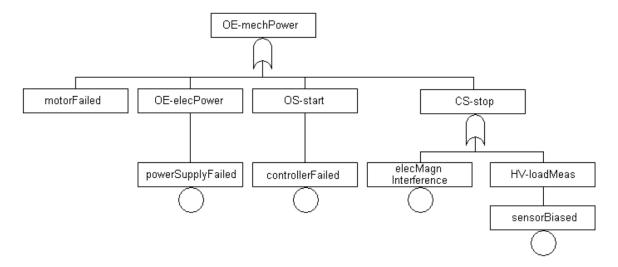

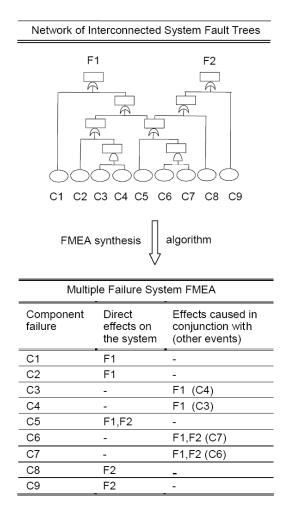

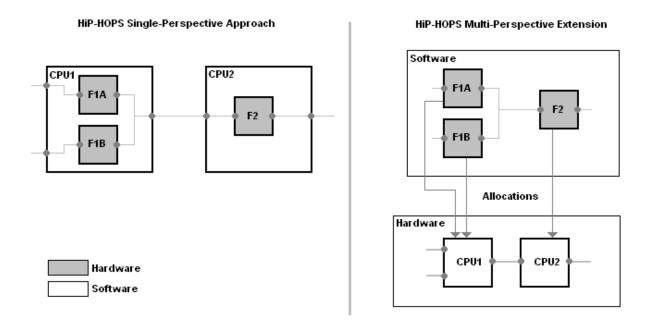

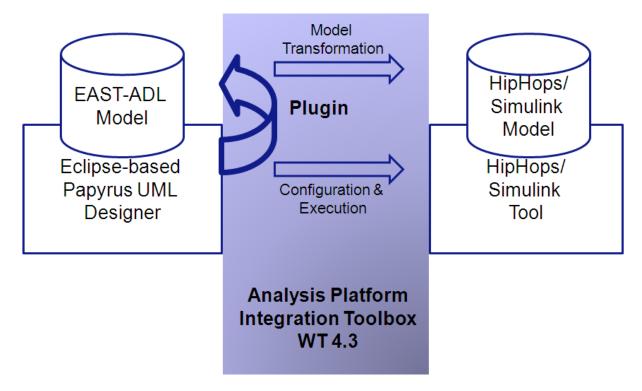

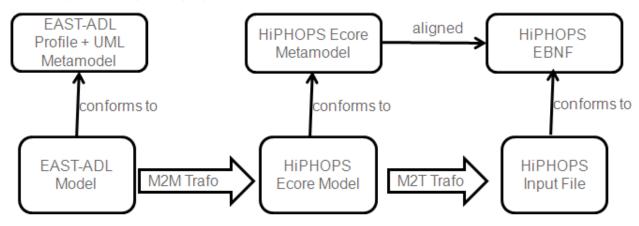

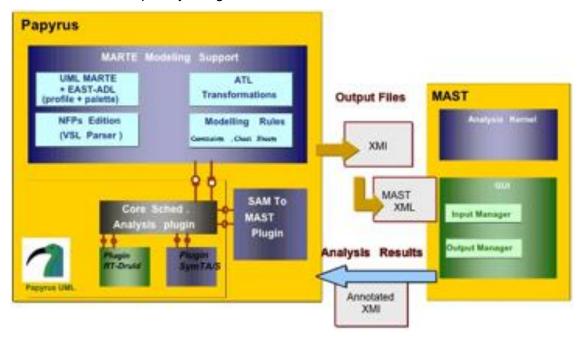

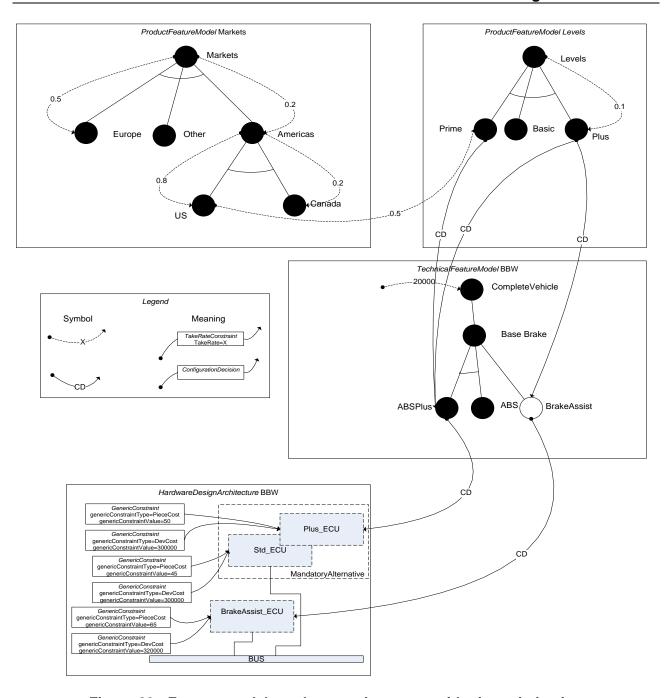

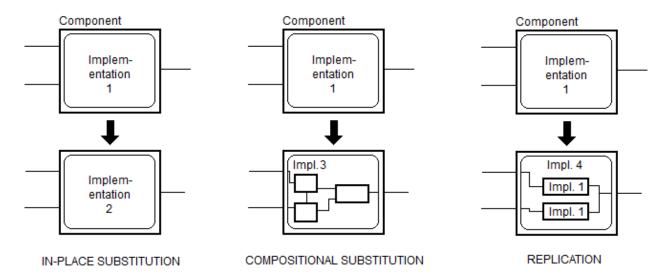

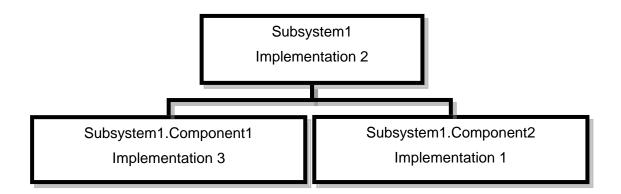

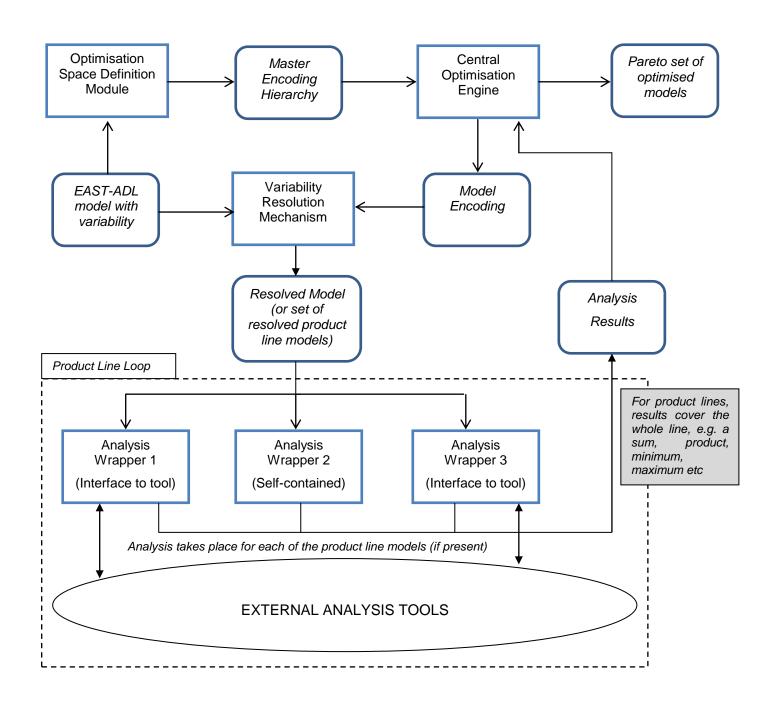

| 4 (#1) | 4 (#2)                                                                                            | 1 (#3b)                                                                                                                                                                                                                                                                                                                                                             | 3 (#3b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |