### **DIWINE**

#### Contract No. CNET-ICT-318177

# **Evaluation of practical system constraints D5.12**

Contractual date: M21

Actual date: M21

Authors: David HALLS, William THOMPSON, Stefano GALIMBERTI,

Stefano SAVAZZI, Tomáš HYNEK, Jan SÝKORA, Justin P. COON

Participants: TREL, P+F, PdM, CTU, UOXF

Work package: WP5

Security: Public

Nature: Report

Version: 1.0

Number of pages: 76

#### Abstract

Detailed assessment of all HW impairments and constraints of the demonstrator platform that affects the algorithms performance and should be reflected in the algorithm design; includes practical measurements of the HW induced effect on performance which should serve as feedback for the algorithm amendment.

#### Keywords

Synchronisation, scalability, processing delay, real-time, propagation, USRP, relay, WirelessHART, TSMP, mesh network, safety critical, industrial wireless.

## **Contents**

| Ab | brevi | iations  |                                                                                  | 5  |  |  |

|----|-------|----------|----------------------------------------------------------------------------------|----|--|--|

| 1  | Exc   | ecutive  | summary                                                                          | 7  |  |  |

| 2  | Sm    | art me   | ter network hardware demonstrator                                                | 9  |  |  |

|    | 2.1   | Intro    | luction                                                                          | 9  |  |  |

|    | 2.2   |          |                                                                                  |    |  |  |

|    |       | 2.2.1    | Bandwidth limitations, host processing, multiplexing and centre frequency        | e  |  |  |

|    |       | 2.2.2    | Air interface, channel estimation and DIWINE pilots                              | 13 |  |  |

|    |       | 2.2.3    | Half-duplex constraint                                                           | 20 |  |  |

|    |       | 2.2.4    | Processing delay                                                                 | 20 |  |  |

|    |       | 2.2.5    | Length of payload                                                                | 24 |  |  |

|    |       | 2.2.6    | Multiple access strategy from gateway to destination nodes                       | 24 |  |  |

|    |       | 2.2.7    | Time of flight and asynchronism                                                  | 25 |  |  |

|    |       | 2.2.8    | System under test                                                                | 27 |  |  |

|    |       | 2.2.9    | Node visibility                                                                  | 28 |  |  |

|    | 2.3   | Distri   | ibuted network synchronisation related constraints                               | 29 |  |  |

|    |       | 2.3.1    | Carrier frequency                                                                |    |  |  |

|    |       | 2.3.2    | Timing offsets                                                                   | 35 |  |  |

|    |       | 2.3.3    | Scheduling and half-duplex constraints                                           | 36 |  |  |

|    |       | 2.3.4    | Sampling frequency                                                               | 39 |  |  |

|    |       | 2.3.5    | Processing delay                                                                 | 41 |  |  |

|    |       | 2.3.6    | Convergence time                                                                 | 41 |  |  |

|    |       | 2.3.7    | Node visibility                                                                  | 42 |  |  |

|    |       | 2.3.8    | Time of flight                                                                   | 42 |  |  |

|    | 2.4   |          | ration of wireless network coding and distributed network aronisation algorithms | 44 |  |  |

|    | 2.5   | Over     | view of potential advanced prototype limitations                                 | 45 |  |  |

| 3  | Cri   | tical in | dustrial monitoring and control demonstrator                                     | 46 |  |  |

|    | 3.1   |          | luction                                                                          |    |  |  |

|    | 3.2   |          | C architecture overview                                                          |    |  |  |

|    | ۷.۷   | 3.2.1    | Layered network architecture                                                     |    |  |  |

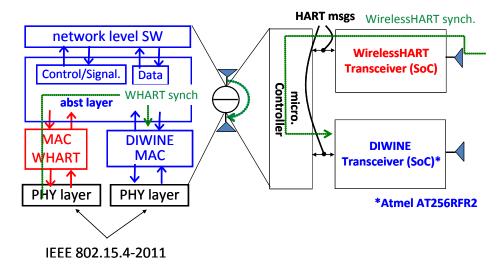

|    |       | 3.2.1    | Dual-RAT implementation                                                          |    |  |  |

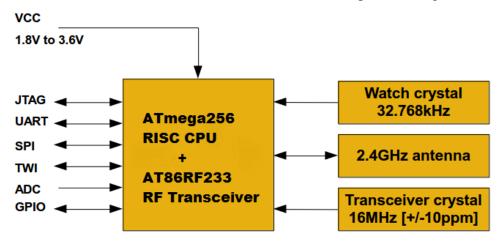

|    |       | 3.2.2    | DIWINE radio module hardware architecture                                        |    |  |  |

|    |       | 5.4.5    | DITTELL TAGIO INOGGIC HATCHWAIC AICHICCEUIC                                      |    |  |  |

|     |        | 3.2.4      | DIWINE radio module software architecture         | 48 |

|-----|--------|------------|---------------------------------------------------|----|

|     | 3.3    | CIMO       | C limitations and constraints                     | 49 |

|     |        | 3.3.1      | Processing-power related constraints              | 49 |

|     |        | 3.3.2      | Dual-RAT RF constraints                           |    |

|     |        | 3.3.3      | Memory resources limitations                      | 59 |

|     |        | 3.3.4      | Response-time and latency constraints             | 60 |

|     |        | 3.3.5      | MAC-related constraints                           | 61 |

|     |        | 3.3.6      | Energy-consumption constraints                    | 63 |

|     |        | 3.3.7      | Wi-Fi coexistence constraints                     | 64 |

| 4   | Co     | nclusio    | ns                                                | 69 |

|     | 4.1    | SMN        | hardware demonstrator                             | 69 |

|     | 4.2    | CIMO       | C hardware demonstrator                           | 70 |

| Bil | oliogr | aphy       |                                                   | 71 |

| 5   | Ap     | pendix     | A – CIMC detailed estimations                     | 73 |

|     | 5.1    | -<br>Matri | ix multiplication algorithm                       | 73 |

|     |        | 5.1.1      | Overview                                          |    |

|     |        | 5.1.2      | Simpler implementation                            | 73 |

|     |        | 5.1.3      | Optimised implementation                          |    |

|     |        | 5.1.4      | Results                                           |    |

|     | 5.2    | Perfo      | ormance improvements with Cortex M0+ architecture |    |

|     |        | 5.2.1      | Overview                                          |    |

|     |        | 5.2.2      | Performance improvements                          | 75 |

|     |        | 5.2.3      | Power consumption improvements                    |    |

|     |        |            |                                                   |    |

#### **Abbreviations**

AF Amplify-and-Forward

BER Bit Error Rate

BSLD Block Structured Layered Design

BSPK Binary Phase Shift Keying

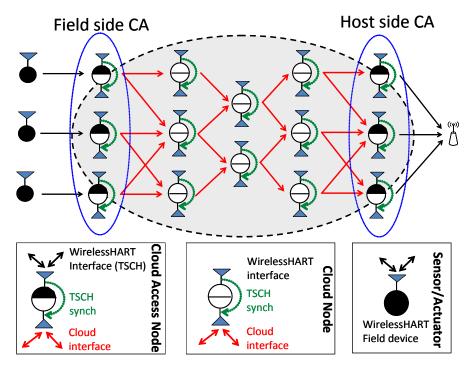

CA Cloud Access

CAZAC Constant Amplitude Zero Autocorrelation

CFO Carrier Frequency Offset

CIMC Critical Industrial Monitoring and Control

CIP Cloud Initialisation Procedure

CP Cyclic Prefix

CPU Central Processing Unit CRB Cramér-Rao Bound

CRC Cyclic Redundancy Check

CSE Channel State Estimation

CSI Channel Station Information

CSMA Carrier Sense Multiple Access

DF Decode-and-Forward

DLA Distributed Learning Algorithm

DSSS Direct-Sequence Spread Spectrum

FCS Frame Check Sequence

FDMA Frequency Division Multiple Access

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

GPS Global Positioning System

GPSDO GPS Disciplined Oscillator

GSM Global System for Mobile Communications

GW Gateway

HIS Hierarchical Side Information HNC Hierarchical Network Codes

HW Hardware

ISM Industrial, Scientific and Medical

LDPC Low Density Parity Check

LoS Line-of-Sight

LQI Link Quality Indicator

MAC Multiple Access Channel; Media Access Control

MAC Medium Access Control

MIMO Multiple Input Multiple Output

MIPS Microprocessor without Interlocked Pipeline Stages

MISO Multiple-Input Single-Output

MSE Mean Squared Error

MTU Maximum Transmission Unit

NIC Network Interface Card

NL Network Layer

NSI Network State Information

OFDM Orthogonal Frequency Division Multiplexing

P2P Peer-to-Peer

PER Packet Error Rate PHY Physical Layer

PL Payload

PLL Phase Locked-Loop

ppb part per billionppm parts per millionPPS Pulse Per SecondQoS Quality of Service

RAM Random Access Memory RAT Radio Access Technology

RF Radio Frequency

RISC Reduced Instruction Set Computing

RSS Received Signal Strength

RSSI Received Signal Strength Indicator

SF Synchronisation Frame

SIR Signal-to-Interference Ratio

SLS System-Level Simulator

SMN Smart Meter Network

SoC System on Chip SPB Samples per Block SPP Samples per Packet

SW Software

TA Timing Advance

TCXO Temperature Compensated Crystal Oscillators

TDMA Time Division Multiple Access

TL Transport Layer TO Timing Offset

TSCH Time Synchronised Channel Hopping

UDP User Datagram Protocol

USRP Universal Software Radio Peripheral WPLNC Wireless Physical Layer Network Coding

ZF Zero-Forcing

#### 1 Executive summary

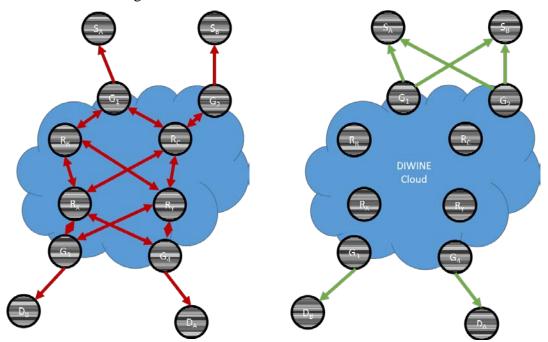

This report evaluates the limitations and constraints of both the Smart Meter Network (SMN) hardware demonstrator and the Critical Industrial Monitoring and Control (CIMC) hardware demonstrator.

The first half the SMN section looks at limitations relating to the WPLNC algorithms. A sampling rate of 1 MS/s is chosen along with the use of Orthogonal Frequency Division Multiplexing (OFDM) with 64 bins at a centre frequency at 2.4 GHz. The DIWINE air interface is updated, including the design and layout of the PiCSE and PiHRC pilots. Some testing is also performed. The half-duplex constraint is discussed and the processing delay of the system is shown to be small enough to allow real-time operation with only basic baseband processing. Once the processing of either the DIWINE algorithms is included, however, the processing delay becomes too long and the system runs in a quasi-real-time fashion. The maximum length of packets is discussed and the multiple access strategy for the final gateway nodes to the destinations is chosen as Time Division Multiple Access (TDMA). Time of flight is shown not to be an issue and there will be minimal asynchronism in the system in the external synchronisation case, and the use of OFDM will mitigate the impact. The system under test is detailed and a maximum of a 9-node setup will be implemented. Node visibility is highlighted as being a minor issue that affects one of the algorithms, but can be circumvented using message passing.

The second half of the SMN section details the hardware limitations relating to the synchronisation phase of the network. This looks into the frequency stability and suitability of two reference oscillators. The modifications of the algorithm to meet the half duplex constraint are also discussed, as well as the need to use a higher sampling rate in the synchronisation phase of 4 MS/s to improve the offset estimation accuracies. Limits on the maximum separation of connected nodes are also detailed based upon the signals' time-of-flight. Discussion on the impact on the limitations and constraints, were an application specific hardware solution to be developed, concludes the SMN section.

The CIMC hardware demonstrator limitations and constraints are highlighted in this report with respect to the relevant industrial scenario and application cases. The material presented in this deliverable provides a detailed description of the demonstrator hardware and software capabilities and provides guidelines to tailor the DIWINE algorithms and minimise implementation-related issues. The CIMC demonstrator implements a dual-processor, and dual radio access architecture, with one section dedicated to the support of DIWINE-identified algorithms while the other ensures the compatibility with the industry standard WirelessHART. The two radio modules are designed to cooperate during synchronisation and topology control sessions. In particular, the DIWINE section ensures a flexible PHY and MAC layer implementation. It provides full support to industry-standard IEEE 8021.5.4 air-interface with extended functionalities to allow for good real-time capability, low energy consumption and software-defined PHY transmission modes. The deliverable highlights the main CIMC expected hardware and software limitations and constraints, with respect to the low-power core processor processing power, PHY, MAC and application layer limitations

for target algorithms/scenarios and interference limitations in unlicensed spectrum sharing scenarios.

#### 2 Smart meter network hardware demonstrator

#### 2.1 Introduction

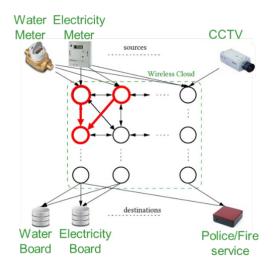

This section of the report provides details on the Smart Meter Network (SMN) hardware demonstrator and evaluates the associated limitations and constraints. The SMN hardware demonstrator is based on the Universal Software Radio Peripheral (USRP) hardware platform combined with the GNU Radio software platform. The SMN hardware demonstrator is made up of a network of USRPs each connected to a 'host' computer running GNU Radio which is an open-source software environment. The contents of the report are vital for the design of the algorithms in WP3 and WP4, such that the algorithms are run within the inherent constraints of the hardware testbed.

The section devoted to the SMN is split into two subsections, devoted to the two main areas of the DIWINE paradigm that will be implemented: Wireless Physical Layer Network Coding (WPLNC) and distributed network synchronisation. The first looks at the limitations and constraints of the Hardware (HW) testbed that are specific to WPLNC. It is decided that a sampling rate of 1 MS/s is sufficient for the implementation of the algorithms, and allows 2 USRPs to be controlled from one laptop. The use of Orthogonal Frequency Division Multiplexing (OFDM) with 64 bins at a centre frequency in the Industrial, Scientific and Medical (ISM) band at 2.4 GHz is also appropriate. Successful testing of the DIWINE pilots is shown. The half-duplex constraint is reinforced; both of the WPLNC algorithms that are to be implemented adhere to this restriction. Once the processing of either WPLNC algorithm is included in the system, the processing delay becomes too long and the system runs in a quasi-real-time fashion.

The length of packets is restricted by buffer sizes in GNU Radio, however they are also limited by the necessity for regular synchronisation frames, so the limit caused by GNU Radio is not a problem. It is shown that the time of flight issue will not affect the system in the indoor testing environment. There should also be minimal asynchronism in the system, especially with the aid of external synchronisation, and using OFDM should mitigate any issues. The system under test entails a maximum of a 9-node setup. Node visibility will be highlighted as being a minor issue that affects one of the WPLNC algorithms but it can be circumvented by enabling message passing in GNU Radio.

The second half of the SMN section looks at limitations related to the distributed synchronisation algorithm. Hardware impairments of the USRPs focuses on the reference oscillators. It is shown that the internal oscillator suffers from significantly more phase drift and frequency instability compared to Ettus' GPSDO. The benefits of using the GPSDO as the reference oscillators is shown, highlighting that the objective of the testbed should be to demonstrate the core DIWINE principals rather than be a final implementation solution. Due to the half-duplex constraint, the scheduling of the synchronisation algorithm has been adapted so that all nodes synchronise to multiples of  $64\,\mu s$ , rather than a single global time. Other modifications to improve the algorithm are discussed, such as the increase in symbol rate and windowing the data to cope with noncomplete capture of synchronisation frames.

The limitations of the system would be relaxed/improved somewhat if an application-specific implementation were used as detailed in Section 2.5. These include the host processing (which would not be required at all), processing delay and packet lengths. The system under test would expand which could lead to time-of-flight and asynchronism issues as well as a change in the node visibility issues. Parameters such as the bandwidth, the half-duplex constraint, the use of OFDM in the ISM band, and the DIWINE air interface would not change, however. With regard to the distributed synchronisation algorithm, the limitations would remain mostly unchanged, although the use of a device with a higher quality crystal oscillator would significantly improve performance.

#### 2.2 Wireless physical layer network coding related constraints

## 2.2.1 Bandwidth limitations, host processing, multiplexing and centre frequency

As reported in [1] an OFDM solution is employed with  $N_{FFT} = 64$  subcarriers. The initial OFDM parameters, including the initial sampling rate are shown in Table 2. The use of OFDM offers scalability, whereby the system bandwidth and Fast Fourier Transform (FFT) size could theoretically be scaled up from these values, although the current values are thought fit for purpose. CTU concur with TREL that since the proposed DIWINE algorithms aim to achieve 'proof-of-concept' the bandwidth of current implementation is sufficient for all the proposed algorithms to show their properties.

| Parameter               | Value   |

|-------------------------|---------|

| FFT size, $N_{FFT}$     | 64      |

| Cyclic prefix length    | 16      |

| Sampling rate           | 1 MS/s  |

| Centre frequency, $f_c$ | 2.4 GHz |

Table 1: OFDM parameters

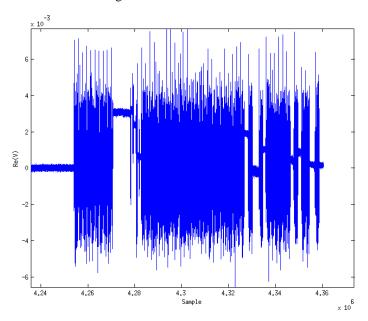

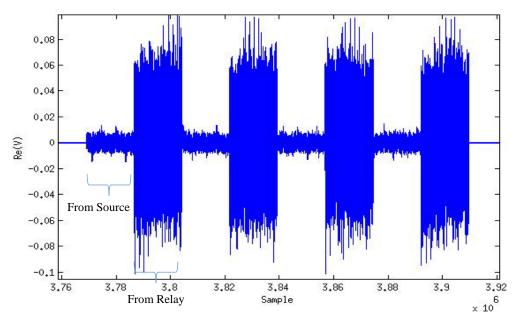

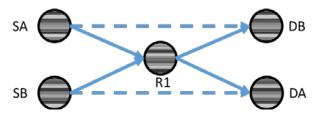

The current use of a sample rate of 1 MS/s is deemed sufficient to provide enough bandwidth for proof-of-concept of the two WPLNC algorithms: the Block Structured Layered Design (BSLD) and the Distributed Learning Algorithm (DLA). Using this sample rate allows two USRPs to be reliably controlled from one i7 Toshiba laptop. In the 2×1 Multiple-Input Single-Output (MISO) scenario (see Figure 1) controlling the two source USRPs from one laptop, and the destination USRP from another laptop, allows reliable free running. However, attempting to run all three USRPs from the same laptop causes occasional glitches in the received signal due to lack of resources. This results in a distorted received signal as illustrated in Figure 2, where the plot *should* show a continuous OFDM waveform as is present at the beginning and end of the trace.

Figure 1: 2×1 MISO scenario

Figure 2: Received waveform with insufficient resources

The reason for this problem is highlighted by the data in Table 2 which shows the approximate processor load of the receiver and transmitter laptops obtained using the 'top' command in Linux. The laptops have quad-core processors, so a total load of 400% is achievable and using the 'System Monitor' tool, it was seen that load balancing across the cores is achieved effectively in that each core was running \( \frac{1}{4} \) of the total load. The two numbers in the receiver (Rx) column in the table indicate when the receiver is running but idle and when it is receiving, i.e. processing data. It can be seen that even at 1 MS/s that the total load is approximately 375% if both transmitter and receiver were running on the same machine. This is not far below the available 400% showing why occasionally, during peak demand, resources are exhausted and glitches in the received waveform occur. The table also shows why sample rates higher than 1 MS/s are not reliably supported because the total required resources exceeds 400%. In the 4 MS/s case, there are not even enough resources for the receiver to run on its own when it is receiving data. Using a desktop i7 PC with an external Gigabit Ethernet port, it was found that all three USRPs could be run more reliably from the one machine, even though 400% of the resources were constantly being used.

| Sample Rate (MS/s) | Rx (idle % / active %) | Tx (%) |

|--------------------|------------------------|--------|

| 1                  | 200/250                | 125    |

| 2                  | 225/350                | 175    |

| 4                  | 335/-                  | 225    |

Table 2: Computational load

Although the processing power of the computers limits the number of USRPs that can be controlled by each laptop, the network capacity is not so restrictive. Each USRP requires 32 b to transfer each 16 b I/Q baseband message. This means that at 1 MS/s only 32 Mbit/s of Ethernet bandwidth is required by each USRP. As a result, up to 30 USRPs can be serviced by one Gigabit switch at 1 MS/s. This gives great flexibility in that up to 30 USRPs, i.e. a number in excess of the system under test in the DIWINE (see Section 2.2.8), can all be connected to the same wired switch to receive and transmit their baseband data.

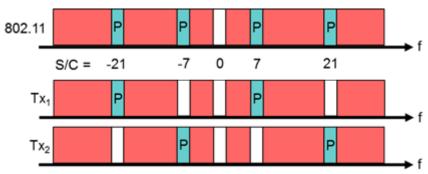

At a sample rate of 1 MS/s the cyclic prefix of 16 samples will be 16 µs, this is sufficient to avoid ISI in the indoor environment in which testing will take place where delay spreads will be of the order of nanoseconds. The initial 64 carrier OFDM system is also deemed sufficient for the WPLNC algorithms. Of the 64 subcarriers in each OFDM symbol there are currently 48 data subcarriers, a DC carrier, 11 guard carriers and four pilot carriers at -21, -7, 7 and 21. The pilot implementation is commensurate with IEEE 802.11 as shown in the top of Figure 3. These pilots, available in each payload symbol, can be used for channel estimation and tracking. In the 2×1 MISO system the pilots are orthogonalised as shown in the bottom of Figure 3, by allocating two of the four pilots to each source. This implementation clearly has limited scalability and although it can be used for the 2-relay butterfly (see Figure 4) where there are two nodes per stage, the more advanced scenarios will require non-orthogonal network synchronisation (see Section 2.3). Where external synchronisation is available, and the channel is relatively static these 'tracking' pilots are not utilised. In the absence of external synchronisation, however, they are used even when the channel is relatively static to correct for residual Carrier Frequency Offset (CFO) after estimation (as detailed in Section 1.2.7 of [1]).

Figure 3: Pilot structure for point-to-point 802.11 (top) and 2×1 MISO (bottom) systems

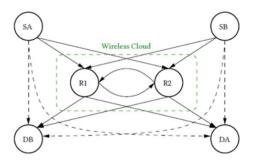

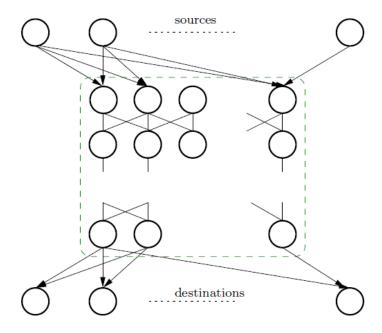

Figure 4: 2-relay butterfly without perfect intra-cloud coordination (S-RC-b)

The centre frequency of 2.4 GHz is suitable for the algorithms under test. Testing has been successfully performed simultaneously at 2.40, 2.45 and 2.48 GHz to allow coexistence of different algorithms and scenarios in the same testing environment. These frequencies have the advantage that they are in the ISM band so no special license is required, however, it suffers from the potential disadvantage of co-channel interference. This has not been found to be a problem in the TREL testing environment where there are no co-existing devices at 2.40, 2.45 or 2.48 GHz.

#### 2.2.2 Air interface, channel estimation and DIWINE pilots

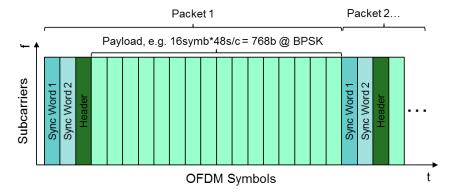

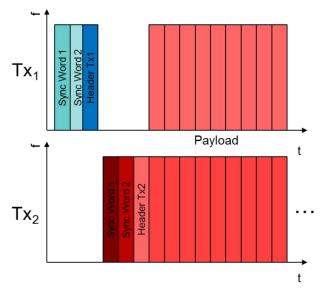

The frame structure for the initial point-to-point testing is shown in Figure 5. The preamble is made up of two synchronisation symbols followed by a header, and then the payload symbols. The two synchronisation symbols were used for timing synchronisation and coarse and fine frequency estimation as detailed in Section 1.2.5 of [1]. The header symbol contains information including packet number, payload length and modulation scheme.

Figure 5: Point-to-point frame structure

This was then expanded to work for the  $2\times1$  MISO system, which is the smallest possible building block of the overall system as shown in Figure 6. In the  $2\times1$  MISO system, in order that the synchronisation and channel estimation can be performed independently between  $Tx_1$  (SA) and DA, and  $Tx_2$  (SB) and DA, the preambles are transmitted orthogonally in time, as shown in Figure 7. As previously mentioned, in this scenario the pilots are also orthogonalised as shown in the bottom of Figure 3, by allocating two of the four pilots to each source, but this is not scalable. In the future

systems, if these pilots are not required due to the DIWINE distributed synchronisation techniques, they can be replaced by data subcarriers.

Figure 6: SMN vision

Figure 7: 2×1 MISO frame structure

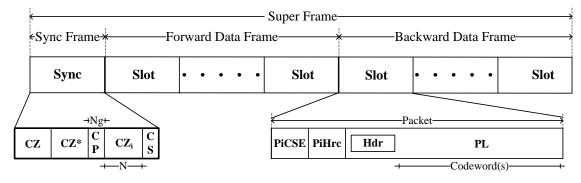

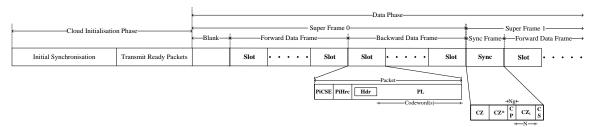

Figure 8: DIWINE super-frame structure

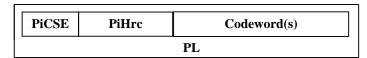

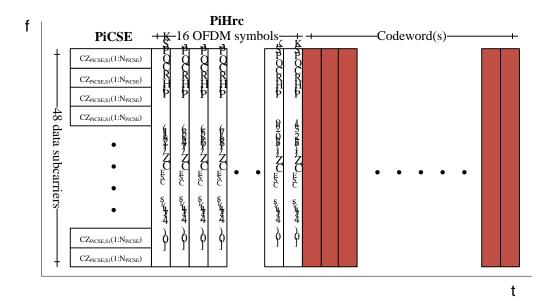

As an interim step to implementing the full DIWINE super-frame structure, shown in Figure 8<sup>1</sup>, testing has been performed by incorporating the DIWINE specific pilots (PiCSE used for Channel State Estimation (CSE) and PiHRC used for hierarchical information) into the Payload (PL) section of the existing 2×1 frame structure (Figure 7) thus resulting in a PL as in Figure 9. This means that the existing preamble can be used for CFO and TO estimation and correction (as well as using the existing channel estimation scheme as a benchmark to test the performance of the CSE using PiCSE).

Figure 9: Interim super-frame structure

The length of the PiCSE and the codeword(s) sections, in terms of number of OFDM symbols, can be varied. The length of PiHRC is currently fixed as 16 OFDM symbols (each containing 2 bits mapped to a Quaternary Phase Shift Keying (QPSK) constellation) with the format shown in Table 3.

| Preamble | S <sub>1</sub> Idx | S <sub>2</sub> Idx | S <sub>3</sub> Idx | S <sub>4</sub> Idx | HNC Idx | Pad     | CRC  |

|----------|--------------------|--------------------|--------------------|--------------------|---------|---------|------|

| 0011     | XXX                | XXX                | XXX                | XXX                | XXXXX   | XXXXXXX | XXXX |

Table 3: PiHRC structure

In order to allow the PiHRC to be transmitter simultaneously from multiple sources, the data mapped to each of the 16 OFDM symbols, i.e. each pair of bits once mapped to a QPSK constellation, are spread along the 48 data subcarriers in frequency using a Constant Amplitude Zero Autocorrelation (CAZAC) sequence of length 47 with root 1, padded with a 0. This use of an odd sequence length provides beneficial cross-correlation properties. The CAZACs used for this spreading also uniquely identify the node transmitting the PiHRC by using a cyclic shift equal to the index of the node, i.e. 0 for  $S_1$  (stored as 000 in PiHRC) and 1 for  $S_2$  (stored as 001 in PiHRC). The index 101 in PiHRC indicates a blank field and was chosen to minimise PAPR issues resulting from long strings of 0. The 5 bits for the HNC index are currently being defined by WP4. The padding is a random series of 7 bits, this may be used at a later date if more information needs to be included in PiHRC. The final 4 bits are a Cyclic Redundancy Check (CRC) with polynomial  $x^4 + x^3 + x^2 + x$ .

Due to the fact that the channel is relatively static over time in the laboratory environment, but timing offsets cause a phase rotation as a function of frequency leading to an apparently non frequency flat channel, the PiCSE are implemented as spreading codes along time. Thus the same CAZAC is repeated over all 48 data subcarriers. This is illustrated in Figure 10 which shows the time-frequency layout of PiCSE and PiHRC. The length of the PiCSE CAZAC can be varied and is given by  $N_{PiCSE}$  in Figure 10.

<sup>&</sup>lt;sup>1</sup> Note the removal of PiAcq, compared to previous versions, as this is achieved by dint of the CAZAC sequences used in the PiCSE instead, and the reordering of PiCSE and PiHRC for convenience.

Figure 10: Time-frequency frame structure of interim air interface

Testing of the performance of PiCSE was undertaken by transmitting over the  $2\times 1$  system. Firstly the CSE is obtained from the preamble. The channel estimation is performed in the frequency domain; it is performed after the FFT and the Cyclic Prefix (CP) removal. A wideband estimate can be obtained from the second synchronisation symbol in the preamble ('Sync Word 2' in Figure 7, abbreviated to 'sync' in the following). The symbol transmitted from  $S_1$  in the frequency domain is  $X_{S_1}^{sync}[k]$ , where  $k=0,\ldots,N_{used}-1$  and  $N_{used}$  is the number used subcarriers, 48 in this case. The synchronisation symbol is a pseudo-random sequence as defined in [2] such that  $X_{S_1}^{sync}[k] \in \{1,-1\}$  for all data subcarriers, and 0 elsewhere. The received symbol in the frequency domain from the second OFDM symbol, i.e. 'Sync Word 2' from  $S_I$ , of the first of the two preambles is given by  $\tilde{Y}^{sync}[k,2]$ . Channel estimation of  $\hat{H}_{S_1}^{sync}[k]$  is performed by:

$$\widehat{H}_{S_1}^{sync}[k] = \frac{\widetilde{Y}^{sync}[k,2]}{X_{S_1}^{sync}[k,2]}.$$

(1)

At a high SNR of approximately 35 dB, achieved with the transmit and receive USRPs in close proximity and a transmit gain of 20 dB, an accurate CSE can be assumed to be obtained in this fashion.

This can then be compared against the CSE obtained from PiCSE. This is obtained per subcarrier k by taking the dot product of the  $N_{PiCSE}$  received symbols with the CAZAC<sub>PiCSE</sub> of the source(s) that are expected to be present in the signal. For example:

$$\begin{split} \widehat{H}_{S_1}^{PiCSE}[k] &= \left( \widetilde{Y}^{PiCSE}[k,1]. \, CZ_{PiCSE,S_1}[1]^* + \widetilde{Y}^{PiCSE}[k,2]. \, CZ_{PiCSE,S_1}[2]^* + \cdots \right. \\ &+ \widetilde{Y}^{PiCSE}[k,N_{PiCSE}]. \, CZ_{PiCSE,S_1}[N_{PiCSE}]^* \right) / N_{PiCSE}. \end{split} \tag{2}$$

The performance of PiCSE relative to the CSE obtained from the preamble for different  $N_{PiCSE}$  are shown in Table 4. The 'relative power' indicates the transmit power of the PiCSE symbols relative to the preamble symbols power. The channel values were normalised by the mean channel powers, and the Mean Squared Error (MSE) between the channel estimate from PiCSE and from the preamble was calculated and is shown in the table. It can be seen that as the transmit power of the PiCSE is reduced, the MSE increases. More importantly it can be seen that using shorter  $N_{PiCSE}$  does not increase the MSE significantly at high PiCSE transmit power, but has it does at lower transmit powers of PiCSE.

|                     | $N_{PiCSE}$ |        |        |  |  |

|---------------------|-------------|--------|--------|--|--|

| Relative Power (dB) | 4           | 8      | 16     |  |  |

| 0                   | 9.2e-4      | 8.5e-4 | 7.8e-4 |  |  |

| -10                 | 1.2e-3      | 9.2e-4 | 8.7e-4 |  |  |

| -20                 | 5.2e-3      | 2.7e-3 | 1.8e-3 |  |  |

| -30                 | 4.0e-2      | 2.4e-2 | 1.0e-2 |  |  |

| -40                 | 3.4e-1      | 3.2e-1 | 8.2e-2 |  |  |

Table 4: MSE between preamble CSE and PiCSE

Once the CSE has been obtained from PiCSE this can be applied to the received PiHRC symbols using a simple Zero-Forcing (ZF) equaliser:

$$\hat{R}_{S_1}^{PiHRC}[k,t] = \frac{\tilde{Y}^{PiHRC}[k,t]}{\hat{H}_{S_1}^{PiCSE}[k]}.$$

(3)

where  $t = 1, ..., N_{PiHRC}$ . The transmitted QPSK on each OFDM symbol of the PiHRC can then be gleaned at the receiver. This is obtained from the dot product of the CAZAC<sub>PiHRC</sub> of the node that transmitted the PiHRC with the  $N_{used} = 48$  equalised symbols, at each OFDM symbol. For example the QPSK symbol on the first OFDM symbol of PiHRC transmitted by  $S_I$  is given by:

$$PiHRC_{S_{1}}[1] = \left(\hat{R}_{S_{1}}^{PiHRC}[1,1].CZ_{PiHRC,S_{1}}[1]^{*} + \hat{R}_{S_{1}}^{PiHRC}[2,1].CZ_{PiHRC,S_{1}}[2]^{*} + \cdots + \hat{R}_{S_{1}}^{PiHRC}[N_{used},1].CZ_{PiHRC,S_{1}}[N_{used}]^{*}\right)/N_{used}.$$

$$(4)$$

and the  $N_{PiHRC}$ -th QPSK symbol is given by:

$$PiHRC_{S_{1}}[N_{PiHRC}]$$

$$= (\hat{R}_{S_{1}}^{PiHRC}[1, N_{PiHRC}]. CZ_{PiHRC,S_{1}}[1]^{*} + \hat{R}_{S_{1}}^{PiHRC}[2, N_{PiHRC}]. CZ_{PiHRC,S_{1}}[2]^{*} + \cdots + \hat{R}_{S_{1}}^{PiHRC}[N_{used}, N_{PiHRC}]. CZ_{PiHRC,S_{1}}[N_{used}]^{*})/N_{used}.$$

(5)

These  $N_{PiHRC}$  (nominally 16) QPSK symbols can then be mapped to the 32 bits of the PiHRC transmitted by  $S_I$ . The same equalisation as equation (3) is also performed on the codewords section of data.

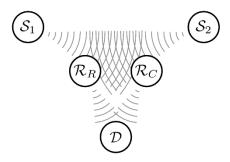

Initial testing using this PiCSE, PiHRC structure and populating the codewords with those generated by the DLA (see Figure 11 for node diagram and Section 2.2.2 of [1] for algorithm details) has begun. So far this includes successful implementation of both source and relay MATLAB code running online as compiled shared libraries within GNU Radio blocks. The relay(s) to destination transmission, and the relay decoding is currently performed offline in MATLAB. Using  $N_{PiCSE} = 4$  was sufficient to achieve 0 BER from end-to-end in the high SNR testing environment in the laboratory (about 35 dB). This will therefore be used as the initial baseline value.

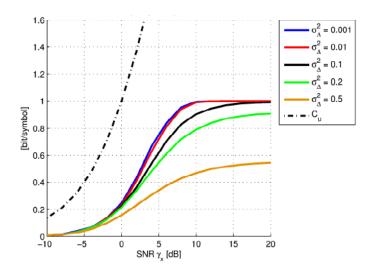

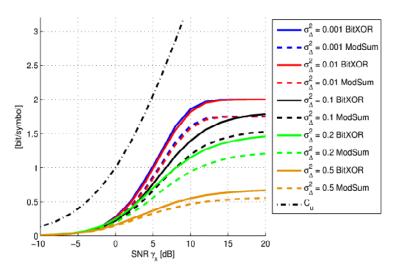

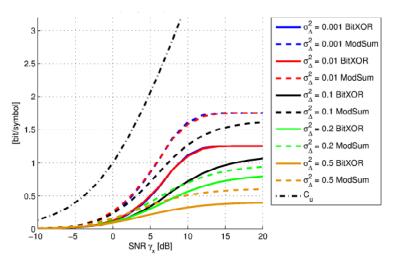

Figure 11: 2-source, 2-relay, 1-destination scenario for distributed learning process algorithm

Since the performance of WPLNC seems to be strongly dependent on channel parameterisations, the quality of the channel estimation is an important factor [3][4]. The impact of channel parameterisation as well as quality of its estimation on the capacity was intensively studied in [5]. Therein a single carrier modulation system in a butterfly network configuration is studied. The results show how the symmetric sumrate capacity is affected by incorrect channel estimation (expressed by the variance of estimation error  $\sigma$ ) for various Hierarchical Network Codes (HNCs), channel parameters and modulation schemes in a two-source one-relay network. The results in the following figures show the dependence of the symmetric Multiple Access Channel (MAC) capacity on the variance of the estimation error  $\sigma_{\Delta}^2$  for Binary Phase Shift Keying (BPSK) and QPSK alphabets. In the case of QPSK, different HNCs are assumed. The true channel parameterisation is assumed to be  $h_i = \hat{h}_i + \Delta h_i$ . It can be stated from the obtained results that as long as the estimation variance is lower then 0.01 it does not have disastrous effect on the channel capacity regardless of the channel parameterisation and HNC function. In [6] they develop a low-complexity channel estimation technique that can achieve the Cramér-Rao Bound (CRB) at high SNR. Compared with a WPLNC scheme with perfect Channel Station Information (CSI), their channel estimation technical has only a 0.5-1 dB loss in end-to-end Bit Error Rate (BER) performance at high SNR. These single carrier results can be straightforwardly extended to the current OFDM implementation.

Figure 12: MAC capacity for BPSK  $h_A = h_B = 1$  [5]

Figure 13: MAC capacity for QPSKa  $h_A = h_B = 1$  [5]

Figure 14: MAC capacity for QPSKa  $h_A = 1$ ,  $h_B = j$  [5]

#### 2.2.3 Half-duplex constraint

The half-duplex constraint is a natural issue that arises with wireless nodes. It forces the communication in the network to be slotted because each node is able to only receive or transmit in any given time instant. All of the proposed WPLNC algorithms take this constraint into account, in order to match the definition of the random connectivity class. The SMN fits into the random connectivity cloud class which assumes random and sparse connectivity and no global Network State Information (NSI) knowledge, as well as a half-duplex constraint [7]. Also the proposed structures of the DIWINE air interface protocol (Figure 8) also respect this limitation. Each node is assigned time slots in which it transmits and it receives in the other slots. The other limitation that emerges from the half-duplex constraint is the time necessary to switch the USRP from receiving to transmitting. The turnaround time of the XCVR2450 daughterboards has not been characterised but Ettus Research has made direct assurances to TREL that it is  $<10\,\mu s$ , which pales into insignificance when compared to the processing delays detailed in Section 2.2.4.

#### 2.2.4 Processing delay

The processing delay in the relays is a very important factor in the HW demonstrator, particularly given the half-duplex constraint. There are a number of parts to the delay: reception and down-conversion, transfer to the laptop (Ethernet protocol related delays), baseband processing performed in GNU Radio on the laptop, e.g. decode/re-encode, then transfer back to the USRP, and finally up-conversion and transmission. It is difficult to accurately profile these individual components.

Figure 15: Single hop relay. From the left: source, relay and destination

It has been found that there is significant latency between the USRP and the host processor, and thus even in a simple Amplify-and-Forward (AF) relay system (shown in Figure 15), which contains only a simple packet detector and gain blocks in the baseband processing flow graph, has a total processing delay of nearly 5 ms. The total processing delay in the node also includes the time taken for data to travel from the USRP to the host processor and then from the host processor back to the USRP.

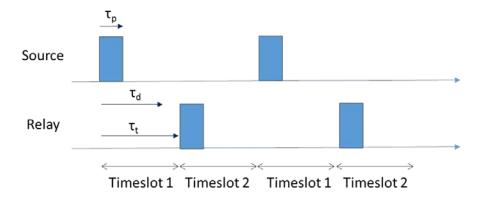

In the current settings for the relay setup shown in Figure 15, a large gap of 7 ms ( $\tau_t$ ) is left in between the beginning of the first time slot (when the source transmits) and the beginning of the second time slot (when the relay transmits) to allow for transmission of

the packet *and* the delay in the relay ( $\tau_d$ , which also includes the negligible propagation delay). This is wasteful as the packet fills only 1.52 ms ( $\tau_p$ ) of the 7 ms timeslot, as shown in Figure 16. This is the 19 OFDM symbols (3 preamble and 16 data), which are each 80 samples long (64 point FFT with ½ CP), at a sampling frequency of 1 MS/s.

If the processing delay in the relay becomes so long that  $\tau_d > \tau_t$  and the relay is forced to transmit after the allotted time slot has started, the USRP reports 'L' indicating that the transmit 'burst' has arrived at the USRP late, i.e. after the allotted transmit time, and the burst is dropped. If  $\tau_t$  is reduced below 7 ms, occasionally late packets are reported, and below 5 ms all packets are reported as late. This shows that there is significant variation in the processing delay caused by buffering in the laptop and the USRPs and the Ethernet link between the laptop and the USRPs. Furthermore, this is thus already quasi-real-time system, and this is before any significant baseband processing is introduced at the relay!

Figure 16: Processing delay example

The next stage of testing was to implement a Decode-and-Forward (DF) relay. As an interim step towards the BSLD implementation, this relay is the receiver from the  $2\times1$  system (Figure 7), with OFDM modulation and transmission functionality added to the end of the flow graph. It should be highlighted that as there is no HNC mapping performed, at this stage, this is not a viable system but simply a flow graph to help test processing delay. It was found setting  $\tau_t$  is above 7 ms resulted in no late packets, thus the total processing delay is very similar to that of the basic AF system. This implies that the baseband processing, in GNU Radio, is a very small element of the total processing delay,  $\tau_d$ .

The Boost library boost::datetime has a microsecond precision clock (although its *accuracy* depends on the platform), from which the function 'gettimeofday' can be used to get microsecond precision timestamps. Adding one timestamp to the point in the GNU Radio code where the first sample of preamble is detected, and one to the final function before transmission, the total baseband processing delay can be estimated. It was found that the total delay through the flow graph was approximately 1 ms. This explains why the total processing delay in the AF and DF cases appear similar; the delay is in other parts of the system not the GNU Radio baseband processing, e.g. the laptop and USRP buffers, and Ethernet transmission.

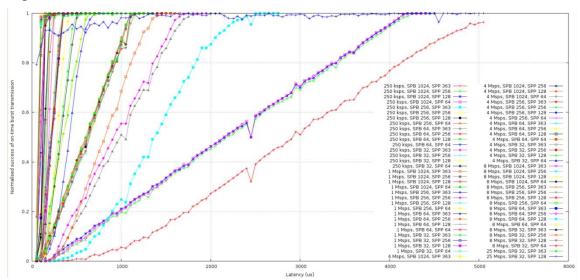

There are a number of USRP parameters than can be adjusted which impact the processing delay, excluding the GNU Radio baseband processing: Samples per Block (SPB), Samples per Packet (SPP), and the receive frame size. The general guidelines are that operating at a higher sample rate will mean data will get to/from the USRP quicker. However, as reported previously there are limitations on this due to host processing power. Choosing a smaller SPB will mean less time filling your buffer on a 'recv' call at the receive USRP, so this is advantageous. In addition choosing a smaller SPP will mean the device will spend less time filling a packet's payload before sending it down the wire. It is also possible to adjust the Network Interface Card (NIC) Maximum Transmission Unit (MTU) size and the NIC interrupt rate. More details are investigated in [8], and the latency results of the latency study are shown in Figure 17. It can be seen that reducing the SPB down to 32 and SPP down to 64 provides the best performance at 1 MS/s. Unfortunately this did not discernibly reduce the overall processing delay and in order to avoid late packets  $\tau_t$  has to remain above 7 ms. Ettus Research have confirmed that when looking at end-to-end latency, rather than just USRP to NIC, 5–10 ms is to be expected.

Figure 17: USRP latency results [8]

One simple way to improve the efficiency, and circumvent the effects of buffering and transfer by Ethernet (and the GNU Radio baseband processing delay), is to increase the number of packets sent in each burst. Transmitting one packet in the MISO case where two preambles means a longer  $\tau_p$ . This is because there are 16 OFDM data symbols (80 samples each) and 6 preamble symbols which gives 1760 samples, i.e. 1.76 ms at 1 MS/s. Sending 10 packets per burst results in 17600 samples which means  $\tau_p = 17.6$  ms at 1 MS/s. It was found that increasing  $\tau_t$  to 17.6 ms enables successful transmission and reception thus enabling a fully real-time system, as illustrated in Figure 18. In this case  $\tau_p = \tau_t > \tau_d$ , and so the processing delay becomes irrelevant. The received time-domain waveform at the destination for four successive bursts, consisting of alternating bursts received from the source (smaller envelope) and the relay (larger envelope). The plot shows the lack of gaps between bursts, and therefore fully real-time operation.

Figure 18: Real-time operation

Figure 19: Received time domain waveform at destination for four successive transmit bursts

When implementing the BSLD algorithm, i.e. including the BSLD decoder in the DF relay code, the BSLD's baseband processing dramatically increases the total processing delay at the relay. In particular the Low Density Parity Check (LDPC) decoder takes a significant time to execute. Using the timing function in Python is was possible to determine the time taken by the various parts of the BSLD implementation. The algorithm was set such that 10 (GNU Radio) packets are transmitted in each timeslot, as in the previous DF testing. These are then processed in one execution, in order to improve the efficiency of the LDPC decoder. This means 7680 data bits per burst, made up of 17600 samples or 17.6 ms at 1 MS/s. The BSLD algorithm takes up to 250 ms in total, with 210 ms of that taken up by the LDPC decoder. The LDPC decoder is implemented in Cython (compiled C-code called from within Python) in or to give speed-up over a pure Python implementation. This long execution time means that the scheme cannot run in real-time, because the delay associated with the BSLD algorithm alone is significantly longer than the length of the source transmission burst. Some further optimisation of the code may be achieved, but this is unlikely to be sufficient and increasing the burst length is limited by buffering in GNU Radio. It is therefore concluded that this algorithm will have to run in a quasi-real-time fashion as shown in Figure 16.

The DLA is implemented in MATLAB, which is compiled as a shared library and run from within a GNU Radio block, and the time taken for the processing of each packet (as defined in Figure 10) at the relay is approximately 40 ms. In the current, initial, testing there are 12 OFDM symbols of codewords, i.e. payload, each of which contains 48 data subcarriers, with a total of 4 bits (2 from each source) per subcarrier. That results in 2304 bits per packet. If one ignores all other components of the processing delay for now, i.e. setting  $\tau_t = 40$ , this would result in an effective data-rate of 57.6 kbit/s. This will be significantly improved by optimising the MATLAB code, including improving efficiency by processing multiple packets per execution as with BSLD or rewriting some code as mex files or in C-code. Extending the length of the payload (see Section 2.2.5) and reducing the overheads, e.g. condensing PiHRC by removing the empty fields, or increasing the number of data subcarriers by removing the pilots or squeezing the guard bands, will also help improve efficiency. The effective data-rate can therefore be significantly improved but the algorithm will likely not be able to run in real-time. However, a proof-of-concept demonstration of a novel and highly complex algorithm will be achieved.

#### 2.2.5 Length of payload

As mentioned in the previous section, the relative lengths of each section is variable but the initial values are  $N_{PiCSE} = 4$ , and  $N_{PiHRC} = 16$ . Due to buffer limits in the multiplexers in GNU Radio which joins the PL section to the existing  $2 \times 1$  preamble before transmission, the total number of OFDM symbols in the PL is limited to 45. This means that the current maximum  $N_{PL} = 25$ . Fairly simple system redesign would allow extension of this by simply multiplexing multiple PL sections per preamble. However, without external synchronisation the impact of CFO and carrier frequency drift might limit the length of PL, considering that as can be seen from Figure 8 there will be a number of 'slots' in between each DIWINE synchronisation frame. See Section 2.3 for more details on CFO and carrier frequency drift.

#### 2.2.6 Multiple access strategy from gateway to destination nodes

On the final stage of communication, the information must be delivered from cloud gateway relays to the final destination nodes, e.g.  $R_R$  and  $R_C$  to D in Figure 11, or the final row of relays to destinations in Figure 20 (although the latter is outside of the scope of the HW demonstrator). When the destination is connected to more than one relay then it has to reliably receive the signals from all of them. Due to the lack of Hierarchical Side Information (HSI) during this stage, the information must be delivered in some classical way. The first option is an orthogonal multiplexing scheme such as Time Division Multiple Access (TDMA) or Frequency Division Multiple Access (FDMA). Due to its relative simplicity TDMA was selected as the initial method to be used in HW testbed.

Figure 20: Unidirectional grid cloud scenario (S-RC-a)

The second option, which is more advanced, is a multi-user detection scheme based on successive decoding and interference cancellation techniques. The achievable rate region of this strategy is given by the cut-set-bound theorem. Since most of the points of the rate region are achievable only by time-sharing there is a strong need for cooperation amongst the gateway relay nodes that may incur significant overhead. If the inter-relay communication is complicated or even impossible, e.g. due to great distance among the gateway nodes, the relay output rate should be lowered to meet the limitations of the MAC. However this has impact on the length of time slots in air interface protocol. This option is thus unlikely to be investigated within the realm of the HW demonstrator but could be implemented in the System-Level Simulator (SLS).

#### 2.2.7 Time of flight and asynchronism

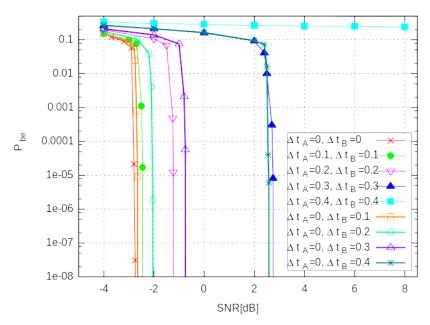

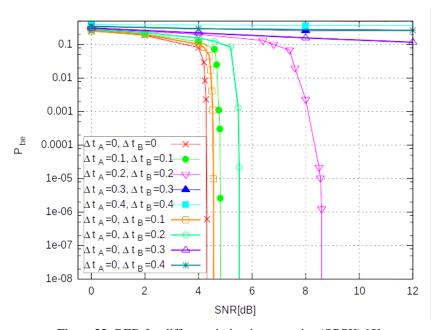

Since the SMN testbed platform will demonstrate short range indoor scenarios, time of flight is not an important issue. If the testbed platform were to be extended to large scale topologies then time of flight (and especially different times of flight from different nodes) could become a problem causing mainly time misalignment in the superposition of the different signals. The impact of this time asynchronism on the system BER was studied in the case of simple network with single carrier modulations in [5].

Figure 21 and Figure 22 show how the BER is degraded for various levels of asynchronism for BPSK and QPSK respectively. The case  $\Delta t_A = \Delta t_B$  represents a fully synchronised system; the other options introduce some level of time asynchronism. All values are expressed as fractions of the symbol period  $T_S$ . As a result it can be stated that a time difference up to  $t_i = 0.1 \, T_S$  does not have a significant impact on the BER. On the other hand, delays higher than  $0.4 \, T_S$  are catastrophic. QPSK seems to be more sensitive to time accuracy than BPSK.

Figure 21: BER for different timing inaccuracies (BPSK) [5]

Figure 22: BER for different timing inaccuracies (QPSK) [5]

In [9] they propose an optimal decoding algorithm for time-domain WPLNC with fractional delay, where timing offset is smaller than a symbol period. The algorithm shows that in this setting, symbol misalignment can make the system *more* robust to phase asynchronism. The impact on fractional timing misalignment using practical pulse shaping waveforms is also investigated in [10]. Where the timing offset is more than a symbol period in the time-domain setting, WPLNC has to be divided into two parts: the overlapping and the non-overlapping parts. This is addressed in [6]. When OFDM is used, however, it can be exploited in WPLNC to combat the time mismatch,

where the delay in the time-domain is transferred to a phase shift in the frequency domain as long as it is within the cyclic prefix [11]. That is because if the relative symbol delay is within the length of the CP, then the time-domain misaligned samples will become aligned in the frequency domain after FFT [12].

If the time of flight means a serious issue in possible future wide range implementations, it could be solved by classical techniques such as Timing Advance (TA) used in Global System for Mobile Communications (GSM) systems [13]. In GSM systems the TA value is normally between 0 and 63. Each of these steps represents an advance of one bit period (approximately  $3.69\,\mu s$ ), which is a change in round-trip distance of about  $1100\,m$ . This means that the TA value changes for each  $550\,m$  change in the range between a mobile and the base station. It also places a limit of  $63\,m \times 550\,m$ , i.e.  $35\,km$  as the maximum cell size. These numbers reaffirm the lack of importance of time of flight correction in short range indoor scenarios.

#### 2.2.8 System under test

The current implementation is a 1-relay butterfly as shown in Figure 23 which supports the BSLD algorithm. In addition a two-source, two-relay, one destination scenario has been implemented (as shown in Figure 11) to implement the DLA. This, however, is only partly 'online' at this stage, as explained in Section 2.2.2.

Figure 23: 1-relay butterfly network

Currently this is controlled by four i7 laptops for demonstration purpose: one for the two sources, one for the relay, and one for each of the destinations. For ease of testing in the lab it is possible to run from just three laptops (running the two destinations from one laptop). The next stage is to expand to the 2-relay butterfly (as shown in Figure 4). This will be able to demonstrate both BSLD and DLA fully. This could be run from a minimum of three laptops, although four or even five would be preferable for demonstration purposes.

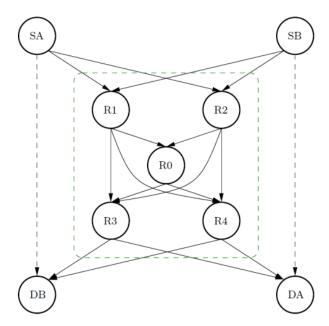

In order to demonstrate the *full* DIWINE principle where there are terminal nodes, cloud gateway nodes and a cloud node, the hidden node cloud scenario (see Figure 24) would be required. As one laptop is required per stage, this will require at least five laptops and, of course, nine USRPs. This can, however, still all be run through one Gigabit switch as the bandwidth will not become saturated (see Section 2.2.1). A 24 port switch is available for this scenario. If this final target is not achievable within the timeframe of the project, an 8-node implementation, i.e. as Figure 24 without R0 will certainly be achieved. This will be able to demonstrate multiple relay 'stages', a key aspect of the DIWINE paradigm.

D5.12 27

Figure 24: Scenario "Hidden Node Cloud" (S-RC-b)

#### 2.2.9 Node visibility

Since the SMN HW demonstrator will be implemented in indoor scenarios it will experience shadowing caused by obstacles such as walls, furniture etc. This will affect the radio visibility among the nodes and thus define the network topology. The proposed algorithms should cope correctly with this situation. This is the case for DLA (see Section 2.2.2 of [1]) that equips the cloud with the ability to change the WPLNC coding scheme so as to reliably deliver the source information to the destinations. As long as the user nodes (sources and destinations) are connected to at least one of the cloud relays, the cloud will be able to modify itself to provide its service correctly.

None of the proposed WPLNC algorithms needs full connectivity among the nodes, including BSLD and DLA (the two that will be implemented in the SMN demonstrator), neither cloud nor terminal. Initially a static topology of the cloud is assumed, i.e. no nodes are moving so the network topology does not change with time, and no nodes are connecting or disconnecting to/from the network. However the proposed algorithms can be easily modified to support cloud adaptability even for time variable network topology, although there are no plans to implement this in the SMN HW demonstrator.

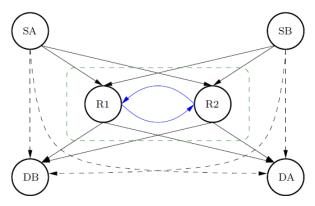

Some of the algorithms are designed for the simplest cloud consisting of one or two nodes, known as the relay butterfly network (as shown in Figure 25). In this case it is assumed that there is no direct link between the source and its destination, e.g.  $S_A$  and  $D_A$  or  $S_B$  and  $D_B$ , in the theoretical work. However this is not the case in the real HW demonstrator deployment. The unwanted direct link is difficult to avoid without also introducing too much error in the wanted direct link which provides the HIS, e.g.  $S_A$  to  $D_B$  and  $S_B$  and  $D_A$ ). To emulate the theoretical assumption it must be artificially cancelled, using perfect HSI passed through the wired backhaul network using User Datagram Protocol (UDP) source/sink blocks in GNU Radio. This method was already tested whilst implementing BSLD algorithm.

Figure 25: Scenario 2-relay butterfly with perfect intra-cloud coordination (S-RC-b)

However, it should be highlighted that the presence of the direct link is an issue only for the 1-relay butterfly network. It is only in this case that reception of the source transmission directly by the destinations is necessary in order to provide HSI. In larger clouds all the information can be provided by the relays themselves and no HSI from a direct link is needed.

#### 2.3 Distributed network synchronisation related constraints

In this section the hardware limitations affecting the distributed synchronisation algorithm will be discussed, as well as how the SMN testbed has been implemented to take these limitations into account.

#### 2.3.1 Carrier frequency

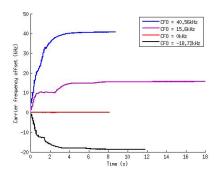

As detailed in D3.01 [14], the CFO between the nodes causes an apparent frequency rotation in the received data stream. The carrier synchronisation algorithm estimates this CFO and adapts the nodes carrier frequency.

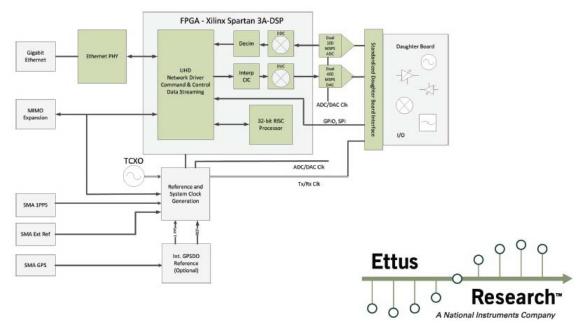

Figure 26: Ettus N210 USRP internal layout [15]

CFO is directly linked to the reference oscillator used within the node, for the USRPs this can either be an inbuilt 100 MHz oscillator, sourced from another USRP via a Multiple Input Multiple Output (MIMO) sync cable, or from an external source. The accuracy and stability of these oscillators will have a direct effect on the CFO. Figure 26 displays the internal configuration of the USRP N210. The block titled 'Reference and System Clock Generation' has multiple inputs illustrating the variety of accepted reference oscillator input sources, Temperature Compensated Crystal Oscillators (TCXO) is the internal oscillator. The output of this block is shown to control the Field Programmable Gate Array (FPGA), digitisers and the Radio Frequency (RF) components of the USRP, as such any variation in the oscillator performance will have a direct effect on these subsystems.

The rest of this section will detail the accuracy and stability of the carrier frequency of the XCVR2450 RF daughter-board, contained within the N210, as well as provide limits based upon worst-case scenarios for the CFO when using different sources of reference oscillator.

#### 2.3.1.1 Frequency Accuracy and Stability

Frequency accuracy is the degree of conformity of a measured or calculated frequency to an ideal or specified reference. The difference is known as the frequency offset, and this changes over time.

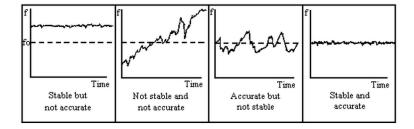

Figure 27: Frequency vs. time

Frequency stability breaks down into three categories:

- Long term stability: measured over hours, days or more;

- Short term stability: measured over periods of fractional seconds to one day;

- Phase noise: deals with very short time scales and produces effects that look like unwanted modulation changing the shape of the waveform rather than a wandering frequency.

#### 2.3.1.2 Phase Noise

Using a spectrum analyser phase noise measurements were made for the XCVR2450 RF board, using both a) no external synchronisation and b) external synchronisation from the Ettus OctoClock-g GPS Disciplined Oscillator (GPSDO) synchronisation distribution system with Global Positioning System (GPS) antenna. It should be noted that in the N210 USRPs all of the RF boards use the master-clock from the motherboard to derive their final LO frequency using Phase Locked-Loop (PLL) synthesis. The

master clock rate is 100 MHz and the daughterboard reference clocks are derived from that. Part of the phase noise will be dominated by the master clock, and part by the loop parameters of the PLL. The master oscillators on the N210 are low phase noise TCXOs which have a frequency accuracy of 2.5 ppm, with the external reference GPSDO this falls to 25 parts per billion (ppb), and further to 10 ppb with a lock on the GPS constellation.

| RF board | Frequency<br>(GHz) | Offset<br>(kHz) | No sync phase<br>noise (dBc/Hz) | External sync<br>phase noise<br>(dBc/Hz) |

|----------|--------------------|-----------------|---------------------------------|------------------------------------------|

|          |                    | 1               | -64                             | -80                                      |

|          | 2.48               | 10              | -65                             | -80                                      |

| VCVD2450 |                    | 100             | -66                             | -80                                      |

| XCVR2450 |                    | 1               | -80                             | -86                                      |

|          | 5                  | 10              | -82                             | -90                                      |

|          |                    | 100             | -81                             | -90                                      |

Table 5: Phase noise

For the XCVR2450 board it can be seen that the phase noise is high, but it is improved significantly by using external synchronisation. In addition to the phase noise results, it was found in the XCVR2450 that the centre frequency visibly moved over the space of a few seconds, i.e. short term stability is very poor without external synchronisation. This problem was even more noticeable at 5 GHz.

The local oscillator single side band suppression values for the XCVR2450 RF board were similar to those quoted by Ettus. In addition small peaks either side of the sidebands were found which can be attributed to a synthesiser problem, again these were even more noticeable in the 5 GHz band than the 2.4 GHz band.

#### 2.3.1.3 Frequency Offset

In order to assess the frequency offset of the USRPs, a 5 kHz complex sinusoid was transmitted. The transmitter and receiver USRP were connected using a cable. From the baseband waveforms, it was possible to perform sinusoidal analysis assuming that there is only one complex exponential present in the signal. By multiplying the transmitted waveform with the conjugate of the received waveform and estimating the frequency of the resulting signal, it was possible to get an estimate of the frequency offset between the two signals.

The results are shown using the XCVR2450 board in the 2.4 GHz band. In this, and all remaining experiments a sampling frequency of 1 MS/s was used. Results are shown where the receiver and transmitter have a) no synchronisation, b) synchronisation between them by the MIMO cable, c) external synchronisation from the Ettus OctoClock-g GPSDO synchronisation distribution system with GPS antenna. As with the external 10 MHz reference, when using the MIMO cable, the USRPs still use their

own oscillator but they should be mutually frequency- and phase-locked, thus the mutual phase noise should be very low. However, there will be a random phase offset every time they are tuned, due to the fractional-*N* synthesis in the synthesiser.

|          | Contro              | Frequency offset (Hz) |                            |                          |

|----------|---------------------|-----------------------|----------------------------|--------------------------|

| Board    | Centre<br>frequency | No<br>synchronisation | MIMO cable synchronisation | External synchronisation |

| XCVR2450 | 2.48 GHz            | 1105.1                | 1.8e <sup>-3</sup>         | 2.7e <sup>-4</sup>       |

Table 6: Single receiver offsets

It has been noted by Ettus that the high level of integration on the XCVR2450 board is likely to lead to poorer performance compared to their WBX boards. It can be seen that the frequency offset is significantly lower when the MIMO cable is used for synchronisation. As the external reference oscillator has a lower phase-noise and higher-accuracy than the internal clocks, then it is still preferable to use that rather than the MIMO cable, and that is borne out by the results in the XCVR2450 case. It should be noted that rather than using the clock distribution system, it is possible to obtain a GPSDO for each individual USRP, the accuracy of which can further be enhanced using a GPS antenna. Alternatively a third party oscillator such as those produced by Quartzlock may be suitable from improving stability.

The experiment was expanded so that instead of just using a 5 kHz signal, 50 kHz and 500 kHz were also used. It can be seen from Table 7 that the frequency offset is not affected by the frequency of the signal tone. It also shows, though, that there is significant experimental variation in the frequency offset of the USRPs.

| Baseband            | Frequency offset (Hz) |                            |                          |  |

|---------------------|-----------------------|----------------------------|--------------------------|--|

| signal<br>frequency | No<br>synchronisation | MIMO cable synchronisation | External synchronisation |  |

| 5 kHz               | 1105.1                | 1.80e <sup>-3</sup>        | 2.7e <sup>-4</sup>       |  |

| 50 kHz              | 654.7                 | 1.42e <sup>-2</sup>        | 5.6e <sup>-3</sup>       |  |

| 500 kHz             | 724.2                 | 1.00e <sup>-2</sup>        | 9.2e <sup>-3</sup>       |  |

Table 7: Single receiver offsets with different signal frequencies

In a second experiment the transmitter USRP is always connected to external synchronisation and transmits at 2.48 GHz with the carrier being modulated by a 5 kHz complex sinusoid. The transmitter is connected to two receivers using a splitter. The receivers have a combination of different synchronisation settings, either a) neither have external synchronisation, b) receiver one has external synchronisation but receiver two does not, c) receiver one has external synchronisation and receiver two is synchronised to this by the MIMO cable, d) receiver one has no external synchronisation and receiver two is synchronised to this by the MIMO cable.

| Scenario | Rx1 sync | Rx2 sync   | Rx1<br>frequency<br>(Hz) | Rx2<br>frequency<br>(Hz) | Difference<br>(Hz) |

|----------|----------|------------|--------------------------|--------------------------|--------------------|

| a)       | None     | None       | 7465.7                   | 6845.4                   | 620.3              |

| b)       | External | None       | 4973.6                   | 6962.1                   | 1988.5             |

| c)       | External | MIMO cable | 4973.6                   | 4973.6                   | 0.035              |

| d)       | None     | MIMO cable | 7706.4                   | 7760.4                   | 0.029              |

Table 8: Dual receiver offsets

It can be seen that there is a significant difference between the frequency of the received signals in case a) and neither is close to 5 kHz. In case c) the difference is even larger as receiver one achieves very close to 5 kHz with the aid of external synchronisation, but receiver two remains approximately the same as in case a). In case c) It can be seen that the frequency of receiver two is brought very close to receiver one by using the MIMO cable, and both are therefore close to 5 kHz. In the final scenario it can be seen that again the MIMO cable brings the accuracy of the receivers very close to one another, although they are very far from the target 5 kHz.

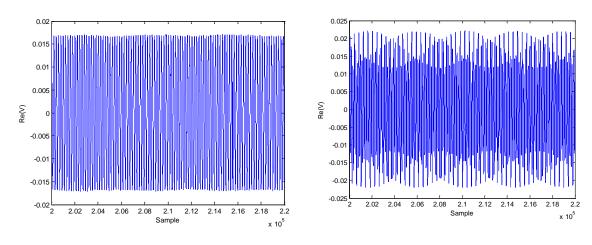

The following plots show a section of the received waveform from receiver one in case a) and case b). As stated previously, phase noise produces effects that look like unwanted modulation changing the shape of the waveform. In the left plot of Figure 28 very slight modulation can be seen where there is external synchronisation and low phase noise. In the right plot of Figure 28 the modulation effect caused by significant phase noise is much clearer.

Figure 28: Received waveform; left: with external synchronisation, right: without external synchronisation

#### 2.3.1.4 Phase offset

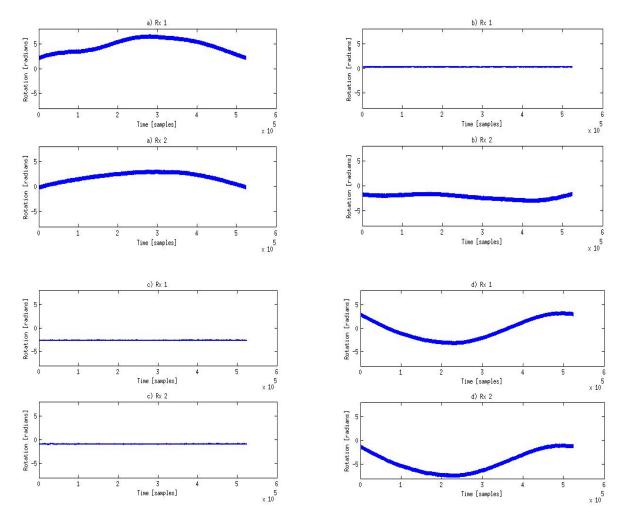

It is possible to calculate the phase drifts of the received signals by down-converting with their respective frequencies (as listed in Table 8). The results are shown in Figure 29 below for each of the four scenarios.

Figure 29: Phase drift of receiver one and two in the different cases: upper-left: case a), upper-right: case b), lower-left: case c), lower-right: case d)

It can be seen that in case a) where there is no external synchronisation that the phase drift is large, and independent between the two receivers. In case b) where receiver one has external synchronisation its phase offset is fixed, but receiver two experiences drift because it has no external synchronisation. When receiver one has external synchronisation, and receiver two is synchronised to it by the MIMO cable, as in case c), they both have a (different) fixed phase offset. In case d), where there is no external synchronisation, but receiver two is synchronised to receiver one by the MIMO cable, there is phase drift. The phase drift is the same in both receivers but with a fixed offset (due to the fractional-*N* synthesis in the synthesiser as discussed earlier).

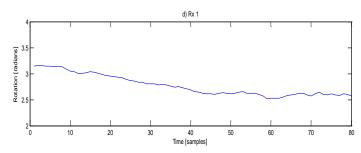

Figure 30 shows the phase drift with no external synchronisation over 80 samples which is one OFDM symbol using 64 subcarriers and a CP of ½. It can be seen that there is very significant drift over this duration.

Figure 30: Phase drift of receiver one in case d) over one OFDM symbol

#### 2.3.1.5 Maximum frequency offset

Using the accuracy of the reference oscillators provided in data sheets by Ettus Research [15][16], it is possible to estimate the maximum frequency offset that we are likely to experience when using various oscillators. The oscillators' accuracies are specified in parts per million (ppm) or ppb, from this the accuracy of the reference oscillator can be estimated, then scaled up to estimate the carrier frequency accuracy. Table 9 states the oscillators' accuracy in the XCVR2450 and the OctoClock-g GPSDO with and without a GPS connection. For this work we assume a carrier frequency of 2.45 GHz.

| Reference oscillator | Stated accuracy | 100 MHz accuracy<br>(Hz) | 2.45 GHz accuracy<br>(Hz) |

|----------------------|-----------------|--------------------------|---------------------------|

| XCVR2450             | 2.5 ppm         | 250                      | 6125                      |

| OctoClock-g w/o GPS  | 25 ppb          | 2.5                      | 61.25                     |

| OctoClock-g with GPS | <1 ppb          | 0.1                      | 2.45                      |

Table 9: Maximum frequency offset caused by various reference oscillators

The data presented in this table shows that if the inbuilt reference oscillators within the XCVR2450 are used for each node, there will be a maximum frequency difference between any two nodes of 12.25 kHz, and this is slightly less than the bandwidth of one OFDM subcarrier, which will be used in the forward and backward data frames. As the synchronisation algorithm is capable of correcting much larger CFO than 6.125 kHz it will be necessary to set a larger artificial CFO at each node, to demonstrate the capability of the integer aspect of the distributed synchronisation algorithm.

#### 2.3.2 Timing offsets

One of the purposes of the synchronisation algorithm is to predict and correct the timing offset (TO) between all nodes. This allows the nodes to have a global time stamp, i.e. all nodes will be able to schedule their transmissions and receptions with respect to other nodes. This concept is discussed in more detail in Sections 2.3.3 and Section 2.4, as the half-duplex constraint complicates the definition of a single global time stamp.

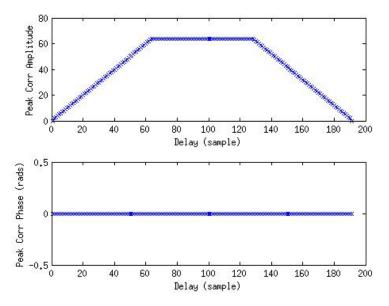

To improve the estimation accuracy of the CFO and TO the symbol rate of the synchronisation frame has been increased from the 1 MS/s of the rest of the system. This allows far greater accuracy in the convergence of CFO and TO within each nodes. To achieve this the signal is sent though either a linear interpolator or matched raised root cosine filter at the transmitter, and processed accordingly at the receiver. This allows finer TO control and better estimation of the CFO. Hardware limitations, such as the Ethernet connection between the USRP and controlling laptop, restrict the interpolation factor to four, resulting in a final sample rate of 4 MS/s.

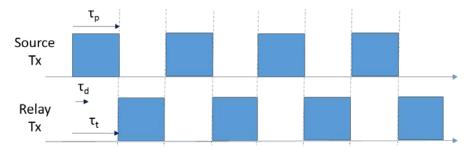

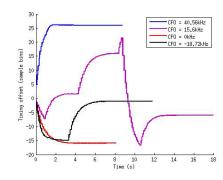

#### 2.3.3 Scheduling and half-duplex constraints

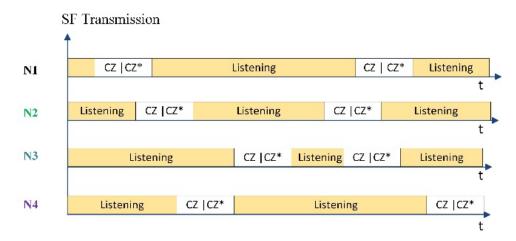

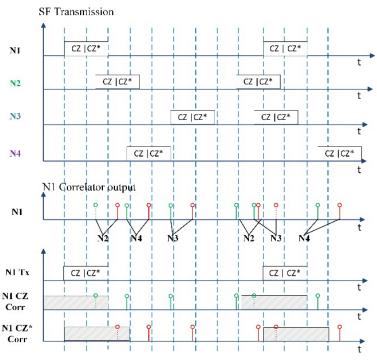

The essential idea behind the synchronisation algorithm is that each node transmits a Synchronisation Frame (SF) at a certain time, and listens for all the other nodes transmissions. It then iteratively adapts its own timing of its retransmissions to coincide with the other nodes, this process of adaption continues until all nodes are transmitting the SF at exactly the same time and frequency. This transmission of a 4-node network is demonstrated in Figure 31, also shown are the outputs of the matched correlators within the receiver of node 1 (N1), the green represents the outputs for the correlator matched to the SFs' first CAZAC sequence, and the red is from the correlator matched to the conjugate CAZAC (CZ\*). Each of the nodes are linked to their corresponding peaks of the correlators. At the end of adaption all the peaks occur at the same time.

Figure 31: Upper plot: Full-duplex SF transmission and reception, i lower plot: matched correlator output for N1

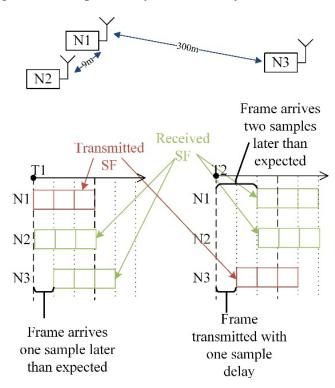

The most significant problem affecting the implementation of this system is the half-duplex constraint imposed by the hardware. This results in the nodes not being able to transmit and receive at the same time, and so it would be pointless if all nodes were transmitting instantaneously, as none would be able to receive the transmission. Instead each node has to transmit, and then listen to the other nodes transmissions. This idea is shown in Figure 32.

Figure 32: Half-duplex sync frame modification showing SF transmissions and listening periods of each node

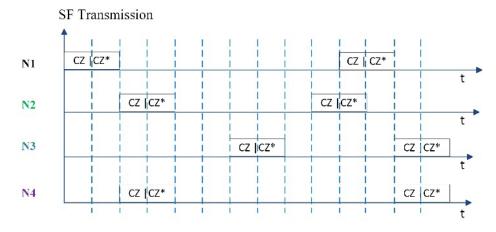

An issue that arises with a system like this, is that it is uncertain what reference time the users should adapt to. To overcome this, instead of all the users converging on a single time, they will adapt so their SF transmissions occur at multiples of a certain period. The duration of this period is relatively arbitrary, however for conformity it has been set to be 64 samples long, which is the same as the duration of the CAZAC sequences. The transmissions of a synchronised 4-node network can be seen in Figure 33, displaying how the transmissions of the nodes only occur at set intervals, note the listening periods are now implicit. To implement this in the synchronisation algorithm, instead of taking the timing offset weights to start from the end of the SF transmission, they are now made periodic between these 64 sample boundaries. A further modification is made, so instead of the timing offset weights being set to vary between 0 and 63, as if a SF arrived just one sample too early its offset weight would go to 63, thus creating a large error, when in reality it was only one sample away from being correct. Instead, the timing offset weights vary between -31 and 32, with zero centred on the ideal sampling time. This results in a SF arriving one sample early, receiving a timing offset weight of iust -1.

Figure 33: Timing of a synchronised half-duplex system, SF transmissions occur at multiples of a fixed period

A final consideration involved in the processing of the received data is the capture of non-complete SFs. This issue is illustrated in Figure 34, from the perspective of N1, their SF transmissions clash with the first transmission from N2 and the second transmission from N3. This is problematic when the output of the correlators are investigated. It should be remembered that the two matched correlators in each node are matched to separate parts of the SF, so one can still produce a peak even if the other half of the SF is not captured, the missing correlation peaks are illustrated by a dashed line in the middle graph in the figure.

Figure 34: Upper plot: SF transmissions on a 4 node network, middle plot: output of correlators at N1, including showing result of non-complete capture of SF, missing correlation peaks shown using dashed lines, lower plot: modified algorithm, nulling part of the captured data for the two correlators

This non-complete capture of SF at N1 results in one correlator producing more peaks than the other, which in turn can interfere with the CFO and TO estimation process. To avoid this, the captured data is windowed, so that the first correlator, which is matched to CZ, nulls the last 64 samples of the captured data. This is implemented because any correlation peaks produced from this data would correspond to the reception of the second half of the SF that is blocked by N1's transmission. Likewise, for the correlator that is matched to CZ\*, the first 64 samples of data are nulled. This is illustrated in the lowest graph of Figure 34, highlighting the SF transmissions of N1, along with its matched correlator outputs, shading out the regions of the signal that are not analysed by the respective correlators.

A quick note on any SF that are now not fully captured, both correlators will output an equality weighted signal. The peaks produced by the correlators will be proportional to how much of the respective CAZAC sequence has been captured. Figure 35 shows the correlator output of a simulated CZ signal passing a capture window 192 samples long, note how when all the signal is captured the magnitude is unity, then linearly decreases

as less of the CZ signal is captured. Also note, capturing less of the signal does not affect the phase of the correlator output, this is important in estimation of the fractional CFO.

Figure 35: Simulated correlation of partially captured CAZAC sequences

The issue of processing delay also complicates the scheduling of the SF transmissions, this is overcome by inserting another null period just after the capture of the signal, and before the SF transmissions to allow the processing of the received data and adaption of the carrier frequency, this is detailed in Section 2.3.5.

#### 2.3.4 Sampling frequency

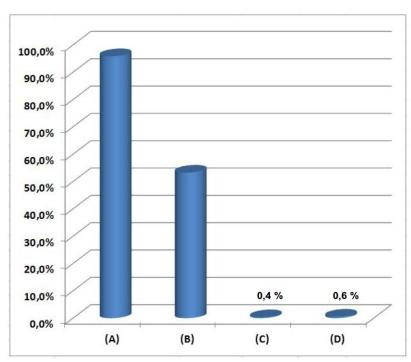

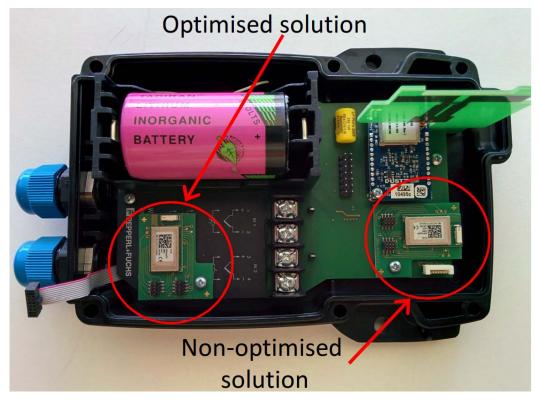

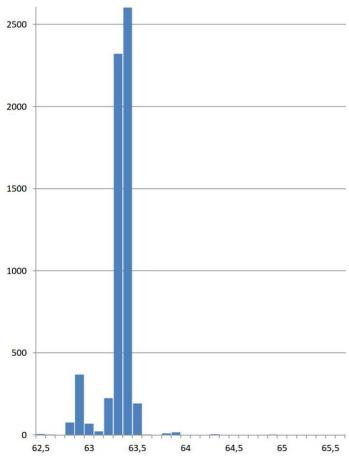

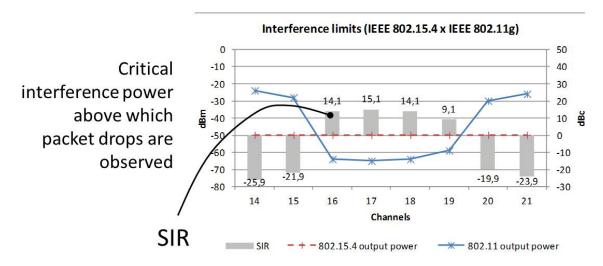

Issues with the exact sampling frequency are related to the CFO, TO, and the hardware of the USRP. As shown in Figure 26, the reference oscillator block within the USRP generates signals for the carrier frequency and digitisers. The USRP will use simple multipliers and dividers to attain the correct sampling and RF frequencies. Thus, if several USRPs have been configured to have the same sampling and carrier frequencies, and they are then all connected to a common clock source, they will all have identical frequencies. If, however, they are connected to oscillators that are different, this will result in different sampling and RF frequencies. How much these frequencies differ is all proportional to the difference in the reference oscillators, and so from the difference in the RF signal, the difference in the sampling signal can also be estimated. This is demonstrated in the example below: