# Energy Efficient Tunnel FET Switches and Circuits

Grant Agreement No.: 619509

Funding Scheme: Collaborative project

**Thematic Area:** Energy efficient switch, tunnel FET, nanotechnology III-V, SiGe and Ge, low power integrated circuits, digital and analog/RF circuits, CMOS, simulation and modeling of nano-electronic devices & circuits

Project start date: 01-11-2013

Deliverable D7.7 First update of the Plan for Use and Dissemination of Foreground (PUDF)

Nature<sup>1</sup>: R

**Dissemination level**<sup>2</sup>: CO

Due date<sup>3</sup>: M24

Date of delivery: M25

Lead partner: EPFL

Contributing partners: LUND, CSS, SCIPROM

Authors Foysol Chowdhury (CCS), Adrian Ionescu (EPFL), Lars-Erik Wernersson (LUND), Véronique Gobry, Kirsten Leufgen, Peter Ulrich (SCIPROM)

<sup>&</sup>lt;sup>1</sup> R = Report, P = Prototype, D = Demonstrator, O = Other

$<sup>^{2}</sup>$  PU = Public, PP = Restricted to other programme participants (including the Commission Services, RE = Restricted to a group specified by the consortium (including the Commission Services), CO = Confidential, only for the members of the consortium (including the Commission Services)

<sup>&</sup>lt;sup>3</sup> Measured in months from the project start date (M01)

## **Revision history**

| Version | Date       | Author                          | Comment                             |

|---------|------------|---------------------------------|-------------------------------------|

| 0.1     | 23-10-2015 | V. Gobry                        | First draft                         |

| 0.2     | 11-11-2015 | LE. Wernersson                  | Completions dissemination           |

| 0.3     | 16-11-2015 | F. Chowdbury                    | Completions exploitation            |

| 0.9     | 24-11-2015 | V. Gobry, K. Leufgen, P. Ulrich | Review, completions, rearrangements |

| 1.0     | 24-11-2015 | K. Leufgen                      | Final version                       |

Point of Contact<sup>4</sup>: Dr. Kirsten Leufgen, SCIPROM. kirsten.leufgen@sciprom.ch +41 21 694 0412

<sup>&</sup>lt;sup>4</sup> For up-to-date contact details, please refer to the contact page of the Members section: http://www.E2SWITCH.org/members/contactdetails/index.php.

## Contents

| SUM        | MARY                                                                               | 4  |

|------------|------------------------------------------------------------------------------------|----|

| <u>1</u> C | VERVIEW                                                                            | 6  |

| 1.1        | LIST OF WP7 DELIVERABLES                                                           | 6  |

| 1.2        | LIST OF MILESTONES                                                                 | 6  |

| 1.3        | DISSEMINATION AND EXPLOITATION MANAGEMENT STRUCTURE                                | 6  |

| <u>2</u> D | DISSEMINATION OF KNOWLEDGE                                                         | 7  |

| 2.1        | MAIN DISSEMINATION ACTIVITIES FOR THE CURRENT PERIOD                               | 7  |

| 2.1.1      | COMMUNICATION TO THE GENERAL PUBLIC (M01 – M42)                                    | 7  |

|            | COMMUNICATION TO THE RELEVANT SCIENTIFIC COMMUNITIES (M07 – M42)                   | 7  |

|            | PUDF PAGE OF THE E <sup>2</sup> SWITCH WEBSITE                                     | 9  |

| 2.3        | UPDATE ON THE PLANNED DISSEMINATION ACTIVITIES FOR THE NEXT PERIOD M25-M42         | 11 |

| <u>3</u> E | EXPLOITABLE KNOWLEDGE AND ITS USE                                                  | 12 |

| 3.1        | PLANNED EXPLOITATION ACTIVITIES                                                    | 12 |

| 3.1.1      | OUTLINE EXPLOITATION PLAN                                                          | 12 |

| 3.1.2      | OUTLINE EXPLOITATION ROADMAP                                                       | 12 |

| 3.1.3      | KEY EXPLOITATION AREAS                                                             | 19 |

| 3.1.4      | CURRENT STEPS TOWARDS SUCCESSFUL EXPLOITATION OF THE E <sup>2</sup> SWITCH RESULTS | 21 |

| <u>4</u> D | DISSEMINATION AND EXPLOITABLE KNOWLEDGE IN FINAL PUDF FORMAT                       | 22 |

| A.         | DISSEMINATION OF KNOWLEDGE (CONFIDENTIAL)                                          | 22 |

| A.1        | SCIENTIFIC (PEER REVIEWED) PUBLICATIONS                                            | 22 |

| B.         | EXPLOITABLE KNOWLEDGE AND ITS USE (CONFIDENTIAL)                                   | 29 |

| B.1        | APPLICATIONS FOR PATENTS, TRADEMARKS, REGISTERED DESIGNS, ETC.                     | 29 |

| B.2        | EXPLOITABLE FOREGROUND                                                             | 32 |

| REF        | ERENCES                                                                            | 34 |

### Summary

This document contains updates on the "**Plan for Use and Dissemination of Foreground (PUDF)**" as set in work package 7 (WP7) of the description of work defined for the E<sup>2</sup>SWITCH project. All dissemination and exploitation activities, together with details of specific deliverables as outlined in WP7 are planned and recorded in this document.

As part of its primary impacts,  $E^2SWITCH$  aims to enable ultra-low voltage/low power nanoelectronic solutions through the exploitation of Tunnel Field Effect Transistors (TFET). Those new devices are anticipated to go beyond current industrial roadmaps in terms of energy efficiency by a factor or 10 to 100 times, with an operating voltage below 250mV with standby power reduction by more than 1000x.

With such potentials for energy efficient solutions, dissemination and exploitation tasks will promote the long-term impact on both the scientific and the technical fields.

The main cornerstones of this work are the following:

- Setup and maintenance of the project's website, publication of results in the scientific community, and dissemination to a wider public through academic, technology transfer and industrial channels.

- Development of a general exploitation strategy for E<sup>2</sup>SWITCH results and definition of a concrete policy for the exploitation of the technical results of the project in industrial applications with two main paths: (i) digital and (ii) analog/RF.

- Networking with other EC funded research projects as well as with ENIAC and ITRS working groups and other possible players concerning publicly available project activities.

- Organisation of international workshops on the specific scientific and technical research addressed by the project: energy efficient devices and technologies and their applications in digital and non-digital applications.

- Contribution to the training of PhD students and senior staff through scientific seminars, summer schools, specific chapters in lectures and books.

- Encouragement of mobility of young researchers and PhDs between partners.

All partners involved with research will continuously and proactively evaluate opportunities for dissemination and exploitation of the project concept and its results. SCIPROM, responsible for  $E^2$ SWITCH management, takes care of the website. LUND, as dissemination manager, will coordinate all dissemination activities and leads the work. CCS, with the help of EPFL, will overlook the project's exploitation based on all  $E^2$ SWITCH findings as agreed by all partners. More details on the  $E^2$ SWITCH dissemination and exploitation strategies and related IPR considerations can be found in Section 3.2 of the DoW [1].

The first two years of the  $E^2$ SWITCH consortium have been very productive in terms of scientific results and the partners have been very active in the dissemination of the results to the various stakeholders including the scientific community, relevant industry, and the general audience. The complete list of dissemination activities is available on the web page of the consortium and within Section 4 of this document. In Table 1 some statistics of the activities during the first 24 months is given:

| Type of dissemination activity            |     |

|-------------------------------------------|-----|

| Film                                      | 1   |

| Flyer                                     | 1   |

| Scientific presentation                   | 54  |

| Poster presentation to a scientific event | 1   |

| Organisation of workshop                  | 2   |

| Press release                             | 1   |

| Publication                               | 39  |

| Web sites / Applications                  | 1   |

| Total                                     | 100 |

**Table 1:** Dissemination activities, status 23 Nov 2015.

Highlights include 6 invited talks, 3 high-impact journal papers (Nature photonics, Nano letters) and 2 high-impact conference papers (IEDM 2015).

The full list of E<sup>2</sup>SWITCH dissemination activities can be found in Section 4 of this document.

#### Workshops:

- In the Quest for Zero Energy Devices and Circuits Workshop at ESSDERC 2014, Venice, Italy

- Steep Slope Transistors International Workshop at Notre Dame, 2015, USA

### 1 Overview

The E<sup>2</sup>SWITCH WP7 comprises all dissemination and exploitation activities.

#### 1.1 List of WP7 Deliverables

- D7.1 Website (first preliminary version) M03

- D7.2 Press release at the project start M01

- D7.3 Press release in the project end M42

- D7.4 Video introduction to the project M06

- D7.5 Project flyer M06

- D7.6 First version of the Plan for Use and Dissemination of Foreground (PUDF) M06

- D7.7 First update of the PUDF M24

- D7.8 First public E<sup>2</sup>SWITCH workshop M24

- D7.9 Roadmap for commercial use of  $E^2$ SWITCH results M42

- D7.10 Final public E<sup>2</sup>SWITCH workshop M42

#### 1.2 List of Milestones

- M7.1 Final PUDF ready for consortium approval M41

- M7.2 Roadmap for commercial use of  $E^2SWITCH$  results ready for consortium approval M41

#### 1.3 Dissemination and Exploitation Management Structure

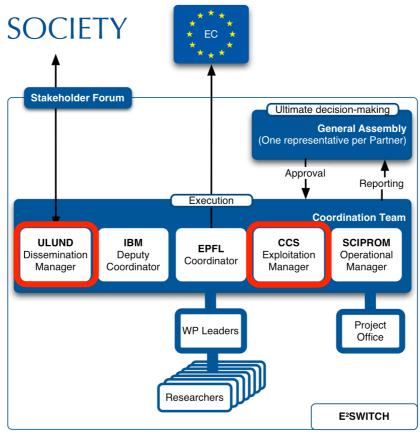

The integration of the dissemination and exploitation activities within the management structure is described in detail in Sections 2.1 and 3.2 of the DoW [1].

Fig. 1. Structure of the E<sup>2</sup>SWITCH management structure with the position of the Dissemination and Exploitation managers.

### 2 Dissemination of knowledge

This section describes the dissemination measures, including any scientific publications relating to foreground. The content of the corresponding section of the online PUDF on SESAM that is part of the final report will be made available in the public domain, thus demonstrating the added value and positive impact of the project on the European Community. However, the present version contains additional information and has to be treated as confidential.

This section includes a list of planned, ongoing and completed dissemination activities (publications, conferences, workshops, web, press releases, flyers, etc). Articles that have been published in the popular press will be listed as well.

The list of all published scientific (peer reviewed) publications relating to the foreground of the project is given in Table A.1 (see Section 4), respectively.

A list of all completed dissemination activities is given in Table A.2.

The impact of  $E^2SWITCH$  on the advancement of science and ultimately the benefit of citizens will be fundamentally linked to the presentation of its results in scientific conferences and especially publications in high-impact journals. In addition, the  $E^2SWITCH$  consortium considers dissemination to stakeholders and a wider public to also be of high importance to its success. The **Dissemination Manager (Lars-Erik Wernersson, LUND)** will liaise with the Exploitation Manager on approving all disclosures. They will develop and administer a procedure for the submission and approval of disclosures before publication. The partners have experience from previous and current collaborative research projects where such procedures have been successfully utilised to ensure widespread and beneficial dissemination whilst protecting valuable Intellectual Property.

The Dissemination Manager, together with SCIPROM, will support coherent and high quality dissemination by providing guidelines and templates for the production of documents, press releases and presentations. In addition, internal peer review of drafts will be supported to ensure articles generated for publication are of the highest quality and appropriate for their target audiences. This will be particularly important in the support and development of new researchers in the project team.

#### 2.1 Main dissemination activities for the current period

#### 2.1.1 Communication to the general public (M01 – M42)

Lead Partner SCIPROM; other partners: All

Communication to the general public has been achieved through a variety of communication means.

The  $E^2$ SWITCH website (D7.1, M03), has been set up, is hosted and maintained by SCIPROM. It contains a consortium-intern section for data exchange and management and a public section that serves as a dissemination gateway. For the latter, care will be taken to specifically address all stakeholders in energy efficient devices and technologies and their applications in digital and non-digital applications.

A press release has been issued in the first year of the project (D7.2). A project flyer (D7.5, M09) introducing the project has been prepared by SCIPROM in collaboration with all partners in the beginning of the project and updated in M14. An introductory video has also been released in the beginning of the second year (D7.4). It is conceived as a teaser directing the different stakeholders to the relevant part of the website.

#### 2.1.2 Communication to the relevant scientific communities (M07 – M42)

Lead Partner: EPFL: other partners: All research partners

One of the major impacts of  $E^2$ SWITCH will be the promotion of European scientific leadership in the area of future electronic devices and low-power technologies. This will be achieved by:

- Scientific publications in high-ranked peer-reviewed scientific journals.

- Arrange partners of E<sup>2</sup>SWITCH to regularly give presentations in international scientific conferences, including the presentation of keynote speeches.

- Organize dedicated dissemination events devoted to the project topics at the major European PhD summer schools, such as for instance: SINANO Italy, MIGAS France, Dresden Academy Germany)

#### 2.1.2.1 Publications

Table A.1 in Section 4.1 shows a list of all E<sup>2</sup>SWITCH peer-reviewed articles published so far.

#### 2.1.2.2 Participation in Scientific conferences

All E<sup>2</sup>SWITCH presentations at scientific conferences and workshops are shown in Table A.2 (Section 4.1).

#### 2.1.2.3 Workshops

Two public workshops have been organized during the period (D7.8, M24) Both workshops were performed in combination with a larger workshop, international conference or trade fair that attract a wide audience in the field. In addition, a final workshop will be organized at the end of the project. It will be combined with a presentation of the main scientific results obtained from the  $E^2SWITCH$  project including prototypes and devices.

The 1st workshop of the E<sup>2</sup>SWITCH project entitled "In the Quest of Zero Power: Energy Efficient Computing Devices and Circuits" was held on September 26th, 2014 in Venice as satellite event to the international conference ESSDERC/ESSCIRC 2014. It was conducted as a scientific dissemination, networking and exploitation event of the E2SWITCH project at the end of the 1st year of work.

The workshop included a series of presentations dealing with state of the art advancements in Tunnel FETs as most promising energy efficient device candidates able to reduce the voltage supply of integrated circuits (ICs) below 0.25V and be hybridized with CMOS technology. It also served as a platform for the discussion of suitable exploitation tracks for the technique.

The programme featured focused reports on DC/AC benchmarking for complementary n- and p-type Tunnel FETs, compact models for digital and analog/RF, device scalability, operational reliability and ITRS metrics. The international keynote invited speakers from USA (prof. Alan Seabaugh) and France (Dr. Francis Balestra and Dr. Costin Anghel) provided vision and opinions from outside the E2-SWITCH Consortium.

The workshop was open to the whole ESSDERC/ESSCIRC audience and to other speakers who attended only the workshop day; the profile of the 25 registrants was very diverse, ranging from PhD students and researchers to industry representatives from both the consortium and the public.

Overall, the different presentations and interactions pointed out the importance and the significant advancement made by the Tunnel FET technology in the last year and its importance as one of the very few device candidates that can offer added value to the well established advanced silicon CMOS.

**The 2nd workshop** of the E<sup>2</sup>SWITCH project entitled "Steep Transistors Workshop" was held at the University of Notre Dame, Notre Dame, IN, October 5-6, 2015.

As part of the dissemination activities of the  $E^2$ SWITCH consortium an International Workshop on Steep Slope Transistors was arranged on Oct 5-6, 2015, at University of Notre Dame, USA. The workshop was a co-arrangement between the European  $E^2$ SWITCH consortium and the US sister organization, LEAST (Low-Energy System Technology). The workshop was co-arranged by Prof. A. Seabaugh at University of Notre Dame and Prof. L.-E. Wernersson at Lund University, who also act as Dissemination Manager for  $E^2$ SWITCH. It was decided to host the workshop in the US to warrant a high participation from the US side as this increased the visibility in the US for the European effort. The workshop was by invitation only, whereas a few, mainly US, PhD-students also attended.

In total 95 participants attended estimated to be about 80% of all active professors in the field, demonstrating the great interest for the workshop. The major contributions were from the US LEAST center and the E<sup>2</sup>SWITCH consortium, but the workshop was open for international contributions as well and in total 38 labs were represented. Industry participation was notable with participation from Intel, Toshiba, Texas Instruments, Taiwan Semiconductor Manufacturing Company (TSMC), Cambridge CMOS Sensors, IBM (US), IBM (Europe), and GlobalFoundries. Both Teledyne and Raytheon unfortunately had to cancel at the last minute, but showed strong interest.

The workshop was divided into different sections with speakers giving 10 min focussed talks on their respective topic of interest. Since the audience knows the field and most of the work at the different groups,

no introductions were needed, but we focussed on the key aspects. From the  $E^2SWITCH$  consortium the following talks were given:

**Table 2.** Presentations at the 2nd  $E^2$ SWITCH workshop entitled "Steep Transistors Workshop", University of Notre Dame, USA (October 5-6, 2015).

| Speaker              | Title of the talk                                                            |  |  |  |  |  |

|----------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| Prof. A. Ionescu     | Functional diversification with TunnelFETs                                   |  |  |  |  |  |

| Prof S. Mantl        | TFETs for ultra low power                                                    |  |  |  |  |  |

| Prof. E. Gnani       | Stress: performance booster or killer for III-V-based NW TFETs?              |  |  |  |  |  |

| Prof. D. Esseni      | Off-State behavior for MOSFETs and Tunnel FETs approaching 10nm gate length  |  |  |  |  |  |

| Dr. H. Riel          | Where are we with TFETs?                                                     |  |  |  |  |  |

| Prof. LE. Wernersson | Nanowire Tunnel FETs: Axial or Radial TFETs?                                 |  |  |  |  |  |

| Dr. F. Chowdhury     | Benchmarking of TFET Analog Circuits: The Sensor Applications<br>Perspective |  |  |  |  |  |

Besides the scientific and technical presentations, we arranged 5 discussion sessions were moderators were given questions that were addressed by two selected speakers from the participants. These moderators and speakers were selected to balance the efforts within the two host organisations that is the US and the European participants. The discussed topics included the Channel Materials, the Fundamental Understanding, Gate Geometry and Gate Stack, Alternative Mechanisms for Steep Transistors, and Accelerating the development of steep transistors. During these sessions we had a vivid discussion on the topics with the goals to pin-point the critical questions in the field of TunnelFETs. Looking at the device structure with many eyes with different backgrounds helped to get a clearer picture on the perspective on the field.

The workshop will be summarized in a short position document that is currently under writing. Generally we can conclude that there is a strong interest in realizing transistors that operate with high performance at 300 mV or below. The TunnelFET is generally believed to be the leading contender among the device structures. In the US, much effort is directed to implement TunnelFETs in Transition Metal Dichalcogenide (TMD) materials, whereas the European efforts are based on Si- and III-V devices, in line with efforts in Asia. The rationale for the US effort has been based on a strategy decision within the funding bodies (Semiconductor Research Corporation, SRC) where industry wanted to focus on TMDs. It appears that that this strategy now will change and it may open for efforts in Si and III-V materials also in the US again.

On the technical side there is still a gap between the performance predicted by simulations and the experimental results. It appears that the modelling is expected to quite well capture the essence of the device structure and the tunnelling mechanisms. However, the experimental implementations need further development both related to the geometrical sizes and the influence of the defects on the transistor properties. Many implementations are based on comparably thick body devices were the electrostatics are not ideal. The transistor is sensitive to the exact doping levels, for instance in the source region, as well as the presence of defects at the very local region of tunnelling. These are issues that the scientific community as well as the members of the  $E^2SWITCH$  consortium will need to address in the future. They were well in line with the current project plan of  $E^2SWITCH$ .

All the information about past or future workshop co-organized by the E<sup>2</sup>SWITCH project is available online on the project workshops webpage: http://e2switch.org/output/workshops/

The consortium will also maintain or establish links for fruitful exchanges and collaborations with other European and global initiatives with scientific relevance to  $E^2SWITCH$ . Potential conflict with intellectual property protection and exploitation of project results will be carefully evaluated before publication of results. All scientific communications will be summarized in the present PUDF (D7.6, D7.7, final report).

### 2.2 PUDF page of the E<sup>2</sup>SWITCH website

In addition to the present PUDF that allows reporting the project's dissemination activities to the EC, all dissemination activities also have to be reported to the Consortium for approval.

As part of the project e-tools, the members section of the project website includes a PUDF page (<u>http://www.e2switch.org/members/pudf/index.php</u>) displaying the approval procedure for any dissemination activities as defined in the project consortium agreement [2] and reminding the acknowledgement of funding rules defined in the project management guidelines [3].

The PUDF page also provides the partners with an online tool to notify, request approval and report a dissemination activity within the consortium.

## Report a dissemination activity

If you are planning a dissemination activity or you want to report a dissemination activity that you have performed, you should follow the procedure below.

| Ste | p 1: | Up | load | additional | information |

|-----|------|----|------|------------|-------------|

|-----|------|----|------|------------|-------------|

Additional information could be an abstract for a conference presentation, a poster, a draft publication. You can only upload one single file, but it may be a zipped folder.

| Select file             |            |        |

|-------------------------|------------|--------|

| Filename                | Size       | Status |

| Drag                    | file here. |        |

| O Add File Start Upload |            |        |

| p 2. Fill in the form   |            |        |

Finally, it gives an overview of the dissemination activities within the consortium along with their current status and a link to the corresponding file

| Dissemination table<br>Status of activity<br>• after submission of form: notified<br>• without objection after 14 days: agreed<br>• in case of objection: @blected<br>• after publication: public |                     |                                                     |                                                   |                                                           |                                                       |                       |                                                                                                                  |                                                                              |                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------|

| Timestamp                                                                                                                                                                                         | Status<br>& link \$ | Type of<br>activity 🔶                               | Contact person<br>\$                              | Title of event                                            | Authors<br>\$                                         | Event date            | Place<br>\$                                                                                                      | Audience<br>+                                                                | Countries<br>\$ |

| 2014-08-08                                                                                                                                                                                        | notified            | Oral<br>presentation<br>to a<br>scientific<br>event | <u>M Foysol</u><br><u>Chowdhury</u><br><u>CCS</u> | TSensors (Trillion Sensors)<br>Summit Munich              | Dr. M F Chowdhury                                     | 15th – 17th Sept 2014 | TSensors Summit<br>, Munich,<br>Germany                                                                          | Scientific<br>Community,<br>Industry(100–<br>499)                            | Worldwide       |

| 2014-06-09                                                                                                                                                                                        | public              | Web sites /<br>Applications                         | Filippo Gander<br>SCIPROM                         | E2SWITCH project website                                  | Filippo Gander                                        | 01-01-2014            | www.e2switch.org                                                                                                 | Scientific<br>Community, Civil<br>Society, Policy<br>makers,<br>Medias(>500) | Worldwide       |

| 2014-04-30                                                                                                                                                                                        | agreed              | Oral<br>presentation<br>to a<br>scientific<br>event | <u>Arnab Biswas</u><br><u>EPFL</u>                | A First Order<br>Capacitance-Voltage<br>model for DG-TFET | Arnab Biswas, Luca De<br>Michielis, Adrian M. Ionescu | 09-09-2014            | International<br>Conference on<br>Simulation of<br>Semiconductor<br>Processes and<br>Devices,<br>Yokohama, Japan | Scientific<br>Community(100–<br>499)                                         | Worldwide       |

Fig. 3. Screenshot of partial dissemination table, showing the layout and colour coding of status as applied.

#### 2.3 Update on the planned dissemination activities for the next period M25-M42

During the period of M25-M42 we plan to continue the dissemination activities according to the original plan described in Section 2.3. In particular, we intend to continue the effort to publish in leading journal and at key conferences following the track-record of the first two years and targeting the same journals and conferences listed in the DoW. We anticipate an even increasing publication effort as results typically are generated towards the end of a project. Currently, there are three upcoming presentations to scientific events (Table 3).

| No | Title                                                                                                  | Main author(s)                                                                                                                                              | Name and location of the event | Date       |

|----|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------|

| 1  | 'Presentation of TFET work on InAs/Si<br>TFETs '                                                       | K. Moselund, D. Cutaia, M. Borg, H.<br>Schmid and H. Riel                                                                                                   | QCom Workshop                  | 31/11/2015 |

| 2  | InAs-GaSb/Si Heterojunction Tunnel<br>MOSFETs: An Alternative to TFETsas<br>Energy-Efficient Switches? | Hamilton Carrillo-Nunez, Mathieu Luisier,<br>Andreas Schenk                                                                                                 | IEDM Washington                | 08/12/2015 |

| 3  | International Electron Devices<br>Meeting (IEDM)                                                       | J. Cao, D. Logoteta, S. Ozkaya, B. Biel, A.<br>Cresti, M.G. Pala, and D. Esseni                                                                             | IEDM in Washington D.C.        | 07/12/2015 |

| 4  | Novel SiGe/Si line tunneling TFET<br>with high lon at low VDD and constant<br>SS                       | S. Blaeser, S. Glass, C. Schulte-Braucks,<br>K. Narimani, N. v. d. Driesch, S. Wirths, A.<br>T. Tiedemann, S. Trellenkamp, D. Buca, Q.<br>T. Zhao, S. Mantl | IEDM 2015 Washington           | 07/12/2015 |

Table 3. List of planned presentations to scientific events (status: 23 November 2015).

We will continue to update and maintain the website with relevant news from the  $E^2$ SWITCH consortium and present scientific highlights as they develop within the project.

We intend to arrange at least one international workshop in the period of M25-M42. Based on the success of the International workshop on Steep Slope Transistors (described in Section 2.3) and the international interest in the field, we plan to arrange a follow up workshop in Europe during the period coordinated from LUND. We also aim for a final workshop at the end of the project aiming at presenting the general results of  $E^2SWITCH$  to a wider audience of stakeholders, including both academia and industry. It is at this stage not clear if these two events will be separate or if they will be combined. The consortium will discuss and decide in the period of M25-M32.

### 3 Exploitable knowledge and its use

Key exploitation will focus on energy efficient electronics for sensors in consumer and automotive industry to guarantee early awareness of the industrial potential originating from the technology and knowledge generated by the project. Furthermore, it will pursue the exploitation of project results by generating IP, device and technology know how.

This Section specifies the exploitable foreground and provides the plans for exploitation.

A summary of the expected exploitable results will be given in Table B.2.1. The template for the exploitation tables are presented in Section 4. The applications for patents, trademarks, registered designs, etc. will be listed in Table B.1.

Exploitable results will then be characterised in more detail in tables B2.2 of the final PUDF.

The exploitation manager (Foysol Chowdhury, CCS) with the help of EPFL will overlook the project's exploitation based on all E2SWITCH findings as agreed by all partners.

#### 3.1 Planned exploitation activities

#### 3.1.1 Outline Exploitation Plan

A plan for the exploitation strategy incorporating key deliverables and milestones is given below.

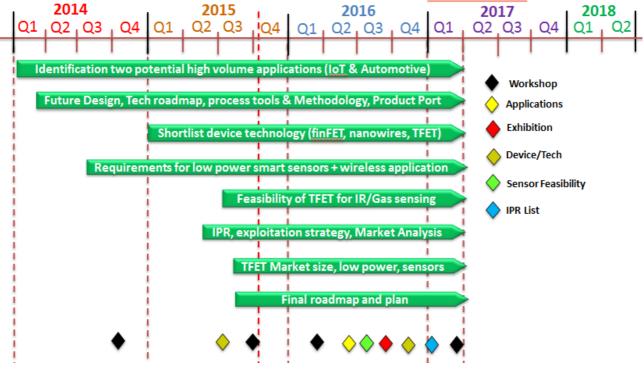

Fig. 4. Exploitation strategy correlation with WP7 deliverables and milestones

#### 3.1.2 Outline Exploitation Roadmap

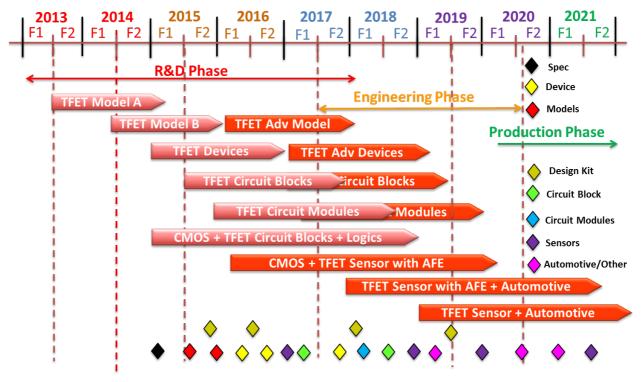

The first Consortium exploitation roadmap has been drafted by CCS and discussed with the  $E^2SWITCH$  members. The exploitation roadmap takes into account the R&D nature of this project and is divided into three phases; (1) R&D, (2) Engineering and (3) Production phase.

The exploitation starts from the novel models and device technologies that are currently developed in the project and is considering them as key circuit blocks allowing the achievement of digital and analog circuit functions. An engineering phase is planned after mid-2017, based on the validated IC blocks based on Tunnel FETs on the two platforms (SiGe and III-V) available in the Consortium. The engineering phase will also realistically consider implementation in two-die solutions, combining mature CMOS design with Tunnel FET circuits, according to the specifications for Internet-Of-Things (IoT) and automotive applications that can benefit from the low power consumption and reduced temperature drift of the new technology.

The Consortium will be proactive in producing patents when possible and seize opportunities on the markets, including partnerships with end-users beyond the lifetime of the project.

The risks associated with this exploitation roadmap are related to the achievements of the final figures of merit of Tunnel FET circuits but also, especially, to the reliability, robustness and cost of the IC implemented in the new technology.

The reliability will be partially addressed in the characterization workpackage, as an additional activity, supporting the potential exploitation. We will particularly try to apply and adapt traditional CMOS reliability test for digital circuit and study the behaviour of the devices and circuits over ranges of temperatures corresponding to industrial applications.

The cost risk is mitigated by the fact that the Consortium approach is to integrated Tunnel FETs on advanced CMOS platforms; therefore, at long term Tunnel FET should become just a design option into existing CMOS libraries. This is expected to reduce high additional costs.

Fig. 5. Initial E<sup>2</sup>SWITCH exploitation roadmap.

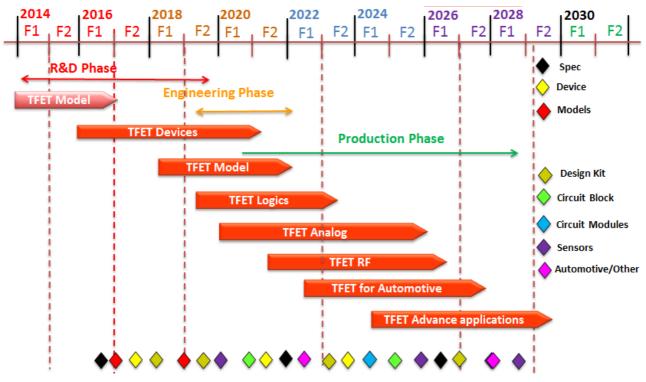

The process and technology roadmap proposed in Figure 5, was considered to be highly optimistic and it was felt that TFET technology in terms of material selection and finalising the device structure will time to evolve and R&D phase could go beyond 2020. The engineering phase will then follow for at least 2 years, after 2022 production phase could begin as show in the revise roadmap in Figure 6.

Fig. 6. E<sup>2</sup>SWITCH technology exploitation revised roadmap.

#### 3.1.2.1 Device/Technology Roadmap

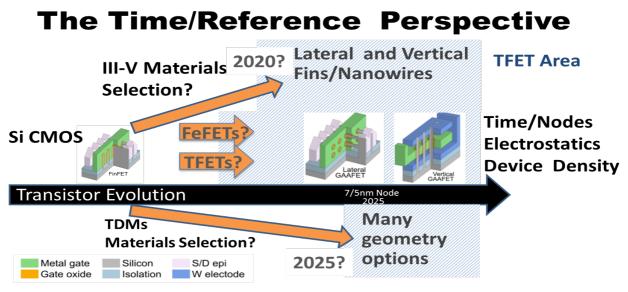

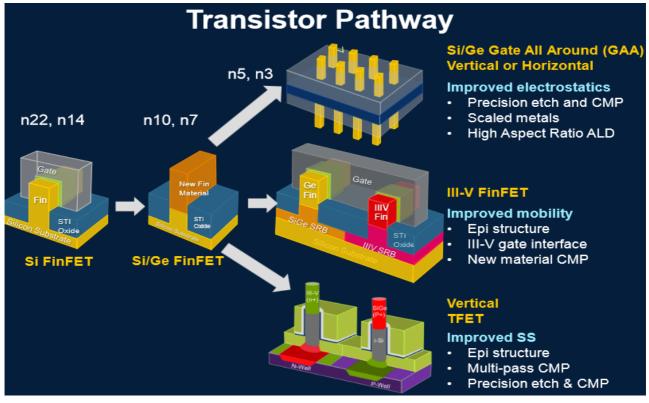

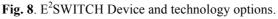

Figure 7, shows a possible device/technology roadmap. As can be seen, there are many options available and success will depend on how easily processes and appropriate tooling can be developed for high volume commercial manufacturing.

**Fig. 7**. E<sup>2</sup>SWITCH Device and technology roadmap.

Gradual transition from FinFET device options to TFET is shown in Figure 8.

# **E<sup>2</sup>SUITCH** Grant Agreement No. 619509

#### 3.1.2.2 Application Roadmap

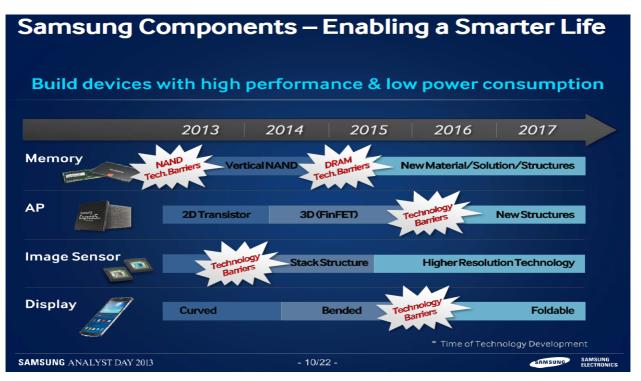

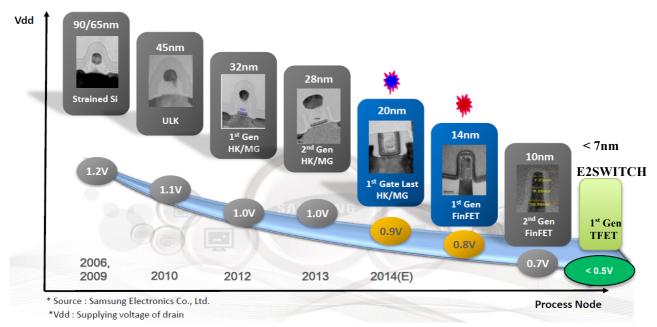

Examples of Samsung's perception of technology and application areas are show in Figure 9, here the main driving factors are performance and low power consumption. Based in this, a similar roadmap can be determined, where key barrier is technology – this is what E2SWITCH project is aiming to contribute in finding solutions.

Fig. 9. Example of high volume application beyond CMOS technology and barriers

Figure 10, shows that  $1^{st}$  Gen, FinFET devices are in commercial production with 0.8V supply voltage, and  $2^{nd}$  generation will follow 0.7V. Beyond this point TFET devices operated below 0.7V, will help to push technology to overcome the barrier. At present there are 1 billion transistors per person!

Fig. 10. Example of technology barriers E2SWITCH is aiming to solve

#### 3.1.2.3 Low power sensor roadmap

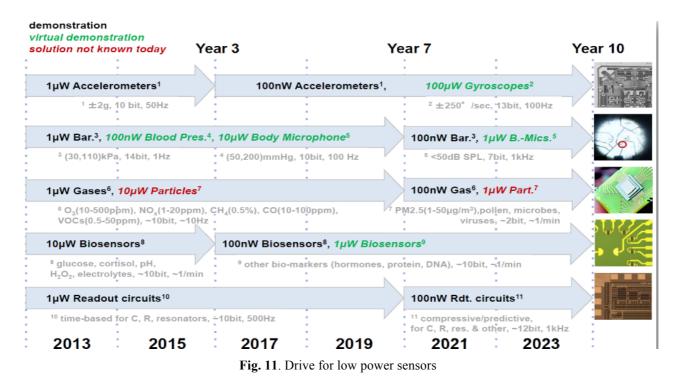

One of the biggest areas where TFET solutions will benefit is the low power sensors for IoT applications, and based on this, nice summary of the power requirement roadmap is shown in Figure 11. With low power sensing solutions, it will also enable wider exploitation of energy-harvested sensing applications.

#### 3.1.2.4 Automotive application roadmap

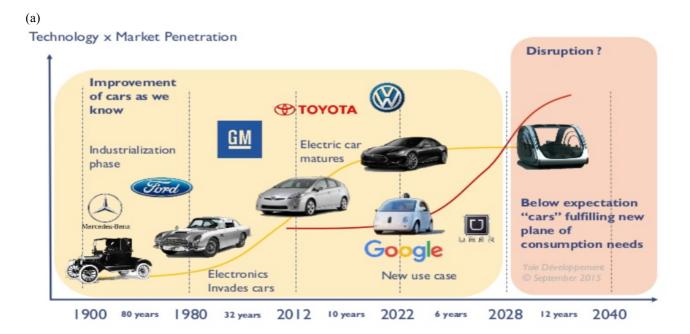

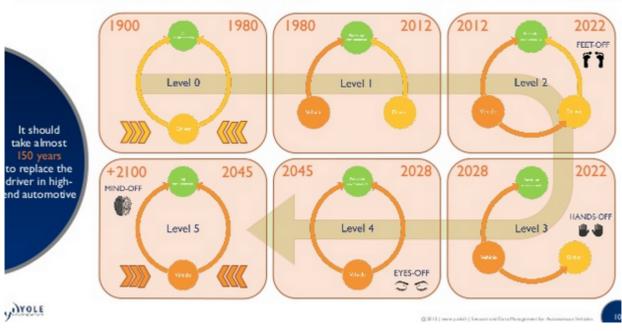

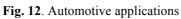

It has been estimated that average car contains an average of \$300 to \$400 worth of electronic devices. With autonomous driver assisted vehicle, demand for low power, high performance electronics will grow. Figure 12a-c summarize some of the key players in this field and market size.

(b)

# **E<sup>2</sup>SUITCH** Grant Agreement No. 619509

#### 3.1.2.5 Market facts and figures

Some market facts and figures for semiconductor industry are shown in Figures 13-16.

Fig. 13. Global Semiconductor companies and market values (Ref - NASDAQ)

## US vs Europe Market Comparison - Semiconductors

Fig. 14. US vs EU Semiconductor companies and market values (Ref – NASDAQ)

## **Expect Dollar Content To Continue To Increase**

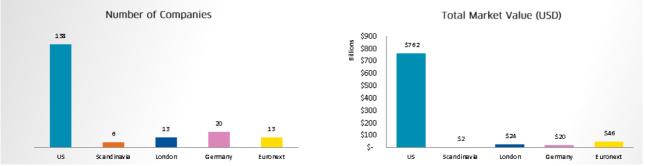

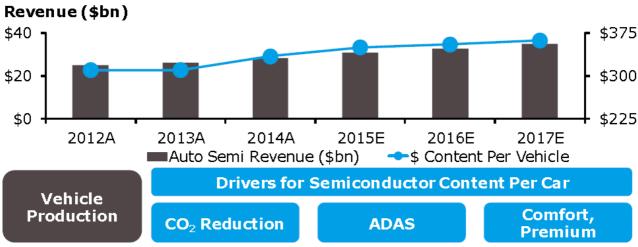

**Fig. 15.** Key driving factors for semiconductor market: Strong Growth in Automotive; Sector IoT – 50 Billion Connected Devices by 2020; Emergence of Big Data; China Inc. Interested In Semiconductors

### Connected Devices to Accelerate Installed Base (bn)

| Target        | Acquirer                                     | Transaction<br>Value <sup>(1)</sup> (\$m) |

|---------------|----------------------------------------------|-------------------------------------------|

| NP            | 建广资产<br>JAC Capital                          | \$1,800                                   |

| ISSI          | 武岳峰资本<br>SUMMITVIEW CAPITAL                  | \$736                                     |

| STATSChipPAC* | 6番电科技                                        | \$780                                     |

| Omni Sision.  | 半创投资<br>HUA CAPITAL                          | \$1,670                                   |

| SPREADTRUM®   | PDSTI<br>上海浦东科技投资有限公司                        | \$616                                     |

|               | <b>股 紫光集团有限公司</b><br>TSTINGHUA UNIGNOUP LTD. | \$1,440                                   |

| RDX           | ▶ 紫光集团有限公司                                   | \$907                                     |

Fig. 16. China acquisition - 7 major transactions, more expected

#### 3.1.3 Key Exploitation Areas

There are two areas of exploitations identified by the consortium:

#### 3.1.3.1 Academic partners

- The knowledge and expertise acquired will underpin further research by the Universities.

- Strengthen their competitiveness as higher education institutions worldwide.

- Initiate **advanced graduate thesis projects** in very appealing and current topics such as "Emerging devices", "TFET circuit design".

- Promote students' awareness and their interest in energy efficient electronics and zero-power autonomous systems. The combination of **high-level universities with well-known research institutes and industry** depicts an excellent environment for students and postdoctoral researchers.

- Provide access to advanced technological and computational platforms and enable insight into the scientific and industrial environment.

- Encourage engineers and scientists in Europe to pursue a career in the field of nanoelectronics.

- Devise new practical and theoretical methods and tools to support future capabilities.

- Establish vehicle for **research funding** applications, studentships, doctoral theses, graduate dissertations and undergraduate projects and thus will help European universities to act strong on common performance metric in a competitive international environment.

- A key goal of E<sup>2</sup>SWITCH is to strengthen the **competitiveness of Europe**.

- Initiate exploitation of the results by transferring technology to industrial partners to ensure rapid spread to European industrial companies.

- Propagate interactions with international centres of competencies in the field of energy-efficient computing to global Stakeholder Forum.

- Engage with licensing of know-how with industry to trigger further R&D co-operation with European and worldwide industry.

#### 3.1.3.2 Industrial partners

- Identify potential for commercial exploitation in two potentially huge applications ICT and sensors, incorporating consumer and automotive market sectors.

- Define **future device/technology roadmap** including the design process tools and methodology and **product portfolio**.

- Evaluate power consumption requirements for future Supercomputers to set a timescale for leading-edge power-efficient logic device technology deployment.

- Shortlist possible device technology such as FinFET architectures, nanowires. SiGe or SOI-CMOS channel materials for pFET and III-V for nFETs, leading to TFET as a stand-alone device.

- Identify the requirements for low power smart sensors for portable applications as well as for wireless sensor network applications.

- Investigate the feasibility of using TFET devices for **smart IR and gas sensors** with integrated circuits having extremely low power consumption and on-chip temperature sensing together with analogue readout.

- Establish state-of-the art, IPR protection strategies, the consortium exploitation strategy and including a *detailed market analysis for semiconductor companies*.

- Provide periodic report of the size of potential application markets for Tunnel FET based circuits in: (i) low power electronics for portable systems and (ii) low power smart systems for high temperature sensing, respectively.

- Produce exploitation roadmap and final exploitation plan, as a part of the final PUDF with feedback to consortium and advice from the members of the stakeholder forum.

Based on the above, outline plan for exploitation activities are summarised in Figure 17.

# **E<sup>2</sup>SUITCH** Grant Agreement No. 619509

Fig. 17: Outline plan for exploitation activities

#### Trade fare/Exhibition:

Possible invited talk at: <u>http://www.idtechex.com/energy-harvesting-europe/speakers.asp</u> This would give an opportunity to promote TFET technology for IoT applications.

#### 3.1.4 Current steps towards successful exploitation of the E<sup>2</sup>SWITCH results

On 26 September 2014, a **first E<sup>2</sup>SWITCH workshop** was held in the frame of the ESSDERC conference 2014 in Venice. Involving speakers from the consortium and leading industry, the exploitation of expected  $E^2SWITCH$  results will be a topic of discussions, centred on an exploitation-focussed keynote and further contributions from industry.

Moreover, details of the  $E^2$ SWITCH exploitation activities have been discussed within the consortium on the basis of the template table B.2.1 (see Section 4) and the "innovation radar" questionnaires of the first project review.

### 4 Dissemination and Exploitable knowledge in final PUDF format

In the following the tables used for the final format of the PUDF are shown.

The dissemination related tables A1 and A2 are completed based on the information available on the online PUDF page of the  $E^2$ SWITCH member section (status 11 November 2015)

#### A. Dissemination of knowledge (confidential)

#### A.1 Scientific (peer reviewed) publications

**Table A.1.** List of scientific (peer reviewed) publications (public). Status 23 November 2015.

| No | Title                                                                                                                    | Authors                                                                                                                                                                         | Title of the<br>periodical or<br>the series             | Volume,<br>pages and<br>year           | Publisher                       | Permanent<br>identifiers (D.O.I) | Open<br>access |

|----|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------|---------------------------------|----------------------------------|----------------|

| 1  | Vertical III-V Nanowire<br>Device Integration on Si(100)                                                                 | B. Mattias Borg, Heinz Schmid,<br>Kirsten E. Moselund, Giorgio<br>Signorello, Lynne Gignac, John<br>Bruley, Chris Breslin, Pratyush<br>das Kanungo, Peter Werner,<br>Heike Riel | Nano Letters                                            | 14 (4), 1914-<br>1920, 2014            | ACS                             | 10.1021/nl404743j                | No             |

| 2  | Electron-Hole Bilayer TFET:<br>Experiments and Comments                                                                  | A. Revelant, A. Villalon, Y. Wu,<br>A. Zaslavsky, C. Le Royer, H.<br>Iwai, S. Cristoloveanu                                                                                     | Transactions<br>on Electron<br>Devices                  | Vol.61, No. 8,<br>2674-2681,<br>2014   | IEEE                            | 10.1109/TED.2014.<br>2329551     | No             |

| 3  | Challenges and opportunities<br>in the design of Tunnel FETs:<br>materials, device<br>architectures, and defects         | D. Esseni, M.G. Pala, A.<br>Revelant, P. Palestri, L. Selmi,<br>M.(Oscar) Li, G. Snider, D. Jena,<br>H.G. Xing                                                                  | ECS<br>Transactions                                     | Vol. 64, issue<br>6, 581-595,<br>2014  | ECS                             | 10.1149/06406.058<br>1ecst       | No             |

| 4  | Pseudopotential calculations<br>of strained-GeSn/SiGeSn<br>hetero-structures                                             | Saurabh Sant and Andreas<br>Schenk                                                                                                                                              | Appl. Phys.<br>Lett.                                    | 105, 162101, ,<br>2014                 | AIP                             | 10.1063/1.4898676                | No             |

| 5  | Vertical InAs-Si Gate-All-<br>Around Tunnel FETs<br>Integrated on Si Using<br>Selective Epitaxy in<br>Nanotube Templates | D.Cutaia, K.E.Moselund, M.Borg,<br>H.Schmid, L.Gignac,<br>C.M.Breslin, S.Karg, E.Uccelli,<br>H.Riel                                                                             | Journal of<br>Electron<br>Device<br>Society (J-<br>EDS) | Vol. 3, Issue<br>3, 176 - 183,<br>2015 | IEEE                            | 10.1109/JEDS.201<br>5.2388793    | No             |

| 6  | Impact of TFET<br>Unidirectionality and<br>Ambipolarity on the<br>Performance of 6T SRAM<br>Cells                        | S. Strangio, P. Palestri, D.<br>Esseni, L. Selmi, F. Crupi, S.<br>Richter, Q. T. Zhao and S. Mantl                                                                              | Journal of<br>Electron<br>Device<br>Society (J-<br>EDS) | Vol. 3, Issue<br>3, 223-232,<br>2015   | IEEE                            | 10.1109/JEDS.201<br>5.2392793    | No             |

| 7  | Strained Si and SiGe<br>Nanowire Tunnel FETs for<br>Logic and Analog<br>Applications                                     | Q. T. Zhao, S. Richter, C.<br>Schulte-Braucks, L. Knoll, S.<br>Blaeser, G.V. Luong, S.<br>Trellenkamp, A. Schäfer, A.<br>Tiedemann, K. K. Bourdelle, S.<br>Mantl                | J. Electronic<br>Devices<br>Society                     | Vol. 3, Issue<br>3, 103-114,<br>2014   | IEEE                            | 10.1109/JEDS.201<br>5.2400371    | No             |

| 8  | Lasing in direct bandgap<br>GeSn alloy grown on Si                                                                       | S. Wirths, S. Mantl, D.Buca, et al.                                                                                                                                             | Nature<br>Photonics                                     | Vol 9, 88-92,<br>2015                  | Nature                          | 10.1038/nphoton.2<br>014.321     | No             |

| 9  | Experimental demonstration<br>of planar SiGe on Si TFETs<br>with counter doped pocket                                    | S. Blaeser, S.Richter, S. Wirths,<br>S. Trellenkamp, D. Buca, Q. T.<br>Zhao, S. Mantl                                                                                           | EUROSOI-<br>ULIS 2015                                   | 297-300, 2015                          | IEEE                            | 10.1109/ULIS.2015<br>.7063832    | No             |

| 10 | Strained Si nanowire GAA n-<br>TFETs for low supply<br>voltages                                                          | G.V.Luobg, S. Trellenkamp, K.K.<br>Bourdelle, Q. T. Zhao, S. Mantl                                                                                                              | EUROSOI-<br>ULIS 2015                                   | 65-68, 2015                            | IEEE                            | 10.1109/ULIS.2015<br>.7063774    | No             |

| 11 | III-V Nanowire CMOS<br>Monolithically Integrated on<br>Si                                                                | Johannes Svensson, Anil Dey,<br>Daniel Jacobson, Lars-Erik<br>Wernersson                                                                                                        | Nano<br>research                                        | Vol 7 Issue<br>12, 1769-<br>1776, 2015 | Tsinghua<br>University<br>Press | 10.1007/s12274-<br>014-0536-6    | No             |

| 12 | Analysis of InAs-Si<br>Heterojunction Nanowire<br>Tunnel FETs: Extreme                                                   | Hamilton Carrillo-Nunez, Mathieu<br>Luisier, Andreas Schenk                                                                                                                     | Solid State<br>Device<br>Research                       | 2014 44th,<br>118-119, 2015            | IEEE                            | 10.1109/ESSDER<br>C.2014.6948772 | No             |

| No | Title                                                                                                                     | Authors                                                                                                                                    | Title of the<br>periodical or<br>the series          | Volume,<br>pages and<br>year            | Publisher | Permanent<br>identifiers (D.O.I) | Open<br>access |

|----|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------|-----------|----------------------------------|----------------|

|    | Confinement vs. Bulk                                                                                                      |                                                                                                                                            | Conference<br>(ESSDERC),<br>European                 |                                         |           |                                  |                |

| 13 | Modeling direct band-to-band<br>tunneling: from bulk to<br>quantum-confined<br>semiconductor devices                      | Hamilton Carrillo-Nunez, Anne<br>Ziegler, Mathieu Luisier, Andreas<br>Schenk                                                               | Journal of<br>Applied<br>Physics                     | 117,<br>234501_1-10,<br>2015            | AIP       | 10.1063/1.4922427                | No             |

| 14 | Negative differential<br>resistance in direct bandgap<br>GeSn p-i-n structures                                            | C. Schulte-Braucks, et al.,                                                                                                                | Journal of<br>Applied<br>Physics                     | 117, 2015                               | AIP       | 10.1063/1.4927622                | No             |

| 15 | Ternary and quaternary<br>Ni(Si)Ge(Sn) contact<br>formation for highly strained<br>Ge p- and n- MOSFETs                   | S. Wirths et al.,                                                                                                                          | Semiconduct<br>or Science<br>and<br>technology       | Vol 30 Issue<br>5, , 2015               | IOP       |                                  | No             |

| 16 | High-k Gate Stacks on Low<br>Bandgap Tensile Strained<br>Ge and GeSn Alloys for<br>Field-E ect Transistors                | S. Wirths et al.,                                                                                                                          | Applied<br>Materials &<br>Interfaces                 | Vol 7 Issue 1,<br>62-67, 2014           | ACS       | 10.1021/am507524<br>8            | No             |

| 17 | Vertical InAs-Si Gate-All-<br>Around Tunnel FETs<br>Integrated on Si Using<br>Selective Epitaxy in<br>Nanotube Templates  | D.Cutaia, K.E.Moselund, M.Borg,<br>H.Schmid, L.Gignac,<br>C.M.Breslin, S.Karg, E.Uccelli,<br>H.Riel                                        | Journal of<br>Electron<br>Device<br>Society,<br>2015 | Vol 3 Issue 3,<br>176-183, 2015         | IEEE      | 10.1109/JEDS.201<br>5.2388793    | No             |

| 18 | Efficient quantum mechanical<br>simulation of band-to-band<br>tunneling                                                   | Cem Alper, Pierpaolo Palestri,<br>Jose L Padilla, Antonio Gnudi,<br>Roberto Grassi, Elena Gnani,<br>Mathieu Luisier, Adrian M<br>Ionescu,  | EUROSOI-<br>ULIS 2015                                | 141-144, 2015                           | IEEE      | 10.1109/ULIS.2015<br>.7063793    | No             |

| 19 | Modeling the Imaginary<br>Branch in III-V Tunneling<br>Devices: Effective Mass vs k<br>· p                                | Cem Alper , Michele Visciarelli,<br>Pierpaolo Palestri, Jose L.<br>Padilla , Antonio Gnudi, Elena<br>Gnani, Adrian M. Ionescu              | SISPAD<br>2015,<br>Washington<br>D.C.                | 273-276, 2015                           | IEEE      | 10.1109/SISPAD.2<br>015.7292312  | No             |

| 20 | Impact of TFET<br>Unidirectionality and<br>Ambipolarity on the<br>Performance of 6T SRAM<br>Cells                         | Sebastiano Strangio, Pierpaolo<br>Palestri, David Esseni, Luca<br>Selmi, Felice Crupi, Simon<br>Richter, Qing-Tai Zhao, Siegfried<br>Mantl | Journal of<br>the Electron<br>Devices<br>Society     | Vol 3 Issue 3,<br>223-232, 2015         | IEEE      | 10.1109/JEDS.201<br>5.2392793    | No             |

| 21 | Two dimensional quantum<br>mechanical simulation of<br>lowdimensional tunneling<br>devices                                | C. Alper, P. Palestri, L. Lattanzio,<br>J.L. Padilla, A.M. Ionescu                                                                         | Solid-State<br>Electronics                           | Vol 113, 167-<br>172, 2015              | Elsevier  | 10.1016/j.sse.2015<br>.05.030    | No             |

| 22 | Capacitance estimation for<br>InAs Tunnel FETs by means<br>of full-quantum k·p<br>simulation. Solid-State<br>Electronics. | Baravelli E., Gnani E., Gnudi A.,<br>Reggiani S., Baccarani, G.                                                                            | ULIS<br>Conference<br>Paper                          | Vol 108, 104-<br>109, 2015              | Elsevier  | 10.1016/j.sse.2014<br>.12.005    | No             |

| 23 | Essential Physics of the<br>OFF-State Current in<br>Nanoscale MOSFETs and<br>Tunnel FETs                                  | Esseni, D.; Pala, M.G.; Rollo, T.,                                                                                                         | IEEE<br>Transactions<br>on Electron<br>Devices       | Vol. 62, n. 9,<br>3084-3091,<br>2015    | IEEE      | 10.1109/TED.2015.<br>2458171     | No             |

| 24 | Mixed Tunnel-FET/MOSFET<br>Level Shifters: a new<br>proposal to extend the<br>Tunnel-FET application<br>domain            | M. Lanuzza, S. Strangio, F.<br>Crupi, P. Palestri, D. Esseni                                                                               | IEEE<br>Transactions<br>on Electron<br>Devices       | vol.62, no.12,<br>pp.3973-3979,<br>2015 | IEEE      | 10.1109/TED.2015.<br>2494845     | No             |

| 25 | III–V device integration on Si<br>using template-assisted<br>selective epitaxy                                            | Schmid, H.; Borg, M.; Moselund,<br>K.; Gignac, L.; Breslin, C.;<br>Bruley, J.; Cutaia, D.; Riel, H.                                        | Device<br>Research<br>Conference                     | vol., no.,<br>pp.255-256,<br>21-24 June | IEEE      | 10.1109/DRC.2015<br>.7175666     | No             |

| No | Title                                                                                                                         | Authors                                                                                                                       | Title of the<br>periodical or<br>the series                                                                                                                     | Volume,<br>pages and<br>year                    | Publisher         | Permanent<br>identifiers (D.O.I)  | Open<br>access |

|----|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------|-----------------------------------|----------------|

|    |                                                                                                                               |                                                                                                                               | (DRC), 2015<br>73rd Annual                                                                                                                                      | 2015                                            |                   |                                   |                |

| 26 | Band-Offset Engineering for<br>GeSn-SiGeSn Hetero Tunnel<br>FETs and the Role of Strain                                       | Sant, S.; Schenk, A.                                                                                                          | Electron<br>Devices<br>Society,<br>IEEE Journal<br>of the                                                                                                       | vol.3, no.3,<br>pp.164-175,<br>May 2015         | IEEE              | 10.1109/JEDS.201<br>5.2390971     | No             |

| 27 | A quasi 2D semianalytical<br>model for the potential profile<br>in hetero and homojunction<br>tunnel FETs                     | Villani, F.; Gnani, E.; Gnudi, A.;<br>Reggiani, S.; Baccarani, G.                                                             | Solid State<br>Device<br>Research<br>Conference<br>(ESSDERC),<br>2014 44th<br>European                                                                          | pp.262-265,<br>22-26 Sept.<br>2014              | IEEE              | 10.1109/ESSDER<br>C.2014.6948810  | No             |

| 28 | Improved Tunnel-FET<br>Inverter Performance with<br>SiGe/Si Heterostructure<br>Nanowire TFETs by<br>Reduction of Ambipolarity | S. Richter, S. Trellenkamp, A.<br>Schäfer, J. M. Hartmann, K. K.<br>Bourdelle, Q. T. Zhao, S. Mantl                           | Solid-State<br>Electronics                                                                                                                                      | Volume 108, ,<br>Pages 97–<br>103, June<br>2015 | Elsevier          | doi:10.1016/j.sse.2<br>015.02.018 | No             |

| 29 | Mechanisms of Template-<br>Assisted Selective Epitaxy of<br>InAs nanowires on Si                                              | M. Borg, H. Schmid, K.E.<br>Moselund, D. Cutaia, H. Riel                                                                      | J. Appl.<br>Phys.                                                                                                                                               | 117, 144303<br>(2015)                           | AIP<br>Publishing | 10.1063/1.4916984                 | No             |

| 30 | Template-assisted selective<br>epitaxy of III–V nanoscale<br>devices for co-planar<br>heterogeneous integration<br>with Si    | D. Cutaia, K. E. Moselund, M.<br>Borg, H. Schmid, L. Gignac, C.M.<br>Breslin, S. Karg, E. Uccelli, P.<br>Nirmalraj, H. Riel   | Appl. Phys.<br>Lett                                                                                                                                             | 106, 233101<br>(2015)                           | AIP<br>Publishing | 10.1063/1.4921962                 | No             |

| 31 | Mixed device-circuit<br>simulations of 6T/8T SRAM<br>cells employing tunnel-FETs                                              | S. Strangio, P. Palestri, D.<br>Esseni, L. Selmi, F. Crupi                                                                    | Gruppo<br>Italiano di<br>Elettronica<br>47th Annual<br>Meeting,<br>Proceedings<br>of the<br>(GE 2015)                                                           | pp. 81-82                                       |                   |                                   | Yes            |

| 32 | Simulation analysis of III-V n-<br>MOSFETs: channel<br>materials, Fermi level pinning<br>and biaxial strain                   | Enrico Caruso, Daniel Lizzit,<br>Patrik Osgnach, David Esseni,<br>Pierpaolo Palestri, Luca Selmi                              | Electron<br>Devices<br>Meeting<br>(IEDM), 2014<br>IEEE<br>International                                                                                         | pp.7.6.1-7.6.4,<br>15-17 Dec.<br>2014           | IEEE              | 10.1109/IEDM.201<br>4.7047006     | No             |

| 33 | State-of-the-art semi-<br>classical Monte Carlo<br>method for carrier transport<br>in nanoscale transistors                   | P. Palestri, E. Caruso, F. Driussi,<br>D. Esseni, D. Lizzit, P. Osgnach,<br>S. Venica, L. Selmi                               | Information<br>and<br>Communicati<br>on<br>Technology,<br>Electronics<br>and<br>Microelectron<br>ics (MIPRO),<br>2015 38th<br>International<br>Convention<br>on | pp.1-8, 25-29<br>May 2015                       | IEEE              | 10.1109/MIPRO.20<br>15.7160227    | No             |

| 34 | Modeling the Imaginary<br>Branch in III-V Tunneling<br>Devices: Effective Mass vs k<br>· p                                    | Cem Alper , Michele Visciarelli,<br>Pierpaolo Palestri, Jose L.<br>Padilla , Antonio Gnudi, Elena<br>Gnani, Adrian M. Ionescu | Simulation of<br>Semiconduct<br>or Processes<br>and Devices<br>(SISPAD),<br>2015                                                                                | pp.273-276, 9-<br>11 Sept. 2015                 | IEEE              | 10.1109/SISPAD.2<br>015.7292312   | No             |

| No | Title                                                                                                 | Authors                                                                                           | Title of the<br>periodical or<br>the series               | Volume,<br>pages and<br>year               | Publisher                             | Permanent<br>identifiers (D.O.I) | Open<br>access |

|----|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------|---------------------------------------|----------------------------------|----------------|

|    |                                                                                                       |                                                                                                   | International<br>Conference<br>on                         |                                            |                                       |                                  |                |

| 35 | III-V Heterostructure<br>Nanowire Tunnel FETs                                                         | Lind, E.; Memisevic, E.; Dey,<br>A.W.; Wernersson, LE.                                            | Electron<br>Devices<br>Society,<br>IEEE Journal<br>of the | vol.3, no.3,<br>pp.96-102,<br>May 2015     | IEEE                                  | 10.1109/JEDS.201<br>5.2388811    | Yes            |

| 36 | Impact of TFET<br>Unidirectionality and<br>Ambipolarity on the<br>Performance of 6T SRAM<br>Cells     | Strangio S., Palestri P., Esseni<br>D., Selmi L., Crupi F., Richter S.,<br>Zhao Q., Mantl, S., ", | Journal of<br>the Electron<br>Devices<br>Society          | n. 3, vol. 3,<br>pag. 223-232,<br>May 2015 | IEEE                                  | 10.1109/JEDS.201<br>5.2392793    | No             |

| 37 | Thin electron beam defined<br>hydrogen silsesquioxane<br>spacers for vertical nanowire<br>transistors | E. Memisevic, É. Lind, LE.<br>Wernersson                                                          | J. Vac. Sci.<br>Technol. B                                | 32, 051211<br>(2014);                      | AIP<br>Publishing                     | 10.1116/1.4895112                | No             |

| 38 | Narrow Gap<br>Semiconductors: From<br>Nanotechnology to RF-<br>Circuits on Si                         | Lars-Erik Wernersson                                                                              | J. Appl.<br>Phys.                                         | 117, 112810<br>(2015);                     | AIP<br>Publishing                     | 10.1063/1.4913836                | No             |

| 39 | III-V compound<br>semiconductor transistors –<br>from planar to nanowire<br>structures                | H. Riel, LE. Wernersson, M.<br>Hong. J. del Alamo                                                 | MRS Bulletin                                              | Vol. 39, Iss.<br>08, pp 668-<br>677, 2014  | Cam-<br>bridge<br>University<br>Press | 10.1557/mrs.2014.<br>137         | No             |

#### **Table A.2.** List of Dissemination activities (public). Status 23 November 2015.

|    |                                                                                                       |                                                                                                                                                       | LIST OF DISS                                        | EMINATIO                                                                                 | N ACTIVITIES |                                               |                             |                               |

|----|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|--------------|-----------------------------------------------|-----------------------------|-------------------------------|

| No | Type of<br>activities                                                                                 | activities leader                                                                                                                                     |                                                     | Start<br>date                                                                            | Place        | Type of audi-<br>ence                         | Size<br>of<br>audi-<br>ence | Coun-<br>tries ad-<br>dressed |

| 1  | Web sites /<br>Applications                                                                           | SCIPROM                                                                                                                                               | E2SWITCH project website                            | 01/01/14 www.e2switch.org                                                                |              | Academic,<br>Public, Policy<br>makers, Medias | >500                        | World                         |

| 2  | Scientific<br>presentation                                                                            | IBM The futur of nanoelectronics 24/02/14 5th International Workshop<br>on Advanced Scanning<br>Probe Microscopy<br>Techniques, Karlsruhe,<br>Germany |                                                     | Academic                                                                                 | 0-99         | World                                         |                             |                               |

| 3  | Scientific<br>presentation                                                                            | IBM                                                                                                                                                   | III-V Semiconductor Nanowires<br>for Future Devices | Vanowires 27/03/14 Design, Automation and<br>Test in Europe 2014,<br>Dresden, Germany    |              | Academic                                      | 0-99                        | Europe                        |

| 4  | Flyer                                                                                                 | SCIPROM                                                                                                                                               | Project flyer                                       | 01/04/14                                                                                 |              | Academic                                      | 100-<br>499                 | World                         |

| 5  | Scientific IUNET 15th International Conference on 07/04/14 Ultimate Integration on Silicon, ULIS 2014 |                                                                                                                                                       | Stockholm; Sweden                                   | Academic                                                                                 | 0-99         | World                                         |                             |                               |

| 6  | Scientific<br>presentation                                                                            |                                                                                                                                                       |                                                     | Swiss NanoConvention.<br>Windisch, Switzerland                                           | Academic     | 0-99                                          | Switzerl and                |                               |

| 7  |                                                                                                       |                                                                                                                                                       | 10/06/14                                            | International Summer<br>School on Physics at<br>Nanoscale, Devet Skal,<br>Czech Republic | Academic     | 0-99                                          | World                       |                               |

|    |                            |                                                                                                                                               | LIST OF DISS                                                                                                                         | EMINATIO                                                                                                        | N ACTIVITIES                                                                 |                       |                             |                               |

|----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------|-----------------------------|-------------------------------|

| No | Type of<br>activities      |                                                                                                                                               |                                                                                                                                      | Start<br>date                                                                                                   | Place                                                                        | Type of audi-<br>ence | Size<br>of<br>audi-<br>ence | Coun-<br>tries ad-<br>dressed |

| 8  | Scientific<br>presentation | JUELICH                                                                                                                                       | Experimental Demonstration of<br>Inverter and NAND Operation in<br>p-TFET logic at Ultra-low Supply<br>Voltages down to VDD = 0.15 V | 22/06/14                                                                                                        | 72nd Device Research<br>Conference (DRC), UC<br>Santa Barbara, USA           | Academic              | 100-<br>499                 | World                         |

| 9  | Scientific presentation    | IBM                                                                                                                                           | Semiconducting Nanowires –<br>From Materials to Devices                                                                              | 07/07/14                                                                                                        | CMOS Emerging<br>Technologies Research<br>2014, Grenoble, France             | Academic              | 0-99                        | Europe                        |

| 10 | Scientific<br>presentation | IBM                                                                                                                                           | Dynamics of III-V MOVPE inside nanotube templates on Si                                                                              | 13/07/14                                                                                                        | ICMOVPE XVII Lausanne                                                        | Academic              | 100-<br>499                 | World                         |