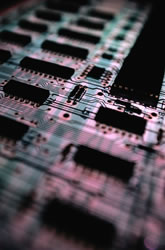

La nouvelle architecture des semi-conducteurs ouvre la voie à une nouvelle ère en nanoélectronique

Dans la mesure où les transistors sont les principaux éléments des circuits intégrés, ils jouent un rôle important dans le fonctionnement correct de l'ensemble du dispositif micro-électronique. Un des types de transistors les plus utilisés est le transistor MOS (Metal Oxide Semiconductor Field Effect Transistors). Utilisés désormais à l'échelle du nanomètre, les composants des transistors MOS ont été analysés en détail et optimisés afin d'assurer le fonctionnement fiable du dispositif. L'un des principaux points d'intérêt de la technologie de source/drain est la hauteur de la barrière de Schottky du contact de siliciure pour la conductivité du courant. Dans le cas des transistors MOS à source/drain Schottky, les zones fortement dopées normalement implantées/diffusées pour la zone source/drain sont remplacées par des zones de siliciure qui se comportent de la même manière que les métaux. En outre, une zone source/drain à base de siliciure de type p avec une faible barrière Schottky présente une grande stabilité thermique. Le projet SODAMOS a conçu, optimisé et fabriqué un ensemble de transistors MOS à faible barrière Schottky sur un film SOI (silicium sur isolant) en vue de résoudre les problèmes critiques liés à l'architecture source/drain. Comparée aux architectures traditionnelles, cette technologie présente plusieurs avantages, tels que de meilleures performances en termes d'immunité aux effets des circuits courts, la suppression de la sensibilité à la fluctuation des dopants et une diminution de la résistance de contact des zones source/drain. Il est en outre apparu que les contacts source/drain Schottky permettaient d'inhiber les problèmes liés à un contrôle serré du dopage source/drain. Au niveau de la technologie des matériaux, il s'est avéré que le développement de blocs élémentaires Pt était compatible avec le transistor CMOS actuel déjà introduit dans la chaîne de fabrication. Il apparaît de manière évidente que ce concept de laboratoire a de grandes chances de devenir une solution attrayante d'un point de vue industriel. En outre, cette innovation répond aux exigences de l'International Technology Roadmap for Semiconductors (ITRS) en s'orientant vers le noeud technologique de 35nm et, à terme, de 22nm.