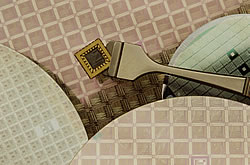

De nouvelles perspectives pour la miniaturisation des circuits intégrés

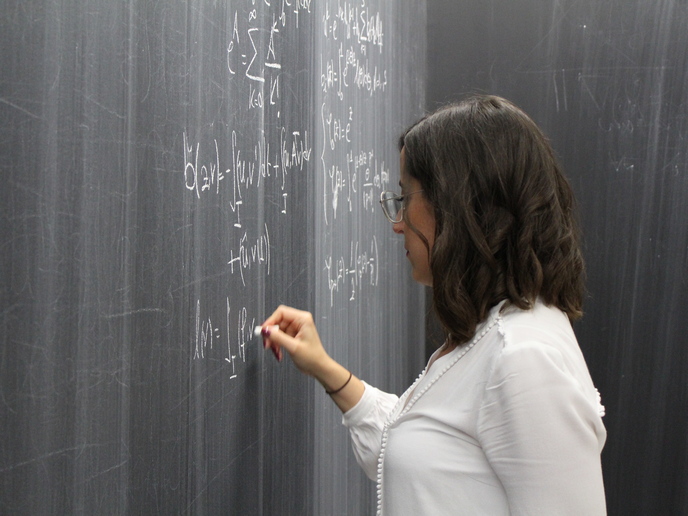

L'évolution des circuits intégrés a eu un impact significatif sur divers domaines d'application où l'échelle nanométrique et la vitesse élevée des dispositifs électroniques jouent un rôle important (analyses médicales, biologiques, chimiques et télécommunications). Cependant, la contrainte mécanique qui s'accumule dans les couches et les substrats durant le traitement des composants des circuits intégrés restreint leur miniaturisation et affecte sérieusement les performances et la fiabilité des dispositifs. Par conséquent, ces contraintes doivent être constamment contrôlées et des mesures doivent être prises pour les réduire. Dans le cas contraire, les déformations des réseaux peuvent atteindre des niveaux excédant les valeurs critiques au-delà desquelles se produisent des dislocations dégradant le dispositif électronique. La microscopie électronique en transmission (TEM) a un rôle essentiel dans l'industrie de la micro-électronique. Elle constitue un moyen efficace de mettre en place des activités rigoureuses de recherche, de développement et de production lorsque les outils d'analyse morphologiques et analytiques sont devenus moins efficaces, en raison de la réduction de taille des dispositifs. L'extension attendue de la TEM dans l'industrie des semi-conducteurs permettra également de promouvoir et d'étendre le champ d'application des diverses fonctionnalités analytiques de cet instrument. La technique de la diffraction électronique en faisceau convergent (CBED) permet d'analyser les déformations des réseaux dans les cristaux. Cependant, cette application a jusqu'à présent connu une utilisation limitée, car la procédure requise pour extraire le tenseur déformation local du schéma TEM/CBED s'effectue de manière essentiellement manuelle, ce qui nécessite des temps d'analyse assez longs. Un module logiciel a été développé dans le cadre du projet STREAM qui permet d'acquérir numériquement les schémas de diffraction et de générer le tenseur déformation dans les régions nanométriques correspondantes de la structure. Le module logiciel dispose d'une routine intégrée permettant de passer de la "valeur de tension au schéma CBED" et d'accélérer la procédure de mesure des contraintes, réduisant ainsi la durée d'évaluation de plusieurs jours à quelques heures, pour une meilleure adéquation avec les temps de réponse classiques de l'industrie. L'utilisation routinière de la méthode TEM/CBED pour analyser les contraintes permettra d'optimiser les processus afin d'éviter la défaillance des dispositifs due à l'apparition de dislocations. La baisse des défaillances inhérentes aux contraintes aura non seulement des avantages économiques, mais générera également une réduction des rebuts, avec des conséquences directes sur la surveillance environnementale.