En route pour l'ère nano-électronique

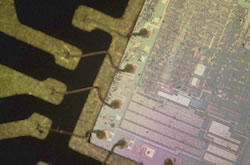

En raison des tendances actuellement observées dans le domaine de la micro-électronique, il s'avère nécessaire de développer des TEC Si à hétérostructure, car ils présentent une meilleure mobilité de porteur de charge. Cette augmentation de mobilité entraîne une amélioration des vitesses de commutation, particulièrement en ce qui concerne le SiGe contraint (ou le Si contraint sur du SiGe relaxé) dans le canal des transistors MOS. Le projet SIGMUND a permis de relever le défi consistant à optimiser les transistors nMODFET sur des couches tampon relaxées en technologie NMOS. Le n-TEC à hétérostructure requiert des couches tampon relaxées minces et le projet a abouti au développement de transistors n-MOSFET très minces (moins de 100nm) basés sur des couches de SiGe contraint contenant 35% et 50% de Ge. De nombreuses études ont été réalisées au cours du projet. Par exemple, les couches tampons relaxées ont été définies au moyen de la microscopie à force atomique, la diffraction des rayons X, la spectroscopie Raman, les simulations, la microscopie optique Nomarski avant et après un léger décapage chimique, et la MEC. Toutes ces études ont démontré que ces MOSFET SiGe à hétérostructure présentent des caractéristiques supérieures aux TEC classiques. C'est ainsi que les MOSFET SiGe du projet SIGMUND présentent des degrés élevés de relaxation et une surface lisse principalement imputables à une très faible augmentation de la température ainsi qu'aux agents de surface. Afin d'optimiser davantage les résultats, des études ont été effectuées sur l'impact de la composition de la couche et des conditions d'adaptation sur le degré de relaxation, la morphologie de surface et l'apparition de défauts. Il convient de signaler que leur processus de développement est si simple qu'il permet une mise en oeuvre aisée à l'échelle industrielle. Le porteur de charge et les performances du dispositif ont fait l'objet de recherches approfondies axées sur la contrainte de la couche, la taille quantique et les dimensions du dispositif. De plus, de nombreuses simulations physiques ont contribué à spécifier les configurations de couche optimales favorisant la mobilité et le courant de commande. La caractérisation du dispositif par rapport à la température (fourchette comprise entre 50 et 300°K) a produit en retour des résultats permettant d'optimiser le dispositif dans les maquettes électriques et de réaliser des applications prospectives dans les simulations prédictives de circuit. Par ailleurs, une caractérisation approfondie a été réalisée mettant l'accent sur la mesure des hautes fréquences et leur utilisation potentielle dans les applications spatiales (cryotempératures). D'aucuns espèrent que l'amélioration des performances permettra d'étendre la technologie à base de Si au domaine des micro-ondes.