Thermal fatigue performance in microelectronics

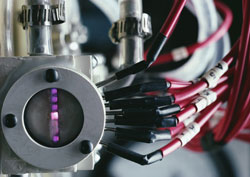

Due to development trends of microelectronics, characterised mainly by ongoing miniaturisation down to the nanoscale, research in the thermal and mechanical fatigue of electronics materials has become a prerequisite. Various inhomogeneities, residual stresses generated during the manufacturing process and extreme environmental conditions contribute to interface delamination and fatigue of solder interconnects. Since currently no standard testing methodology is available, a testing methodology was combined within the MEVIPRO project with numerical simulations for the evaluation of this mode of failure. Designed for the experimental investigation of the deformation of material compounds subjected to thermally induced shear loadings, it has been accordingly named 'Thermal Lap Shear Test'. The test is based on the thermal mismatch of a lap-shear specimen, containing an arbitrary shaped joint and mounted on a loading frame with slightly different thermal expansion coefficient. It is intended to make deformation and degradation of the joint surface visible by means of microscopic observations or provide in-situ measurements with the use of the MicroDAC method. Microscopic in-situ analysis of the deforming joint surface allows the observation of local deformations at different temperatures, which can also be played as a video sequence visualising local microstructure movements. These provides the essential means to adjust the fatigue-controlled crack propagation to that calculated by the finite element analyses, as well as for comparisons with numerical simulations. The test is applicable to both static loadings, induced by heating up and cooling down at different rates, and cyclic thermal loading applied in the temperature chamber of the microscope. It has been employed by FhG-IZM researchers to analyse the deformation and failure behaviour of SnPb-, SnAg- and SnAgCu specimens at different stages of thermal cycle tests. The combined experimental-numerical methodology showed universal application potentials, for studies on the fatigue-induced degradation of solders with spurious alloying elements, electronic adhesives and many more.