Die Steuerung von Mikroprozessoren der nächsten Generation

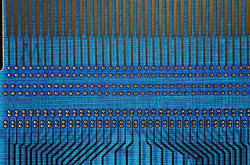

Die Lithografie ist ein Verfahren, mit dem Mikroschaltkreise in Siliziumwafer geätzt werden. Dabei werden die Schaltkreismuster häufig auf fototechnischem Wege aufgedruckt. Um die Schaltkreise und deren Komponenten weiter verkleinern zu können, muss der Grad der Auflösung bei fotolithografischen Verfahren verbessert werden, wobei die Auflösung abhängig von der Wellenlänge des verwendeten Lichts ist. Die International Technology Roadmap for Semiconductors (ITRS - Internationaler Technologiefahrplan für Halbleiterelemente) hat eine Reihe von "technologischen Knotenpunkten" als Meilensteine auf dem Weg zu weiterer Miniaturisierung definiert, die auf einer abnehmenden "kritischen Abmessung" (CD - Critical Dimension) von Bestandteilen der Schaltkreiselemente basiert. Bei Mikroprozessoren ist beispielsweise die Gate-Länge von Transistoren eine kritische Abmessung im Hinblick auf die Prozessorgeschwindigkeit. Im Rahmen des Projekts "Usable vacuum ultra violet lithography" (UV2Litho) wurden vier metrologische Verfahren zur Messung und Fertigungskontrolle untersucht, die zur Fabrikation von Elementen der kritischen Abmessung von 65nm erforderlich sind. Die folgenden vier Messverfahren wurden dabei ausgewertet: Rasterelektronenmikroskopie (CD-SEM), CD-Scatterometrie, Rasterkraftmikroskopie (CD-AFM) und kombinierte Methoden. Fünf Kriterien wurden zur Bewertung herangezogen: zeitnahe Verfügbarkeit, höchstmögliche Auflösung, Präzision, Wechselwirkung mit den gemessenen Strukturen und universale Anwendbarkeit. Als Richtgröße wurde für jedes der Verfahren die ITRS zum Vergleich herangezogen. Dabei wurde versucht, innovative Methoden zu bewerten und Schwachstellen der neuesten dieser Technologien auszumachen. Durch das Projekt wurde herausgefunden, dass der Toolabgleich, d.h. die Sicherstellung der Konsistenz der Messungen mit verschiedenen Metrologietools in unterschiedlichen Herstellerbetrieben, einen kritischen Punkt darstellt. Das Team stellte fest, das keines der untersuchten Messverfahren die Anforderungen an den Geräteabgleich für die 65nm-Technologie erfüllte. In der Anfangsphase der Entwicklung von 65nm-Nodes könnte jedoch ein einzelnes Gerät für die Messung von Siliziumwafern in geringem Umfang bei höchster Auflösung und Genauigkeit eingesetzt werden. Im Handel erhältliche Geräte kommen den erforderlichen Leistungsparametern schon nahe. In der Folge des Projekts werden jetzt Hersteller von Halbleiterbauteilen gesucht, welche die Ergebnisse kommerziell verwerten und empfohlene Verfahren zum (Mess-)Toolabgleich nutzen möchten. Die Ergebnisse unterstützen wahrscheinlich die Auswahl von Metrologietools und umfassen Folgerungen für die Abstimmung von Tools anhand unterschiedlicher Verfahren wie z.B. die Kombination von gebündelter Ionenstrahl- und Rasterelektronenmikroskopie (FIB+SEM) mit CD-AFM und CD-Scatterometrie. Weiterhin sucht das Team Kontakt zu Halbleiterproduzenten bzw. -konsortien, um bei weiteren Entwicklungsschritten in Richtung der 45nm-Node-Technologie zusammenzuarbeiten. Die Ergebnisse sind auch für 65nm-Verfahren interessant, die nicht die Fotolithografie mit Wellenlängen von 157nm verwenden.