Le potentiel des FinFET enfin concrétisé

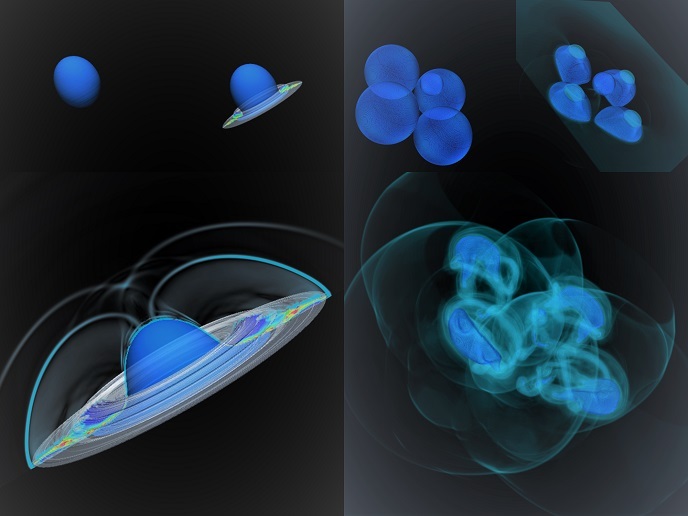

Pour concevoir des circuits intégrés, on peut choisir entre trois types de transistors: classiques planaires massifs et à effet de champ, (FET), silicium sur isolant «complètement déplété» (FD-SOI), et FinFET. Seuls les FinFET permettent de pousser les CMOS jusqu'aux 10 nanomètres. Les chercheurs du projet PERSEUS (3D modelling of the performance and variability of high electron mobility transistors for future digital applications), financé par l'UE, ont étudié l'évolutivité des FinFET au silicium et à l'InGaAs. Dans une structure FinFET à plusieurs portes, le corps semi-conducteur est placé sur la tranche pour former un «aileron» (fin en anglais) de matériau, perpendiculaire au plan de la galette. Une électrode de porte est formée sur l'aileron. L'équipe de PERSEUS a utilisé une simulation 3D de pointe pour étudier les performances de différents FinFET, dont les dimensions ont été choisies pour répondre aux objectifs du calendrier technologique international 2012 des semi-conducteurs. Pour un FinFET de type silicium sur isolant (SOI), le fait de réduire la longueur de la porte de 12,8 à 8,1 nanomètres augmente de 64 % le courant ON. Pour un FinFET en arséniure d'indium-gallium sur isolant (InGaAs-OI), l'augmentation a été de 44 % lorsque la longueur de la porte est réduite de 14 à 10,4 nanomètres. Les chercheurs de PERSEUS ont aussi étudié l'impact de trois sources microscopiques de fluctuations sur les performances des FinFET SOI et InGaAs-OI. Ils ont simulé dans 300 transistors différents à l'échelle microscopique la présence de dopants aléatoires, de rugosités ligne-bord, et de variations dans la fonction de la porte métallique. Les dopants aléatoires ont induit des variations de tension dans les FinFET en SOI et InGaAs-OI. Les rugosités ligne-bord ont eu un effet similaire. Cependant, la fonction de porte métallique a été la source dominante de perturbations. Les travaux sur les FinFET sont très importants, pour les universités comme pour le secteur, afin de satisfaire aux exigences des systèmes et des circuits. Les résultats du projet PERSEUS devraient apporter des indices pour faire le meilleur choix en fonction des applications numériques futures. Pour le secteur européen des semi-conducteurs, ils réduiront le coût de la production et amélioreront l'efficacité avec des dispositifs plus résistants à la variabilité.