Potencjał FinFET wykorzystany

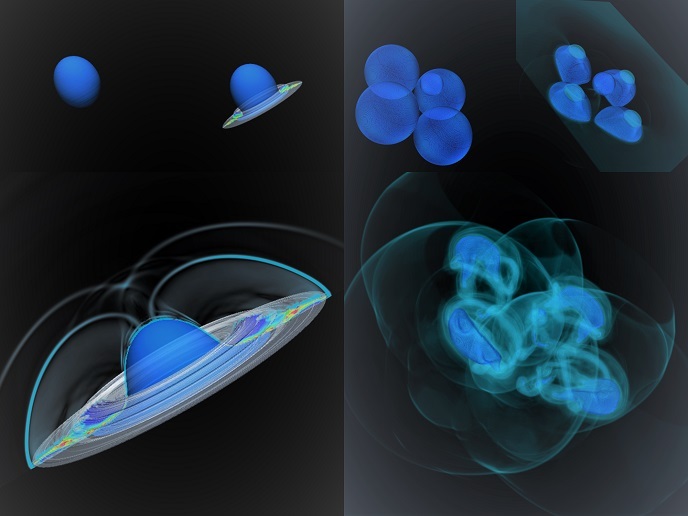

Projektanci układów scalonych mają do wyboru trzy rodzaje tranzystorów: tradycyjne płaskie tranzystory polowe (FET), tranzystory FD-SOI (fully depleted silicon-on-insulator) oraz tranzystory FinFET. Tylko FinFET dają możliwość rozszerzenia technologii CMOS na wymiary mniejsze niż 10 nanometrów. W ramach projektu PERSEUS (3D modelling of the performance and variability of high electron mobility transistors for future digital applications), finansowanego ze środków UE, naukowcy podjęli się zbadania skalowalności FinFET z Si i InGaAs. W tej wielobramkowej strukturze półprzewodnik obracany jest na bok i tworzy "płetwę" materiału umieszczonego prostopadle do płaszczyzny płytki. Wzdłuż "płetwy" powstaje elektroda bramki. Przy pomocy nowoczesnych narzędzi do symulacji 3D zespół projektu PERSEUS badał działanie różnych FinFET o wymiarach wybranych w celu spełnienia wymagań określonych w międzynarodowym planie działań technologicznych w dziedzinie półprzewodników z 2012 r. W przypadku FinFET z izolatorem SOI zmniejszenie długości bramki z 12,8 do 8,1 nanometra spowodowało zwiększenie prądu załączania o 64%. W przypadku FinFET typu InGaAs-OI (InGaAs-On-Insulator) wzrost ten wyniósł 44% po skróceniu bramki z 14,0 do 10,4 nanometra. Ponadto uczeni zbadali wpływ trzech różnych źródeł mikroskopowych na fluktuacje oddziałujące na sprawność FinFET typu SOI i InGaAs-OI. Obecność bezładnych domieszek, szorstkość linii krawędzi i zmiany funkcji metalowej bramki symulowano w 300 różnych tranzystorach w skali mikroskopowej. Bezładne domieszki indukowały zmiany napięcia zarówno w FinFET typu SOI, jak i InGaAs-OI. Szorstkość linii krawędzi również powodowała podobne zmiany napięcia. Głównym źródłem zakłóceń były jednak zmiany funkcji bramki metalowej. Prowadzone w ramach projektu badania nad FinFET mają nieocenione znaczenie dla nauki i przemysłu, gdyż pomagają w spełnieniu przyszłych wymagań dotyczących obwodów i systemów. Inicjatywa PERSEUS powinna dostarczyć konstruktorom wskazówek dotyczących tego, które rozwiązania będą najbardziej odpowiednie dla przyszłych urządzeń cyfrowych. Europejska branża półprzewodnikowa skorzysta natomiast na obniżeniu kosztów produkcji i poprawie wydajności urządzeń, które będą bardziej stabilne.