Realizzato il potenziale della tecnologia FinFET

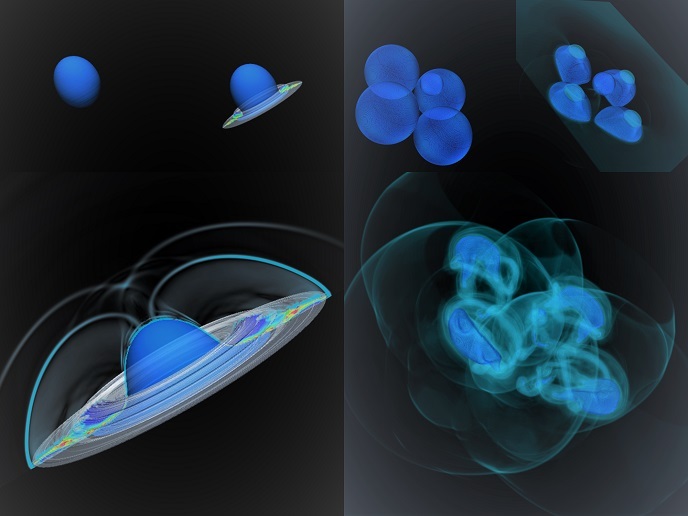

Nella progettazione dei circuiti integrati, esistono tre tipi di transistor: transistor planari tradizionali a effetto di campo (FET), transistor FD-SOI e FinFET. Solo i FinFET offrono la possibilità di estendere la tecnologia CMOS per dimensioni al di sotto dei 10 nanometri. Nell’ambito del progetto PERSEUS (3D modelling of the performance and variability of high electron mobility transistors for future digital applications), finanziato dall’UE, i ricercatori hanno studiato la scalabilità di Si e InGaAs nei transistor FinFET. In questa struttura a entrata multipla, il corpo del semiconduttore è girato su un lato per formare una “pinna” di materiale perpendicolare rispetto al piano del wafer. Un elettrodo gate è formato lungo la pinna. Utilizzando strumenti di simulazione 3D all’avanguardia, il team PERSEUS ha studiato le prestazioni di diversi FinFET, aventi dimensioni selezionate per raggiungere gli obiettivi fissati dalla International technology roadmap for semiconductors del 2012. Per un SOI FinFET, la riduzione della lunghezza relativa al gate, da 12,8 a 8,1 nanometri, ha aumentato la corrente di saturazione del 64 %. Per il FinFET InGaAs-OI, l’aumento risulta essere del 44 %, quando la lunghezza del gate è stata ridimensionata da 14,0 a 10,4 nanometri. Inoltre, i ricercatori PERSEUS hanno studiato l’impatto di tre diverse fonti microscopiche di fluttuazione, che influenzano le prestazioni dei FinFET SOI e InGaAs-OI. La presenza di droganti casuali, rugosità ai bordi e variazioni di funzionamento del gate in metallo sono state simulate in 300 transistor diversi a livello microscopico. I droganti casuali hanno indotto variazioni di tensione nei FinFET SOI e InGaAs-OI. La rugosità ai bordi ha provocato variazioni di tensione simili a quelle prodotte dai droganti casuali. Tuttavia, le variazioni di funzione del gate in metallo hanno costituito la fonte principale di dispersioni. I risultati del progetto sui FinFET hanno un valore inestimabile per il mondo accademico e industriale, al fine di soddisfare i rigorosi requisiti di circuito e sistema futuri. I risultati del progetto PERSEUS dovrebbero fornire ai progettisti un’idea riguardo alla scelta migliore per le future applicazioni digitali. Il beneficio portato all’industria europea dei semiconduttori è costituito da un minor costo di produzione e una maggiore efficienza, per dispositivi con una maggiore resistenza alla variabilità.