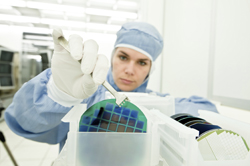

Geschwindigkeitsbarriere bei Halbleitern durchbrechen

Intel-Mitbegründer Gordon Moore sagte in den 1960er Jahren voraus, dass sich die Anzahl der Transistoren auf einem Chip ungefähr alle 24 Monate verdoppeln wird. Diese als Mooresches Gesetz bekannte Prognose bildete im Wesentlichen das Geschäftsmodell für die Halbleiterindustrie, deren exponentielles Wachstum bis heute ungebremst andauert. Die Quantität verliert jedoch angesichts des Drucks in Richtung kleiner und leistungsfähigerer Elektronik an Einfluss gegenüber der Qualität, die in diesem Fall durch die Leistung gemessen wird. Will man die der Geschwindigkeit in CMOS-Schaltungen (komplementärer Metalloxidhalbleiter) über ein bestimmtes Maß hinaus optimieren, sind neue Materialien mit höherer Elektronenbeweglichkeit als Silizium (Si) erforderlich. Am vielversprechendsten sind Verbindungshalbleiter auf Basis von Materialien der Gruppen III bis V wie zum Beispiel Galliumarsenid (GaAs), Indiumgalliumarsenid (InGaAs) und Indiumphosphid (InP). Deren Integration in Si-CMOS-Technologiestellte aufgrund der Erschaffung einer Art Elektronenbeweglichkeitsbarriere zwischen dem Kanal- und dem Gate-Dielektrikum in Folge von Fehlern in den Halbleiteroberflächen eine Herausforderung dar. Die besten Resultate ergab die Atomlagenabscheidung (ALD) von Aluminiumoxid (Al2O3) anstelle von Siliziumdioxid (SiO2) als die Grenzfläche zu den III-V-Halbleitern. Dennoch ist die Defektdichte immer noch sehr viel größer als für SiO2/Si-Grenzflächen. So starteten Wissenschaftler das EU-finanzierte Projekt "Clustered atomic layer deposition for emerging microelectonic applications" (CALDERA), um kombinierte und gleichzeitig vor Ort erfolgende Messverfahren zu entwickeln, mit denen man mehr über die Defektentstehung während der Abscheidungsprozesse erfährt. Die Forscher setzten Rastertunnelmikroskopie, Rastertunnelspektroskopie und Synchrotron-Röntgen-Fotoelektronenspektroskopie ein, die noch nie zuvor bei einer einzelnen In-situ-Analyse (unter Vermeidung von jeglichem Kontakt mit Luft) derselben Probe miteinander kombiniert wurden. Die Verfahren versetzten die Forscher in die Lage festzustellen, dass die Defekterzeugung auf der InP-Oberfläche auf Oberflächenoxidation zurückzuführen war. Somit erfordert eine kostengünstige Fertigung von Hochleistungs-InP-Bauelementen zum Hochgeschwindigkeitsrechnen die Beseitigung aller Oxidationsquellen einschließlich des Abschlusses gegenüber Umgebungsluft während des gesamten Bauelementfertigungsprozesses. CALDERA führte die erste kombinierte In-situ-Analyse des Al2O3-Atomlagenabscheidungsprozesses durch, die eindeutig die Quelle der Oberflächendefekte enthüllte, welche die verminderte Leistung der Transistoren verursachen. Ausgestattet mit diesem Wissen können die Hersteller nun die Hindernisse überwinden, welche bislang einer Erhöhung der Geschwindigkeit der Transistorsschaltoperationen im Wege standen, was großen Einfluss auf die Anwendungen des Hochgeschwindigkeitsrechnens von morgen haben wird.