Rompere la barriera della velocità nei semiconduttori

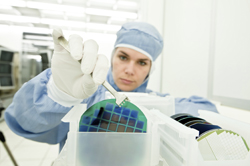

Gordon Moore, cofondatore di Intel, negli anni 60, aveva previsto che il numero di transistori in un chip sarebbe raddoppiato all'incirca ogni 24 mesi. Nota come la Legge di Moore, questa legge sostanzialmente definiva il modello di business per l'industria dei semi conduttori, la cui crescita esponenziale continua tutt'oggi. La quantità, tuttavia, sta perdendo terreno rispetto alla qualità, misurata in base alla performance in questo caso, data la spinta verso sistemi elettronici più piccoli e più potenti. L'ottimizzazione della velocità nei circuiti di semiconduttori in ossido di metallo complementari (CMOS) oltre un certo livello richiede nuovi materiali con una mobilità di elettroni superiore rispetto al silicio (Si). I più promettenti sono i semiconduttori composti basati sui materiali dei gruppi III-V, tra cui l'arseniuro di gallio (GaAs), l'arseniuro di gallio-indio (InGaAs) e il fosfuro di indio (InP). L'integrazione di questi all'interno della tecnologia Si CMOS ha rappresentato una sfida, a causa della creazione di una sorta di barriera di mobilità di elettroni tra il canale e il dielettrico di gate, quale risultato delle imperfezioni nelle superfici dei semiconduttori. La deposizione di strati atomici (ALD) di ossido di alluminio (Al2O3) al posto dell'ossido di silicio (SiO2), come l'interfaccia con i semiconduttori III-V, ha prodotto i risultati più promettenti. Ciò nonostante, la densità di difetti continua a essere ancora più ampia rispetto a quella per le interfacce SiO2/Si. Gli scienziati hanno avviato il progetto CALDERA ("Clustered atomic layer deposition for emerging microelectonic applications"), finanziato dall'UE, al fine di sviluppare tecniche di misurazione in loco, combinate e simultanee, per una maggiore comprensione della produzione dei difetti durante i processi di deposizione. I ricercatori non avevano mai adoperato prima di allora il microscopio a effetto tunnel, la spettroscopia a effetto tunnel e la spettroscopia fotoelettronica a raggi X sincrotronica, in modo combinato in una singola analisi in loco (evitando tutta l'esposizione all'aria) dello stesso campione. Le tecniche hanno consentito ai ricercatori di stabilire che la generazione dei difetti sulla superficie InP era da ricondurre all'ossidazione della superficie. Pertanto, una produzione efficiente dal punto di vista dei costi di dispositivi InP ad alte prestazioni per la computazione ad alta velocità richiederà l'eliminazione di tutte le fonti di ossidazione, compresa l'esposizione all'aria ambientale lungo tutto il processo di fabbricazione del dispositivo. CALDERA ha fornito la prima analisi combinata in loco del processo di deposizione ALD Al2O3, rivelando chiaramente la fonte dei difetti superficiali che porta a una minore prestazione dei transistori. Forti di questa esperienza, i produttori sono ora in grado di superare le precedenti barriere all'incremento della velocità delle operazioni di commutazione dei transistori per un enorme impatto sulle applicazioni di computazione ad alta velocità di domani.