Neue Modelle zur Minimierung von Schäden an Prüfspitzen

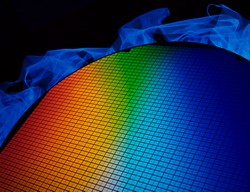

Da die Bauelemente und somit auch die Prüfspitzen immer kleiner werden, wird gleichermaßen die Strombelastbarkeit (current carrying capability, CCC) der Prüfspitze geringer. Gleichzeitig steigt der Maximalstrom, der zur Prüfung einiger Komponenten erforderlich ist. Insgesamt nimmt die Gefahr der strombedingten Prüfspitzenbeschädigung oder -verbrennung zu und das kann wiederum den Wafer selbst beschädigen. Den Wissenschaftlern gelang die Entwicklung von Modellen der Phänomene der Strombelastbarkeit, um bessere Prüfspitzenbauformen für Hochleistungswafertests zu realisieren und sie können dabei auf die EU-Finanzmittel des Projekts PROBE-BURN (Probe burn phenomena: Predictive modeling and characterization for high power wafer test applications) zurückgreifen. Die Strombelastbarkeit ist für Prüfkarten (probe cards) von entscheidender Bedeutung und hängt in der Hauptsache vom Prüfspitzendurchmesser, der Umgebungstemperatur, den thermophysikalischen Materialeigenschaften, der Dauer des angelegten Stroms und dem Kontaktwiderstand an der Prüfspitzengrenzfläche ab. Den Wissenschaftlern gelang die erfolgreiche Entwicklung eines numerischen Verfahrens, das die Temperaturverteilung entlang eines Prüfspitzenkörpers berechnen kann. Die experimentellen und rechnerischen Resultate befanden sich in ausgezeichneter Übereinstimmung und bestätigten die Gültigkeit der numerischen Verfahren zur Bestimmung der Strombelastbarkeit. Das Team entwickelte überdies Modelle, die Hilfestellung dabei geben, die Prüfkopfbauformen zu optimieren und die Grenzen der Strombelastbarkeit, bevor der Wafer beschädigt wird, genau vorherzusagen. Zudem wurden neue Simulationen entwickelt, um die Wärmeübertragung zwischen der beheizten Sonde und ihrer Umgebung zu analysieren. Experimente mit Federsonden, die in der laminaren Luftströmung und ohne Luftströmung durchgeführt wurden, befanden sich in guter Übereinstimmung mit den numerischen Resultaten. Verbrennungen an Prüfspitzen sind ein zunehmend verbreitetes Problem bei Wafertests. Neuartige Instrumente zur Gestaltung sowie zur Überwachung von Prüfspitzen während der Wafertests werden die Auswirkungen dieses drängenden Problems maßgeblich eindämmen. Resultat dessen werden außerdem erhebliche Einsparungen für die Halbleiterindustrie in Form von Geld, Zeit und Ressourcen sein.