Nuovi modelli per ridurre al minimo la bruciatura delle punte delle sonde

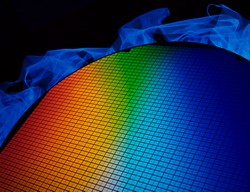

Il ridimensionamento dei dispositivi e, di conseguenza, delle punte delle sonde di prova durante le attività di testing, determina anche una riduzione della capacità di trasporto della corrente (current carrying capability, CCC). Allo stesso tempo, si assiste a un aumento della corrente massima necessaria per la conduzione dei test su alcuni componenti. Nel complesso, tali attività provocano un aumento del rischio di danneggiamento o bruciatura delle punte delle sonde di corrente che, a sua volta, determina un danneggiamento del wafer stesso. Con il finanziamento dell’UE del progetto PROBE-BURN (Probe burn phenomena: Predictive modeling and characterization for high power wafer test applications), gli scienziati sono riusciti a sviluppare modelli di fenomeni di CCC per permettere di creare sonde potenziate in grado di garantire test su wafer a elevata potenza. La CCC è fondamentale per le schede delle sonde e dipende soprattutto dal diametro della punta della sonda, la temperatura, le proprietà materiali termofisiche, la durata della corrente applicata e la resistenza di contatto all’interfaccia di aderenza della punta della sonda. Gli scienziati sono riusciti a sviluppare un metodo numerico che consente di calcolare la distribuzione della temperatura lungo il corpo di una sonda. I dati sperimentali e numerici, che hanno generato risultati estremamente coerenti, hanno confermato la validità dei metodi matematici ai fini del calcolo della capacità di trasporto della corrente. Il team ha anche sviluppato modelli in grado di aiutare a ottimizzare le sonde e prevedere esattamente i limiti di CCC prima di danneggiare il wafer. Inoltre, sono state sviluppate nuove simulazioni per analizzare il trasferimento di calore tra la sonda riscaldata e l’ambiente circostante. Gli esperimenti condotti con le sonde a molla in flusso d’aria laminare e senza flusso d’aria corrispondevano tutto sommato con i risultati numerici. Le bruciature delle sonde rappresentano un problema sempre più pressante associato ai test condotti sui wafer. L’ideazione di nuovi utensili tesi alla progettazione e al monitoraggio delle punte delle sonde nel corso delle prove condotte sui wafer dovrebbe garantire una drastica riduzione dell’impatto di tale barriera. Tali risorse dovrebbero inoltre offrire enormi risparmi per l’industria dei semiconduttori in termini di denaro, tempo e risorse.